Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | 8032                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 24MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, UART/USART                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 46                                                                      |

| Program Memory Size        | 288KB (288K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                               |

| Data Converters            | A/D 4x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 80-LQFP                                                                 |

| Supplier Device Package    | -                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/upsd3254bv-24u6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 9.1                 | External reset                                      | 55   |

|----|---------------------|-----------------------------------------------------|------|

|    | 9.2                 | Low V <sub>DD</sub> voltage reset                   | 55   |

|    | 9.3                 | Watchdog timer overflow                             | 56   |

|    | 9.4                 | USB reset                                           | 56   |

| 10 | Watc                | hdog timer                                          | 57   |

| 11 | Time                | r/counters (Timer 0, Timer 1 and Timer 2)           | 59   |

|    | 11.1                | Timer 0 and Timer 1                                 | 59   |

|    |                     | 11.1.1 Mode 0                                       | . 60 |

|    |                     | 11.1.2 Mode 1                                       | . 60 |

|    |                     | 11.1.3 Mode 2                                       | . 61 |

|    |                     | 11.1.4 Mode 3                                       | . 62 |

|    | 11.2                | Timer 2                                             | 62   |

| 12 | Stan                | dard serial interface (UART)                        | 66   |

|    | 12.1                | Multiprocessor communications                       | 66   |

|    | 12.2                | Serial port control register                        | 67   |

|    |                     | 12.2.1 Baud rates                                   | . 68 |

|    |                     | 12.2.2 Using Timer 1 to generate baud rates         | . 68 |

|    |                     | 12.2.3 Using Timer/counter 2 to generate baud rates | . 68 |

|    |                     | 12.2.4 More about Mode 0                            | . 69 |

|    |                     | 12.2.5 More about Mode 1                            | . 70 |

|    |                     | 12.2.6 More about Modes 2 and 3                     | . 71 |

| 13 | Anal                | og-to-digital convertor (ADC)                       | 77   |

|    | 13.1                | ADC interrupt                                       | 77   |

| 14 | Pulse               | e width modulation (PWM)                            | 80   |

|    | 14.1                | 4-channel PWM unit (PWM 0-3)                        | 80   |

|    | 14.2                | Programmable period 8-bit PWM                       | 82   |

|    | 14.3                | PWM 4-channel operation                             |      |

| 15 | I <sup>2</sup> C ir | nterface                                            | 84   |

|    | 15.1                | Serial status register (SxSTA: S1STA, S2STA)        |      |

|    | 15.2                | Data shift register (SxDAT: S1DAT, S2DAT)           |      |

|    |                     |                                                     | 55   |

Figure 13. State sequence in UPSD325xx devices

Table 16. List of all SFRs (continued)

| æ þ | Day Name    |     |        |           | Bit Regist | er Name    |            |            |      | set<br>ue      | 0                                   |

|-----|-------------|-----|--------|-----------|------------|------------|------------|------------|------|----------------|-------------------------------------|

| SFR | Reg Name    | 7   | 6      | 5         | 4          | 3          | 2          | 1          | 0    | Reset<br>Value | Comments                            |

| C9  | T2MOD       |     |        |           |            |            |            |            | DCEN | 00             | Timer 2<br>mode                     |

| CA  | RCAP2L      |     |        |           |            |            |            |            |      | 00             | Timer 2<br>Reload low               |

| СВ  | RCAP2H      |     |        |           |            |            |            |            |      | 00             | Timer 2<br>Reload High              |

| СС  | TL2         |     |        |           |            |            |            |            |      | 00             | Timer 2 Low<br>byte                 |

| CD  | TH2         |     |        |           |            |            |            |            |      | 00             | Timer 2 High<br>byte                |

| D0  | PSW         | CY  | AC     | FO        | RS1        | RS0        | OV         |            | Р    | 00             | Program<br>Status Word              |

| D1  | S1SETU<br>P |     |        |           |            |            |            |            |      | 00             | DDC I <sup>2</sup> C<br>(S1) Setup  |

| D2  | S2SETUP     |     |        |           |            |            |            |            |      | 00             | I <sup>2</sup> C (S2)<br>Setup      |

| D4  | RAMBUF      |     |        |           |            |            |            |            |      | xx             | DDC Ram<br>Buffer                   |

| D5  | DDCDAT      |     |        |           |            |            |            |            |      | 00             | DDC Data<br>xmit<br>register        |

| D6  | DDCADR      |     |        |           |            |            |            |            |      | 00             | Addr<br>pointer<br>register         |

| D7  | DDCCON      | _   | EX_DAT | SWEN<br>B | DDC_A<br>X | DDCIN<br>T | DDC1E<br>N | SWHIN<br>T | MO   | 00             | DDC<br>Control<br>Register          |

| D8  | S1CON       | CR2 | ENI1   | STA       | STO        | ADDR       | AA         | CR1        | CR0  | 00             | DDC I <sup>2</sup> C<br>Control Reg |

| D9  | S1STA       | GC  | Stop   | Intr      | TX-Md      | Bbusy      | Blost      | ACK_R      | SLV  | 00             | DDC I <sup>2</sup> C<br>Status      |

| DA  | S1DAT       |     |        |           |            |            |            |            |      | 00             | Data Hold<br>Register               |

| DB  | S1ADR       |     |        |           |            |            |            |            |      | 00             | DDC I <sup>2</sup> C address        |

| DC  | S2CON       | CR2 | EN1    | STA       | STO        | ADDR       | AA         | CR1        | CR0  | 00             | I <sup>2</sup> C Bus<br>Control Reg |

| DD  | S2STA       | GC  | Stop   | Intr      | TX-Md      | Bbusy      | Blost      | ACK_R      | SLV  | 00             | I <sup>2</sup> C Bus<br>Status      |

| DE  | S2DAT       |     |        |           |            |            |            |            |      | 00             | Data Hold<br>Register               |

| DF  | S2ADR       |     |        |           |            |            |            |            |      | 00             | I <sup>2</sup> C address            |

| E0  | ACC         |     |        |           |            |            |            |            |      | 00             | Accumulator                         |

Symbol Circuit Function PORT1 <3:0>, PORT3, PORT4<7:3,1:0> Bidirectional I/O port with internal pull-ups Schmitt input CMOS compatible interface PORT2 Bidirectional I/O port with internal PORT1 < 7:4 > I/O pull-ups Schmitt input CMOS compatible interface Analog input option an\_enb Bidirectional I/O port with internal pull-ups I/O PORT4.2 Schmitt input. TTL compatible interface Pull-up when reset Address Latch Enable Program Strobe Enable Bidirectional I/O port Schmitt input

TTL compatible interface USB - , USB + I/O AI06654

Figure 17. Port type and description (Part 2)

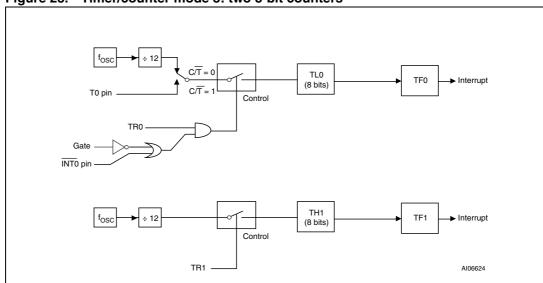

#### 11.1.4 Mode 3

Timer 1 in Mode 3 simply holds its count. The effect is the same as setting TR1 = 0.

Timer 0 in Mode 3 establishes TL0 and TH0 as two separate counters. The logic for Mode 3 on Timer 0 is shown in *Figure 23*. TL0 uses the Timer 0 control Bits: C/T, GATE, TR0, INT0, and TF0. TH0 is locked into a timer function (counting machine cycles) and takes over the use of TR1 and TF1 from Timer 1. Thus, TH0 now controls the "Timer 1" Interrupt.

Mode 3 is provided for applications requiring an extra 8-bit timer on the counter. With Timer 0 in Mode 3, an UPSD325xx devices can look like it has three Timer/Counters. When Timer 0 is in Mode 3, Timer 1 can be turned on and off by switching it out of and into its own Mode 3, or can still be used by the serial port as a baud rate generator, or in fact, in any application not requiring an interrupt.

Figure 23. Timer/counter mode 3: two 8-bit counters

#### 11.2 Timer 2

Like Timers 0 and 1, Timer 2 can operate as either an event timer or as an event counter. This is selected by Bit C/T2 in the special function register T2CON. It has three operating modes: Capture, Auto-reload, and Baud Rate Generator, which are selected by bits in the T2CON as shown in *Table 41*. In the Capture mode there are two options which are selected by Bit EXEN2 in T2CON. if EXEN2 = 0, then Timer 2 is a 16-bit timer or counter which upon overflowing sets Bit TF2, the Timer 2 Overflow bit, which can be used to generate an interrupt. If EXEN2 = 1, then Timer 2 still does the above, but with the added feature that a 1-to-0 transition at external input T2EX causes the current value in the Timer 2 registers, TL2 and TH2, to be captured into registers RCAP2L and RCAP2H, respectively. In addition, the transition at T2EX causes Bit EXF2 in T2CON to be set, and EXF2 like TF2 can generate an interrupt. The Capture mode is illustrated in *Figure 24*.

In the Auto-reload mode, there are again two options, which are selected by bit EXEN2 in T2CON. If EXEN2 = 0, then when Timer 2 rolls over it not only sets TF2 but also causes the Timer 2 registers to be reloaded with the 16-bit value in registers RCAP2L and RCAP2H, which are preset by software. If EXEN2 = 1, then Timer 2 still does the above, but with the added feature that a 1-to-0 transition at external input T2EX will also trigger the 16-bit reload

As data bits shift out to the right, zeros are clocked in from the left. When the MSB of the data byte is at the output position of the shift register, then the '1' that was initially loaded into the 9th position is just to the left of the MSB, and all positions to the left of that contain zeros. This condition flags the TX Control unit to do one last shift and then deactivate SEND and set TI. This occurs at the 10th divide-by-16 rollover after "WRITE to SBUF."

Reception is initiated by a detected 1-to-0 transition at RxD. For this purpose RxD is sampled at a rate of 16 times whatever baud rate has been established. When a transition is detected, the divide-by-16 counter is immediately reset, and 1FFH is written into the input shift register. Resetting the divide-by-16 counter aligns its roll-overs with the boundaries of the incoming bit times.

The 16 states of the counter divide each bit time into 16ths. At the 7th, 8th, and 9th counter states of each bit time, the bit detector samples the value of RxD. The value accepted is the value that was seen in at least 2 of the 3 samples. This is done for noise rejection. If the value accepted during the first bit time is not '0,' the receive circuits are reset and the unit goes back to looking for an-other 1-to-0 transition. This is to provide rejection of false start bits. If the start bit proves valid, it is shifted into the input shift register, and reception of the reset of the frame will proceed.

As data bits come in from the right, '1s' shift out to the left. When the start bit arrives at the left-most position in the shift register (which in Mode 1 is a 9-bit register), it flags the RX Control block to do one last shift, load SBUF and RB8, and set RI. The signal to load SBUF and RB8, and to set RI, will be generated if, and only if, the following conditions are met at the time the final shift pulse is generated:

- 1. R1 = 0, and

- 2. Either SM2 = 0, or the received Stop bit = 1.

If either of these two conditions is not met, the received frame is irretrievably lost. If both conditions are met, the Stop bit goes into RB8, the 8 data bits go into SBUF, and RI is activated. At this time, whether the above conditions are met or not, the unit goes back to looking for a 1-to-0 transition in RxD.

#### 12.2.6 More about Modes 2 and 3

Eleven bits are transmitted (through TxD), or received (through RxD): a Start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a Stop bit (1). On transmit, the 9th data bit (TB8) can be assigned the value of '0' or '1.' On receive, the data bit goes into RB8 in SCON. The baud rate is programmable to either 1/16 or 1/32 the CPU clock frequency in Mode 2. Mode 3 may have a variable baud rate generated from Timer 1.

*Figure 30* and *Figure 32* show a functional diagram of the serial port in Modes 2 and 3. The receive portion is exactly the same as in Mode 1. The transmit portion differs from Mode 1 only in the 9th bit of the transmit shift register.

Transmission is initiated by any instruction that uses SBUF as a destination register. The "WRITE to SBUF" signal also loads TB8 into the 9th bit position of the transmit shift register and flags the TX Control unit that a transmission is requested. Transmission commences at S1P1 of the machine cycle following the next roll-over in the divide-by-16 counter. (Thus, the bit times are synchronized to the divide-by-16 counter, not to the "WRITE to SBUF" signal.)

The transmission begins with activation of SEND, which puts the start bit at TxD. One bit time later, DATA is activated, which enables the output bit of the transmit shift register to TxD. The first shift pulse occurs one bit time after that. The first shift clocks a '1' (the Stop bit) into the 9th bit position of the shift register. There-after, only zeros are clocked in. Thus,

# 16.1.1 DDCDAT register

DDC1 DATA register for transmission (DDCDAT: 0D5h)

- 8-bit READ and WRITE register

- Indicates DATA BYTE to be transmitted in DDC1 protocol

# 16.1.2 DDCADR register

Address pointer for DDC interface (DDCADR: 0D6h)

- 8-bit READ and WRITE register.

- Address pointer with the capability of the post increment. After each access to RAMBUF register (either by software or by hardware DDC1 interface), the content of this register will be increased by one. It's available both in DDC1, DDC2 (DDC2B, DDC2B+, and DDC2AB) and system operation.

Table 60. DDC SFR memory map

| SFR  | Reg        |   | Bit Register Name |           |            |            |        |            |    | Reset | Comments                   |

|------|------------|---|-------------------|-----------|------------|------------|--------|------------|----|-------|----------------------------|

| Addr | Name       | 7 | 6                 | 5         | 4          | 3          | 2      | 1          | 0  | Value | Comments                   |

| D4   | RAMBUF     |   |                   |           |            |            |        |            |    | xx    | DDC Ram<br>Buffer          |

| D5   | DDCDAT     |   |                   |           |            |            |        |            |    | 00    | DDC Data<br>xmit register  |

| D6   | DDCADR     |   |                   |           |            |            |        |            |    | 00    | Addr pointer register      |

| D7   | DDCCO<br>N | l | EX_DAT            | SWEN<br>B | DDC_A<br>X | DDCIN<br>T | DDC1EN | SWHIN<br>T | MO | 00    | DDC<br>Control<br>Register |

Table 61. Description of the DDCON register bits

| Bit | Symbol | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | _      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6   | EX_DAT | 0 = The SRAM has 128 bytes (Default)<br>1 = The SRAM has 256 bytes                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5   | SWENB  | Note: This bit is valid for DDC1 & DDC2b modes  0 = Data is automatically read from SRAM at the current location of DDCADR and sent out via current DDC protocol. (Default)  1 = MCU is interrupted during the current data byte transmission period to load the next byte of data to send out.                                                                                                                                                                    |

| 4   | DDC_AX | Note: This bit is valid for DDC1 & DDC2b modes  0 = Data is automatically read from SRAM at the current location of DDCADR and sent out via current DDC protocol. (Default)  1 = MCU is interrupted during the current data byte transmission period to load the next byte of data to send out.  This bit only affects DDC2b mode Operation:  0 = DDC2b I2C Address is AO/A1 (default)  1 = DDC2b I2C Address is AX. Least 3 significant address bits are ignored. |

- Reset DDC1 enable (by default, DDC1 enable is cleared as LOW after Power-on Reset).

- 2. Set SWENB as high (the default value is zero.)

- 3. Depending on the data size of EDID data, set EX\_DAT as LOW (128 bytes) or HIGH (256 bytes).

- 4. By using bulky moving commands (DDCADR, RAMBUF involved) to move the entire EDID data to RAM buffer.

- 5. Reset SWENB to LOW.

- 6. Reset DDCADR to 00h.

- 7. Set DDC1 enable as HIGH.

In case SWENB is set as high, interrupt service routine is finished within 133 machine cycle in 40MHz System clock.

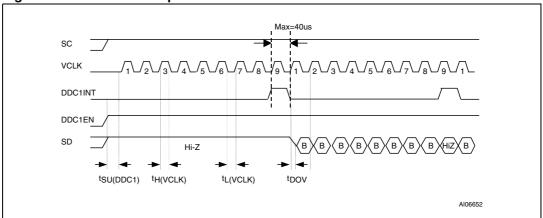

The maximum  $V_{SYNC}$  ( $V_{CLK}$ ) frequency is 25Khz (40 $\mu$ s). And the 9th clock of  $V_{SYNC}$  ( $V_{CLK}$ ) is interrupt period.

So the machine cycle be needed is calculated as below. For example,

- When 40MHz system clock,  $40\mu s = 133 x (25ns x 12)$ ; 133 machine cycle.

- 12MHz system clock, 40µs = 40 x (83.3ns x 12); 40 machine cycle.

- 8MHz system clock, 40μs = 26 x (125ns x 12); 26 machine cycle.

Note:

If EX\_DAT equals to LOW, it is meant the lower part is occupied by DDC1 operation and the upper part is still free to the system. Nevertheless, the effect of the post increment just applies to the part related to DDC1 operation. In other words, the system program is still able to address the locations from 128 to 255 in the RAM buffer through MOVX command but without the facility of the post increment. For example, the case of accessing 200 of the RAM Buffer:

MOV R0, #200, and MOVX A, @R0

Figure 41. Transmission protocol in the DDC1 interface

Table 72. Description of the UCON1 bits

| Bit    | Symbol                   | R/W | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|--------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | TSEQ1                    | R/W | Endpoint 1/ Endpoint 2 Transmit Data Packet PID. (0=DATA0, 1=DATA1) This bit determines which type of data packet (DATA0 or DATA1) will be sent during the next IN transaction directed to Endpoint 1 or Endpoint 2.  Toggling of this bit must be controlled by software. RESET clears this bit.                                                                                                                                                                                                                                                                |

| 6      | EP12SEL                  | R/W | Endpoint 1/ Endpoint 2 Transmit Selection. (0=Endpoint 1, 1=Endpoint 2)  This bit specifies whether the data inside the registers UDT1 are used for Endpoint 1 or Endpoint 2. If all the conditions for a successful Endpoint 2 USB response to a hosts IN token are satisfied (TXD1F=0, TX1E=1, STALL2=0, and EP2E=1) except that the EP12SEL Bit is configured for Endpoint 1, the USB responds with a NAK handshake packet. RESET clears this bit.                                                                                                            |

| 5      | TX1E                     | R/W | Endpoint1 / Endpoint2 Transmit Enable. This bit enables a transmit to occur when the USB Host Controller send an IN token to Endpoint 1 or Endpoint 2. The appropriate endpoint enable bit, EP1E or EP2E Bit in the UCON2 register, should also be set. Software should set the TX1E Bit when data is ready to be transmitted. It must be cleared by software when no more data needs to be transmitted. If this bit is '0' or TXD1F is set, the USB will respond with a NAK handshake to any Endpoint 1 or Endpoint 2 directed IN token. RESET clears this bit. |

| 4      | FRESUM                   | R/W | Force Resume.  This bit forces a resume state ("K" on non-idle state) on the USB data lines to initiate a remote wake-up. Software should control the timing of the forced resume to be between 10ms and 15ms. Setting this bit will not cause the RESUMF Bit to set.                                                                                                                                                                                                                                                                                            |

| 3 to 0 | TP1SIZ3<br>to<br>TP1SIZ0 | R/W | The number of transmit data bytes. These bits are cleared by RESET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# Table 73. USB control register (UCON2: 0ECh)

| 7 | 6 | 5 | 4    | 3    | 2    | 1      | 0      |

|---|---|---|------|------|------|--------|--------|

| _ | _ | _ | SOUT | EP2E | EP1E | STALL2 | STALL1 |

# Table 74. Description of the UCON2 bits

| Bit    | Symbol     | R/W | Function                                                                          |

|--------|------------|-----|-----------------------------------------------------------------------------------|

| 7 to 5 | _          | _   | Reserved                                                                          |

| 4      | 4 SOUT R/W |     | Status out is used to automatically respond to the OUT of a control READ transfer |

| 3      | EP2E       | R/W | Endpoint2 enable. RESET clears this bit                                           |

# 20 PSD module register description and address offset

*Table 84* shows the offset addresses to the PSD module registers relative to the CSIOP base address. The CSIOP space is the 256 bytes of address that is allocated by the user to the internal PSD module registers. *Table 84* provides brief descriptions of the registers in CSIOP space. The following section gives a more detailed description.

Table 84. Register address offset

| Register Name                           | Port A | Port B | Port C | Port D | Other <sup>(1)</sup> | Description                                                                                                   |

|-----------------------------------------|--------|--------|--------|--------|----------------------|---------------------------------------------------------------------------------------------------------------|

| Data In                                 | 00     | 01     | 10     | 11     |                      | Reads Port pin as input, MCU I/O Input mode                                                                   |

| Control                                 | 02     | 03     |        |        |                      | Selects mode between MCU I/O or<br>Address Out                                                                |

| Data Out                                | 04     | 05     | 12     | 13     |                      | Stores data for output to Port pins,<br>MCU I/O Output mode                                                   |

| Direction                               | 06     | 07     | 14     | 15     |                      | Configures Port pin as input or output                                                                        |

| Drive Select                            | 08     | 09     | 16     | 17     |                      | Configures Port pins as either CMOS or Open Drain on some pins, while selecting high slew rate on other pins. |

| Input Macrocell                         | 0A     | 0B     | 18     |        |                      | Reads Input Macrocells                                                                                        |

| Enable Out                              | 0C     | 0D     | 1A     | 1B     |                      | Reads the status of the output enable to the I/O Port driver                                                  |

| Output Macrocells<br>AB                 | 20     | 20     |        |        |                      | READ – reads output of macrocells AB WRITE – loads macrocell flip-flops                                       |

| Output Macrocells<br>BC                 |        | 21     | 21     |        |                      | READ – reads output of macrocells BC<br>WRITE – loads macrocell flip-flops                                    |

| Mask Macrocells<br>AB                   | 22     | 22     |        |        |                      | Blocks writing to the Output Macrocells<br>AB                                                                 |

| Mask Macrocells<br>BC                   |        | 23     | 23     |        |                      | Blocks writing to the Output Macrocells BC                                                                    |

| Primary Flash<br>Protection             |        |        |        |        | C0                   | Read-only – Primary Flash Sector<br>Protection                                                                |

| Secondary Flash<br>memory<br>Protection |        |        |        |        | C2                   | Read-only – PSD module Security and<br>Secondary Flash memory Sector<br>Protection                            |

| PMMR0                                   |        |        |        |        | В0                   | Power Management Register 0                                                                                   |

| PMMR2                                   |        |        |        |        | B4                   | Power Management Register 2                                                                                   |

| Page                                    |        |        |        |        | E0                   | Page Register                                                                                                 |

| VM                                      |        |        |        |        | E2                   | Places PSD module memory areas in Program and/or Data space on an individual basis.                           |

<sup>1.</sup> Other registers that are not part of the I/O ports.

Suspend Sector Erase is accepted only during an Erase cycle and defaults to READ mode. A Suspend Sector Erase instruction executed during an Erase time-out period, in addition to suspending the Erase cycle, terminates the time out period.

The Toggle Flag bit (DQ6) stops toggling when the internal logic is suspended. The status of this bit must be monitored at an address within the Flash memory sector being erased. The Toggle Flag bit (DQ6) stops toggling between 0.1µs and 15µs after the Suspend Sector Erase instruction has been executed. The Flash memory is then automatically set to READ mode.

If an Suspend Sector Erase instruction was executed, the following rules apply:

- Attempting to read from a Flash memory sector that was being erased outputs invalid data.

- Reading from a Flash sector that was not being erased is valid.

- The Flash memory *cannot* be programmed, and only responds to Resume Sector Erase and Reset Flash instructions (READ is an operation and is allowed).

- If a Reset Flash instruction is received, data in the Flash memory sector that was being erased is invalid.

#### 22.7.4 Resume Sector Erase

If a Suspend Sector Erase instruction was previously executed, the erase cycle may be resumed with this instruction. The Resume Sector Erase instruction consists of writing 030h to any address while an appropriate Sector Select (FS0-FS7 or CSBOOT0-CSBOOT3) is High. (See *Table 85*.)

# 22.8 Specific features

#### 22.8.1 Flash memory sector protect

Each primary and secondary Flash memory sector can be separately protected against Program and Erase cycles. Sector Protection provides additional data security because it disables all Program or Erase cycles. This mode can be activated through the JTAG Port or a Device Programmer.

Sector protection can be selected for each sector using the PSDsoft Express Configuration program. This automatically protects selected sectors when the device is programmed through the JTAG Port or a Device Programmer. Flash memory sectors can be unprotected to allow updating of their contents using the JTAG Port or a Device Programmer. The MCU can read (but cannot change) the sector protection bits.

Any attempt to program or erase a protected Flash memory sector is ignored by the device. The Verify operation results in a READ of the protected data. This allows a guarantee of the retention of the Protection status.

The sector protection status can be read by the MCU through the Flash memory protection registers (in the CSIOP block). See *Table 87* and *Table 88*.

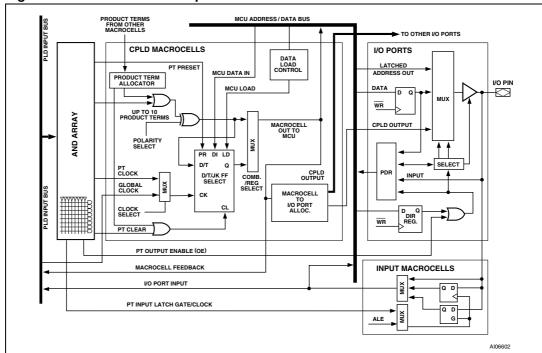

The Input Macrocells (IMC) and Output Macrocells (OMC) are connected to the PSD module internal data bus and can be directly accessed by the MCU. This enables the MCU software to load data into the Output Macrocells (OMC) or read data from both the Input and Output Macrocells (IMC and OMC).

This feature allows efficient implementation of system logic and eliminates the need to connect the data bus to the AND Array as required in most standard PLD macrocell architectures.

Figure 58. Macrocell and I/O ports

# 23.4 Output macrocell (OMC)

Eight of the Output Macrocells (OMC) are connected to Ports A and B pins and are named as McellAB0-McellAB7. The other eight macrocells are connected to Ports B and C pins and are named as McellBC0-McellBC7. If an McellAB output is not assigned to a specific pin in PSDsoft, the Macrocell Allocator block assigns it to either Port A or B. The same is true for a McellBC output on Port B or C. *Table 92* shows the macrocells and port assignment.

The Output Macrocell (OMC) architecture is shown in *Figure 59*. As shown in the figure, there are native product terms available from the AND Array, and borrowed product terms available (if unused) from other Output Macrocells (OMC). The polarity of the product term is controlled by the XOR gate. The Output Macrocell (OMC) can implement either sequential logic, using the flip-flop element, or combinatorial logic. The multiplexer selects between the sequential or combinatorial logic outputs. The multiplexer output can drive a port pin and has a feedback path to the AND Array inputs.

The flip-flop in the Output Macrocell (OMC) block can be configured as a D, T, JK, or SR type in PSDsoft. The flip-flop's clock, preset, and clear inputs may be driven from a product term of the AND Array. Alternatively, CLKIN (PD1) can be used for the clock input to the flip-

flop. The flip-flop is clocked on the rising edge of CLKIN (PD1). The preset and clear are active High inputs. Each clear input can use up to two product terms.

Table 92. Output macrocell port and data bit assignments

| Output    | Port<br>Assignment | Native Product | Max. Borrowed | Data Bit for       |

|-----------|--------------------|----------------|---------------|--------------------|

| Macrocell | (1,2)              | Terms          | Product Terms | Loading or Reading |

| McellAB0  | Port A0, B0        | 3              | 6             | D0                 |

| McellAB1  | Port A1, B1        | 3              | 6             | D1                 |

| McellAB2  | Port A2, B2        | 3              | 6             | D2                 |

| McellAB3  | Port A3, B3        | 3              | 6             | D3                 |

| McellAB4  | Port A4, B4        | 3              | 6             | D4                 |

| McellAB5  | Port A5, B5        | 3              | 6             | D5                 |

| McellAB6  | Port A6, B6        | 3              | 6             | D6                 |

| McellAB7  | Port A7, B7        | 3              | 6             | D7                 |

| McellBC0  | Port B0            | 4              | 5             | D0                 |

| McellBC1  | Port B1            | 4              | 5             | D1                 |

| McellBC2  | Port B2, C2        | 4              | 5             | D2                 |

| McellBC3  | Port B3, C3        | 4              | 5             | D3                 |

| McellBC4  | Port B4, C4        | 4              | 6             | D4                 |

| McellBC5  | Port B5            | 4              | 6             | D5                 |

| McellBC6  | Port B6            | 4              | 6             | D6                 |

| McellBC7  | Port B7, C7        | 4              | 6             | D7                 |

<sup>1.</sup> McellAB0-McellAB7 can only be assigned to Port B in the 52-pin package

#### 23.5 Product term allocator

The CPLD has a Product Term Allocator. PSDsoft uses the Product Term Allocator to borrow and place product terms from one macrocell to another. The following list summarizes how product terms are allocated:

- McellAB0-McellAB7 all have three native product terms and may borrow up to six more

- McellBC0-McellBC3 all have four native product terms and may borrow up to five more

- McellBC4-McellBC7 all have four native product terms and may borrow up to six more.

Each macrocell may only borrow product terms from certain other macrocells. Product terms already in use by one macrocell are not available for another macrocell.

If an equation requires more product terms than are available to it, then "external" product terms are required, which consume other Output Macrocells (OMC). If external product terms are used, extra delay is added for the equation that required the extra product terms.

This is called product term expansion. PSDsoft Express performs this expansion as needed.

<sup>2.</sup> Port PC0, PC1, PC5, and PC6 are assigned to JTAG pins and are not available as Macrocell outputs.

# 24.8 Port configuration registers (PCR)

Each Port has a set of Port Configuration Registers (PCR) used for configuration. The contents of the registers can be accessed by the MCU through normal READ/WRITE bus cycles at the addresses given in *Table 84*. The addresses in *Table 84* are the offsets in hexadecimal from the base of the CSIOP register.

The pins of a port are individually configurable and each bit in the register controls its respective pin. For example, Bit 0 in a register refers to Bit 0 of its port. The three Port Configuration Registers (PCR), shown in *Table 96*, are used for setting the Port configurations. The default Power-up state for each register in *Table 96* is 00h.

#### 24.8.1 Control register

Any bit reset to '0' in the Control Register sets the corresponding port pin to MCU I/O mode, and a '1' sets it to Address Out mode. The default mode is MCU I/O. Only Ports A and B have an associated Control Register.

#### 24.8.2 Direction register

The Direction Register, in conjunction with the output enable (except for Port D), controls the direction of data flow in the I/O Ports. Any bit set to '1' in the Direction Register causes the corresponding pin to be an output, and any bit set to '0' causes it to be an input. The default mode for all port pins is input.

Figure 63 and Figure 64 show the Port Architecture diagrams for Ports A/B and C, respectively. The direction of data flow for Ports A, B, and C are controlled not only by the direction register, but also by the output enable product term from the PLD AND Array. If the output enable product term is not active, the Direction Register has sole control of a given pin's direction.

An example of a configuration for a Port with the three least significant bits set to output and the remainder set to input is shown in *Table 99*. Since Port D only contains two pins (shown in *Figure 66*), the Direction Register for Port D has only two bits active.

#### 24.8.3 Drive Select register

The Drive Select Register configures the pin driver as Open Drain or CMOS for some port pins, and controls the slew rate for the other port pins. An external pull-up resistor should be used for pins configured as Open Drain.

A pin can be configured as Open Drain if its corresponding bit in the Drive Select Register is set to a '1.' The default pin drive is CMOS.

Note:

The slew rate is a measurement of the rise and fall times of an output. A higher slew rate means a faster output response and may create more electrical noise. A pin operates in a high slew rate when the corresponding bit in the Drive Register is set to '1.' The default rate is slow slew.

*Table 100* shows the Drive Register for Ports A, B, C, and D. It summarizes which pins can be configured as Open Drain outputs and which pins the slew rate can be set for.

Table 106. Status during Power-on RESET, Warm RESET and Power-down mode

| Port Configuration | Power-On RESET                                         | Warm RESET | Power-down mode                                                   |

|--------------------|--------------------------------------------------------|------------|-------------------------------------------------------------------|

| MCU I/O            | Input mode                                             | Input mode | Unchanged                                                         |

| PLD Output         | Valid after internal PSD configuration bits are loaded | Valid      | Depends on inputs to<br>PLD (addresses are<br>blocked in PD mode) |

| Address Out        | Tri-stated                                             | Tri-stated | Not defined                                                       |

| Peripheral I/O     | Tri-stated                                             | Tri-stated | Tri-stated                                                        |

| Register                    | Power-On RESET                                                    | Warm RESET                                                        | Power-down mode                  |

|-----------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------|

| PMMR0 and PMMR2             | Cleared to '0'                                                    | Unchanged                                                         | Unchanged                        |

| Macrocells flip-flop status | Cleared to '0' by internal Power-on RESET                         | Depends on .re and .pr equations                                  | Depends on .re and .pr equations |

| VM Register <sup>(1)</sup>  | Initialized, based on the selection in PSDsoft Configuration menu | Initialized, based on the selection in PSDsoft Configuration menu | Unchanged                        |

| All other registers         | Cleared to '0'                                                    | Cleared to '0'                                                    | Unchanged                        |

<sup>1.</sup> The SR\_cod and Periphmode Bits in the VM Register are always cleared to '0' on Power-on RESET or Warm RESET.

scan the status out serially using the standard JTAG channel. See Application Note *AN1153*.

TERR indicates if an error has occurred when erasing a sector or programming a byte in Flash memory. This signal goes Low (active) when an Error condition occurs, and stays Low until an "ISC\_CLEAR" command is executed or a chip Reset (RESET) pulse is received after an "ISC\_DISABLE" command.

TSTAT behaves the same as Ready/Busy described in Section 22.2.1: Ready/Busy (PC3). TSTAT is High when the PSD module device is in READ mode (primary and secondary Flash memory contents can be read). TSTAT is Low when Flash memory Program or Erase cycles are in progress, and also when data is being written to the secondary Flash memory.

TSTAT and TERR can be configured as open-drain type signals during an "ISC\_ENABLE" command.

# 27.3 Security and Flash memory protection

When the Security Bit is set, the device cannot be read on a Device Programmer or through the JTAG Port. When using the JTAG Port, only a Full Chip Erase command is allowed.

All other Program, Erase and Verify commands are blocked. Full Chip Erase returns the part to a non-secured blank state. The Security Bit can be set in PSDsoft Express Configuration.

All primary and secondary Flash memory sectors can individually be sector protected against erasures. The sector protect bits can be set in PSDsoft Express Configuration.

# 32 DC and AC parameters

This section summarizes the operating and measurement conditions, and the DC and AC characteristics of the device. The parameters in the DC and AC Characteristic tables that follow are derived from tests performed under the Measurement Conditions summarized in the relevant tables. Designers should check that the operating conditions in their circuit match the measurement conditions when relying on the quoted parameters.

Table 113. Operating conditions (5 V devices)

| Symbol          | Parameter                                  | Min. | Max. | Unit |

|-----------------|--------------------------------------------|------|------|------|

| V <sub>CC</sub> | Supply voltage                             | 4.5  | 5.5  | V    |

| T <sub>A</sub>  | Ambient operating temperature (industrial) | -40  | 85   | °C   |

|                 | Ambient operating temperature (commercial) | 0    | 70   | °C   |

Table 114. Operating conditions (3 V devices)

| Symbol          | Parameter                                  | Min. | Max. | Unit |

|-----------------|--------------------------------------------|------|------|------|

| V <sub>CC</sub> | Supply voltage                             | 3.0  | 3.6  | V    |

| т               | Ambient operating temperature (industrial) | -40  | 85   | °C   |

| IA              | Ambient operating temperature (commercial) | 0    | 70   | °C   |

Table 115. AC signal letters for timing

| А | Address               |  |  |  |

|---|-----------------------|--|--|--|

| С | Clock                 |  |  |  |

| D | Input Data            |  |  |  |

| I | Instruction           |  |  |  |

| L | ALE                   |  |  |  |

| N | RESET Input or Output |  |  |  |

| Р | PSEN signal           |  |  |  |

| Q | Output Data           |  |  |  |

| R | RD signal             |  |  |  |

| W | WR signal             |  |  |  |

| М | Output Macrocell      |  |  |  |

|   |                       |  |  |  |

<sup>1.</sup> Example: t<sub>AVLX</sub> = Time from Address Valid to ALE Invalid.

Table 116. AC signal behavior symbols for timing

| t  | Time                          |

|----|-------------------------------|

| L  | Logic Level Low or ALE        |

| Н  | Logic Level High              |

| V  | Valid                         |

| Х  | No Longer a Valid Logic Level |

| Z  | Float                         |

| PW | Pulse Width                   |

<sup>1.</sup> Example:  $t_{AVLX}$  = Time from Address Valid to ALE Invalid.

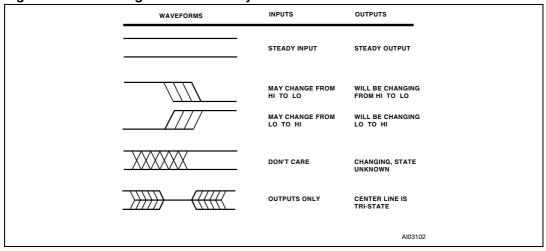

Figure 72. Switching waveforms - key

Table 117. Major parameters

| Parameters/conditions/<br>comments                                                                                                   | 5 V test<br>conditions                                              | 5.0 V value      | 3.3 V test conditions                                              | 3.3 V<br>value   | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------|--------------------------------------------------------------------|------------------|------|

| Operating voltage                                                                                                                    | -                                                                   | 4.5 to 5.5       | -                                                                  | 3.0 to 3.6       | V    |

| Operating temperature                                                                                                                | _                                                                   | -40 to 85        | _                                                                  | -40 to 85        | °C   |

| MCU frequency<br>12 MHz (min) for USB;<br>8 MHz (min) for I <sup>2</sup> C                                                           | _                                                                   | 1 Min, 40<br>Max | -                                                                  | 1 Min, 24<br>Max | MHz  |

| Active current, typical<br>(25°C operation; 80% Flash<br>and 15% SRAM accesses,<br>45 PLD product terms used;<br>PLD Turbo mode Off) | 24 MHz MCU<br>clock, 12 MHz<br>PLD input<br>frequency, 4 MHz<br>ALE | 72               | 12 MHz MCU<br>clock, 6 MHz<br>PLD input<br>frequency,<br>2 MHz ALE | 21               | mA   |

| Idle current, typical (CPU halted but some peripherals active; 25°C operation; 45 PLD product terms used; PLD Turbo mode Off)        | 24 MHz MCU<br>clock, 12 MHz<br>PLD input<br>frequency               | 25               | 12 MHz MCU<br>clock, 1 MHz<br>PLD input<br>frequency               | 7                | mA   |

Table 118. DC characteristics (5 V devices)

| Symbol           | Parameter                                                               | Test conditions (in addition to those in <i>Table 113</i> ) | Min.                  | Тур. | Max.                  | Unit |

|------------------|-------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------|------|-----------------------|------|

| V <sub>IH</sub>  | Input high voltage (Ports 1, 2, 3, 4[Bits 7,6,5,4,3,1,0], XTAL1, RESET) | 4.5 V < V <sub>CC</sub> < 5.5 V                             | 0.7 V <sub>CC</sub>   |      | V <sub>CC</sub> + 0.5 | V    |

| V <sub>IH1</sub> | Input high voltage (Ports A, B, C, D, 4[Bit 2], USB+, USB-)             | 4.5 V < V <sub>CC</sub> < 5.5 V                             | 2.0                   |      | V <sub>CC</sub> + 0.5 | V    |

| V <sub>IL</sub>  | Input low voltage (Ports 1, 2, 3, 4[Bits 7,6,5,4,3,1,0], XTAL1, RESET)  | 4.5 V < V <sub>CC</sub> < 5.5 V                             | V <sub>SS</sub> - 0.5 |      | 0.3 V <sub>C</sub>    | V    |

| V <sub>IL1</sub> | Input low voltage<br>(Ports A, B, C, D, 4[Bit 2])                       | 4.5 V < V <sub>CC</sub> < 5.5 V                             | -0.5                  |      | 0.8                   | V    |

| VIL1             | Input low voltage<br>(USB+, USB-)                                       | 4.5 V < V <sub>CC</sub> < 5.5 V                             | V <sub>SS</sub> - 0.5 |      | 0.8                   | V    |

| V <sub>OL</sub>  | Output low voltage<br>(Ports A,B,C,D)                                   | I <sub>OL</sub> = 20 μA<br>V <sub>CC</sub> = 4.5 V          |                       | 0.01 | 0.1                   | V    |

| VOL              |                                                                         | $I_{OL} = 8 \text{ mA}$ $V_{CC} = 4.5 \text{ V}$            |                       | 0.25 | 0.45                  | V    |

| V <sub>OL1</sub> | Output low voltage (Ports 1,2,3,4, WR, RD)                              | I <sub>OL</sub> = 1.6 mA                                    |                       |      | 0.45                  | V    |

| V <sub>OL2</sub> | Output low voltage<br>(Port 0, ALE, PSEN)                               | I <sub>OL</sub> = 3.2 mA                                    |                       |      | 0.45                  | V    |

| V                | Output high voltage<br>(Ports A,B,C,D)                                  | $I_{OH} = -20 \mu A$<br>$V_{CC} = 4.5 V$                    | 4.4                   | 4.49 |                       | V    |

| V <sub>OH</sub>  |                                                                         | $I_{OH} = -2 \text{ mA}$ $V_{CC} = 4.5 \text{ V}$           | 2.4                   | 3.9  |                       | V    |

| W                | Output high voltage (Port 0 in ext. Bus mode, ALE,                      | I <sub>OH</sub> = -800 μA                                   | 2.4                   |      |                       | V    |

| V <sub>OH2</sub> | PSEN)                                                                   | I <sub>OH</sub> = -80 μA                                    | 4.05                  |      |                       | V    |

| V <sub>LVR</sub> | Low Voltage RESET                                                       | 0.1 V hysteresis                                            | 3.75                  | 4.0  | 4.25                  | V    |

| V <sub>OP</sub>  | XTAL open bias voltage (XTAL1, XTAL2)                                   | I <sub>OL</sub> = 3.2 mA                                    | 2.0                   |      | 3.0                   | V    |

| V <sub>LKO</sub> | V <sub>CC</sub> (min) for Flash Erase<br>and Program                    |                                                             | 2.5                   |      | 4.2                   | V    |

| I <sub>IL</sub>  | Logic '0' input current (Ports 1,2,3,4)                                 | V <sub>IN</sub> = 0.45 V<br>(0 V for Port 4[pin 2])         | -10                   |      | -50                   | μΑ   |

| I <sub>TL</sub>  | Logic 1-to-0 transition current (Ports 1,2,3,4)                         | V <sub>IN</sub> = 3.5 V<br>(2.5 V for Port 4[pin 2])        | -65                   |      | -650                  | μΑ   |

| I <sub>RST</sub> | Reset pin pull-up current (RESET)                                       | V <sub>IN</sub> = V <sub>SS</sub>                           | -10                   |      | <b>–</b> 55           | μΑ   |

Table 124. External data memory AC characteristics (with the 5 V MCU module)

| Symbol             | Parameter <sup>(1)</sup>    | 40 MHz oscillator |      | Variable oscillator<br>1/t <sub>CLCL</sub> = 24 to 40 MHz |                          | Unit |

|--------------------|-----------------------------|-------------------|------|-----------------------------------------------------------|--------------------------|------|

|                    |                             | Min.              | Max. | Min.                                                      | Max.                     |      |

| t <sub>RLRH</sub>  | RD pulse width              | 120               |      | 6 t <sub>CLCL</sub> – 30                                  |                          | ns   |

| t <sub>WLWH</sub>  | WR pulse width              | 120               |      | 6 t <sub>CLCL</sub> – 30                                  |                          | ns   |

| t <sub>LLAX2</sub> | Address hold after ALE      | 10                |      | t <sub>CLCL</sub> – 15                                    |                          | ns   |

| t <sub>RHDX</sub>  | RD to valid data in         |                   | 75   |                                                           | 5 t <sub>CLCL</sub> – 50 | ns   |

| t <sub>RHDX</sub>  | Data hold after RD          | 0                 |      | 0                                                         |                          | ns   |

| t <sub>RHDZ</sub>  | Data float after RD         |                   | 38   |                                                           | 2 t <sub>CLCL</sub> – 12 | ns   |

| t <sub>LLDV</sub>  | ALE to valid data in        |                   | 150  |                                                           | 8 t <sub>CLCL</sub> - 50 | ns   |

| t <sub>AVDV</sub>  | Address to valid data in    |                   | 150  |                                                           | 9 t <sub>CLCL</sub> – 75 | ns   |

| t <sub>LLWL</sub>  | ALE to WR or RD             | 60                | 90   | 3 t <sub>CLCL</sub> – 15                                  | t <sub>CLCL</sub> + 15   | ns   |

| t <sub>AVWL</sub>  | Address valid to WR or RD   | 70                |      | 4 t <sub>CLCL</sub> – 30                                  |                          | ns   |

| t <sub>WHLH</sub>  | WR or RD High to ALE High   | 10                | 40   | t <sub>CLCL</sub> – 15                                    | t <sub>CLCL</sub> + 15   | ns   |

| t <sub>QVWX</sub>  | Data valid to WR transition | 5                 |      | t <sub>CLCL</sub> – 20                                    |                          | ns   |

| t <sub>QVWH</sub>  | Data set-up before WR       | 125               |      | 7 t <sub>CLCL</sub> – 50                                  |                          | ns   |

| t <sub>WHQX</sub>  | Data hold after WR          | 5                 |      | t <sub>CLCL</sub> – 20                                    |                          | ns   |

| t <sub>RLAZ</sub>  | Address float after RD      |                   | 0    |                                                           | 0                        | ns   |

<sup>1.</sup> Conditions (in addition to those in *Table 113*,  $V_{CC}$  = 4.5 to 5.5 V):  $V_{SS}$  = 0 V;  $C_L$  for Port 0, ALE and PSEN output is 100 pF;  $C_L$  for other outputs is 80 pF