#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HC11                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 4MHz                                                                    |

| Connectivity               | SCI, SPI                                                                |

| Peripherals                | POR, PWM, WDT                                                           |

| Number of I/O              | 37                                                                      |

| Program Memory Size        | -                                                                       |

| Program Memory Type        | ROMIess                                                                 |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 768 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                             |

| Data Converters            | A/D 8x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 84-LCC (J-Lead)                                                         |

| Supplier Device Package    | 84-PLCC (29.29x29.29)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc11k0cfne4 |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC68HC11K Family Technical Data

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Motorola and (A) are registered trademarks of Motorola, Inc. DigitalDNA is a trademark of Motorola, Inc.

© Motorola, Inc., 2001

M68HC11K Family

**Technical Data**

MOTOROLA

Semiconductor, Inc.

Freescale

# Freescale Semiconductor, Inc.

List of Figures

| Figur | e Title                                          | Page |

|-------|--------------------------------------------------|------|

| 4-13  | System Configuration Register (CONFIG)           | 101  |

| 4-14  | System Configuration Register (CONFIG)           | 102  |

| 4-15  | System Configuration Options 2 Register (OPT2)   | 103  |

| 5-1   | System Configuration Register (CONFIG)           |      |

| 5-2   | System Configuration Options Register (OPTION)   |      |

| 5-3   | Arm/Reset COP Timer Circuitry Register (COPRST)  |      |

| 5-4   | System Configuration Options Register (OPTION)   |      |

| 5-5   | System Configuration Options Register 2 (OPT2)   |      |

| 5-6   | System Configuration Options Register (OPTION)   | 121  |

| 5-7   | Highest Priority I-Bit Interrupt                 |      |

|       | and Miscellaneous Register (HPRIO)               |      |

| 5-8   | Processing Flow Out of Reset                     |      |

| 5-9   | Interrupt Priority Resolution                    |      |

| 5-10  | Interrupt Priority Resolution Within SCI System  |      |

| 5-11  | System Configuration Options Register (OPTION)   |      |

| 5-12  | System Configuration Options 3 Register (OPT3)   |      |

| 5-13  | Slow Mode Example for M68HC(7)11KS Devices Only. | 133  |

| 6-1   | Port A Data Register (PORTA)                     | 138  |

| 6-2   | Port A Data Direction Register (DDRA)            | 138  |

| 6-3   | Port B Data Register (PORTB)                     |      |

| 6-4   | Port B Data Direction Register (DDRB)            |      |

| 6-5   | Port C Data Register (PORTC).                    |      |

| 6-6   | Port C Data Direction Register (DDRC)            |      |

| 6-7   | System Configuration Options 2 Register (OPT2)   |      |

| 6-8   | Port D Data Register (PORTD).                    |      |

| 6-9   | Port D Data Direction Register (DDRD)            |      |

| 6-10  | Port E Data Register (PORTE)                     |      |

| 6-11  | Port F Data Register (PORTF)                     |      |

| 6-12  | Port F Data Direction Register (DDRF)            |      |

| 6-13  | Port G Data Register (PORTG)                     |      |

| 6-14  | Port G Data Direction Register (DDRG)            |      |

| 6-15  | Port H Data Register (PORTH).                    |      |

| 6-16  | Port H Data Direction Register (DDRH)            | 146  |

| Technical | Data |

|-----------|------|

18

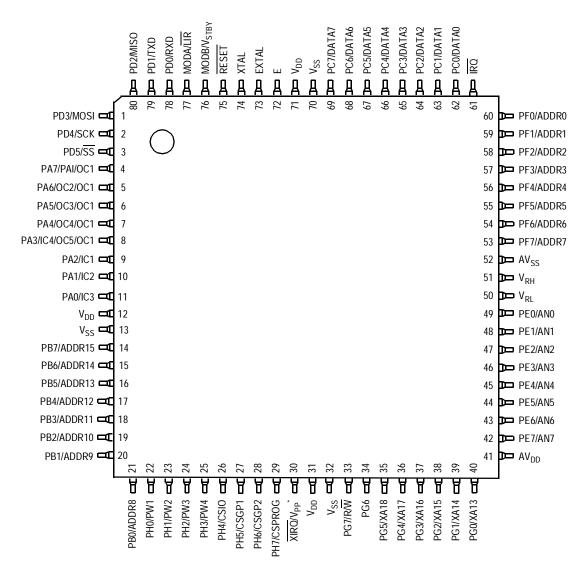

Pin Description Introduction

\* V<sub>PP</sub> applies only to EPROM devices.

M68HC11K Family

Operating Modes and On-Chip Memory EEPROM and the CONFIG Register

#### 4.8.2.2 EEPROM Bulk Erase

BULKE

ROWE

| LDAB | #\$06  |                                      |

|------|--------|--------------------------------------|

| STAB | \$003B | Set EELAT and ERASE.                 |

| STAA | \$0,X  | Store any data to any EEPROM address |

| LDAB | #\$07  |                                      |

| STAB | \$002B | Set EEPGM bit as well                |

|      |        | to enable EEPROM programming voltage |

| JSR  | DLY10  | Delay 10 ms                          |

| CLR  | \$003B | Turn off programming voltage and set |

|      |        | to READ mode                         |

#### 4.8.2.3 EEPROM Row Erase

| LDAB | #\$07  |                                      |

|------|--------|--------------------------------------|

| STAB | \$003B | Set EELAT, ERASE and ROW.            |

| STAA | \$0,X  | Store any data to any EEPROM address |

|      |        | in row                               |

| LDAB | #\$07  |                                      |

| STAB | \$002B | Set EEPGM bit as well                |

|      |        | to enable EEPROM programming voltage |

| JSR  | DLY10  | Delay 10 ms                          |

| CLR  | \$003B | Turn off programming voltage and set |

|      |        | to READ mode                         |

#### 4.8.2.4 EEPROM Byte Erase

| BYTEE | LDAB<br>STAB<br>STAA | #\$16<br>\$003B<br>\$0,X | Set EELAT, ERASE and BYTE.<br>Store any data to targeted EEPROM<br>address |

|-------|----------------------|--------------------------|----------------------------------------------------------------------------|

|       | LDAB                 | #\$17                    |                                                                            |

|       | STAB                 | \$002B                   | Set EEPGM bit as well<br>to enable EEPROM programming voltage              |

|       | JSR                  | DLY10                    | Delay 10 ms                                                                |

|       | CLR                  | \$003B                   | Turn off programming voltage and set<br>to READ mode                       |

**Resets and Interrupts**

- All nine timer interrupts are disabled because their mask bits have been cleared.

- The I4/O5 bit in the PACTL register is cleared to configure the I4/O5 function as OC5; however, the OM5:OL5 control bits in the TCTL1 register are clear so OC5 does not control the PA3 pin.

- Real-time interrupt (RTI)

- The RTI enable bit in TMSK2 is cleared, masking automatic hardware interrupts.

- The rate control bits are cleared after reset and can be initialized by software before the RTI system is enabled.

- Pulse accumulator

- The pulse accumulator system is disabled at reset.

- The PAI input pin defaults to a general-purpose input pin (PA7).

- Computer operating properly (COP) watchdog system

- The COP watchdog system is enabled if the NOCOP control bit in the CONFIG register is clear and disabled if NOCOP is set.

- The OPTION register's CR[1:0] bits are cleared, setting the COP rate for the shortest duration timeout.

- Serial communications interface (SCI)

- At reset, the SCI baud rate control register (7.9.1 SCI Baud Rate Control Register) is initialized to \$0004.

- All transmit and receive interrupts are masked and both the transmitter and receiver are disabled so the port pins default to being general-purpose I/O lines.

- The SCI frame format is initialized to an 8-bit character size.

- The send break and receiver wake-up functions are disabled.

- The TDRE and TC status bits in the SCI status register are both set, indicating that there is no transmit data in either the transmit data register or the transmit serial shift register.

**Technical Data**

MOTOROLA

Semiconductor, Inc

eescale

**Resets and Interrupts**

Technical Data

M68HC11K Family

MOTOROLA

Serial Peripheral Interface (SPI)

extra hardware. The SPI system can send data at up to one half of the E-clock rate when configured as master and the full E-clock rate when configured as a slave.

# 8.3 SPI Functional Description

The SPI is a 4-wire, full-duplex communication system. Characters are eight bits, transmitted most significant bit (MSB) first. One master device exchanges data with one or more slave devices. Each device selects its mode by writing either a 1 (master) or 0 (slave) to the MSTR bit in the serial peripheral control register (SPCR). As a master device transmits data to a slave device via the MOSI (master out slave in) line, the slave transmits data to the master via the MISO (master in slave out) line. The master produces a common synchronization clock signal and drives it on its SCK (serial clock) pin, which is configured as an output. The slave SCK pin is configured as an input to receive the clock. An external logic low signal is applied to the slave select pin ( $\overline{SS}$ ) of each slave device for which a particular message is intended. Devices not selected ( $\overline{SS}$  high) ignore the transmission.

Received characters are double-buffered. Serial input bits are fed into a shift register; when the last bit is received, the completed character is parallel-loaded to a read data buffer. This allows the next message to be received while the current message is being read. As long as the buffer is read before the next received character is ready to be transferred to the buffer, no overrun condition occurs.

Transmitted characters are not double-buffered, they are written directly to the output shift register. This means that new data for transmission cannot be written to the shift register until the previous transmission is complete. An attempt to write during data transmission will not go through; the transmission in progress will proceed undisturbed, and the MCU will set the write collision (WCOL) status bit in the serial peripheral status register (SPSR). After the last bit of a character is shifted out, the SPI transfer complete flag (SPIF) of the SPSR is set. This will also generate an interrupt if the SPIE (SPI interrupt enable) bit in the SPCR is set.

Technical Data

Semiconductor, Inc

eescale

Serial Peripheral Interface (SPI) SPI Signal Descriptions

# 8.4.4 Slave Select (SS)

The slave select  $(\overline{SS})$  input is used to target specific devices in the SPI system. It must be pulled low on a targeted slave device prior to any communication with a master and must remain low for the duration of the transaction.  $\overline{SS}$  must always be high on any device in master mode. Pulling  $\overline{SS}$  low on a master mode device generates a mode fault error (see 8.5.1 Mode Fault Error).

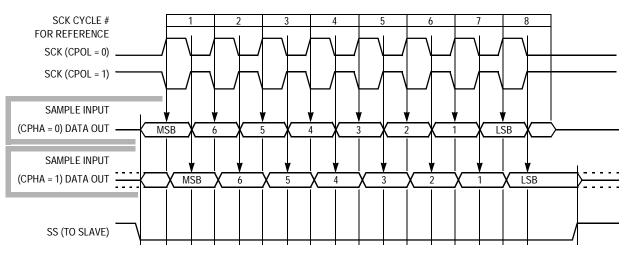

## 8.4.5 SPI Timing

Four possible timing relationships are available through control bits CPOL (clock polarity) and CPHA (clock phase) in the SPCR. These bits must be the same in both master and slave devices. The master device always places data on the MOSI line approximately a half-cycle before the SCK clock edge. This enables the slave device to latch the data. See Figure 8-2.

A write collision is normally a slave error because a slave has no control over when a master initiates a transfer. A master knows when a transfer is in progress, so there is no reason for a master to generate a write-collision error, although the SPI logic can detect write collisions in both master and slave devices.

Figure 8-2. Data Clock Timing Diagram

M68HC11K Family

MOTOROLA

Timing System Output Compare (OC)

After a match occurs, change the appropriate OC1D bit to the opposite polarity, then add a value representing the width of the pulse to the original value and write it to the output compare register.

Because the pin state changes occur at specific values of the free-running counter, the pulse width can be controlled accurately to the resolution of the free-running counter, independent of software latencies. To generate an output signal of a specific frequency and duty cycle, repeat this pulse-generating procedure.

#### 9.6.1 Timer Output Compare Registers

|                 | Bit 7                                                      | 6          | 5      | 4      | 3      | 2      | 1     | Bit 0 |  |

|-----------------|------------------------------------------------------------|------------|--------|--------|--------|--------|-------|-------|--|

| Address:        | Address: \$0016 — TOC1 (High)                              |            |        |        |        |        |       |       |  |

| Read:<br>Write: | Bit 15                                                     | Bit 14     | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |  |

| Reset:          | 1                                                          | 1          | 1      | 1      | 1      | 1      | 1     | 1     |  |

| Address:        | \$0017 — T                                                 | OC1 (Low)  |        |        |        |        |       |       |  |

| Read:<br>Write: | Bit 7                                                      | Bit 6      | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |  |

| Reset:          | 1                                                          | 1          | 1      | 1      | 1      | 1      | 1     | 1     |  |

| Address:        | \$0018 — T                                                 | OC2 (High) |        |        |        |        |       |       |  |

| Read:<br>Write: | Bit 15                                                     | Bit 14     | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |  |

| Reset:          | 1                                                          | 1          | 1      | 1      | 1      | 1      | 1     | 1     |  |

| Address:        | \$0019 — T                                                 | OC2 (Low)  |        |        |        |        |       |       |  |

| Read:<br>Write: | Bit 7                                                      | Bit 6      | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |  |

| Reset:          | 1                                                          | 1          | 1      | 1      | 1      | 1      | 1     | 1     |  |

|                 | Figure 9-13. Timer Output Compare<br>Registers (TOC1–TOC4) |            |        |        |        |        |       |       |  |

Timing System Pulse-Width Modulator (PWM)

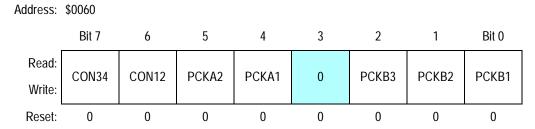

The three clocks are derived from the E clock by writing to registers which determine their scaling factors. The clock A frequency is equal to E divided by 1, 2, 4, or 8, depending on which bits (PCKA[2:1]) in the PWCLK register are set. The clock B frequency is equal to the E clock divided by a power of two determined by bits PCKB[3:1] in the PWCLK register. Clock S is derived by dividing clock A by the integer (1 to 256) stored in the PWSCAL register, then by two.

Two channels can be concatenated by setting the appropriate bit (CON34 or CON12) in the PWCLK register. In this mode, the clock source is determined by the low-order channel, which is channel two in CON12 and channel four in CON34. The output is also placed on the pin associated with the low-order channels, so when two channels are concatenated the pin associated with the high-order channel (PH0 and/or PH2) can be used for GPIO. A read of the high-order byte causes the low-order byte to be latched for one cycle to guarantee that double-byte reads are accurate. A write to the low-order byte of the counter causes reset of the entire counter. A write to the high-order byte

#### 9.9.2 Pulse-Width Modulation Control Registers

The PWM control registers are described here.

9.9.2.1 Pulse-Width Modulation Timer Clock Select Register

Figure 9-31. Pulse-Width Modulation Timer Clock Select (PWCLK)

M68HC11K Family

Timing System

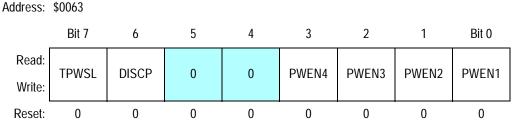

#### 9.9.2.4 Pulse-Width Modulation Timer Enable Register

Figure 9-34. Pulse-Width Modulation Timer Enable Register (PWEN)

TPWSL — PWM Scaled Clock Test Bit — factory use only; only accessible in special test mode

- 0 = Normal operation

- 1 = Clock S is output to PWSCAL register (test only)

DISCP — Disable Compare Scaled E-Clock Bit — factory use only; only accessible in special test mode

- 0 = Normal operation

- 1 = Match of period does not reset associated count register (test only)

PWEN[4:1] — Pulse-Width Enable for Channels [4:1] Bits

- 0 = Channel disabled

- 1 = Channel enabled at port H bits [3:0]

Technical Data

|                    | Window Size             |                         |            |                                          |  |  |  |  |

|--------------------|-------------------------|-------------------------|------------|------------------------------------------|--|--|--|--|

| Number<br>of Banks | 8 Kbytes                | 16 Kbytes               | 32 Kbytes  | 32 Kbytes<br>(Window Based<br>at \$4000) |  |  |  |  |

| 2                  | ADDR[12:0]              | ADDR[13:0]              | ADDR[14:0] | ADDR[13:0]                               |  |  |  |  |

|                    | XA13                    | XA14                    | XA15       | XA[15:14]                                |  |  |  |  |

| 4                  | ADDR[12:0]              | ADDR[13:0]              | ADDR[14:0] | ADDR[13:0]                               |  |  |  |  |

|                    | XA[14:13]               | XA[15:14]               | XA[16:15]  | XA[16:14]                                |  |  |  |  |

| 8                  | ADDR[12:0]              | ADDR[13:0]              | ADDR[14:0] | ADDR[13:0]                               |  |  |  |  |

|                    | XA[15:13]               | XA[16:14]               | XA[17:15]  | XA[17:14]                                |  |  |  |  |

| 16                 | ADDR[12:0]              | ADDR[13:0]              | ADDR[14:0] | ADDR[13:0]                               |  |  |  |  |

|                    | XA[16:13]               | XA[17:14]               | XA[18:15]  | XA[18:14]                                |  |  |  |  |

| 32                 | ADDR[12:0]<br>XA[17:13] | ADDR[13:0]<br>XA[18:14] |            |                                          |  |  |  |  |

| 64                 | ADDR[12:0]<br>XA[18:13] | _                       | —          |                                          |  |  |  |  |

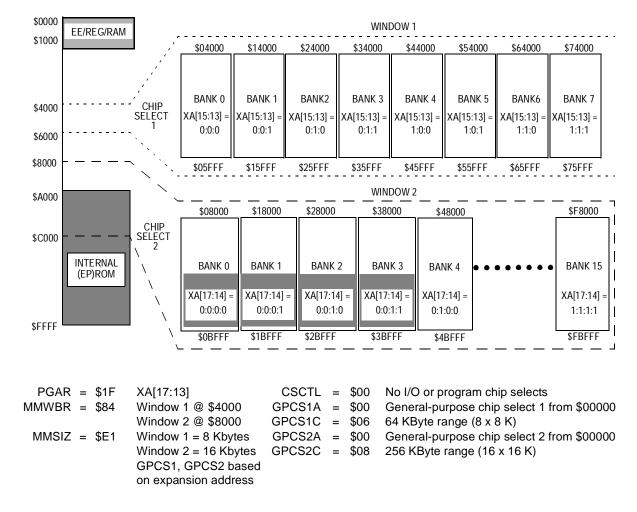

Table 11-1. CPU Address and Address Expansion Signals

The base address for each window must be an integer multiple of the window size, with one exception. When the window size is 32 Kbytes, the base address can be at \$4000 as well as the 32-Kbyte multiples \$0000 and \$8000.

This special case requires a modification in address line deployment. Normally, when the bank size is 32 Kbytes and the bank address is \$0000 or \$8000, CPU address lines ADDR[14:0] select individual bytes within the 32-Kbyte space and the ADDR[14:0] pins are connected to address lines A[14:0] of the memory device. When the base address is \$4000, the CPU address signal ADDR14 must be inverted to allow 32 Kbytes of contiguous memory. To do this, the CPU drives the inverted ADDR14 signal onto the XA14 pin when the window is active, and the non-inverted CPU ADDR14 signal onto the XA14 pin when the window is not active. Therefore, address 14 of the memory device must be connected to expansion line XA14 rather than normal address line ADDR14.

If the two memory windows overlap, window 1 has priority, and only the portion of window 2 that does not overlap window 1 remains active. If a

#### 11.3.2.4 Memory Mapping Window Control Registers

Each of the memory mapping window control registers (MM1CR and MM2CR) determine the active memory bank for the corresponding window, containing the value to be output on the expansion address lines when the CPU selects addresses within its extended memory window. To change banks, write the address of the new bank into the appropriate window register.

| Address:                                                                  | Address: \$0058 Memory Mapping Window 1 Control Register (MM1CR) |           |             |              |                |        |       |       |

|---------------------------------------------------------------------------|------------------------------------------------------------------|-----------|-------------|--------------|----------------|--------|-------|-------|

|                                                                           | Bit 7                                                            | 6         | 5           | 4            | 3              | 2      | 1     | Bit 0 |

| Read:<br>Write:                                                           | 0                                                                | X1A18     | X1A17       | X1A16        | X1A15          | X1A14  | X1A13 | 0     |

| Reset:                                                                    | 0                                                                | 0         | 0           | 0            | 0              | 0      | 0     | 0     |

| Address:                                                                  | \$0059                                                           | Memory Ma | apping Wind | low 2 Contro | ol Register (l | MM1CR) |       |       |

| Read:<br>Write:                                                           | 0                                                                | X2A18     | X2A17       | X2A16        | X2A15          | X2A14  | X2A13 | 0     |

| Reset:                                                                    | 0                                                                | 0         | 0           | 0            | 0              | 0      | 0     | 0     |

| Figure 11-4. Memory Mapping Window Control<br>Registers (MM1CR and MM2CR) |                                                                  |           |             |              |                |        |       |       |

- X1A[18:13] Memory Mapping Window 1 Expansion Address Line Select Bits

- X2A[18:13] Memory Mapping Window 2 Expansion Address Line Select Bits

Each bit value written to the MMxCR registers is driven on the corresponding port G expansion address line (if enabled by PGAR) to enable the specified bank in the window.

M68HC11K Family

MOTOROLA

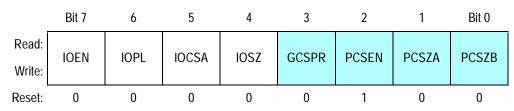

#### 11.4.2 Input/Output Chip Select

The I/O chip select (CSIO) is programmable for a 4-Kbyte size located at addresses \$1000–\$1FFF or 8-Kbyte size located at addresses \$0000–\$1FFF. The default active-low polarity can be changed to active high by setting the IOPL bit in CSCTL. Default validity during high E clock can be changed to address valid time by setting the IOCSA bit in CSCTL. Clock stretching can be set from zero to three cycles (See 11.4.5 Clock Stretching). CSIO is disabled out of reset.

Figure 11-6. Chip-Select Control Register (CSCTL)

IOEN — I/O Chip-Select Enable Bit

0 = CSIO is disabled and port H bit 4 is GPIO.

1 = CSIO is enabled and uses port H bit 4.

#### IOPL — I/O Chip-Select Polarity Select Bit

0 = CSIO active low

1 = CSIO active high

IOCSA — I/O Chip-Select Address Valid Bit

0 = CSIO is valid during E-clock high time.

1 = CSIO is valid during address valid time.

IOSZ — I/O Chip-Select Size Select Bit

0 = CSIO size is four Kbytes at \$1000–\$1FFF.

1 = CSIO size is eight Kbytes at \$0000-\$1FFF.

Semiconductor, Inc.

reescale

# **Freescale Semiconductor, Inc.**

Memory Expansion and Chip Selects Memory Expansion Examples

The second example system shown in **Figure 11-16** contains two memory windows. The first window is organized as in the previous example, 8 banks of 8 Kbytes each. The second window accesses 256 Kbytes of memory in 16 banks of 16 Kbyte each. To access 16 Kbytes, or 2<sup>14</sup> address locations, the CPU will need 14 address lines, ADDR[13:0]. Since ADDR13 is driven on XA13 in this example, XA13 replaces ADDR13 to drive the A13 line in the 6226 devices, but ADDR13 could be used as well. 16  $(2^4)$  memory banks require four expansion address lines, A[17:14]. Refer to Figure 11-16 for a memory map and schematic drawing of this system.

Figure 11-16. Memory Expansion Example 2 (Sheet 1 of 2) Memory Map for One 8-Kbyte Window with Eight Banks and One 16-Kbyte Window with 16 Banks of External Memory

```

M68HC11K Family

```

MOTOROLA

Electrical Characteristics Functional Operating Range

# 12.4 Functional Operating Range

| Rating                                                                         | Symbol          | Value                                                                        | Unit |

|--------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------|------|

| Operating temperature range<br>MC68HC(7)11KC<br>MC68HC(7)11KV<br>MC68HC(7)11KM | T <sub>A</sub>  | T <sub>L</sub> to T <sub>H</sub><br>-40 to +85<br>-40 to +105<br>-40 to +125 | °C   |

| Operating voltage range                                                        | V <sub>DD</sub> | 5.0±10%                                                                      | V    |

# **12.5 Thermal Characteristics**

| Characteristic                                                                                                                                                                                                                                            | Symbol           | Value                                                                | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------|------|

| Average junction temperature                                                                                                                                                                                                                              | Τ <sub>J</sub>   | $T_A + (P_D \times \Theta_JA)$                                       | °C   |

| Ambient temperature                                                                                                                                                                                                                                       | T <sub>A</sub>   | User-determined                                                      | °C   |

| Package thermal resistance (junction-to-ambient)<br>80-pin low-profile quad flat pack<br>68-pin plastic leaded chip carrier<br>68-pin windowed ceramic cerquad (EPROM)<br>84-pin plastic leaded chip carrier<br>80-pin quad flat pack<br>84-pin J-cerquad | Θ <sub>JA</sub>  | 80<br>50<br>60<br>50<br>85<br>50                                     | °C/W |

| Total power dissipation <sup>(1)</sup>                                                                                                                                                                                                                    | P <sub>D</sub>   | P <sub>INT</sub> + P <sub>I/O</sub><br>K / T <sub>J</sub> + 273 °C   | W    |

| Device internal power dissipation                                                                                                                                                                                                                         | P <sub>INT</sub> | $I_{DD} \times V_{DD}$                                               | W    |

| I/O pin power dissipation <sup>(2)</sup>                                                                                                                                                                                                                  | P <sub>I/O</sub> | User-determined                                                      | W    |

| A constant <sup>(3)</sup>                                                                                                                                                                                                                                 | к                | $P_{D} \times (T_{A} + 273^{\circ}C) + \Theta_{JA} \times P_{D}^{2}$ | W/°C |

1. This is an approximate value, neglecting  $P_{I/O}$ .

2. For most applications,  $\mathsf{P}_{I/O} \leq \mathsf{P}_{INT}$  and can be neglected.

3. K is a constant pertaining to the device. Solve for K with a known T<sub>A</sub> and a measured P<sub>D</sub> (at equilibrium). Use this value of K to solve for P<sub>D</sub> and T<sub>J</sub> iteratively for any value of T<sub>A</sub>.

## **Electrical Characteristics**

## **12.6 Electrical Characteristics**

| Characteristic <sup>(1)</sup>                                                                                                                 | Symbol                             | Min                                            | Max                                            | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------------|------------------------------------------------|------|

| Output voltage, $I_{Load} = \pm 10.0 \ \mu A^{(2)}$ )<br>All outputs except XTAL<br>All outputs except XTAL, RESET, and MODA                  | V <sub>ol</sub><br>V <sub>oh</sub> | <br>V <sub>DD</sub> – 0.1                      | 0.1                                            | V    |

| Output high voltage, $I_{Load} = -0.8 \text{ mA}$ , $V_{DD} = 4.5 \text{ V}^{(2)}$<br>All outputs except XTAL, RESET, and MODA                | V <sub>OH</sub>                    | V <sub>DD</sub> - 0.8                          | _                                              | V    |

| Output low voltage, I <sub>Load</sub> = 1.6 mA<br>All outputs except XTAL                                                                     | V <sub>OL</sub>                    |                                                | 0.4                                            | V    |

| Input high voltage<br>All inputs except RESET<br>RESET                                                                                        | V <sub>IH</sub>                    | 0.7 x V <sub>DD</sub><br>0.8 x V <sub>DD</sub> | V <sub>DD</sub> + 0.3<br>V <sub>DD</sub> + 0.3 | V    |

| Input low voltage<br>All Inputs                                                                                                               | V <sub>IL</sub>                    | V <sub>SS</sub> – 0.3                          | 0.2 x V <sub>DD</sub>                          | V    |

| I/O ports, three-state leakage, $V_{In} = V_{IH}$ or $V_{IL}$<br>Ports A, B, C, D, F, G, H, MODA/LIR, RESET                                   | I <sub>oz</sub>                    |                                                | ±10                                            | μΑ   |

| Input leakage current, $V_{In} = V_{DD}$ or $V_{SS}^{(3)}$<br>IRQ, XIRQ on standard devices<br>MODB/V <sub>STBY</sub> , XIRQ on EPROM devices | l <sub>In</sub>                    |                                                | ±1<br>±10                                      | μΑ   |

| Input current with pullup resistors, $V_{In} = V_{IL}$<br>Ports B, F, G, and H                                                                | I <sub>IPR</sub>                   | 100                                            | 500                                            | μA   |

| RAM standby voltage, power down                                                                                                               | V <sub>SB</sub>                    | 2.0                                            | V <sub>DD</sub>                                | V    |

| RAM standby current, power down                                                                                                               | I <sub>SB</sub>                    | _                                              | 10                                             | μA   |

| Input capacitance<br>PE[7:0], IRQ, XIRQ, EXTAL<br>Ports A, B, C, D, F, G, H, MODA/LIR, RESET                                                  | C <sub>In</sub>                    | _                                              | 8<br>12                                        | pF   |

| Output load capacitance<br>All outputs except PD[4:1], XOUT, XTAL, MODA/LIR<br>PD[4:1]<br>XOUT                                                | CL                                 |                                                | 90<br>200<br>30                                | pF   |

1.  $V_{DD} = 5.0 \text{ Vdc} \pm 10\%, V_{SS} = 0 \text{ Vdc}, T_A = T_L \text{ to } T_H, \text{ unless otherwise noted}$ 2.  $V_{OH}$  specification for RESET and MODA is not applicable because they are open-drain pins.  $V_{OH}$  specification not applicable to ports C and D in wired-OR mode.

3. Refer to 12.10 Analog-to-Digital Converter Characteristics for leakage current for port E.

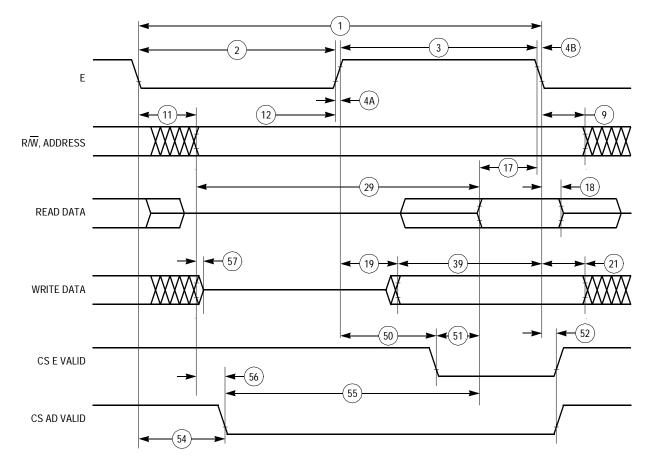

# **Electrical Characteristics**

Figure 12-9. Expansion Bus Timing

Technical Data

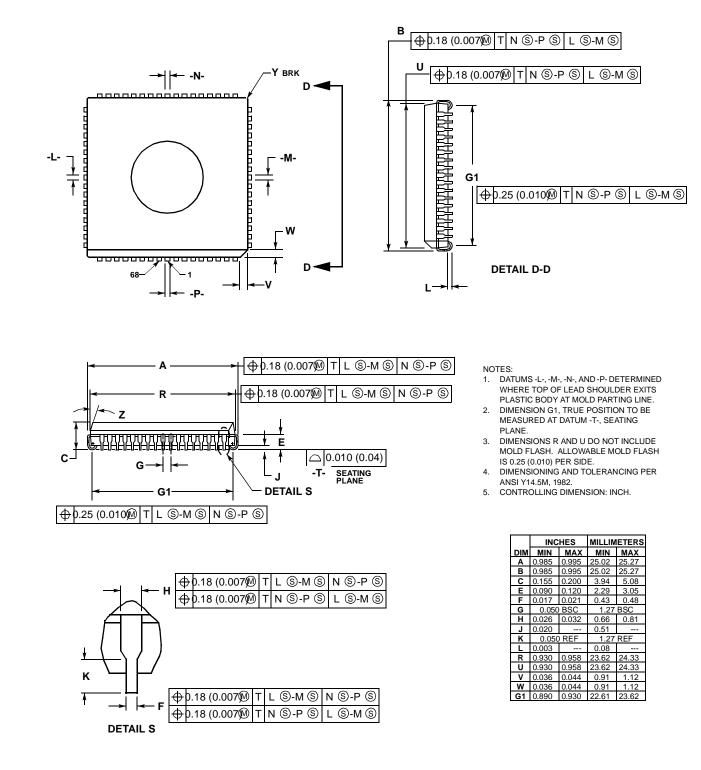

**Mechanical Data**

# 13.8 68-Pin J-Cerquad (Case 779A)

Technical Data

M68HC11K Family

MOTOROLA

Semiconductor, Inc.

Freescale

| OPTION | System Configuration Options               |     |

|--------|--------------------------------------------|-----|

| CME    | Clock Monitor Enable                       | 111 |

| CR[1:0 | )] COP Timer Rate Select Bits              | 109 |

| DLY    | Enable Oscillator Startup Delay            | 132 |

| IRQE   | Configure IRQ for Edge-Sensitive Operation | 121 |

|        |                                            |     |

# Ρ

| PACTL Pulse Accumulator Control          |      |

|------------------------------------------|------|

| I4/O5 Input Capture 4/Output Compare 5   | 191  |

| PAEN Pulse Accumulator System Enable     | 205  |

| PAMOD Pulse Accumulator Mode             | 206  |

| RTR[1:0] Real Time Interrupt Rate Select | 210  |

| PPROG EPROM Programming Control          |      |

| ELAT PROM Latch Control                  | . 93 |

# S

M68HC11K Family

MOTOROLA