Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC11                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 4MHz                                                                   |

| Connectivity               | SCI, SPI                                                               |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 37                                                                     |

| Program Memory Size        | -                                                                      |

| Program Memory Type        | ROMIess                                                                |

| EEPROM Size                | 640 x 8                                                                |

| RAM Size                   | 768 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                            |

| Data Converters            | A/D 8x8b                                                               |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 84-LCC (J-Lead)                                                        |

| Supplier Device Package    | 84-PLCC (29.29x29.29)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc11k1cfn4 |

|                            |                                                                        |

10

# Freescale Semiconductor, Inc.

# **Table of Contents**

| 4.9 XOUT Pin Control                                                                          | 102 |

|-----------------------------------------------------------------------------------------------|-----|

| 4.9.1 System Configuration Register                                                           | 102 |

| 4.9.2 System Configuration Options 2 Register                                                 |     |

|                                                                                               |     |

| Section 5. Resets and Interrupts                                                              |     |

| 5.1 Contents                                                                                  | 105 |

| 5.2 Introduction                                                                              | 106 |

| 5.3 Sources of Resets                                                                         | 106 |

| 5.3.1 Power-On Reset (POR)                                                                    |     |

| 5.3.2 External Reset (RESET)                                                                  |     |

| Computer Operating Properly (COP) System                                                      |     |

| 5.3.3.1 System Configuration Register                                                         |     |

| 5.3.3.2 System Configuration Options Register                                                 |     |

| 5.3.3.3 Arm/Reset COP Timer Circuitry Register                                                |     |

| 5.3.4 Clock Monitor Reset                                                                     |     |

| 5.3.4.1 System Configuration Options Register 5.3.4.2 System Configuration Options Register 2 |     |

| 5.3.4.2 System Configuration Options Register 2                                               | 112 |

| 5.4 Effects of Reset                                                                          | 115 |

| 5.5 Interrupts                                                                                | 117 |

| 5.5.1 Non-Maskable Interrupts                                                                 | 120 |

| 5.5.1.1 Non-Maskable Interrupt Request (XIRQ)                                                 | 120 |

| 5.5.1.2 Illegal Opcode Trap                                                                   |     |

| 5.5.1.3 Software Interrupt (SWI)                                                              |     |

| 5.5.2 Maskable Interrupts                                                                     | 121 |

| 5.6 Reset and Interrupt Priority                                                              | 122 |

| 5.7 Reset and Interrupt Processing                                                            | 123 |

| 5.8 Low-Power Operation                                                                       |     |

| 5.8.1 Wait Mode                                                                               |     |

| 5.8.2 Stop Mode                                                                               |     |

| 5.8.3 Slow Mode                                                                               | 132 |

**Table of Contents**

| 11.4 Chip Selects                                                                                                       | 238 |

|-------------------------------------------------------------------------------------------------------------------------|-----|

| 11.4.1 Program Chip Select                                                                                              |     |

| 11.4.2 Input/Output Chip Select                                                                                         |     |

| 11.4.3 General-Purpose Chip Selects                                                                                     |     |

| <ul><li>11.4.3.1 Memory Mapping Size Register</li><li>11.4.3.2 General-Purpose Chip Select 1 Address Register</li></ul> |     |

| 11.4.3.3 General-Purpose Chip Select 1 Control Register                                                                 |     |

| 11.4.3.4 General-Purpose Chip Select 2 Address Register                                                                 |     |

| 11.4.3.5 General-Purpose Chip Select 2 Control Register                                                                 | 245 |

| 11.4.4 One Chip Select Driving Another                                                                                  |     |

| 11.4.4.1 General-Purpose Chip Select 1 Control Register                                                                 |     |

| 11.4.4.2 General-Purpose Chip Select 2 Control Register                                                                 |     |

| 11.4.5 Clock Stretching                                                                                                 |     |

| 11.5 Memory Expansion Examples                                                                                          | 249 |

| Continu 42 Floatwing Characteristics                                                                                    |     |

| Section 12. Electrical Characteristics                                                                                  |     |

| 12.1 Contents                                                                                                           | 253 |

| 12.2 Introduction                                                                                                       | 254 |

| 12.3 Maximum Ratings for Standard Devices                                                                               | 254 |

| 12.4 Functional Operating Range                                                                                         | 255 |

| 12.5 Thermal Characteristics                                                                                            | 255 |

| 12.6 Electrical Characteristics                                                                                         | 256 |

| 12.7 Power Dissipation Characteristics                                                                                  | 257 |

| 12.8 Control Timing                                                                                                     | 259 |

| 12.9 Peripheral Port Timing                                                                                             | 263 |

| 12.10 Analog-to-Digital Converter Characteristics                                                                       | 265 |

| 12.11 Expansion Bus Timing                                                                                              | 267 |

| 12.12 Serial Peripheral Interface Timing                                                                                | 269 |

| 12.13 EEPROM Characteristics                                                                                            | 272 |

# Technical Data — M68HC11K Family

# **List of Figures**

| Figur | e Title                                            | Page |

|-------|----------------------------------------------------|------|

| 1-1   | M68HC11K4 Family Block Diagram                     | 29   |

| 1-2   | M68HC11KS Family Block Diagram                     | 30   |

| 2-1   | Pin Assignments for M68HC11K 84-Pin PLCC/J-Cerquad |      |

| 2-2   | Pin Assignments for M6811K 80-Pin QFP              |      |

| 2-3   | Pin Assignments for M6811KS 68-Pin PLCC/J-Cerquad  |      |

| 2-4   | Pin Assignments for M6811KS 80-Pin LQFP            |      |

| 2-5   | External Reset Circuit                             |      |

| 2-6   | Common Crystal Connections                         |      |

| 2-7   | System Configuration Options 2 (OPT2)              | 40   |

| 2-8   | LIR Timing                                         |      |

| 2-9   | MODB/V <sub>STBY</sub> Connection                  | 41   |

| 3-1   | Programming Model                                  | 46   |

| 3-2   | Stacking Operations                                | 49   |

| 4-1   | Register and Control Bit Assignments               | 65   |

| 4-2   | Highest Priority I-Bit Interrupt                   |      |

|       | and Miscellaneous Register (HPRIO)                 | 80   |

| 4-3   | M68HC11K4 Family Memory Map                        | 82   |

| 4-4   | M68HC11KS2 Family Memory Map                       | 83   |

| 4-5   | RAM and I/O Mapping Register (INIT)                | 84   |

| 4-6   | System Configuration Register (CONFIG)             | 88   |

| 4-7   | EEPROM Mapping Register (INIT2)                    | 89   |

| 4-8   | EPROM Programming Control Register (EPROG)         | 91   |

| 4-9   | EEPROM Programming Control Register (PPROG)        | 94   |

| 4-10  | Block Protect Register (BPROT)                     |      |

| 4-11  | System Configuration Options Register (OPTION)     |      |

| 4-12  | Block Protect Register (BPROT)                     |      |

|       |                                                    |      |

# **List of Tables**

| Table | Title                                      | Page |

|-------|--------------------------------------------|------|

| 7-1   | SCI Receiver Flags                         | 153  |

| 7-2   | SCI+ Baud Rates                            | 159  |

| 8-1   | SPI+ Baud Rates                            | 175  |

| 9-1   | Main Timer Rates                           | 184  |

| 9-2   | Timer Prescale                             | 190  |

| 9-3   | Input Capture Edge Selection               | 195  |

| 9-4   | Timer Output Compare Actions               | 201  |

| 9-5   | Pulse Accumulator Timing                   | 203  |

| 9-6   | Pulse Accumulator Edge Control             |      |

| 9-7   | Real-Time Interrupt Rate versus RTR[1:0]   |      |

| 9-8   | Clock A Prescaler                          |      |

| 9-9   | Clock B Prescaler                          | 214  |

| 10-1  | A/D Converter Channel Selection            | 225  |

| 11-1  | CPU Address and Address Expansion Signals  | 233  |

| 11-2  | Window Size Select                         | 235  |

| 11-3  | Memory Expansion Window Base Address       | 236  |

| 11-4  | Chip Select Control Parameter Summary      |      |

| 11-5  | Program Chip Select Size                   |      |

| 11-6  | General-Purpose Chip Select 1 Size Control |      |

| 11-7  | General-Purpose Chip Select 2 Size Control |      |

| 11-8  | One Chip Select Driving Another            |      |

| 11-9  | CSCSTR Bits Versus Clock Cycles            | 249  |

| 14-1  | M68HC11K Family Devices                    | 281  |

# Technical Data — M68HC11K Family

# **Section 2. Pin Description**

## 2.1 Contents

| 2.2  | Introduction                                                                                            |

|------|---------------------------------------------------------------------------------------------------------|

| 2.3  | Power Supply (V <sub>DD</sub> , V <sub>SS</sub> , AV <sub>DD</sub> , and AV <sub>SS</sub> )36           |

| 2.4  | Reset (RESET)                                                                                           |

| 2.5  | Crystal Driver and External Clock Input (XTAL and EXTAL)                                                |

| 2.6  | XOUT38                                                                                                  |

| 2.7  | E-Clock Output (E)                                                                                      |

| 2.8  | Interrupt Request (IRQ) and Non-Maskable Interrupt (XIRQ)                                               |

| 2.9  | Mode Selection, Instruction Cycle Reference, and Standby Power (MODA/LIR and MODB/V <sub>STBY</sub> )39 |

| 2.10 | V <sub>RH</sub> and V <sub>RL</sub> 41                                                                  |

| 2.11 | Port Signals41                                                                                          |

|      |                                                                                                         |

### 2.2 Introduction

The M68HC11K Family is available in a variety of packages, as shown in **Table 1-1. M68HC11K Family Devices**. Most pins on this MCU serve two or more functions, as described in this section. Pin assignments for the various package types are shown in **Figure 2-1**, **Figure 2-2**, **Figure 2-3**, and **Figure 2-4**.

Central Processor Unit (CPU)

Opcodes and Operands

there are no special requirements for alignment of instructions or operands.

## 3.5 Opcodes and Operands

The M68HC11 Family of microcontrollers uses 8-bit opcodes. Every instruction requires a unique opcode for each of its addressing modes. The resulting number of opcodes exceeds the 256 available in an 8-bit binary number. A 4-page opcode map has been implemented to accommodate the extra instructions. An additional byte, called a prebyte, directs the processor from page 0 of the opcode map to one of the other three pages. As its name implies, the additional byte precedes the opcode.

A complete instruction consists of a prebyte, if any, an opcode, and zero to three operands. The operands contain information the CPU needs for executing the instruction. Complete instructions can be from one to five bytes long.

# 3.6 Addressing Modes

Six addressing modes can be used to access memory:

- 1. Immediate

- 2. Direct

- 3. Extended

- 4. Indexed

- 5. Inherent

- Relative

All modes except inherent mode use an effective address. The effective address is the memory address where the argument is fetched or stored or the address from which execution is to proceed. The effective address can be specified within an instruction or it can be calculated.

Operating Modes and On-Chip Memory

Control Registers

| Addr.  | Register Name                                                  |                 | Bit 7 | 6          | 5      | 4     | 3          | 2     | 1           | Bit 0 |

|--------|----------------------------------------------------------------|-----------------|-------|------------|--------|-------|------------|-------|-------------|-------|

| \$0062 | Pulse Width Modulation<br>Timer Prescaler<br>Register (PWSCAL) | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|        | See page 215.                                                  | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0063 | Pulse Width Modulation<br>Timer Enable Register<br>(PWEN)      | Read:<br>Write: | TPWSL | DISCP      | 0      | 0     | PWEN4      | PWEN3 | PWEN2       | PWEN1 |

|        | See page 216.                                                  | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0064 | Pulse Width Modulation<br>Timer Counter 1<br>Register (PWCNT1) | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|        | See page 217.                                                  | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0065 | Pulse Width Modulation<br>Timer Counter 2<br>Register (PWCNT2) | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|        | See page 217.                                                  | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0066 | Pulse Width Modulation Timer Counter 3                         | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|        | Register (PWCNT3) See page 217.                                | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0067 | Pulse Width Modulation<br>Timer Counter 4<br>Register (PWCNT4) | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|        | See page 217.                                                  | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0068 | Pulse Width Modulation<br>Timer Period 1 Register<br>(PWPER1)  | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|        | See page 218.                                                  | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0069 | Pulse Width Modulation<br>Timer Period 2 Register<br>(PWPER2)  | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|        | See page 218.                                                  | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$006A | Pulse Width Modulation<br>Timer Period 3 Register<br>(PWPER3)  | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|        | See page 218.                                                  | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

| \$006B | Pulse Width Modulation<br>Timer Period 4 Register<br>(PWPER4)  | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|        | See page 218.                                                  | Reset:          | 0     | 0          | 0      | 0     | 0          | 0     | 0           | 0     |

|        |                                                                |                 |       | = Unimplem | nented | R     | = Reserved |       | U = Undefir | ned   |

Figure 4-1. Register and Control Bit Assignments (Sheet 9 of 11)

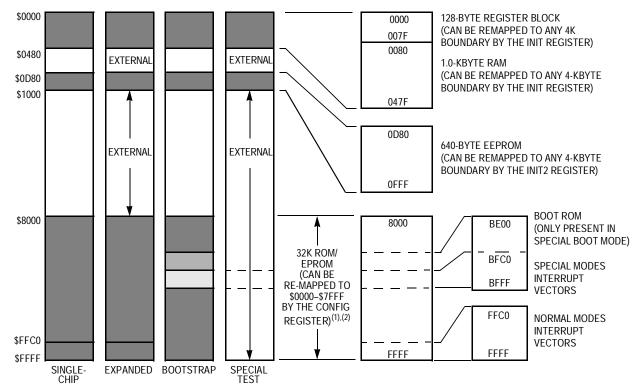

Operating Modes and On-Chip Memory Memory Map

Note: 1.EPROM can be enabled in special test mode by setting the ROMON bit in the CONFIG register after reset.

Figure 4-4. M68HC11KS2 Family Memory Map

**Table 4-4** shows the default memory map addresses for the M68HC11K Family devices.

**Table 4-4. Default Memory Map Addresses**

|           | [7]11K4       | [7]11KS2      |

|-----------|---------------|---------------|

| Registers | \$0000-\$007F | \$0000-\$007F |

| RAM       | \$0080-\$037F | \$0080-\$047F |

| EEPROM    | \$0D80-\$0FFF | \$0D80-\$0FFF |

| ROM/EPROM | \$A000-\$FFFF | \$8000-\$FFFF |

## Resets and Interrupts

Three registers are involved in COP operation:

- The CONFIG register contains a bit which determines whether the COP system is enabled or disabled.

- The OPTION register contains two bits which determine the COP timeout period.

- The COPRST register must be written by software to reset the watchdog timer.

**NOTE:** Throughout this manual, the registers are discussed by function. In the event that not all bits in a register are referenced, the bits that are not discussed are shaded.

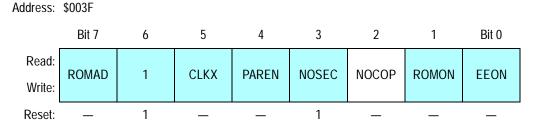

### 5.3.3.1 System Configuration Register

In normal modes, COP is enabled out of reset and does not depend on software action. To disable the COP system, set the NOCOP bit in the CONFIG register (see **Figure 5-1**). In special test and bootstrap operating modes, the COP system is initially inhibited by the disable resets (DISR) control bit in the TEST1 register. The DISR bit can subsequently be written to 0 to enable COP resets.

Figure 5-1. System Configuration Register (CONFIG)

**NOTE:** CONFIG is writable once in normal modes and writable at any time in special modes.

NOCOP — COP System Disable Bit 0 = COP enabled 1 = COP disabled

Resets and Interrupts

Interrupts

- The RDRF, IDLE, OR, NF, FE, PF, and RAF receive-related status bits are cleared.

- Serial peripheral interface (SPI)

- The SPI system is disabled by reset.

- The port pins associated with this function default to being general-purpose I/O lines.

- Analog-to-digital (A/D) converter

- The ADPU bit in the OPTION register is cleared, disabling the A/D system.

- The conversion complete flag in the ADCTL register is also cleared.

### System

- The external IRQ pin has the highest I-bit interrupt priority because PSEL[4:0] in the HPRIO register are initialized with the value %00110 (where % indicates a binary value).

- The RBOOT, SMOD, and MDA bits in the HPRIO register reflect the status of the MODB and MODA inputs at the rising edge of reset.

- The IRQ pin is configured for level-sensitive operation for wired-OR systems.

- The DLY control bit in the OPTION register is set, enabling oscillator startup delay after recovery from stop mode.

- The clock monitor system is disabled because the CME and FCME bits in the OPTION register are cleared.

# 5.5 Interrupts

The MCU has 18 interrupt vectors that support 22 interrupt sources. The 19 maskable interrupts are generated by on-chip peripheral systems. They are recognized when the I bit in the CCR is clear. The three non-maskable interrupt sources are illegal opcode trap, software interrupt, and  $\overline{\text{XIRQ}}$  pin. Table 5-5 lists the interrupt sources and vector assignments for each source.

## **Serial Communications Interface (SCI)**

The M68HC11K series offers several enhancements to the basic MC68HC11 SCI, including:

- 13-bit modulus prescaler in the baud generator

- Receiver-active flag

- Transmitter and receiver hardware parity

- Accelerated idle line detection

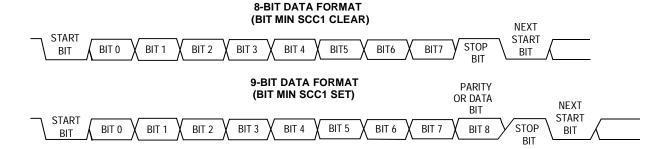

#### 7.3 Data Format

The SCI uses the standard non-return to zero mark/space data format illustrated in **Figure 7-1**.

Figure 7-1. SCI Data Formats

Data is transmitted in frames consisting of a start bit, a word of eight or nine data bits, and a stop bit. The step-by-step transmission procedure is:

- The transmission line is idle before a message is transmitted. This

means that the line is in a logic 1 state for at least one frame time.

- 2. A start bit, logic 0, is transmitted, indicating the start of a frame.

- 3. An 8-bit or 9-bit word is transmitted, least significant bit (LSB) first.

- 4. A stop bit, logic 1, is transmitted to indicate the end of a frame.

- 5. An optional number of breaks can be transmitted. A break is the transmission of a logic low state for one frame time. After the last break character is sent, the line goes high for at least one bit time.

Semiconductor, Inc.

**RAF**

Receiver active

During receive operations, data from the TxD pin is shifted into the serial shift register. A completed word is parallel-loaded to a receive data register (RDR), which can be read through SCDRH/L. This double-buffered operation allows reception of the current character while the MCU reads the previous character.

The SCI receiver has seven status flags, summarized in Table 7-1.

Interrupt Set When Flag Name **Enable Bit** Receive data Character transferred from shift register **RDRF** RIE register full to RDR Idle-line IDLE ILIE Active transmit line goes idle detected Character ready for RDR while previous OR Overrun error RIE character unread NF Noise error Samples of data bit not unanimous FE Frame error 0 detected where stop bit expected Calculated parity does not match data PF Parity error parity bit

Table 7-1. SCI Receiver Flags

Three of the flags can generate interrupt requests if the corresponding enable bits in SCCR2 are set. The status flags are set by the SCI logic in response to specific conditions in the receiver. These flags can be read (polled) at any time by software. Each bit except RAF is cleared by reading SCSR1 and SCDR sequentially.

A character is being received

- The receive data register full (RDRF) flag is set when the last bit

of a character is received and data is transferred from the shift

register to the RDR.

- The IDLE flag is set after a transition on the RxD line from an active state to an idle state. This prevents repeated interrupts during the time RxD remains idle.

Timing System Input Capture (IC)

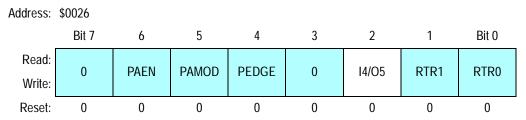

### 9.4.5 Pulse Accumulator Control Register

Figure 9-7. Pulse Accumulator Control Register (PACTL)

14/O5 — Input Capture 4/Output Compare 5 Bit

0 = Configure PA3 as OC5

1 = Configure PA3 as IC4

To configure PA3 as input compare 4, clear DDA3 and set I4/05. To configure PA3 as output compare 5, set DDA3 and clear I4/05. If the DDA3 bit is set (configuring PA3 as an output) and IC4 is enabled, writing a one to TI4/O5 causes an input capture. Writing to TI4/O5 has no effect when DDA3 is cleared and/or OC5 is enabled.

# 9.5 Input Capture (IC)

The input capture function records the time an external event occurs by latching the value of the free-running counter into one of the timer input capture (TIC) registers when a selected edge is detected at its associated timer input pin. Software can store latched values and use them to compute the period and duration of events. For example, by storing the times of successive edges of an incoming signal, software can determine the period and pulse width of a signal. To measure the period, two successive edges of the same polarity are captured. To measure pulse width, two alternate polarity edges are captured.

Capture requests are latched on the opposite half cycle of PH2 from when the timer counter is being incremented. This synchronization process introduces a delay between edge occurrence and counter value detection. Because these delays offset each other when the time between two edges is measured, they can be ignored. There is a similar delay for output compare between the actual compare point and when the output pin changes state.

# **Timing System**

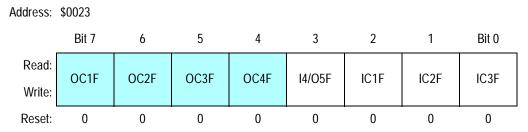

### 9.5.3 Timer Interrupt Flag 1 Register

Figure 9-10. Timer Interrupt Flag 1 Register (TFLG1)

Clear each flag by writing a 1 to the corresponding bit position.

ICxF — Input Capture x Flag

Set each time a selected active edge is detected on the corresponding input capture line.

14/O5F — Input Capture 4/Output Compare 5 Flag

Set each time a selected active edge is detected on the IC4 line if IC4 is enabled.

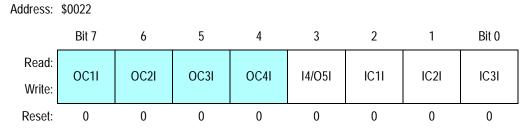

#### 9.5.4 Timer Interrupt Mask 1 Register

Figure 9-11. Timer Interrupt Mask 1 Register (TMSK1)

Bits in TMSK1 correspond bit for bit with flag bits in TFLG1.

ICxI — Input Capture Interrupt Enable Bit

If the ICxI enable bit is set when the ICxF flag bit is set, a hardware interrupt sequence is requested.

Technical Data M68HC11K Family

Go to: www.freescale.com

## 10.4.3 Analog-to-Digital Converter Result Registers

These read-only registers hold an 8-bit conversion result. Writes to these registers have no effect. Data in the A/D converter result registers is valid when the CCF flag in the ADCTL register is set, indicating a conversion sequence is complete. If conversion results are needed sooner, refer to Figure 10-2, which shows the A/D conversion sequence diagram.

|                             | Bit 7                                      | 6           | 5                      | 4                          | 3           | 2     | 1     | Bit 0 |  |  |  |

|-----------------------------|--------------------------------------------|-------------|------------------------|----------------------------|-------------|-------|-------|-------|--|--|--|

| Address:                    | \$0031                                     | Analog-to-E | Digital Resul          | lt Register 1              |             |       |       |       |  |  |  |

| Read:                       | Bit 7                                      | Bit 6       | Bit 5                  | Bit 4                      | Bit 3       | Bit 2 | Bit 1 | Bit 0 |  |  |  |

| Write:                      |                                            |             |                        |                            |             |       |       |       |  |  |  |

| Reset:                      | Undefined after reset                      |             |                        |                            |             |       |       |       |  |  |  |

| Address:                    | \$0032 Analog-to-Digital Result Register 2 |             |                        |                            |             |       |       |       |  |  |  |

| Read:                       | Bit 7                                      | Bit 6       | Bit 5                  | Bit 4                      | Bit 3       | Bit 2 | Bit 1 | Bit 0 |  |  |  |

| Write:                      |                                            |             |                        |                            |             |       |       |       |  |  |  |

| Reset:                      |                                            |             |                        | Undefined                  | after reset |       |       |       |  |  |  |

| Address:                    | \$0033                                     | Analog-to-D | Digital Resul          | lt Register 3              |             |       |       |       |  |  |  |

| Read:                       | Bit 7                                      | Bit 6       | Bit 5                  | Bit 4                      | Bit 3       | Bit 2 | Bit 1 | Bit 0 |  |  |  |

| Write:                      |                                            |             |                        |                            |             |       |       |       |  |  |  |

| winto.                      |                                            |             |                        |                            |             |       |       |       |  |  |  |

| Reset:                      |                                            |             |                        | Undefined                  | after reset |       |       |       |  |  |  |

|                             | \$0034                                     | Analog-to-E | Digital Resul          | Undefined<br>It Register 4 |             |       |       |       |  |  |  |

| Reset:                      | \$0034<br>Bit 7                            | Analog-to-E | Digital Resul<br>Bit 5 |                            |             | Bit 2 | Bit 1 | Bit 0 |  |  |  |

| Reset:<br>Address:          |                                            | 1           |                        | lt Register 4              |             | Bit 2 | Bit 1 | Bit 0 |  |  |  |

| Reset:<br>Address:<br>Read: |                                            | 1           |                        | lt Register 4              | Bit 3       | Bit 2 | Bit 1 | Bit 0 |  |  |  |

Figure 10-5. Analog-to-Digital Result Registers (ADR1-ADR4))

# **Memory Expansion and Chip Selects**

### 11.3.2.3 Memory Mapping Window Base Register

The memory mapping window base register (MMWBR) defines the starting address of each of the two windows within the CPU 64-Kbyte address range. The windows normally begin at a boundary related to their size (an 8-Kbyte window can begin on any 8-Kbyte boundary, beginning at \$0000).

Address: \$0057 Bit 7 3 2 1 Bit 0 6 5 4 Read: W2A15 W2A14 W2A13 0 W1A15 W1A14 W1A13 0 Write: 0 0 0 0 0 0 Reset:

Figure 11-3. Memory Mapping Window Base Register (MMWBR)

W2A[15:13] — Window 2 Base Address Bits

Selects the three most significant bits (MSB) of the base address for memory mapping window 2. Refer to **Table 11-3**.

W1A[15:13] — Window Base 1 Address Bits

Selects the three MSB of the base address for memory mapping window 1. Refer to **Table 11-3**.

**Table 11-3. Memory Expansion Window Base Address**

| MSB Bits   | Window Base Address |           |           |  |  |  |

|------------|---------------------|-----------|-----------|--|--|--|

| WxA[15:13] | 8 Kbytes            | 16 Kbytes | 32 Kbytes |  |  |  |

| 000        | \$0000              | \$0000    | \$0000    |  |  |  |

| 001        | \$2000              | \$0000    | \$0000    |  |  |  |

| 010        | \$4000              | \$4000    | \$4000    |  |  |  |

| 011        | \$6000              | \$4000    | \$4000    |  |  |  |

| 100        | \$8000              | \$8000    | \$8000    |  |  |  |

| 101        | \$A000              | \$8000    | \$8000    |  |  |  |

| 110        | \$C000              | \$C000    | \$8000    |  |  |  |

| 111        | \$E000              | \$C000    | \$8000    |  |  |  |

# **Memory Expansion and Chip Selects**

### 11.4.3.3 General-Purpose Chip Select 1 Control Register

Address: \$005D 3 Bit 0 Bit 7 6 5 4 2 1 Read: G1DPC G1DG2 G1POL G1AV G1SZA G1SZB G1SCC G1SZD Write: Reset: 0 0 0 0 0

Figure 11-9. General-Purpose Chip Select 1

Control Register (GPCS1C)

G1POL — General-Purpose Chip Select 1 Polarity Select Bit

0 = CSGP1 active low

1 = CSGP1 active high

G1AV — General-Purpose Chip Select 1 Address Valid Select Bit

0 = CSGP1 is valid during E high time.

1 = CSGP1 is valid during address valid time.

G1SZ[A:D] — General-Purpose Chip Select 1 Size Bits

They select the range of GPCS1. Refer to Table 11-6.

Table 11-6. General-Purpose Chip Select 1 Size Control

| G1SZ[A:D] | Size (Bytes)     | Valid Bits<br>(MXGS1 = 0) | Valid Bits<br>(MXGS1 = 1) |

|-----------|------------------|---------------------------|---------------------------|

| 0 0 0 0   | Disabled         | None                      | None                      |

| 0 0 0 1   | 2 K              | G1A[15:11]                | G1A[18:11]                |

| 0 0 1 0   | 4 K              | G1A[15:11]                | G1A[18:12]                |

| 0 0 1 1   | 8 K              | G1A[15:13]                | G1A[18:13]                |

| 0100      | 16 K             | G1A[15:14]                | G1A[18:14]                |

| 0101      | 32 K             | G1A[15]                   | G1A[18:15]                |

| 0110      | 64 K             | None                      | G1A[18:16]                |

| 0111      | 128 K            | None                      | G1A[18:17]                |

| 1000      | 256 K            | None                      | G1A18                     |

| 1 0 0 1   | 512 K            | None                      | None                      |

| 1010      | Follow window 1  | None                      | None                      |

| 1 0 1 1   | Follow window 2  | None                      | None                      |

| 1100–1111 | Default to 512 K | None                      | None                      |

# **Memory Expansion and Chip Selects**

Table 11-8. One Chip Select Driving Another

| G1DG2 | G1DPC | G2DPC | Program CS Pin<br>is Asserted<br>When Address is in: | General 2 CS Pin<br>is Asserted<br>When Address is in: | General 1 CS Pin<br>is Asserted<br>When Address is in: |

|-------|-------|-------|------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| 0     | 0     | 0     | A valid program area                                 | A valid general 2 area                                 | A valid general 1 area                                 |

| 0     | 0     | 1     | A valid program or general 2 area                    | Never asserted                                         | A valid general 1 area                                 |

| 0     | 1     | 0     | A valid program or general 1 area                    | A valid general 2 area                                 | Never asserted                                         |

| 0     | 1     | 1     | A valid program or general 1 or 2 area               | Never asserted                                         | Never asserted                                         |

| 1     | 0     | 0     | A valid program area                                 | A valid general 2 or general 1 area                    | Never asserted                                         |

| 1     | 0     | 1     | A valid program or general 2 area                    | Never asserted                                         | A valid general 1 area                                 |

| 1     | 1     | 0     | A valid program or general 1 area                    | A valid general 2 area                                 | Never asserted                                         |

| 1     | 1     | 1     | A valid program or general 1 or 2 area               | Never asserted                                         | Never asserted                                         |

### 11.4.5 Clock Stretching

Chip select and bus control signals are synchronized with the external E clock. To accommodate devices that are slower than the MCU, the E clock can be stretched when a chip select is asserted so that it remains high for one to three extra bus cycles. During this stretch, which can occur only during accesses to addresses in that chip select's address range, the other clocks continue running normally, maintaining the integrity of the timers and baud generators. Each chip select has two associated bits in the chip-select clock stretch (CSCSTR) register that set its clock stretching from zero (disabled) to three cycles.

**Ordering Information**