# Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HC11                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 3MHz                                                                    |

| Connectivity               | SCI, SPI                                                                |

| Peripherals                | POR, PWM, WDT                                                           |

| Number of I/O              | 37                                                                      |

| Program Memory Size        | -                                                                       |

| Program Memory Type        | ROMIess                                                                 |

| EEPROM Size                | 640 x 8                                                                 |

| RAM Size                   | 768 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                             |

| Data Converters            | A/D 8x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 84-LCC (J-Lead)                                                         |

| Supplier Device Package    | 84-PLCC (29.29x29.29)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc11k1cfne3 |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

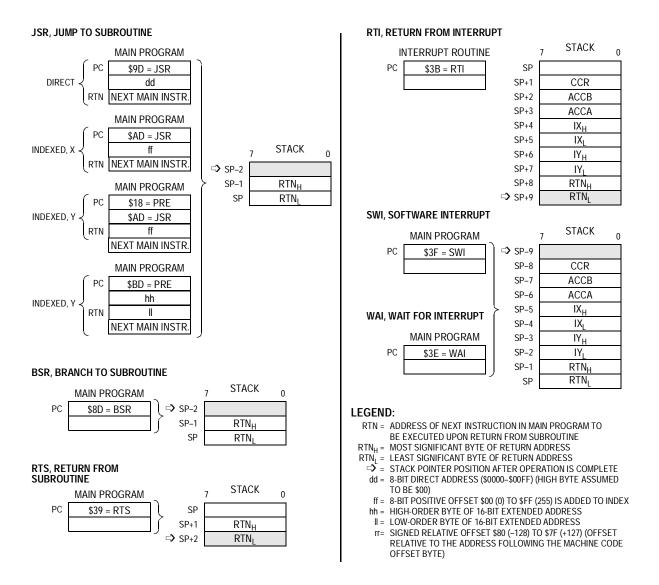

Figure 3-2. Stacking Operations

M68HC11K Family

Operating Modes and On-Chip Memory Control Registers

| Addr.    | Register Name                                                       |                 | Bit 7 | 6          | 5     | 4            | 3           | 2     | 1             | Bit 0 |  |

|----------|---------------------------------------------------------------------|-----------------|-------|------------|-------|--------------|-------------|-------|---------------|-------|--|

| \$0028   | Serial Peripheral<br>Control Register<br>(SPCR)                     | Read:<br>Write: | SPIE  | SPE        | DWOM  | MSTR         | CPOL        | CPHA  | SPR1          | SPR0  |  |

|          | See page 174.                                                       | Reset:          | 0     | 0          | 0     | 0            | 0           | 1     | U             | U     |  |

| \$0029   | Serial Peripheral Status<br>Register (SPSR)                         | Read:<br>Write: | SPIF  | WCOL       | 0     | MODF         | 0           | 0     | 0             | 0     |  |

|          | See page 176.                                                       | Reset:          | 0     | 0          | 0     | 0            | 0           | 0     | 0             | 0     |  |

| \$002A   | Serial Peripheral Data<br>Register (SPDR)                           | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5 | Bit 4        | Bit 3       | Bit 2 | Bit 1         | Bit 0 |  |

|          | See page 177.                                                       | Reset:          |       | -          |       | Undefined    | after reset |       |               |       |  |

| \$002B   | EPROM Programming<br>Control Register<br>(EPROG) <sup>(1)</sup>     | Read:<br>Write: | R     | 0          | ELAT  | EXCOL        | EXROW       | 0     | 0             | EPGM  |  |

|          | See page 91.                                                        | Reset:          | 0     | 0          | 0     | 0            | 0           | 0     | 0             | 0     |  |

| 1. Prese | ent only in EPROM (711)                                             | devices         |       |            |       |              |             |       |               |       |  |

|          |                                                                     | Deed            |       |            |       |              | [           | [     |               |       |  |

| \$002C   | Port Pullup Assignment<br>Register (PPAR)                           | Read:<br>Write: | 0     | 0          | 0     | 0            | HPPUE       | GPPUE | FPPUE         | BPPUE |  |

|          | See page 147.                                                       | Reset:          | 0     | 0          | 0     | 0            | 1           | 1     | 1             | 1     |  |

| \$002D   | Port G Assignment<br>Register (PGAR)                                | Read:<br>Write: | 0     | 0          | PGAR5 | PGAR4        | PGAR3       | PGAR2 | PGAR1         | PGAR  |  |

|          | See page 235.                                                       | Reset:          | 0     | 0          | 0     | 0            | 0           | 0     | 0             | 0     |  |

| \$002E   | System Configuration<br>Options 3 Register<br>(OPT3) <sup>(2)</sup> | Read:<br>Write: |       | SM         |       |              |             |       |               |       |  |

|          | See page 132.                                                       | Reset:          | 0     | 0          | 0     | 0            | 0           | 0     | 0             | 0     |  |

| 2. Not a | vailable on M68HC11K4 (                                             | devices         |       |            |       |              |             |       |               |       |  |

| \$002F   | Reserved                                                            | [               | R     | R          | R     | R            | R           | R     | R             | R     |  |

|          | Analog-to-Digital                                                   | Read:           |       |            |       |              |             |       |               |       |  |

| \$0030   | Control/Status Register<br>(ADCTL)                                  | Write:          | CCF   | 0          | SCAN  | MULT         | CD          | CC    | СВ            | CA    |  |

|          | See page 227.                                                       | Reset:          | 0     | 0          | U     | U            | U           | U     | U             | U     |  |

| \$0031   | Analog-to-Digital<br>Results Register 1                             | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5 | Bit 4        | Bit 3       | Bit 2 | Bit 1         | Bit 0 |  |

|          | (ADR1)<br>See page 229.                                             | Reset:          |       |            |       | Undefined    | after reset |       |               |       |  |

|          | 1.5                                                                 | E C             |       | = Unimpler |       | R = Reserved |             |       | U = Undefined |       |  |

Figure 4-1. Register and Control Bit Assignments (Sheet 5 of 11)

M68HC11K Family

MOTOROLA

# **Operating Modes and On-Chip Memory**

| Addr.  | Register Name                                                     |                 | Bit 7 | 6          | 5      | 4                     | 3     | 2     | 1             | Bit 0 |

|--------|-------------------------------------------------------------------|-----------------|-------|------------|--------|-----------------------|-------|-------|---------------|-------|

| \$006C | Pulse Width Modulation<br>Timer Duty Cycle 1                      | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4                 | Bit 3 | Bit 2 | Bit 1         | Bit 0 |

|        | Register (PWDTY1)<br>See page 219.                                | Reset:          | 0     | 0          | 0      | 0                     | 0     | 0     | 0             | 0     |

| \$006D | Pulse Width Modulation<br>Timer Duty Cycle 2<br>Register (PWDTY2) | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4                 | Bit 3 | Bit 2 | Bit 1         | Bit 0 |

|        | See page 219.                                                     | Reset:          | 0     | 0          | 0      | 0                     | 0     | 0     | 0             | 0     |

| \$006E | Pulse Width Modulation<br>Timer Duty Cycle 3<br>Register (PWDTY3) | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4                 | Bit 3 | Bit 2 | Bit 1         | Bit 0 |

|        | See page 219.                                                     | Reset:          | 0     | 0          | 0      | 0                     | 0     | 0     | 0             | 0     |

| \$006F | Pulse Width Modulation<br>Timer Duty Cycle 4<br>Register (PWDTY4) | Read:<br>Write: | Bit 7 | Bit 6      | Bit 5  | Bit 4                 | Bit 3 | Bit 2 | Bit 1         | Bit 0 |

|        | See page 219.                                                     | Reset:          | 0     | 0          | 0      | 0                     | 0     | 0     | 0             | 0     |

| \$0070 | 5 5 7                                                             | Read:<br>Write: | BTST  | BSPL       | 0      | SBR12                 | SBR11 | SBR10 | SBR9          | SBR8  |

|        | See page 158.                                                     | Reset:          | 0     | 0          | 0      | 0                     | 0     | 0     | 0             | 0     |

| \$0071 | SCI Baud Rate Control<br>Register Low (SCBDL)<br>See page 158.    | Read:<br>Write: | SBR7  | SBR6       | SBR5   | SBR4                  | SBR3  | SBR2  | SBR1          | SBR0  |

|        |                                                                   | Reset:          | 0     | 0          | 0      | 0                     | 0     | 1     | 0             | 0     |

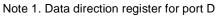

| \$0072 | SCI Control Register 1<br>(SCCR1)<br>See page 160.                | Read:<br>Write: | LOOPS | WOMS       | 0      | М                     | WAKE  | ILT   | PE            | PT    |

|        |                                                                   | Reset:          | U     | U          | 0      | 0                     | 0     | 0     | 0             | 0     |

| \$0073 | SCI Control Register 2<br>(SCCR2)<br>See page 161.                | Read:<br>Write: | TIE   | TCIE       | RIE    | ILIE                  | TE    | RE    | RWU           | SBK   |

|        |                                                                   | Reset:          | 0     | 0          | 0      | 0                     | 0     | 0     | 0             | 0     |

| \$0074 | SCI Status Register 1<br>(SCSR1)                                  | Read:<br>Write: | TDRE  | TC         | RDRF   | IDLE                  | OR    | NF    | FE            | PF    |

|        | See page 162.                                                     | Reset:          | 0     | 0          | 0      | 0                     | 0     | 0     | 0             | 0     |

| \$0075 | SCI Status Register 2<br>(SCSR2)                                  | Read:<br>Write: | 0     | 0          | 0      | 0                     | 0     | 0     | 0             | RAF   |

|        | See page 164.                                                     | Reset:          | 1     | 1          | 0      | 0                     | 0     | 0     | 0             | 0     |

| \$0076 | SCI Data Register<br>(SCDR)                                       | Read:<br>Write: | R8    | Т8         | 0      | 0                     | 0     | 0     | 0             | 0     |

|        | See page 165.                                                     | Reset:          |       |            |        | Undefined after reset |       |       |               |       |

|        |                                                                   |                 |       | = Unimplen | nented | R = Reserved          |       |       | U = Undefined |       |

Figure 4-1. Register and Control Bit Assignments (Sheet 10 of 11)

**Technical Data**

M68HC11K Family

Semiconductor, Inc.

Freescale

### **Operating Modes and On-Chip Memory**

Port B provides the high-order address byte (Addr[15:8]), port F the low-order address byte (Addr[7:0]), port C the data bus (Data[7:0]), and port G pin 7 the read/write line (R/W) which controls direction of data flow.

Additionally, the E clock output can be used to synchronize external decoders for enable signals.

Expanded mode also enables these two special features available only on the K4 Family devices:

- 1. Memory expansion uses port G[5:0] to increase the available external address space to 1 Mbyte.

- 2. Four chip-select lines on port H[7:4] simplify selection of external memory devices.

Both of these features are described in **Section 11. Memory Expansion** and Chip Selects.

#### 4.5.3 Bootstrap Mode

Resetting the MCU in special bootstrap mode selects a reset vector to a special ROM bootloader program at addresses \$BE00–\$BFFF. The bootloader program is used to download code, such as programming algorithms, into on-chip RAM through the SCI. To do this:

- 1. Send a synchronization character (see **Table 4-2**) to the SCI receiver at the specified baud rate.

- Download up to 768 bytes (1 Kbyte for KS2) of program data, which the CPU places into RAM starting at \$0080 and also echoes back on the TxD signal. The bootloader program ends the download after the RAM is full or when the received data line is idle for at least four character times. See Table 4-2.

When loading is complete, the MCU jumps to location \$0080 and begins executing the code. Interrupt vectors are directed to RAM, which allows the use of interrupts through a jump table. The SCI transmitter requires an external pullup resistor since it is part of port D, which the bootloader configures for wired-OR operation.

Technical Data

Operating Modes and On-Chip Memory EEPROM and the CONFIG Register

LVPI — Low-Voltage Programming Inhibit Bit

LVPI is a read-only bit which always reads as 0. The functionality of this status bit was changed from early versions of the M68HC11K Family. The low-voltage programming inhibit function is disabled on all recent devices.

- BYTE Byte/Other EEPROM Erase Mode Bit

- 0 = Row or bulk erase mode used

- 1 = Erase only one byte of EEPROM

- ROW Row/All EEPROM Erase Mode Bit

- 0 = All 640 bytes of EEPROM erased

- 1 = Erase only one 16-byte row of EEPROM

- **NOTE:** ROW is valid only when BYTE = 0.

The BYTE and ROW bits work together to determine the scope of erasing, as shown in **Table 4-8**.

| BYTE | ROW                 | Action                    |

|------|---------------------|---------------------------|

| 0    | 0                   | Bulk erase; all 640 bytes |

| 0    | Row erase; 16 bytes |                           |

| 1    | 0                   | Byte erase                |

| 1    | 1                   | Byte erase                |

Table 4-8. Scope of EEPROM Erase

ERASE — Erase/Normal Control for EEPROM Bit

- 0 = Normal read or program mode

- 1 = Erase mode

- EELAT EEPROM Latch Control Bit

- 0 = EEPROM address and data bus configured for normal reads

- 1 = EEPROM address and data bus configured for programming or erasing

EEPGM — EEPROM Program Command Bit

- 0 = Program or erase voltage switched off to EEPROM array

- 1 = Program or erase voltage switched on to EEPROM array

M68HC11K Family

Operating Modes and On-Chip Memory EEPROM and the CONFIG Register

#### 4.8.2.2 EEPROM Bulk Erase

BULKE

ROWE

| LDAB | #\$06  |                                      |

|------|--------|--------------------------------------|

| STAB | \$003B | Set EELAT and ERASE.                 |

| STAA | \$0,X  | Store any data to any EEPROM address |

| LDAB | #\$07  |                                      |

| STAB | \$002B | Set EEPGM bit as well                |

|      |        | to enable EEPROM programming voltage |

| JSR  | DLY10  | Delay 10 ms                          |

| CLR  | \$003B | Turn off programming voltage and set |

|      |        | to READ mode                         |

#### 4.8.2.3 EEPROM Row Erase

| LDAB | #\$07  |                                      |

|------|--------|--------------------------------------|

| STAB | \$003B | Set EELAT, ERASE and ROW.            |

| STAA | \$0,X  | Store any data to any EEPROM address |

|      |        | in row                               |

| LDAB | #\$07  |                                      |

| STAB | \$002B | Set EEPGM bit as well                |

|      |        | to enable EEPROM programming voltage |

| JSR  | DLY10  | Delay 10 ms                          |

| CLR  | \$003B | Turn off programming voltage and set |

|      |        | to READ mode                         |

#### 4.8.2.4 EEPROM Byte Erase

| BYTEE | LDAB<br>STAB<br>STAA | #\$16<br>\$003B<br>\$0,X | Set EELAT, ERASE and BYTE.<br>Store any data to targeted EEPROM<br>address |

|-------|----------------------|--------------------------|----------------------------------------------------------------------------|

|       | LDAB                 | #\$17                    |                                                                            |

|       | STAB                 | \$002B                   | Set EEPGM bit as well<br>to enable EEPROM programming voltage              |

|       | JSR                  | DLY10                    | Delay 10 ms                                                                |

|       | CLR                  | \$003B                   | Turn off programming voltage and set<br>to READ mode                       |

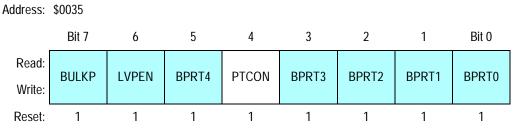

### **Operating Modes and On-Chip Memory**

#### 4.8.3 CONFIG Register Programming

The CONFIG register is implemented with EEPROM cells, so EEPROM procedures are required to change it. CONFIG can be programmed or erased (including byte erase) while the MCU is operating in any mode, provided that PTCON in BPROT is clear.

Figure 4-12. Block Protect Register (BPROT)

PTCON — Protect for CONFIG Bit

0 = CONFIG register can be programmed or erased normally.

1 = CONFIG register cannot be programmed or erased.

To change the value in the CONFIG register, complete this procedure. Do not initiate a reset until the procedure is complete.

- Erase the CONFIG register.

- Program the new value to the CONFIG address.

- Initiate reset.

#### 4.8.4 RAM and EEPROM Security

The NOSEC bit in the CONFIG register enables and disables an optional security feature which protects the contents of EEPROM and RAM from unauthorized access. This is done by restricting operation to single-chip modes, preventing the memory locations from being monitored externally. Single-chip modes do not allow visibility of the internal address and data buses. Resident programs, however, have unlimited access to the internal EEPROM and RAM and can read, write, or transfer the contents of these memories.

Technical Data

M68HC11K Family

MOTOROLA

Semiconductor, Inc

reescale

**Resets and Interrupts**

Three registers are involved in COP operation:

- The CONFIG register contains a bit which determines whether the COP system is enabled or disabled.

- The OPTION register contains two bits which determine the COP timeout period.

- The COPRST register must be written by software to reset the watchdog timer.

- **NOTE:** Throughout this manual, the registers are discussed by function. In the event that not all bits in a register are referenced, the bits that are not discussed are shaded.

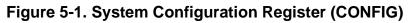

### 5.3.3.1 System Configuration Register

In normal modes, COP is enabled out of reset and does not depend on software action. To disable the COP system, set the NOCOP bit in the CONFIG register (see Figure 5-1). In special test and bootstrap operating modes, the COP system is initially inhibited by the disable resets (DISR) control bit in the TEST1 register. The DISR bit can subsequently be written to 0 to enable COP resets.

**NOTE:** CONFIG is writable once in normal modes and writable at any time in special modes.

NOCOP — COP System Disable Bit

0 = COP enabled

1 = COP disabled

**NOTE:** The slow mode function should not be enabled while using the A/D converter or during an erase/program operation of the EEPROM, unless the internal RC oscillator is turned on.

The clock monitor function should not be used if the resultant E clock will be slower than 200 kHz.

Figure 5-13. Slow Mode Example for M68HC(7)11KS Devices Only

M68HC11K Family

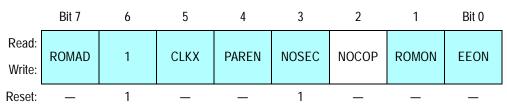

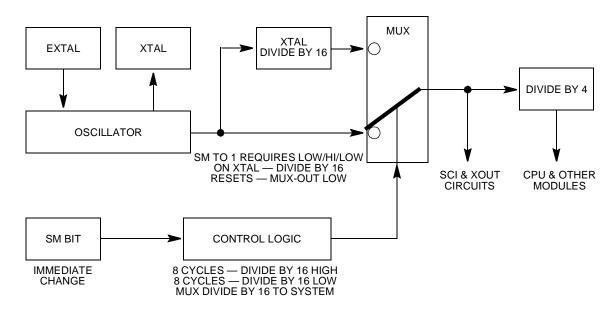

### 6.11 Internal Pullup Resistors

M68HC11KS series devices contain selectable internal pullup resistors for ports B, F, G, and H. The resistors for each port are enabled by setting the corresponding bit in the PPAR register. PPAR itself must be enabled by setting the PAREN bit in the system configuration register (CONFIG). Refer to **Figure 6-17** and **Figure 6-18**.

Address: \$002C

Figure 6-17. Port Pullup Assignment Register (PPAR)

xPPUE — Port x Pin Pullup Enable Bits

Only active when enabled by the PAREN bit in the CONFIG register

- 0 = Port x pin on-chip pullup devices disabled

- 1 = Port x pin on-chip pullup devices enabled

- **NOTE:** FPPUE and BPPUE do not apply in expanded mode because port F and B are address outputs.

Address: \$003F

|                 | Bit 7 | 6 | 5    | 4     | 3     | 2     | 1     | Bit 0 |

|-----------------|-------|---|------|-------|-------|-------|-------|-------|

| Read:<br>Write: | ROMAD | 1 | CLKX | PAREN | NOSEC | NOCOP | ROMON | EEON  |

| Reset:          | _     | 1 | _    | _     | 1     | _     | _     | _     |

Figure 6-18. System Configuration Register (CONFIG)

**NOTE:** CONFIG is writable once in normal modes and writable at any time in special modes.

PAREN — Pullup Assignment Register Enable Bit

- 0 = PPAR register disabled

- 1 = PPAR register enabled; pullups can be enabled through PPAR

M68HC11K Family

Parallel Input/Output

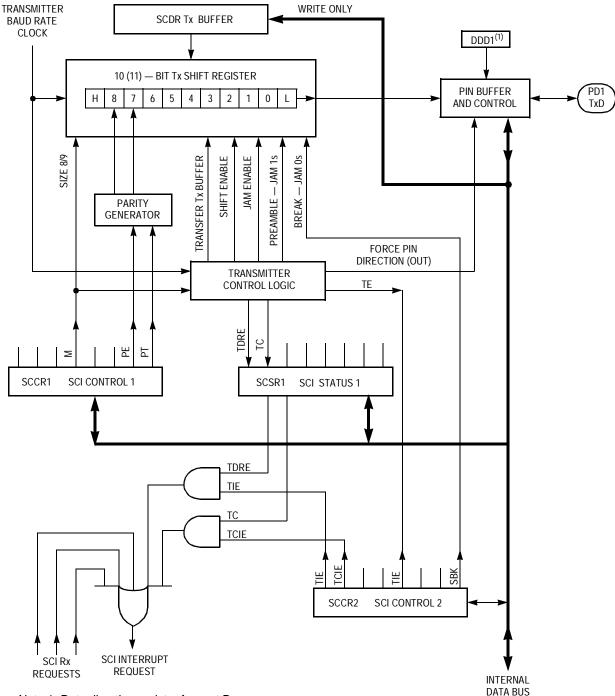

### Serial Communications Interface (SCI)

Technical Data

### Serial Communications Interface (SCI)

#### 7.9.2 Serial Communications Control Register 1

#### Figure 7-7. SCI Control Register 1 (SCCR1)

LOOPS - SCI Loop Mode Enable Bit

Both the transmitter and receiver must be enabled to use the loop mode. When the loop mode is enabled, the TxD pin is driven high (idle line state) if the transmitter is enabled.

- 0 = SCI transmit and receive operate normally.

- 1 = SCI transmit and receive are disconnected from TxD and RxD pins, and transmitter output is fed back into the receiver input.

#### WOMS - Wired-OR Mode for SCI Pins PD[1:0] Bits

See also **8.6.1 Serial Peripheral Control Register** for a description of the DWOM (port D wired-OR mode) bit in the serial peripheral control register (SPCR).

- 0 = TxD and RxD operate normally.

- 1 = TxD and RxD are open drains if operating as outputs.

- M Mode (SCI Word Size) Bit

- 0 =Start bit, 8 data bits, 1 stop bit

- 1 = Start bit, 9 data bits, 1 stop bit

- WAKE Wakeup Mode Bit

- 0 = Wake up by idle line recognition

- 1 = Wake up by address mark (most significant data bit set)

- ILT Idle Line Type Bit

- 0 = Short (SCI counts consecutive 1s after start bit.)

- 1 = Long (SCI counts one only after stop bit.)

#### Serial Peripheral Interface (SPI)

**NOTE:** Throughout this manual, the registers are discussed by function. In the event that not all bits in a register are referenced, the bits that are not discussed are shaded.

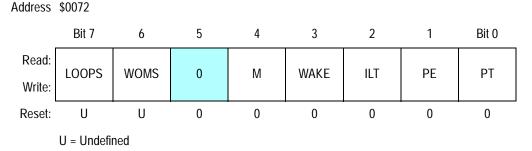

#### 8.6.1 Serial Peripheral Control Register

Address: \$0028

|                 | Bit 7 | 6   | 5    | 4    | 3    | 2    | 1    | Bit 0 |

|-----------------|-------|-----|------|------|------|------|------|-------|

| Read:<br>Write: | SPIE  | SPE | DWOM | MSTR | CPOL | СРНА | SPR1 | SPR2  |

| Reset:          | 0     | 0   | 0    | 0    | 0    | 1    | U    | U     |

U = Undefined

- SPIE Serial Peripheral Interrupt Enable Bit

- 0 = SPI interrupt disabled

- 1 = SPI interrupt is enabled each time the SPIF or MODF status flag in SPSR is set.

- SPE Serial Peripheral System Enable Bit

- 0 = SPI off

- 1 = SPI on PD[5:2] function as SPI signals

- DWOM Port D Wired-OR Mode Bit

DWOM affects only the four SPI pins on port D, PD[5:2]. See also **7.9.2 Serial Communications Control Register 1** for a discussion of the WOMS (wired-OR Mode for SCI pins) bit in the serial communications control register 1 (SCCR1).

- 0 = Normal CMOS outputs

- 1 = Open-drain outputs

- MSTR Master Mode Select Bit

- 0 = Slave mode

- 1 = Master mode

**Technical Data**

M68HC11K Family

Semiconductor, Inc

reescale

Timing System Pulse-Width Modulator (PWM)

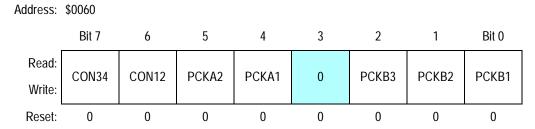

The three clocks are derived from the E clock by writing to registers which determine their scaling factors. The clock A frequency is equal to E divided by 1, 2, 4, or 8, depending on which bits (PCKA[2:1]) in the PWCLK register are set. The clock B frequency is equal to the E clock divided by a power of two determined by bits PCKB[3:1] in the PWCLK register. Clock S is derived by dividing clock A by the integer (1 to 256) stored in the PWSCAL register, then by two.

Two channels can be concatenated by setting the appropriate bit (CON34 or CON12) in the PWCLK register. In this mode, the clock source is determined by the low-order channel, which is channel two in CON12 and channel four in CON34. The output is also placed on the pin associated with the low-order channels, so when two channels are concatenated the pin associated with the high-order channel (PH0 and/or PH2) can be used for GPIO. A read of the high-order byte causes the low-order byte to be latched for one cycle to guarantee that double-byte reads are accurate. A write to the low-order byte of the counter causes reset of the entire counter. A write to the high-order byte

#### 9.9.2 Pulse-Width Modulation Control Registers

The PWM control registers are described here.

9.9.2.1 Pulse-Width Modulation Timer Clock Select Register

Figure 9-31. Pulse-Width Modulation Timer Clock Select (PWCLK)

M68HC11K Family

Timing System

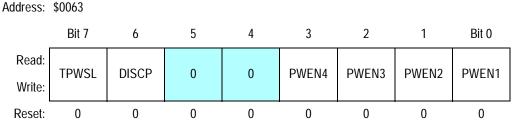

#### 9.9.2.4 Pulse-Width Modulation Timer Enable Register

Figure 9-34. Pulse-Width Modulation Timer Enable Register (PWEN)

TPWSL — PWM Scaled Clock Test Bit — factory use only; only accessible in special test mode

- 0 = Normal operation

- 1 = Clock S is output to PWSCAL register (test only)

DISCP — Disable Compare Scaled E-Clock Bit — factory use only; only accessible in special test mode

- 0 = Normal operation

- 1 = Match of period does not reset associated count register (test only)

PWEN[4:1] — Pulse-Width Enable for Channels [4:1] Bits

- 0 = Channel disabled

- 1 = Channel enabled at port H bits [3:0]

Technical Data

Address: \$0039

|                 | Bit 7 | 6    | 5    | 4                  | 3   | 2    | 1   | Bit 0 |

|-----------------|-------|------|------|--------------------|-----|------|-----|-------|

| Read:<br>Write: | ADPU  | CSEL | IRQE | DLY <sup>(1)</sup> | CME | FCME | CR1 | CR0   |

| Reset:          | 0     | 0    | 0    | 1                  | 0   | 0    | 0   | 0     |

1. DLY can be written only once in the first 64 cycles out of reset in normal modes or at any time in special modes.

#### Figure 10-3. System Configuration Options Register (OPTION)

ADPU — A/D Power-up

- 0 = A/D powered down

- 1 = A/D powered up

CSEL — Clock Select

- 0 = A/D and EEPROM use system E clock.

- 1 = A/D and EEPROM use internal RC clock.

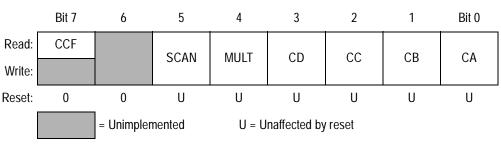

#### 10.4.2 A/D Control/Status Register

All bits in this register can be read or written except bit 7, which is a read-only status indicator, and bit 6, which always reads as 0. Writing to ADCTL initiates a conversion, aborting any conversion in progress.

Address: \$0030

Figure 10-4. Analog-to-Digital Control/Status Register (ADCTL)

Semiconductor, Inc

reescale

### **Memory Expansion and Chip Selects**

### **11.3 Memory Expansion**

The M68HC11K Family devices employ a register-based paging scheme to extend their address range beyond the physical 64-Kbyte limit of the 16 CPU address lines. Pages are selected using the expansion address lines XA[18:13] available on port G. This selection can be facilitated by the chip-select lines on port H, discussed in **11.4 Chip Selects**. The M68HC11KS devices do not provide these features since they lack the required port G and port H lines. Refer to **Figure 1-2. M68HC11KS Family Block Diagram**.

#### 11.3.1 Memory Size and Address Line Allocation

To access expanded memory, the user first allocates portion(s) of the 64 Kbyte address space, or window(s), through which the CPU will view external memory. One or two windows can be designated, and the size of each window can be 0 (disabled), 8, 16, or 32 Kbytes.

Expanded memory is addressed with a combination of the CPU's normal address lines ADDR[15:0] and the expansion address lines XA[18:13]. The expansion address lines select a memory bank, and the CPU's normal address lines select a particular location within the bank. The size of the window(s) and the number of memory banks determine exactly which expansion address lines are used. The port G assignment register (PGAR) controls which port G pins function as expanded address lines. Any port G pins not allocated for memory expansion can serve as general-purpose input/output (GPIO). When a configuration uses any of the lower three expansion address lines XA[15:13] they replace the CPU's equivalent address lines (ADDR[15:13]). Table 11-1 shows how address and expansion lines are allocated for various combinations of memory banks and window size.

**Technical Data**

M68HC11K Family

232

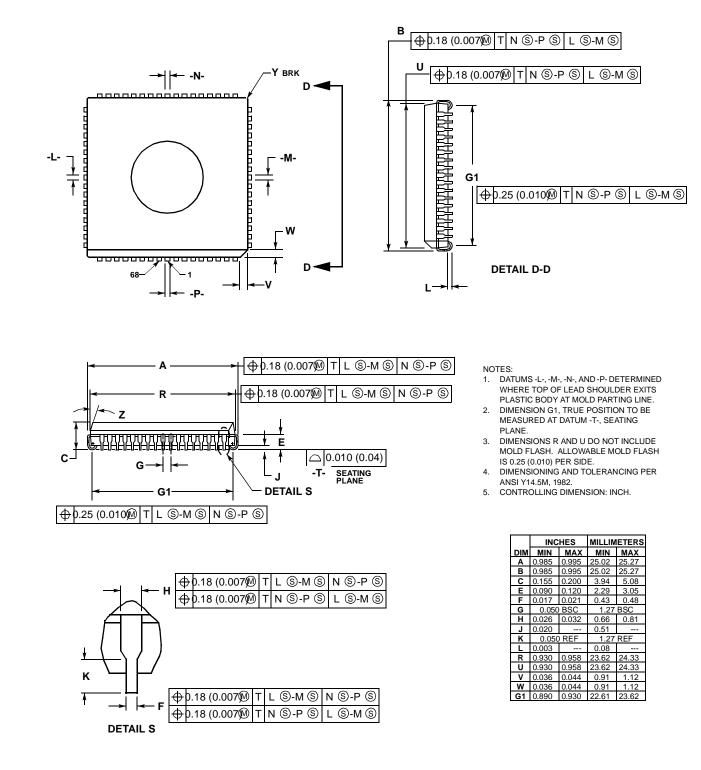

**Mechanical Data**

## 13.8 68-Pin J-Cerquad (Case 779A)

Technical Data

M68HC11K Family

MOTOROLA

**Ordering Information**

Technical Data

M68HC11K Family

MOTOROLA