Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HC11                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 4MHz                                                                    |

| Connectivity               | SCI, SPI                                                                |

| Peripherals                | POR, PWM, WDT                                                           |

| Number of I/O              | 37                                                                      |

| Program Memory Size        | -                                                                       |

| Program Memory Type        | ROMIess                                                                 |

| EEPROM Size                | 640 x 8                                                                 |

| RAM Size                   | 768 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                             |

| Data Converters            | A/D 8x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 80-QFP                                                                  |

| Supplier Device Package    | 80-QFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc11k1cfue4 |

## List of Figures

| Figure |      | e Title                                         | Page |

|--------|------|-------------------------------------------------|------|

|        | 4-13 | System Configuration Register (CONFIG)          | 101  |

|        | 4-14 | System Configuration Register (CONFIG)          | 102  |

|        | 4-15 | System Configuration Options 2 Register (OPT2)  | 103  |

|        | 5-1  | System Configuration Register (CONFIG)          |      |

|        | 5-2  | System Configuration Options Register (OPTION)  |      |

|        | 5-3  | Arm/Reset COP Timer Circuitry Register (COPRST) |      |

|        | 5-4  | System Configuration Options Register (OPTION)  |      |

|        | 5-5  | System Configuration Options Register 2 (OPT2)  |      |

|        | 5-6  | System Configuration Options Register (OPTION)  | 121  |

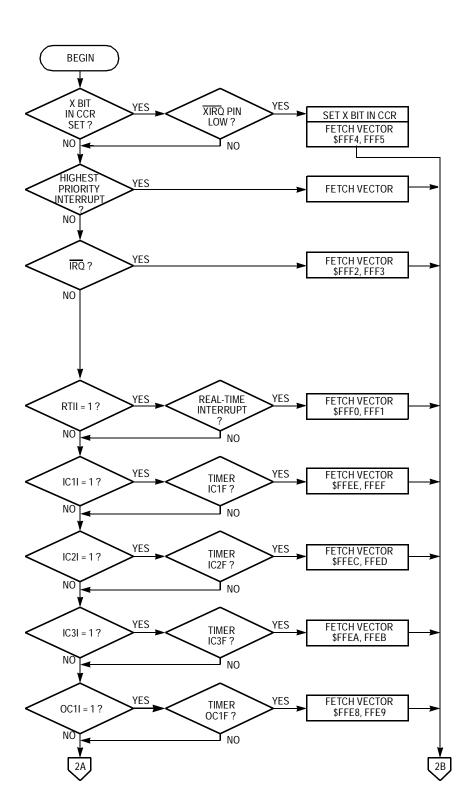

|        | 5-7  | Highest Priority I-Bit Interrupt                |      |

|        |      | and Miscellaneous Register (HPRIO)              |      |

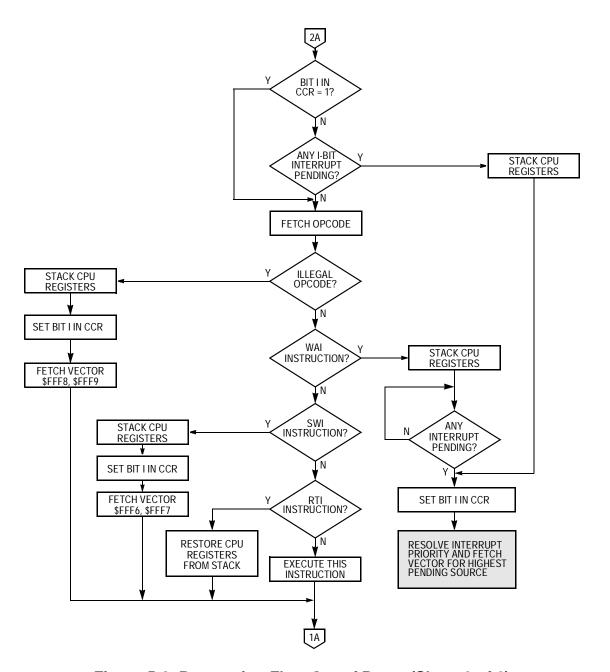

|        | 5-8  | Processing Flow Out of Reset                    |      |

|        | 5-9  | Interrupt Priority Resolution                   |      |

|        | 5-10 | Interrupt Priority Resolution Within SCI System |      |

|        | 5-11 | System Configuration Options Register (OPTION)  |      |

|        | 5-12 | System Configuration Options 3 Register (OPT3)  |      |

|        | 5-13 | Slow Mode Example for M68HC(7)11KS Devices Only | 133  |

|        | 6-1  | Port A Data Register (PORTA)                    | 138  |

|        | 6-2  | Port A Data Direction Register (DDRA)           |      |

|        | 6-3  | Port B Data Register (PORTB)                    |      |

|        | 6-4  | Port B Data Direction Register (DDRB)           |      |

|        | 6-5  | Port C Data Register (PORTC)                    |      |

|        | 6-6  | Port C Data Direction Register (DDRC)           |      |

|        | 6-7  | System Configuration Options 2 Register (OPT2)  |      |

|        | 6-8  | Port D Data Register (PORTD)                    |      |

|        | 6-9  | Port D Data Direction Register (DDRD)           |      |

|        | 6-10 | Port E Data Register (PORTE)                    |      |

|        | 6-11 | Port F Data Register (PORTF)                    |      |

|        | 6-12 | Port F Data Direction Register (DDRF)           |      |

|        | 6-13 | Port G Data Register (PORTG)                    |      |

|        | 6-14 | Port G Data Direction Register (DDRG)           |      |

|        | 6-15 | Port H Data Register (PORTH)                    |      |

|        | 6-16 | Port H Data Direction Register (DDRH)           | 146  |

**Technical Data**

# Freescale Semiconductor, Inc.

## List of Figures

| Figur | e Title                                                                                                                                                                                              | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9-13  | Timer Output Compare                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | Registers (TOC1–TOC4)                                                                                                                                                                                | 197                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-14  | Timer Input Capture 4/Output                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | Compare 5 Register (TI4/O5)                                                                                                                                                                          | 199                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-15  | Timer Interrupt Flag 1 Register (TFLG1)                                                                                                                                                              | 199                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-16  | Timer Interrupt Mask 1 Register (TMSK1)                                                                                                                                                              | 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-17  | Timer Control Register 1 (TCTL1)                                                                                                                                                                     | 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-18  | Timer Compare Force Register (CFORC)                                                                                                                                                                 | 201                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-19  | Output Compare 1 Mask Register (OC1M)                                                                                                                                                                | 202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-20  | Output Compare 1 Data Register (OC1D)                                                                                                                                                                | 202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-21  | Pulse Accumulator                                                                                                                                                                                    | 204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-22  | Port A Data Direction Register (DDRA)                                                                                                                                                                | 205                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-23  | Pulse Accumulator Control Register (PACTL)                                                                                                                                                           | 205                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-24  | Timer Interrupt Flag 2 (TFLG2)                                                                                                                                                                       | 206                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-25  | Timer Interrupt Mask 2 (TMSK2)                                                                                                                                                                       | 207                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-26  | Pulse Accumulator Count Register (PACNT)                                                                                                                                                             | 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-27  | Timer Interrupt Flag 2 Register (TFLG2)                                                                                                                                                              | 209                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-28  | Timer Interrupt Mask 2 Register (TMSK2)                                                                                                                                                              | 209                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-29  | Pulse Accumulator Control Register (PACTL)                                                                                                                                                           | 210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-30  | Pulse-Width Modulation Timer Block Diagram                                                                                                                                                           | 212                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-31  | Pulse-Width Modulation Timer Clock Select (PWCLK)                                                                                                                                                    | 213                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-32  | Pulse-Width Modulation Timer                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | Polarity Register (PWPOL)                                                                                                                                                                            | 215                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-33  | Pulse-Width Modulation Timer                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | •                                                                                                                                                                                                    | 215                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-34  |                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       |                                                                                                                                                                                                      | 216                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-35  |                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       |                                                                                                                                                                                                      | 217                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-36  |                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       |                                                                                                                                                                                                      | 218                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9-37  |                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | Duty Cycle 1 to 4 (PWDTY1 to PWDTY4)                                                                                                                                                                 | 219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

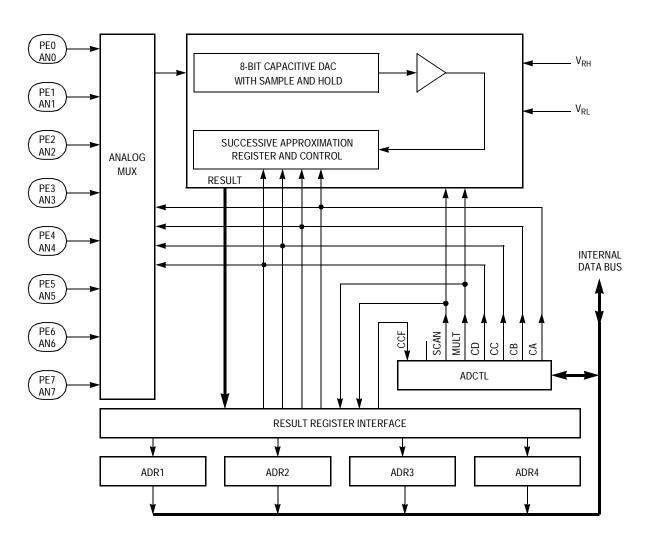

| 10-1  | A/D Converter Block Diagram                                                                                                                                                                          | 222                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10-2  | A/D Conversion Sequence                                                                                                                                                                              | 224                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | M68HC                                                                                                                                                                                                | C11K Family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 9-13<br>9-14<br>9-15<br>9-16<br>9-17<br>9-18<br>9-19<br>9-20<br>9-21<br>9-22<br>9-23<br>9-24<br>9-25<br>9-26<br>9-27<br>9-28<br>9-29<br>9-30<br>9-31<br>9-32<br>9-33<br>9-34<br>9-35<br>9-36<br>9-37 | 9-13 Timer Output Compare Registers (TOC1-TOC4) 9-14 Timer Input Capture 4/Output Compare 5 Register (TI4/O5) 9-15 Timer Interrupt Flag 1 Register (TFLG1) 9-16 Timer Interrupt Mask 1 Register (TMSK1) 9-17 Timer Control Register 1 (TCTL1) 9-18 Timer Compare Force Register (CFORC) 9-19 Output Compare 1 Mask Register (OC1M) 9-20 Output Compare 1 Data Register (OC1D) 9-21 Pulse Accumulator 9-22 Port A Data Direction Register (DDRA) 9-23 Pulse Accumulator Control Register (PACTL) 9-24 Timer Interrupt Flag 2 (TFLG2) 9-25 Timer Interrupt Mask 2 (TMSK2) 9-26 Pulse Accumulator Count Register (PACNT) 9-27 Timer Interrupt Flag 2 Register (TFLG2) 9-28 Timer Interrupt Mask 2 Register (PACTL) 9-30 Pulse-Width Modulation Timer Block Diagram 9-31 Pulse-Width Modulation Timer Block Diagram 9-31 Pulse-Width Modulation Timer Clock Select (PWCLK) 9-33 Pulse-Width Modulation Timer Polarity Register (PWPOL) 9-34 Pulse-Width Modulation Timer Prescaler Register (PWSCAL) 9-35 Pulse-Width Modulation Timer Enable Register (PWEN) 9-36 Pulse-Width Modulation Timer Prescaler Register (PWEN) 9-37 Pulse-Width Modulation Timer Periods 1 to 4 (PWCNT1 to PWCNT4) 9-38 Pulse-Width Modulation Timer Periods 1 to 4 (PWCNT1 to PWCNT4) 9-39 Pulse-Width Modulation Timer Periods 1 to 4 (PWPER1 to PWPER4) 9-37 Pulse-Width Modulation Timer Duty Cycle 1 to 4 (PWDTY1 to PWDTY4) |

## Technical Data — M68HC11K Family

## **Section 2. Pin Description**

### 2.1 Contents

| 2.2  | Introduction                                                                                            |

|------|---------------------------------------------------------------------------------------------------------|

| 2.3  | Power Supply (V <sub>DD</sub> , V <sub>SS</sub> , AV <sub>DD</sub> , and AV <sub>SS</sub> )36           |

| 2.4  | Reset (RESET)                                                                                           |

| 2.5  | Crystal Driver and External Clock Input (XTAL and EXTAL)                                                |

| 2.6  | XOUT38                                                                                                  |

| 2.7  | E-Clock Output (E)                                                                                      |

| 2.8  | Interrupt Request (IRQ) and Non-Maskable Interrupt (XIRQ)                                               |

| 2.9  | Mode Selection, Instruction Cycle Reference, and Standby Power (MODA/LIR and MODB/V <sub>STBY</sub> )39 |

| 2.10 | V <sub>RH</sub> and V <sub>RL</sub> 41                                                                  |

| 2.11 | Port Signals41                                                                                          |

|      |                                                                                                         |

#### 2.2 Introduction

The M68HC11K Family is available in a variety of packages, as shown in **Table 1-1. M68HC11K Family Devices**. Most pins on this MCU serve two or more functions, as described in this section. Pin assignments for the various package types are shown in **Figure 2-1**, **Figure 2-2**, **Figure 2-3**, and **Figure 2-4**.

Pin Description

## **Central Processor Unit (CPU)**

### 3.3.5 Program Counter (PC)

The 16-bit program counter contains the address of the next instruction to be executed. Its initial value after reset is fetched from one of six possible vectors, depending on operating mode and the cause of reset, as described in **5.3 Sources of Resets**.

#### 3.3.6 Condition Code Register (CCR)

This 8-bit register contains:

- Five condition code indicators (C, V, Z, N, and H)

- Two interrupt masking bits (IRQ and XIRQ)

- A stop disable bit (S)

Most instructions update condition codes automatically, as described in the following paragraphs. Certain instructions, such as pushes, pulls, add B to X (ABX), add B to Y (ABY), and transfer/exchange instructions do not affect the condition codes. **Table 3-1** shows which condition codes are affected by each instruction.

#### 3.3.6.1 Carry/Borrow (C)

The C bit is set if the CPU performs a carry or borrow during an arithmetic operation. This bit also acts as an error flag for multiply and divide operations. Shift and rotate instructions operate with and through the carry bit to facilitate multiple-word shift operations.

#### 3.3.6.2 Overflow (V)

The overflow bit is set if an operation results in a two's complement overflow of the 8-bit signed range –128 to +127. Otherwise, the V bit is cleared.

#### 3.3.6.3 Zero (Z)

The Z bit is set if the result of an arithmetic, logic, or data manipulation operation is 0. Otherwise, the Z bit is cleared. Compare instructions do

Operating Modes and On-Chip Memory Control Registers

**NOTE:** Throughout this manual, the registers are discussed by function. In the event that not all bits in a register are referenced, the bits that are not discussed are shaded.

| Addr.  | Register Name                            |                 | Bit 7                 | 6          | 5      | 4         | 3           | 2    | 1           | Bit 0 |

|--------|------------------------------------------|-----------------|-----------------------|------------|--------|-----------|-------------|------|-------------|-------|

| \$0000 | Port A Data Register<br>(PORTA)          | Read:<br>Write: | PA7                   | PA6        | PA5    | PA4       | PA3         | PA2  | PA1         | PA0   |

|        | See page 138.                            | Reset:          |                       | •          | •      | Undefined | after reset |      | •           | •     |

| \$0001 | Port A Data Direction<br>Register (DDRA) | Read:<br>Write: | DDA7                  | DDA6       | DDA5   | DDA4      | DDA3        | DDA2 | DDA1        | DDA0  |

|        | See page 138.                            | Reset:          | 0                     | 0          | 0      | 0         | 0           | 0    | 0           | 0     |

| \$0002 | Port B Data Direction<br>Register (DDRB) | Read:<br>Write: | DDB7                  | DDB6       | DDB5   | DDB4      | DDB3        | DDB2 | DDB1        | DDB0  |

|        | See page 139.                            | Reset:          | 0                     | 0          | 0      | 0         | 0           | 0    | 0           | 0     |

| \$0003 | Port F Data Direction<br>Register (DDRF) | Read:<br>Write: | DDF7                  | DDF6       | DDF5   | DDF4      | DDF3        | DDF2 | DDF1        | DDF0  |

|        | See page 144.                            | Reset:          | 0                     | 0          | 0      | 0         | 0           | 0    | 0           | 0     |

| \$0004 | Port B Data Register<br>(PORTB)          | Read:<br>Write: | PB7                   | PB6        | PB5    | PB4       | PB3         | PB2  | PB1         | PB0   |

|        | See page 139.                            | Reset:          |                       |            |        | Undefined | after reset |      |             |       |

| \$0005 | Port F Data Register<br>(PORTF)          | Read:<br>Write: | PF7                   | PF6        | PF5    | PF4       | PF3         | PF2  | PF1         | PF0   |

|        | See page 144.                            | Reset:          | Undefined after reset |            |        |           |             |      |             |       |

| \$0006 | Port C Data Register<br>(PORTC)          | Read:<br>Write: | PC7                   | PC6        | PC5    | PC4       | PC3         | PC2  | PC1         | PC0   |

|        | See page 140.                            | Reset:          |                       |            |        | Undefined | after reset |      |             |       |

| \$0007 | Port C Data Direction<br>Register (DDRC) | Read:<br>Write: | DDC7                  | DDC6       | DDC5   | DDC4      | DDC3        | DDC2 | DDC1        | DDC0  |

|        | See page 141.                            | Reset:          | 0                     | 0          | 0      | 0         | 0           | 0    | 0           | 0     |

| \$0008 | Port D Data Register<br>(PORTD)          | Read:<br>Write: | 0                     | 0          | PD5    | PD4       | PD3         | PD2  | PD1         | PD0   |

|        | See page 142.                            | Reset:          | 0                     | 0          | U      | U         | U           | U    | U           | U     |

| \$0009 | Port D Data Direction<br>Register (DDRD) | Read:<br>Write: | 0                     | 0          | DDD5   | DDD4      | DDD3        | DDD2 | DDD1        | DDD0  |

|        | See page 142.                            | Reset:          | 0                     | 0          | 0      | 0         | 0           | 0    | 0           | 0     |

|        |                                          |                 |                       | = Unimplen | nented | R         | = Reserved  |      | U = Undefir | ned   |

Figure 4-1. Register and Control Bit Assignments (Sheet 1 of 11)

## **Operating Modes and On-Chip Memory**

Address: \$003F Bit 7 6 5 3 2 1 Bit 0 4 Read: CLKX **PAREN NOSEC NOCOP ROMON EEON ROMAD** 1 Write: Reset:

Figure 4-6. System Configuration Register (CONFIG)

**NOTE:** CONFIG is writable once in normal modes and writable at any time in special modes.

ROMAD — ROM Address Mapping Control Bit

Set out of reset in single-chip mode

0 = (EP)ROM set at \$2000-\$7FFF;

\$0000-\$7FFF in [7]11KS2;

\$0000-\$BFFF in [7]11KS8

(expanded mode only)

1 = (EP)ROM set at \$A000-\$FFFF;

\$8000-\$FFFF in [7]11KS2;

\$4000-\$FFFF in [7]11KS8

ROMON — ROM/PROM Enable Bit

Set by reset in single-chip mode; cleared by reset in special test mode

0 = (EP)ROM removed from the memory map

1 = (EP)ROM present in the memory map

EEON — EEPROM Enable Bit

0 = 640-byte EEPROM disabled

1 = 640-byte EEPROM enabled

Operating Modes and On-Chip Memory EEPROM and the CONFIG Register

#### 4.8.2.2 EEPROM Bulk Erase

| BULKE | LDAB | #\$06  |                                      |

|-------|------|--------|--------------------------------------|

|       | STAB | \$003B | Set EELAT and ERASE.                 |

|       | STAA | \$0,X  | Store any data to any EEPROM address |

|       | LDAB | #\$07  |                                      |

|       | STAB | \$002B | Set EEPGM bit as well                |

|       |      |        | to enable EEPROM programming voltage |

|       | JSR  | DLY10  | Delay 10 ms                          |

|       | CLR  | \$003B | Turn off programming voltage and set |

|       |      |        | to READ mode                         |

#### 4.8.2.3 EEPROM Row Erase

| DOME | TDND | # ¢ 0.7 |                                      |

|------|------|---------|--------------------------------------|

| ROWE | LDAB | #\$07   |                                      |

|      | STAB | \$003B  | Set EELAT, ERASE and ROW.            |

|      | STAA | \$0,X   | Store any data to any EEPROM address |

|      |      |         | in row                               |

|      | LDAB | #\$07   |                                      |

|      | STAB | \$002B  | Set EEPGM bit as well                |

|      |      |         | to enable EEPROM programming voltage |

|      | JSR  | DLY10   | Delay 10 ms                          |

|      | CLR  | \$003B  | Turn off programming voltage and set |

|      |      |         | to READ mode                         |

#### 4.8.2.4 EEPROM Byte Erase

| BYTEE | LDAB<br>STAB<br>STAA | #\$16<br>\$003B<br>\$0,X | Set EELAT, ERASE and BYTE. Store any data to targeted EEPROM |

|-------|----------------------|--------------------------|--------------------------------------------------------------|

|       | SIAA                 | ŞU,Δ                     | Store any data to targeted EEPROM                            |

|       |                      |                          | address                                                      |

|       | LDAB                 | #\$17                    |                                                              |

|       | STAB                 | \$002B                   | Set EEPGM bit as well                                        |

|       |                      |                          | to enable EEPROM programming voltage                         |

|       | JSR                  | DLY10                    | Delay 10 ms                                                  |

|       | CLR                  | \$003B                   | Turn off programming voltage and set                         |

|       |                      |                          | to READ mode                                                 |

## Resets and Interrupts

- All nine timer interrupts are disabled because their mask bits have been cleared.

- The I4/O5 bit in the PACTL register is cleared to configure the I4/O5 function as OC5; however, the OM5:OL5 control bits in the TCTL1 register are clear so OC5 does not control the PA3 pin.

- Real-time interrupt (RTI)

- The RTI enable bit in TMSK2 is cleared, masking automatic hardware interrupts.

- The rate control bits are cleared after reset and can be initialized by software before the RTI system is enabled.

- Pulse accumulator

- The pulse accumulator system is disabled at reset.

- The PAI input pin defaults to a general-purpose input pin (PA7).

- Computer operating properly (COP) watchdog system

- The COP watchdog system is enabled if the NOCOP control bit in the CONFIG register is clear and disabled if NOCOP is set.

- The OPTION register's CR[1:0] bits are cleared, setting the COP rate for the shortest duration timeout.

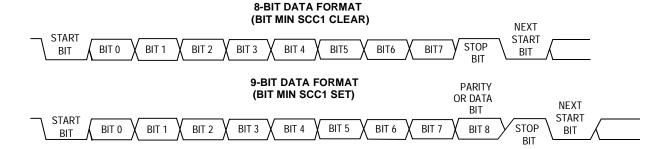

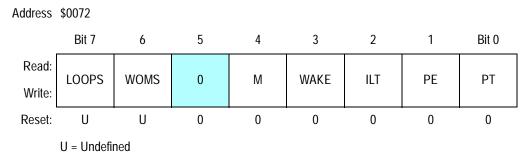

- Serial communications interface (SCI)