Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | HC11                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 2MHz                                                                 |

| Connectivity               | SCI, SPI                                                             |

| Peripherals                | POR, PWM, WDT                                                        |

| Number of I/O              | 62                                                                   |

| Program Memory Size        | 24KB (24K x 8)                                                       |

| Program Memory Type        | OTP                                                                  |

| EEPROM Size                | 640 x 8                                                              |

| RAM Size                   | 768 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                          |

| Data Converters            | A/D 8x8b                                                             |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 84-LCC (J-Lead)                                                      |

| Supplier Device Package    | 84-PLCC (29.29x29.29)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc711k4cfne2 |

|                            |                                                                      |

# MC68HC11K Family

### **Technical Data**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Motorola and

are registered trademarks of Motorola, Inc.

DigitalDNA is a trademark of Motorola, Inc.

© Motorola, Inc., 2001

**Table of Contents**

| 11.4 Chip Selects                                                                                                       | .238  |

|-------------------------------------------------------------------------------------------------------------------------|-------|

| 11.4.1 Program Chip Select                                                                                              |       |

| 11.4.2 Input/Output Chip Select                                                                                         |       |

| 11.4.3 General-Purpose Chip Selects                                                                                     |       |

| <ul><li>11.4.3.1 Memory Mapping Size Register</li><li>11.4.3.2 General-Purpose Chip Select 1 Address Register</li></ul> |       |

| 11.4.3.3 General-Purpose Chip Select 1 Control Register                                                                 |       |

| 11.4.3.4 General-Purpose Chip Select 2 Address Register                                                                 |       |

| 11.4.3.5 General-Purpose Chip Select 2 Control Register                                                                 |       |

| 11.4.4 One Chip Select Driving Another                                                                                  |       |

| 11.4.4.1 General-Purpose Chip Select 1 Control Register                                                                 |       |

| 11.4.4.2 General-Purpose Chip Select 2 Control Register                                                                 |       |

| 11.4.5 Clock Stretching                                                                                                 |       |

| 11.5 Memory Expansion Examples                                                                                          | .249  |

| Coation 42 Floatnical Characteristics                                                                                   |       |

| Section 12. Electrical Characteristics                                                                                  |       |

| 12.1 Contents                                                                                                           | .253  |

| 12.2 Introduction                                                                                                       | .254  |

| 12.3 Maximum Ratings for Standard Devices                                                                               | . 254 |

| 12.4 Functional Operating Range                                                                                         | .255  |

| 12.5 Thermal Characteristics                                                                                            | .255  |

| 12.6 Electrical Characteristics                                                                                         | .256  |

| 12.7 Power Dissipation Characteristics                                                                                  | . 257 |

| 12.8 Control Timing                                                                                                     | .259  |

| 12.9 Peripheral Port Timing                                                                                             | .263  |

| 12.10 Analog-to-Digital Converter Characteristics                                                                       | .265  |

| 12.11 Expansion Bus Timing                                                                                              | .267  |

| 12.12 Serial Peripheral Interface Timing                                                                                | .269  |

| 12.13 EEPROM Characteristics                                                                                            | 272   |

List of Figures

| Figur | e Title                                                  | Page |

|-------|----------------------------------------------------------|------|

| 6-17  | Port Pullup Assignment Register (PPAR)                   | 147  |

| 6-18  | System Configuration Register (CONFIG)                   | 147  |

| 7-1   | SCI Data Formats                                         |      |

| 7-2   | SCI Transmitter Block Diagram                            | 152  |

| 7-3   | SCI Receiver Block Diagram                               | 155  |

| 7-4   | SCI Baud Generator Circuit Diagram                       | 157  |

| 7-5   | SCI Baud Rate Control Register High (SCBDH)              | 158  |

| 7-6   | SCI Baud Rate Control Register Low (SCBDL)               | 158  |

| 7-7   | SCI Control Register 1 (SCCR1)                           | 160  |

| 7-8   | SCI Control Register 2 (SCCR2)                           | 161  |

| 7-9   | SCI Status Register 1 (SCSR1)                            | 162  |

| 7-10  | SCI Status Register 2 (SCSR2)                            | 164  |

| 7-11  | SCI Data Register (SCDR)                                 | 165  |

| 8-1   | SPI Block Diagram                                        | 169  |

| 8-2   | Data Clock Timing Diagram                                | 171  |

| 8-3   | Serial Peripheral Control Register (SPCR)                | 174  |

| 8-4   | Serial Peripheral Status Register (SPSR)                 | 176  |

| 8-5   | Serial Peripheral Data Register (SPDR)                   | 177  |

| 8-6   | Port D Data Direction Register (DDRD)                    | 178  |

| 8-7   | System Configuration Options 2 Register (OPT2)           | 179  |

| 9-1   | Timer Clock Divider Chains                               | 183  |

| 9-2   | Capture/Compare Block Diagram                            | 187  |

| 9-3   | Timer Counter Register (TCNT)                            | 188  |

| 9-4   | Timer Interrupt Flag 2 (TFLG2)                           | 189  |

| 9-5   | Timer Interrupt Mask 2 (TMSK2)                           | 189  |

| 9-6   | Port A Data Direction Register (DDRA)                    | 190  |

| 9-7   | Pulse Accumulator Control Register (PACTL)               | 191  |

| 9-8   | Timer Input Capture Registers (TIC1–TIC3)                | 192  |

| 9-9   | Timer Input Capture 4/Output Compare 5 Register (TI4/O5) | 103  |

| 9-10  | Timer Interrupt Flag 1 Register (TFLG1)                  |      |

| 9-10  | Timer Interrupt Mask 1 Register (TMSK1)                  |      |

| 9-12  | Timer Control 2 Register (TCTL2)                         |      |

| J-12  | Timor Control 2 Register (TOTL2)                         | 133  |

MOTOROLA

General Description Structure

#### 1.5 Structure

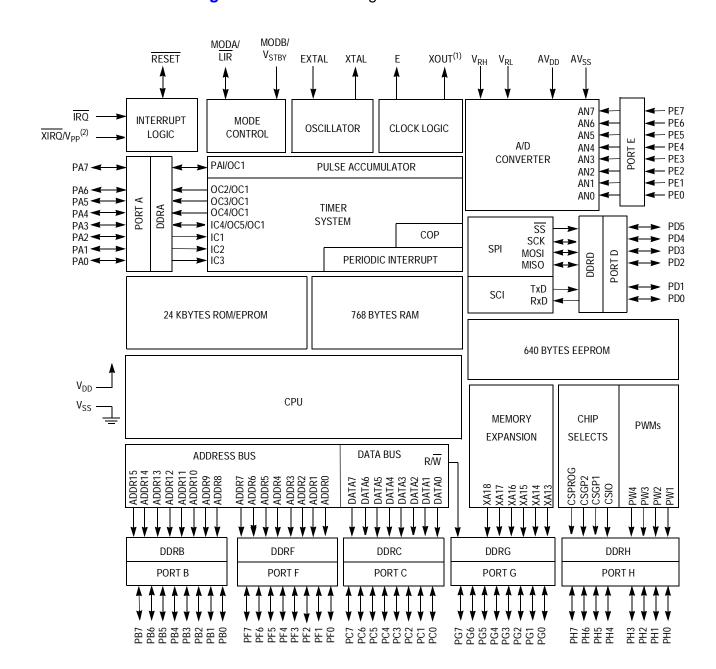

**Figure 1-1** is a block diagram of the M68HC11K Family MCU. **Figure 1-2** is a block diagram of the M68HC11KS devices.

#### Notes:

- 1. XOUT pin omitted on 80-pin QFP

- 2. V<sub>PP</sub> applies only to EPROM devices.

Figure 1-1. M68HC11K4 Family Block Diagram

Pin Description

Central Processor Unit (CPU) Instruction Set

Table 3-1. Instruction Set (Sheet 6 of 7)

|            |                               | B                                      | Addressing                                    | li                               | nstruction                    |                       |   |          | Co | nditio | n Coc | les |   |   |

|------------|-------------------------------|----------------------------------------|-----------------------------------------------|----------------------------------|-------------------------------|-----------------------|---|----------|----|--------|-------|-----|---|---|

| Mnemonic   | Operation                     | Description                            | Mode                                          | Opcode                           | Operand                       | Cycles                | S | Х        | Н  | ı      | N     | Z   | V | С |

| SBA        | Subtract B from               | $A - B \Rightarrow A$                  | INH                                           | 10                               | <u> </u>                      | 2                     | _ | _        | _  | _      | Δ     | Δ   | Δ | Δ |

| SBCA (opr) | A Subtract with Carry from A  | $A - M - C \Rightarrow A$              | A IMM<br>A DIR<br>A EXT<br>A IND,X            | 82<br>92<br>B2<br>A2             | ii<br>dd<br>hh II<br>ff       | 2<br>3<br>4<br>4      | _ | _        | _  | _      | Δ     | Δ   | Δ | Δ |

| SBCB (opr) | Subtract with<br>Carry from B | $B - M - C \Rightarrow B$              | A IND,Y B IMM B DIR B EXT B IND,X             | 18 A2 C2 D2 F2 E2                | ff<br>ii<br>dd<br>hh II<br>ff | 5<br>2<br>3<br>4<br>4 | _ | _        | _  | _      | Δ     | Δ   | Δ | Δ |

| SEC        | Cat Carmi                     | 1 ⇒ C                                  | B IND,Y                                       | 18 E2 0D                         | ff                            | 5 2                   |   |          |    |        |       |     |   |   |

| SEI        | Set Carry Set Interrupt Mask  | 1 ⇒ l                                  | INH                                           | 0F                               | _                             | 2                     | = | _        | _  | 1      | =     | _   | = | 1 |

| SEV        | Set Overflow<br>Flag          | 1 ⇒ V                                  | INH                                           | 0B                               | _                             | 2                     | - | _        | _  | _      | -     | _   | 1 | _ |

| STAA (opr) | Store<br>Accumulator<br>A     | $A \Rightarrow M$                      | A DIR<br>A EXT<br>A IND,X<br>A IND,Y          | 97<br>B7<br>A7<br>18 A7          | dd<br>hh II<br>ff             | 3<br>4<br>4<br>5      | _ | _        | _  | _      | Δ     | Δ   | 0 | _ |

| STAB (opr) | Store<br>Accumulator<br>B     | $B \Rightarrow M$                      | B DIR B EXT B IND,X B IND,Y                   | D7<br>F7<br>E7<br>18 E7          | dd<br>hh II<br>ff             | 3<br>4<br>4<br>5      | _ | _        | _  | _      | Δ     | Δ   | 0 |   |

| STD (opr)  | Store<br>Accumulator<br>D     | $A \Rightarrow M, B \Rightarrow M + 1$ | DIR<br>EXT<br>IND,X<br>IND,Y                  | DD FD ED 18 ED                   | dd<br>hh II<br>ff             | 4<br>5<br>5<br>6      | _ | _        | _  | _      | Δ     | Δ   | 0 |   |

| STOP       | Stop Internal<br>Clocks       | _                                      | INH                                           | CF                               | _                             | 2                     | - | _        | _  | _      | _     | _   | _ | _ |

| STS (opr)  | Store Stack<br>Pointer        | SP ⇒ M : M + 1                         | DIR<br>EXT<br>IND,X<br>IND,Y                  | 9F<br>BF<br>AF<br>18 AF          | dd<br>hh II<br>ff             | 4<br>5<br>5<br>6      | _ | _        | _  | _      | Δ     | Δ   | 0 | _ |

| STX (opr)  | Store Index<br>Register X     | IX ⇒ M : M + 1                         | DIR<br>EXT<br>IND,X<br>IND,Y                  | DF<br>FF<br>EF<br>CD EF          | dd<br>hh II<br>ff             | 4<br>5<br>5<br>6      | _ | _        | _  | _      | Δ     | Δ   | 0 | _ |

| STY (opr)  | Store Index<br>Register Y     | IY ⇒ M : M + 1                         | DIR<br>EXT<br>IND,X<br>IND,Y                  | 18 DF<br>18 FF<br>1A EF<br>18 EF | dd<br>hh II<br>ff             | 5<br>6<br>6           | _ | _        | _  | _      | Δ     | Δ   | 0 | _ |

| SUBA (opr) | Subtract<br>Memory from<br>A  | $A-M\RightarrowA$                      | A IMM<br>A DIR<br>A EXT<br>A IND,X<br>A IND,Y | 80<br>90<br>B0<br>A0<br>18 A0    | ii<br>dd<br>hh II<br>ff       | 2<br>3<br>4<br>4<br>5 | _ | _        | _  | _      | Δ     | Δ   | Δ | Δ |

| SUBB (opr) | Subtract<br>Memory from<br>B  | $B - M \Rightarrow B$                  | A IMM A DIR A EXT A IND,X A IND,Y             | C0<br>D0<br>F0<br>E0<br>18 E0    | ii<br>dd<br>hh II<br>ff       | 2<br>3<br>4<br>4<br>5 | _ | _        | _  | _      | Δ     | Δ   | Δ | Δ |

| SUBD (opr) | Subtract<br>Memory from<br>D  | D − M : M + 1 ⇒ D                      | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y           | 83<br>93<br>B3<br>A3<br>18 A3    | jj kk<br>dd<br>hh II<br>ff    | 4<br>5<br>6<br>6<br>7 | _ | _        | _  | _      | Δ     | Δ   | Δ | Δ |

| SWI        | Software<br>Interrupt         | See Figure 3-2                         | INH                                           | 3F                               | _                             | 14                    | - | _        | _  | 1      | _     | _   | _ | _ |

| TAB        | Transfer A to B               | $A \Rightarrow B$                      | INH                                           | 16                               | _                             | 2                     |   |          |    |        | Δ     | Δ   | 0 | _ |

| TAP        | Transfer A to CC Register     | A ⇒ CCR                                | INH                                           | 06                               | _                             | 2                     | Δ | <b>\</b> | Δ  | Δ      | Δ     | Δ   | Δ | Δ |

| TBA        | Transfer B to A               | $B \Rightarrow A$                      | INH                                           | 17                               | _                             | 2                     |   | _        | _  | _      | Δ     | Δ   | 0 | _ |

| TEST       | TEST (Only in<br>Test Modes)  | Address Bus Counts                     | INH                                           | 00                               | _                             | *                     | - | _        | _  | _      | _     | _   | _ | _ |

Semiconductor, Inc

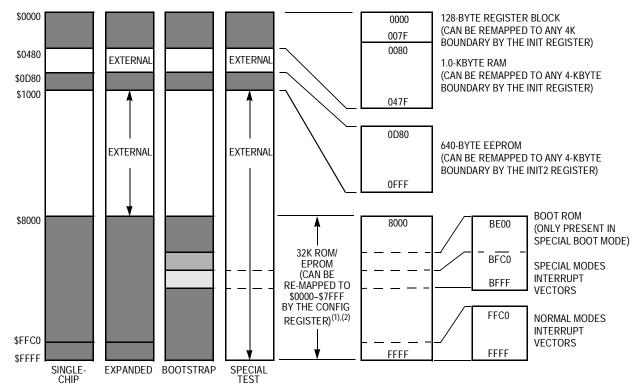

### 4.5 Operating Modes

The two normal modes of operation in the M68HC11K Family are:

- Single-chip mode All port pins available for input/output (I/O); only on-board memory accessible

- Expanded mode Access to internal and external memory; 25

I/O pins used for interface

The two special modes of operation are:

- Bootstrap mode A variation of single-chip mode; executes a bootloader program in an internal bootstrap read-only memory (ROM)

- Test mode A variation of the expanded mode used in production testing; allows privileged access to internal resources

The logic levels applied at reset to input pins MODA and MODB determine the operating mode. See **4.5.5 Mode Selection**.

### 4.5.1 Single-Chip Mode

In single-chip mode, the MCU functions as a self-contained microcontroller. In this mode, all address and data activity occurs within the MCU. Ports B, C, F, G, and H are available for general-purpose I/O because the external address and data buses are not required.

#### 4.5.2 Expanded Mode

In expanded mode, the MCU uses ports B, C, F, and G to access a 64-Kbyte address space. This includes:

- The same on-chip memory addresses used in single-chip mode

- External memory

- Peripheral devices

M68HC11K Family

Technical Data

Operating Modes and On-Chip Memory Memory Map

Note: 1.EPROM can be enabled in special test mode by setting the ROMON bit in the CONFIG register after reset.

Figure 4-4. M68HC11KS2 Family Memory Map

**Table 4-4** shows the default memory map addresses for the M68HC11K Family devices.

**Table 4-4. Default Memory Map Addresses**

|           | [7]11K4       | [7]11KS2      |

|-----------|---------------|---------------|

| Registers | \$0000-\$007F | \$0000-\$007F |

| RAM       | \$0080-\$037F | \$0080-\$047F |

| EEPROM    | \$0D80-\$0FFF | \$0D80-\$0FFF |

| ROM/EPROM | \$A000-\$FFFF | \$8000-\$FFFF |

Operating Modes and On-Chip Memory Map

**Table 4-5. RAM Mapping**

| RAM[3:0] | Address <sup>(1)</sup>       | Address <sup>(2)</sup> |

|----------|------------------------------|------------------------|

| 0000     | \$0080-\$037F <sup>(3)</sup> | \$0000-\$02FF          |

| 0001     | \$1080-\$137F                | \$1000-\$12FF          |

| 0010     | \$2080-\$237F                | \$2000-\$22FF          |

| 0011     | \$3080-\$337F                | \$3000-\$32FF          |

| 0100     | \$4080–\$437F                | \$4000-\$42FF          |

| 0101     | \$5080-\$537F                | \$5000-\$52FF          |

| 0110     | \$6080-\$637F                | \$6000-\$62FF          |

| 0111     | \$7080-\$737F                | \$7000-\$72FF          |

| 1000     | \$8080-\$837F                | \$8000-\$82FF          |

| 1001     | \$9080-\$937F                | \$9000-\$92FF          |

| 1010     | \$A080-\$A37F                | \$A000-\$A2FF          |

| 1011     | \$B080-\$B37F                | \$B000-\$B2FF          |

| 1100     | \$C080-\$C37F                | \$C000-\$C2FF          |

| 1101     | \$D080-\$D37F                | \$D000-\$D2FF          |

| 1110     | \$E080-\$E37F                | \$E000-\$E2FF          |

| 1111     | \$F080-\$F37F                | \$F000-\$F2FF          |

<sup>1.</sup> RAM[3:0] = REG[3:0]: On the [7]11KS2, RAM address range is \$x080-\$x47F.

<sup>2.</sup>  $RAM[3:0] \neq REG[3:0]$ : On the [7]11KS2, RAM address range is \$x000-\$x37F.

<sup>3.</sup> Default locations out of reset

### **Operating Modes and On-Chip Memory**

#### ELAT — EPROM Latch Control Bit

Setting ELAT latches the address and data of writes to the EPROM. The EPROM cannot be read. ELAT can be read at any time. ELAT can be written any time except when PGM = 1, which disables writes to ELAT.

- 0 = EPROM address and data bus configured for normal reads. EPROM cannot be programmed.

- 1 = EPROM address and data bus are configured for programming. Address and data of writes to EPROM are latched. EPROM cannot be read.

#### EXCOL — Select Extra Columns Bit

EXCOL is for factory use only and is accessible only in special test mode. When EXCOL equals 1, extra columns can be accessed at bit 7 and bit 0. Addresses use bits [11:5]. Bits [4:1] are ignored.

- 0 = User array selected

- 1 = Extra columns selected and user array disabled

#### EXROW — Select Extra Rows Bit

EXROW is for factory use only and is only accessible in special test mode. When EXROW equals 1, two extra rows are available. Addresses use bits [5:0]. Bits [11:6] are ignored.

- 0 = User array selected

- 1 = Extra rows selected and user array is disabled

#### EPGM — EPROM Programming Enable Bit

EPGM applies programming voltage ( $V_{PP}$ ) to the EPROM. EPGM can be read at any time. EPGM can be written only when ELAT = 1.

- 0 = Programming voltage to EPROM array is disconnected

- 1 = Programming voltage to EPROM array is connected; ELAT cannot be changed.

Operating Modes and On-Chip Memory EEPROM and the CONFIG Register

This procedure programs one byte into EPROM. On entry, accumulator A contains the byte of data to be programmed and X contains the target EPROM address.

```

EPROG LDAB #$20

STAB $002B Set ELAT bit to enable EPROM latches.

(EPGM must be 0.)

STAA $0,X Store data to EPROM address

LDAB #$21

STAB $002B Set EPGM bit with ELAT=1

to enable EPROM programming voltage

JSR DLYEP Delay 1-2 ms

CLR $002B Turn off programming voltage and set to READ mode

```

### 4.8 EEPROM and the CONFIG Register

The 640-byte on-board EEPROM is enabled by the EEON bit in the CONFIG register and located on a 4-K boundary determined by the INIT2 register (4.6.3 EEPROM). An internal charge pump supplies the programming voltage for the EEPROM, eliminating the need for an external high-voltage supply.

When appropriate bits in the BPROT register are cleared, the PPROG register controls programming and erasing the EEPROM. The PPROG register can be read or written at any time, but logic enforces defined programming and erasing sequences to prevent unintentional changes to EEPROM data. When the EELAT bit in the PPROG register is cleared, the EEPROM can be read as if it were a ROM.

The clock source driving the charge pump is software selectable. When the clock select (CSEL) bit in the OPTION register is 0, the E clock is used; when CSEL is 1, an on-chip resistor-capacitor (RC) oscillator is used.

The EEPROM programming voltage power supply voltage to the EEPROM array is not enabled until there has been a write to PPROG with EELAT set and PGM cleared. This must be followed by a write to a valid EEPROM location or to the CONFIG address, and then a write to PPROG with both the EELAT and EPGM bits set. Any attempt to set

**Operating Modes and On-Chip Memory**

### Technical Data — M68HC11K Family

# **Section 5. Resets and Interrupts**

#### 5.1 Contents

| 5.2 Introduction                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.3Sources of Resets1065.3.1Power-On Reset (POR)1075.3.2External Reset (RESET)1075.3.3Computer Operating Properly (COP) System1075.3.3.1System Configuration Register1085.3.3.2System Configuration Options Register1095.3.3.3Arm/Reset COP Timer Circuitry Register1105.3.4Clock Monitor Reset1105.3.4.1System Configuration Options Register111 |

| <ul><li>5.3.4.1 System Configuration Options Register</li></ul>                                                                                                                                                                                                                                                                                   |

| 5.4 Effects of Reset                                                                                                                                                                                                                                                                                                                              |

| 5.5       Interrupts.       .117         5.5.1       Non-Maskable Interrupts       .120         5.5.1.1       Non-Maskable Interrupt Request (XIRQ)       .120         5.5.1.2       Illegal Opcode Trap       .120         5.5.1.3       Software Interrupt (SWI)       .121         5.5.2       Maskable Interrupts       .121                  |

| 5.6 Reset and Interrupt Priority122                                                                                                                                                                                                                                                                                                               |

| 5.7 Reset and Interrupt Processing123                                                                                                                                                                                                                                                                                                             |

| 5.8       Low-Power Operation       129         5.8.1       Wait Mode       130         5.8.2       Stop Mode       130         5.8.3       Slow Mode       132                                                                                                                                                                                   |

### Resets and Interrupts

#### 5.3.3.3 Arm/Reset COP Timer Circuitry Register

Address: \$003A Bit 7 6 5 4 3 2 1 Bit 0 Read: Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Write: Reset: 0

Figure 5-3. Arm/Reset COP Timer Circuitry Register (COPRST)

To prevent a COP reset, this sequence must be completed:

- 1. Write \$55 to COPRST to arm the COP timer clearing mechanism.

- 2. Write \$AA to COPRST to clear the COP timer.

**NOTE:** Performing instructions between these two steps is possible as long as both steps are completed in the correct sequence before the timer times out.

#### 5.3.4 Clock Monitor Reset

The clock monitor can serve as a backup for the COP system. Its circuit is based on an internal RC time delay. If no MCU clock edges are detected within this RC time delay, the clock monitor generates a system reset. Because the COP needs a clock to function, it is disabled when the clocks stop. Thus, the clock monitor system can detect clock failures not detected by the COP system.

### **Resets and Interrupts**

Figure 5-8. Processing Flow Out of Reset (Sheet 2 of 2)

## Parallel Input/Output

#### 6.3 Port A

Semiconductor, Inc.

Port A provides the I/O lines for the timer functions and pulse accumulator. The eight port A bits (PA[7:0]) are configured as high-impedance general-purpose inputs out of reset. Writes to DDRA can change any of the bits to outputs. Writes to timer registers enable the various timer functions (see Section 9. Timing System).

| Address:                | \$0000                |     |     |     |         |     |     |       |

|-------------------------|-----------------------|-----|-----|-----|---------|-----|-----|-------|

|                         | Bit 7                 | 6   | 5   | 4   | 3       | 2   | 1   | Bit 0 |

| Read:<br>Write:         | PA7                   | PA6 | PA5 | PA4 | PA3     | PA2 | PA1 | PA0   |

| Reset:                  | Undefined after reset |     |     |     |         |     |     |       |

| Alternate Pin Function: | PAI                   | OC2 | OC3 | OC4 | IC4/OC5 | IC1 | IC2 | IC3   |

| And/or:                 | OC1                   | OC1 | OC1 | OC1 | OC1     | _   | _   | _     |

Figure 6-1. Port A Data Register (PORTA)

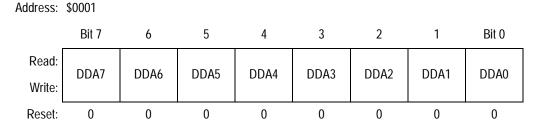

Figure 6-2. Port A Data Direction Register (DDRA)

DDA[7:0] — Data Direction for Port A Bits 0 = Input1 = Output

### **Timing System**

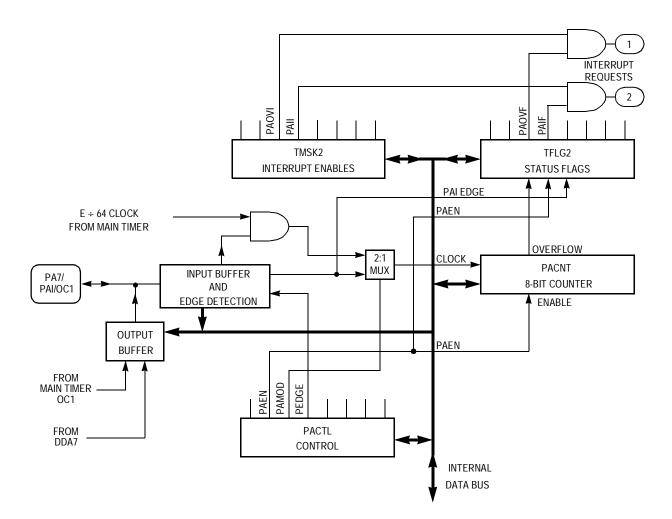

Figure 9-21. Pulse Accumulator

Registers involved in pulse accumulator operation include:

- Data direction register A (DDRA)

- Pulse accumulator control register (PACTL)

- Timer interrupt mask 2 register (TMSK2)

- Timer interrupt flag 2 (TFLG2)

- Pulse accumulator count register (PACNT)

Technical Data M68HC11K Family

Go to: www.freescale.com

**Timing System**

### **Memory Expansion and Chip Selects**

#### 11.4.3.3 General-Purpose Chip Select 1 Control Register

Address: \$005D 3 Bit 0 Bit 7 6 5 4 2 1 Read: G1DPC G1DG2 G1POL G1AV G1SZA G1SZB G1SCC G1SZD Write: Reset: 0 0 0 0 0

Figure 11-9. General-Purpose Chip Select 1

Control Register (GPCS1C)

G1POL — General-Purpose Chip Select 1 Polarity Select Bit

0 = CSGP1 active low

1 = CSGP1 active high

G1AV — General-Purpose Chip Select 1 Address Valid Select Bit

0 = CSGP1 is valid during E high time.

1 = CSGP1 is valid during address valid time.

G1SZ[A:D] — General-Purpose Chip Select 1 Size Bits

They select the range of GPCS1. Refer to Table 11-6.

Table 11-6. General-Purpose Chip Select 1 Size Control

| G1SZ[A:D] | Size (Bytes)     | Valid Bits<br>(MXGS1 = 0) | Valid Bits<br>(MXGS1 = 1) |

|-----------|------------------|---------------------------|---------------------------|

| 0000      | Disabled         | None                      | None                      |

| 0 0 0 1   | 2 K              | G1A[15:11]                | G1A[18:11]                |

| 0 0 1 0   | 4 K              | G1A[15:11]                | G1A[18:12]                |

| 0 0 1 1   | 8 K              | G1A[15:13]                | G1A[18:13]                |

| 0100      | 16 K             | G1A[15:14]                | G1A[18:14]                |

| 0 1 0 1   | 32 K             | G1A[15]                   | G1A[18:15]                |

| 0110      | 64 K             | None                      | G1A[18:16]                |

| 0 1 1 1   | 128 K            | None                      | G1A[18:17]                |

| 1000      | 256 K            | None                      | G1A18                     |

| 1 0 0 1   | 512 K            | None                      | None                      |

| 1010      | Follow window 1  | None                      | None                      |

| 1 0 1 1   | Follow window 2  | None                      | None                      |

| 1100–1111 | Default to 512 K | None                      | None                      |

**MOTOROLA**

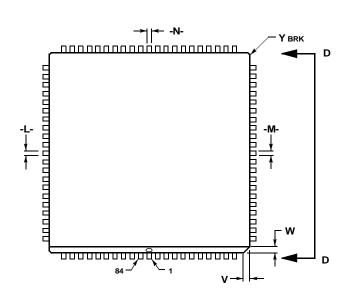

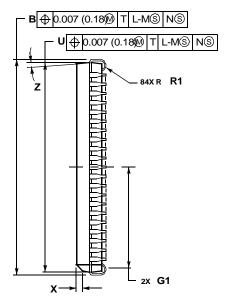

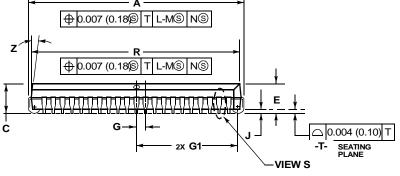

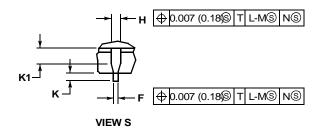

Mechanical Data 84-Pin Plastic-Leaded Chip Carrier (Case 780)

### 13.3 84-Pin Plastic-Leaded Chip Carrier (Case 780)

VIEW D-D

- NOTES:

1. DATUMS L, M, AND N DETERMINED WHERE TOP OF LEAD SHOULDER EXITS PACKAGE BODY AT MOLD PARTING LINE.

- DIMENSION G1 TO BE MEASURED AT CLOSEST APPROACH OF LEAD TO DATUM T, SEATING PLANE.

- DIMENSIONS R AND U DO NOT INCLUDE MOLD FLASH.

- ALLOWABLE MOLD FLASH IS 0.010 (0.25) PER SIDE. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- CONTROLLING DIMENSION: INCH.

- THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM BY UP TO 0.012 (0.300). DIMENSIONS R AND U ARE DETERMINED AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH. TIE BAR BURRS, GATE BURRS AND INTERLEAD FLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

- DIMENSION H DOES NOT INCLUDE DAMBAR PROTRUSION OR INTRUSION. THE DAMBAR PROTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE GREATER THAN 0.037 (0.94). THE DAMBAR INTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE SMALLER THAN 0.025 (0.635).

|     | INC   | HES   | MILLIN | IETERS |

|-----|-------|-------|--------|--------|

| DIM | MIN   | MAX   | MIN    | MAX    |

| Α   | 1.185 | 1.195 | 30.10  | 30.35  |

| В   | 1.185 | 1.195 | 30.10  | 30.35  |

| С   | 0.165 | 0.180 | 4.20   | 4.57   |

| Ε   | 0.090 | 0.120 | 2.29   | 3.05   |

| F   | 0.013 | 0.021 | 0.33   | 0.53   |

| G   | 0.050 | BSC   | 1.27   | BSC    |

| Н   | 0.026 | 0.032 | 0.66   | 0.81   |

| J   | 0.020 |       | 0.51   |        |

| K   | 0.025 |       | 0.64   |        |

| R   | 1.150 | 1.156 | 29.21  | 29.36  |

| U   | 1.150 | 1.156 | 29.21  | 29.36  |

| ٧   | 0.042 | 0.048 | 1.07   | 1.21   |

| W   | 0.042 | 0.048 | 1.07   | 1.21   |

| Х   | 0.042 | 0.056 | 1.07   | 1.42   |

| Υ   |       | 0.020 | -      | 0.50   |

| Ζ   | 2°    | 10°   | 2°     | 10°    |

| G1  | 0.545 | 0.565 | 13.84  | 14.35  |

| K1  | 0.060 |       | 1.52   |        |

| R1  | 0.025 | 0.045 | 0.64   | 1.14   |

|     |       |       |        |        |