#### Details

E·XFI

#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | HC11                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 4MHz                                                                 |

| Connectivity               | SCI, SPI                                                             |

| Peripherals                | POR, PWM, WDT                                                        |

| Number of I/O              | 62                                                                   |

| Program Memory Size        | 24KB (24K x 8)                                                       |

| Program Memory Type        | OTP                                                                  |

| EEPROM Size                | 640 × 8                                                              |

| RAM Size                   | 768 × 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                          |

| Data Converters            | A/D 8x8b                                                             |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 84-LCC (J-Lead)                                                      |

| Supplier Device Package    | 84-PLCC (29.29x29.29)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc711k4vfne4 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC68HC11K Family Technical Data

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Motorola and (A) are registered trademarks of Motorola, Inc. DigitalDNA is a trademark of Motorola, Inc.

© Motorola, Inc., 2001

M68HC11K Family

**Technical Data**

MOTOROLA

## **Table of Contents**

## **Section 1. General Description**

| 1.1 | Contents                  |

|-----|---------------------------|

| 1.2 | Introduction              |

| 1.3 | M68HC11K Family Members26 |

| 1.4 | Features                  |

| 1.5 | Structure                 |

## **Section 2. Pin Description**

| 2.1  | Contents                                                                                                   |

|------|------------------------------------------------------------------------------------------------------------|

| 2.2  | Introduction                                                                                               |

| 2.3  | Power Supply ( $V_{DD}$ , $V_{SS}$ , $AV_{DD}$ , and $AV_{SS}$ )                                           |

| 2.4  | Reset (RESET)                                                                                              |

| 2.5  | Crystal Driver and External Clock Input (XTAL and EXTAL)37                                                 |

| 2.6  | XOUT                                                                                                       |

| 2.7  | E-Clock Output (E)                                                                                         |

| 2.8  | Interrupt Request ( $\overline{IRQ}$ ) and Non-Maskable Interrupt ( $\overline{XIRQ}$ ) .38                |

| 2.9  | Mode Selection, Instruction Cycle Reference,<br>and Standby Power (MODA/LIR and MODB/V <sub>STBY</sub> )39 |

| 2.10 | $V_{RH}$ and $V_{RL}$                                                                                      |

| 2.11 | Port Signals                                                                                               |

## **Table of Contents**

## Section 8. Serial Peripheral Interface (SPI)

| 8.1                                              | Contents                                                                                                                                                                                      |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.2                                              | Introduction                                                                                                                                                                                  |

| 8.3                                              | SPI Functional Description                                                                                                                                                                    |

| 8.4<br>8.4.1<br>8.4.2<br>8.4.3<br>8.4.4<br>8.4.5 | SPI Signal Descriptions170Master In Slave Out (MISO)170Master Out Slave In (MOSI)170Serial Clock (SCK)170Slave Select (SS)171SPI Timing171                                                    |

| 8.5<br>8.5.1<br>8.5.2                            | SPI System Errors172Mode Fault Error172Write Collision Error173                                                                                                                               |

| 8.6<br>8.6.1<br>8.6.2<br>8.6.3<br>8.6.4<br>8.6.5 | SPI Registers173Serial Peripheral Control Register174Serial Peripheral Status Register176Serial Peripheral Data Register177Port D Data Direction Register178System Configuration Options 2179 |

## Section 9. Timing System

| 9.1   | Contents                                  |

|-------|-------------------------------------------|

| 9.2   | Introduction                              |

| 9.3   | Timer Structure                           |

| 9.4   | Input Capture and Output Compare Overview |

| 9.4.1 | Timer Counter Register                    |

| 9.4.2 | Timer Interrupt Flag 2 Register           |

| 9.4.3 | Timer Interrupt Mask 2 Register           |

| 9.4.4 | Port A Data Direction Register            |

| 9.4.5 | Pulse Accumulator Control Register        |

Technical Data

MOTOROLA

#### **Operating Modes and On-Chip Memory**

Port B provides the high-order address byte (Addr[15:8]), port F the low-order address byte (Addr[7:0]), port C the data bus (Data[7:0]), and port G pin 7 the read/write line (R/W) which controls direction of data flow.

Additionally, the E clock output can be used to synchronize external decoders for enable signals.

Expanded mode also enables these two special features available only on the K4 Family devices:

- 1. Memory expansion uses port G[5:0] to increase the available external address space to 1 Mbyte.

- 2. Four chip-select lines on port H[7:4] simplify selection of external memory devices.

Both of these features are described in **Section 11. Memory Expansion** and Chip Selects.

#### 4.5.3 Bootstrap Mode

Resetting the MCU in special bootstrap mode selects a reset vector to a special ROM bootloader program at addresses \$BE00–\$BFFF. The bootloader program is used to download code, such as programming algorithms, into on-chip RAM through the SCI. To do this:

- 1. Send a synchronization character (see **Table 4-2**) to the SCI receiver at the specified baud rate.

- Download up to 768 bytes (1 Kbyte for KS2) of program data, which the CPU places into RAM starting at \$0080 and also echoes back on the TxD signal. The bootloader program ends the download after the RAM is full or when the received data line is idle for at least four character times. See Table 4-2.

When loading is complete, the MCU jumps to location \$0080 and begins executing the code. Interrupt vectors are directed to RAM, which allows the use of interrupts through a jump table. The SCI transmitter requires an external pullup resistor since it is part of port D, which the bootloader configures for wired-OR operation.

Technical Data

Operating Modes and On-Chip Memory EEPROM and the CONFIG Register

#### 4.8.2.2 EEPROM Bulk Erase

BULKE

ROWE

| LDAB | #\$06  |                                      |

|------|--------|--------------------------------------|

| STAB | \$003B | Set EELAT and ERASE.                 |

| STAA | \$0,X  | Store any data to any EEPROM address |

| LDAB | #\$07  |                                      |

| STAB | \$002B | Set EEPGM bit as well                |

|      |        | to enable EEPROM programming voltage |

| JSR  | DLY10  | Delay 10 ms                          |

| CLR  | \$003B | Turn off programming voltage and set |

|      |        | to READ mode                         |

#### 4.8.2.3 EEPROM Row Erase

| LDAB | #\$07  |                                      |

|------|--------|--------------------------------------|

| STAB | \$003B | Set EELAT, ERASE and ROW.            |

| STAA | \$0,X  | Store any data to any EEPROM address |

|      |        | in row                               |

| LDAB | #\$07  |                                      |

| STAB | \$002B | Set EEPGM bit as well                |

|      |        | to enable EEPROM programming voltage |

| JSR  | DLY10  | Delay 10 ms                          |

| CLR  | \$003B | Turn off programming voltage and set |

|      |        | to READ mode                         |

#### 4.8.2.4 EEPROM Byte Erase

| BYTEE | LDAB<br>STAB<br>STAA | #\$16<br>\$003B<br>\$0,X | Set EELAT, ERASE and BYTE.<br>Store any data to targeted EEPROM<br>address |

|-------|----------------------|--------------------------|----------------------------------------------------------------------------|

|       | LDAB                 | #\$17                    |                                                                            |

|       | STAB                 | \$002B                   | Set EEPGM bit as well<br>to enable EEPROM programming voltage              |

|       | JSR                  | DLY10                    | Delay 10 ms                                                                |

|       | CLR                  | \$003B                   | Turn off programming voltage and set<br>to READ mode                       |

- The RDRF, IDLE, OR, NF, FE, PF, and RAF receive-related status bits are cleared.

- Serial peripheral interface (SPI)

- The SPI system is disabled by reset.

- The port pins associated with this function default to being general-purpose I/O lines.

- Analog-to-digital (A/D) converter

- The ADPU bit in the OPTION register is cleared, disabling the A/D system.

- The conversion complete flag in the ADCTL register is also cleared.

- System

- The external IRQ pin has the highest I-bit interrupt priority because PSEL[4:0] in the HPRIO register are initialized with the value %00110 (where % indicates a binary value).

- The RBOOT, SMOD, and MDA bits in the HPRIO register reflect the status of the MODB and MODA inputs at the rising edge of reset.

- The IRQ pin is configured for level-sensitive operation for wired-OR systems.

- The DLY control bit in the OPTION register is set, enabling oscillator startup delay after recovery from stop mode.

- The clock monitor system is disabled because the CME and FCME bits in the OPTION register are cleared.

## 5.5 Interrupts

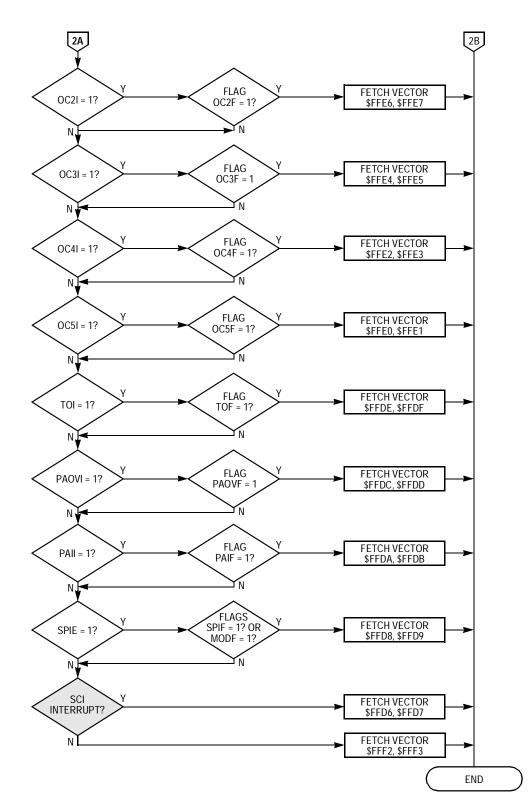

The MCU has 18 interrupt vectors that support 22 interrupt sources. The 19 maskable interrupts are generated by on-chip peripheral systems. They are recognized when the I bit in the CCR is clear. The three non-maskable interrupt sources are illegal opcode trap, software interrupt, and XIRQ pin. Table 5-5 lists the interrupt sources and vector assignments for each source.

M68HC11K Family

MOTOROLA

Semiconductor, Inc.

Freescale

## Freescale Semiconductor, Inc.

**Resets and Interrupts**

**Technical Data**

M68HC11K Family

MOTOROLA

Resets and Interrupts Low-Power Operation

to restart the system, a normal reset sequence results and all pins and registers are reinitialized.

To use the IRQ pin as a means of recovering from STOP, the I bit in the CCR must be clear (IRQ not masked). The XIRQ pin can be used to wake up the MCU from STOP regardless of the state of the X bit in the CCR, although the state of this bit does affect the recovery sequence. If X is clear (XIRQ not masked), the MCU executes a normal XIRQ service routine. If X is set (XIRQ masked or inhibited), then processing continues with the instruction that immediately follows the STOP instruction, and no XIRQ interrupt service is requested or pending.

Executing a STOP instruction requires special consideration when the clock monitor is enabled. Because the stop function halts all clocks, the clock monitor function will generate a reset sequence if it is enabled at the time the stop mode was initiated. To prevent this, clear the CME and FCME bits in the OPTION register before executing a STOP instruction to disable the clock monitor. After recovery from STOP, set the CME bit to enable the clock monitor.

Systems using the internal oscillator require a delay after restart upon leaving STOP to allow the oscillator to stabilize. If a stable external oscillator is used, the DLY control bit in the OPTION register can be used to bypass this startup delay (see **Figure 5-11**). Reset sets the DLY control bit; it can be cleared during initialization. Do not use reset to recover from STOP if the DLY is to be bypassed, since reset sets the DLY bit again, causing the restart delay. This same delay will follow a power-on reset, regardless of the state of the DLY control bit, but does not apply to a reset while the clocks are running.

#### Address: \$0039

|        | Bit 7 | 6    | 5                   | 4                  | 3     | 2                   | 1                  | Bit 0              |

|--------|-------|------|---------------------|--------------------|-------|---------------------|--------------------|--------------------|

| Read:  | ADPLE | DSEL | IRQE <sup>(1)</sup> | DLY <sup>(1)</sup> | CME   | FCME <sup>(1)</sup> | CR1 <sup>(1)</sup> | CR0 <sup>(1)</sup> |

| Write: | ADPLE | DSEL | IKUE''              | DLT                | CIVIE | F GIVIE Y           | CR11               | CKU <sup>V</sup>   |

| Reset: | 0     | 0    | 0                   | 1                  | 0     | 0                   | 0                  | 0                  |

1. Can be written only once in first 64 cycles out of reset in normal modes or at any time in special modes

#### Figure 5-11. System Configuration Options Register (OPTION)

M68HC11K Family

MOTOROLA

**Resets and Interrupts**

Technical Data

M68HC11K Family

MOTOROLA

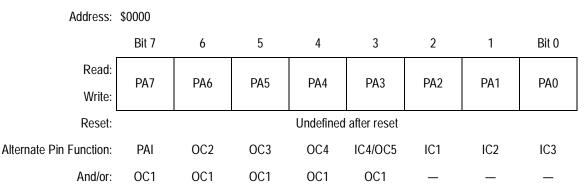

## 6.3 Port A

Port A provides the I/O lines for the timer functions and pulse accumulator. The eight port A bits (PA[7:0]) are configured as high-impedance general-purpose inputs out of reset. Writes to DDRA can change any of the bits to outputs. Writes to timer registers enable the various timer functions (see Section 9. Timing System).

Figure 6-1. Port A Data Register (PORTA)

|                 | Bit 7 | 6    | 5    | 4    | 3    | 2    | 1    | Bit 0 |

|-----------------|-------|------|------|------|------|------|------|-------|

| Read:<br>Write: | DDA7  | DDA6 | DDA5 | DDA4 | DDA3 | DDA2 | DDA1 | DDA0  |

| write.          |       |      |      |      |      |      |      |       |

| Reset:          | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0     |

Figure 6-2. Port A Data Direction Register (DDRA)

DDA[7:0] — Data Direction for Port A Bits

1 = Output

Technical Data

<sup>0 =</sup> Input

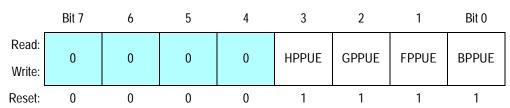

#### 6.11 Internal Pullup Resistors

M68HC11KS series devices contain selectable internal pullup resistors for ports B, F, G, and H. The resistors for each port are enabled by setting the corresponding bit in the PPAR register. PPAR itself must be enabled by setting the PAREN bit in the system configuration register (CONFIG). Refer to **Figure 6-17** and **Figure 6-18**.

Address: \$002C

Figure 6-17. Port Pullup Assignment Register (PPAR)

xPPUE — Port x Pin Pullup Enable Bits

Only active when enabled by the PAREN bit in the CONFIG register

- 0 = Port x pin on-chip pullup devices disabled

- 1 = Port x pin on-chip pullup devices enabled

- **NOTE:** FPPUE and BPPUE do not apply in expanded mode because port F and B are address outputs.

Address: \$003F

|                 | Bit 7 | 6 | 5    | 4     | 3     | 2     | 1     | Bit 0 |

|-----------------|-------|---|------|-------|-------|-------|-------|-------|

| Read:<br>Write: | ROMAD | 1 | CLKX | PAREN | NOSEC | NOCOP | ROMON | EEON  |

| Reset:          | _     | 1 | _    | _     | 1     | _     | _     | _     |

Figure 6-18. System Configuration Register (CONFIG)

**NOTE:** CONFIG is writable once in normal modes and writable at any time in special modes.

PAREN — Pullup Assignment Register Enable Bit

- 0 = PPAR register disabled

- 1 = PPAR register enabled; pullups can be enabled through PPAR

M68HC11K Family

Parallel Input/Output

Serial Communications Interface (SCI) SCI Registers

- PE Parity Enable Bit

- 0 = Parity disabled

- 1 = Parity enabled

- PT Parity Type Bit

- 0 = Parity even (even number of 1s causes parity bit to be 0, odd number of 1s causes parity bit to be 1)

- 1 = Parity odd (odd number of 1s causes parity bit to be 0, even number of 1s causes parity bit to be 1)

#### 7.9.3 Serial Communications Control Register 2

Address \$0073

|        | Bit 7 | 6    | 5   | 4    | 3  | 2  | 1   | Bit 0 |

|--------|-------|------|-----|------|----|----|-----|-------|

| Read:  | TIE   | TCIE | RIE | ILIE | TE | RE | RWU | SBK   |

| Write: |       | TOIL |     |      | 16 |    | RWO | JUK   |

| Reset: | 0     | 0    | 0   | 0    | 0  | 0  | 0   | 0     |

#### Figure 7-8. SCI Control Register 2 (SCCR2)

- TIE Transmit Interrupt Enable Bit

- 0 = TDRE interrupts disabled

- 1 = SCI interrupt is requested when the TDRE status flag is set.

- TCIE Transmit Complete Interrupt Enable Bit

- 0 = TC interrupts disabled

- 1 = SCI interrupt is requested when the TC status flag is set.

- RIE Receiver Interrupt Enable Bit

- 0 = RDRF and OR interrupts disabled

- 1 = SCI interrupt is requested when the RDRF flag or OR flag is set.

- ILIE Idle Line Interrupt Enable Bit

- 0 = IDLE interrupts disabled

- 1 = SCI interrupt is requested when the IDLE status flag is set.

Timing System Input Capture and Output Compare Overview

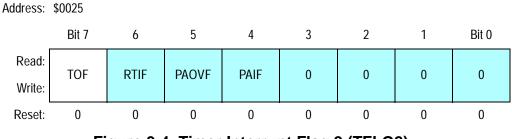

#### 9.4.2 Timer Interrupt Flag 2 Register

Figure 9-4. Timer Interrupt Flag 2 (TFLG2)

Clear each flag by writing a 1 to the corresponding bit position.

TOF — Timer Overflow Flag

Set when TCNT changes from \$FFFF to \$0000.

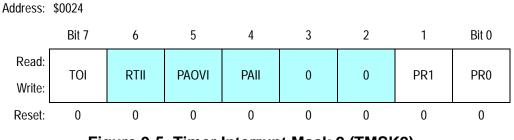

#### 9.4.3 Timer Interrupt Mask 2 Register

Figure 9-5. Timer Interrupt Mask 2 (TMSK2)

Bits in TMSK2 correspond bit for bit with flag bits in TFLG2.

TOI — Timer Overflow Interrupt Enable Bit

- 0 = Timer overflow interrupt disabled

- 1 = An interrupt request is generated when TOF is set.

**Timing System Output Compare (OC)**

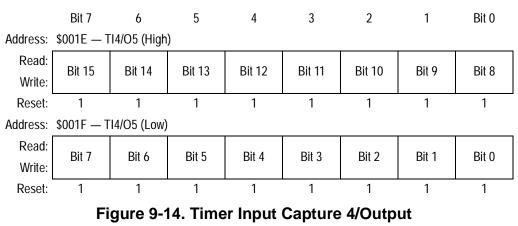

#### 9.6.2 Timer Input Capture 4/Output Compare 5 Register

Compare 5 Register (TI4/O5)

Functions as the output compare register for OC5 when PA3 is configured for output compare 5. This register is 16-bit read-write. It can be used as a storage location if it is not used for output compare or input capture.

#### 9.6.3 Timer Interrupt Flag 1 Register

Address: \$0023

|                 | Bit 7 | 6    | 5    | 4    | 3      | 2    | 1    | Bit 0 |

|-----------------|-------|------|------|------|--------|------|------|-------|

| Read:<br>Write: | OC1F  | OC2F | OC3F | OC4F | 14/05F | IC1F | IC2F | IC3F  |

| Reset:          | 0     | 0    | 0    | 0    | 0      | 0    | 0    | 0     |

Clear each flag by writing a 1 to the corresponding bit position.

OCxF — Output Compare x Flag

Set each time the counter matches output compare x value.

14/O5F — Input Capture 4/Output Compare 5 Flag

Set each time the counter matches output compare 5 value if OC5 is enabled.

M68HC11K Family

**Timing System**

**Technical Data**

Analog-to-Digital (A/D) Converter

#### **10.5 Design Considerations**

This section discusses design considerations.

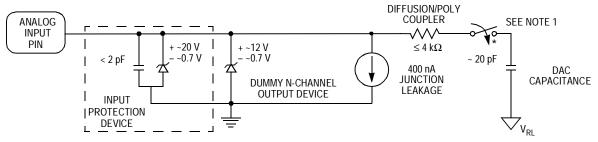

#### 10.5.1 A/D Input Pins

Port E pins can also be used as general-purpose digital inputs. Digital reads of port E pins are not recommended during the sample portion of an A/D conversion cycle, when the gate signal to the N-channel input is on. No P-channel devices are directly connected to either input pins or reference voltage pins, so voltages above  $V_{DD}$  do not cause a latchup problem, although current should be limited according to maximum ratings. Refer to Figure 10-6.

Note 1. This analog switch is closed only during the 12-cycle sample time.

#### Figure 10-6. Electrical Model of an A/D Input Pin (Sample Mode)

#### 10.5.2 Operation in Stop and Wait Modes

If a conversion sequence is in progress when either the stop or wait mode is entered, the conversion of the current channel is suspended. When the MCU resumes normal operation, that channel is resampled and the conversion sequence is resumed. As the MCU exits the wait mode, the A/D circuits are stable and valid results can be obtained on the first conversion. However, in stop mode, all analog bias currents are disabled and it is necessary to allow a stabilization period when leaving stop mode. If stop mode is exited with a delay (DLY = 1), there is enough time for these circuits to stabilize before the first conversion. If stop mode is exited with no delay (DLY bit in OPTION register = 0), allow 10 ms for the A/D circuitry to stabilize to avoid invalid results.

Technical Data

#### Memory Expansion and Chip Selects

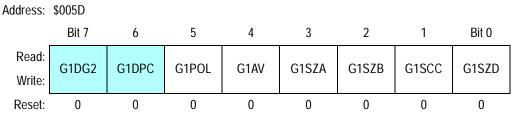

#### 11.4.3.3 General-Purpose Chip Select 1 Control Register

- G1POL General-Purpose Chip Select 1 Polarity Select Bit

- 0 = CSGP1 active low

- 1 = CSGP1 active high

- G1AV General-Purpose Chip Select 1 Address Valid Select Bit

- 0 = CSGP1 is valid during E high time.

- 1 = CSGP1 is valid during address valid time.

G1SZ[A:D] — General-Purpose Chip Select 1 Size Bits

They select the range of GPCS1. Refer to Table 11-6.

| G1SZ[A:D] | Size (Bytes)               | Valid Bits<br>(MXGS1 = 0) | Valid Bits<br>(MXGS1 = 1) |  |  |

|-----------|----------------------------|---------------------------|---------------------------|--|--|

| 0000      | Disabled                   | None                      | None                      |  |  |

| 0001      | 2 K                        | G1A[15:11]                | G1A[18:11]                |  |  |

| 0010      | 4 K                        | G1A[15:11]                | G1A[18:12]                |  |  |

| 0011      | 8 K                        | G1A[15:13]                | G1A[18:13]                |  |  |

| 0100      | 0 1 0 0 16 K               |                           | G1A[18:14]                |  |  |

| 0101      | 0 1 0 1 32 K               |                           | G1A[18:15]                |  |  |

| 0110      | 64 K                       | None                      | G1A[18:16]                |  |  |

| 0111      | 0 1 1 1 128 K              |                           | G1A[18:17]                |  |  |

| 1000      | 1 0 0 0 256 K              |                           | G1A18                     |  |  |

| 1001      | 1 0 0 1 512 K              |                           | None                      |  |  |

| 1010      | 1010 Follow window 1       |                           | None                      |  |  |

| 1011      | Follow window 2            | None                      | None                      |  |  |

| 1100–1111 | 1100–1111 Default to 512 K |                           | None                      |  |  |

M68HC11K Family

## **12.9 Peripheral Port Timing**

|                                                                                                                                                                                                                                                                                                                   | Symbol            | 1.0 MHz |                          | 2.0 MHz |                          | 3.0 MHz |                          | 4.0 MHz |                 | 11:0:14 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|--------------------------|---------|--------------------------|---------|--------------------------|---------|-----------------|---------|

| Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                                                     |                   | Min     | Max                      | Min     | Max                      | Min     | Max                      | Min     | Max             | Unit    |

| Frequency of operation (E clock)                                                                                                                                                                                                                                                                                  | f <sub>o</sub>    | dc      | 1.0                      | dc      | 2.0                      | dc      | 3.0                      | dc      | 4.0             | MHz     |

| E-clock period                                                                                                                                                                                                                                                                                                    | t <sub>cyc</sub>  | 1000    |                          | 500     |                          | 333     |                          | 250     | _               | ns      |

| Peripheral data setup time <sup>(2)</sup><br>MCU read of ports A, B, C, D, E,<br>F, G, and H                                                                                                                                                                                                                      | t <sub>PDSU</sub> | 100     |                          | 100     |                          | 100     |                          | 100     |                 | ns      |

| Peripheral data hold time<br>MCU read of ports A, B, C, D, E,<br>F, G, and H                                                                                                                                                                                                                                      | t <sub>PDH</sub>  | 50      | _                        | 50      | _                        | 50      |                          | 50      | _               | ns      |

| Delay time, peripheral data write<br>Standard devices<br>MCU write to port A, B, G, and H<br>MCU write to ports C, D, and F<br>$(t_{PWD} = 1/4 t_{cyc} + 100 \text{ ns})$<br>Extended voltage<br>MCU write to port A, B, G, and H<br>MCU write to ports C, D, and F<br>$(t_{PWD} = 1/4 t_{cyc} + 150 \text{ ns})$ | t <sub>PWD</sub>  |         | 200<br>350<br>250<br>400 |         | 200<br>225<br>250<br>225 |         | 200<br>183<br>250<br>233 |         | 200<br>162<br>— | ns      |

V<sub>DD</sub> = 4.5 to 5.5 Vdc for standard devices, V<sub>SS</sub> = 0 Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub> All timing measurements refer to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless otherwise noted.

Ports C and D timing is valid only in active drive mode. (CWOM and DWOM bits are cleared in OPT2 and SPCR registers, respectively.)

M68HC11K Family

## 12.11 Expansion Bus Timing

| Num      | Characteristic <sup>(1)</sup>                                                                    | Cumbal                           | 2.0 MHz |          | 3.0 MHz |          | 4.0 MHz |          | Unit |

|----------|--------------------------------------------------------------------------------------------------|----------------------------------|---------|----------|---------|----------|---------|----------|------|

|          |                                                                                                  | Symbol                           | Min     | Max      | Min     | Max      | Min     | Max      | Unit |

|          | Frequency of operation (E clock) <sup>(2)</sup>                                                  | f <sub>o</sub>                   | dc      | 2.0      | dc      | 3.0      | dc      | 4.0      | MHz  |

| 1        | Cycle time, $t_{cyc} = 1/f_o$                                                                    | t <sub>cyc</sub>                 | 500     | _        | 333     | _        | 250     | _        | ns   |

| 2        | Pulse width, E low, $PW_{EL} = 1/2 t_{cyc} - 20 ns$                                              | PW <sub>EL</sub>                 | 230     | _        | 147     | _        | 105     | _        | ns   |

| 3        | Pulse width, E high <sup>(3)</sup><br>PW <sub>EH</sub> = $1/2 t_{cyc} - 25 ns$                   | PW <sub>EH</sub>                 | 225     | _        | 142     | _        | 100     | _        | ns   |

| 4A<br>4B | E clock<br>Rise time<br>Fall time                                                                | t <sub>r</sub><br>t <sub>f</sub> |         | 20<br>20 |         | 20<br>18 |         | 20<br>15 | ns   |

| 9        | Address hold time, $t_{AH} = 1/8 t_{cyc} - 10 ns$                                                | t <sub>AH</sub>                  | 53      | _        | 32      | —        | 21      | _        | ns   |

| 11       | Address delay time, $t_{AD} = 1/8 t_{cyc} + 40 \text{ ns}$                                       | t <sub>AD</sub>                  | —       | 103      | _       | 82       | _       | 71       | ns   |

| 12       | Address valid time to E rise<br>$t_{AV} = PW_{EL} - t_{AD}$                                      | t <sub>AV</sub>                  | 128     | _        | 65      | _        | 34      | _        | ns   |

| 17       | Read data setup time                                                                             | t <sub>DSR</sub>                 | 30      | _        | 30      | _        | 20      | _        | ns   |

| 18       | Read data hold time                                                                              | t <sub>DHR</sub>                 | 0       | _        | 0       | —        | 0       | _        | ns   |

| 19       | Write data delay time                                                                            | t <sub>DDW</sub>                 | —       | 40       | _       | 40       | _       | 40       | ns   |

| 21       | Write data hold time, $t_{DHW} = 1/8 t_{cyc}$                                                    | t <sub>DHW</sub>                 | 63      | _        | 42      |          | 31      | _        | ns   |

| 29       | MPU address access time <sup>(3)</sup><br>$t_{ACCA} = t_{cyc} - t_f - t_{DSR} - t_{AD}$          | t <sub>ACCA</sub>                | 348     | _        | 203     |          | 144     |          | ns   |

| 39       | Write data setup time <sup>(3)</sup><br>$t_{DSW} = PW_{EH} - t_{DDW}$                            | t <sub>DSW</sub>                 | 185     | _        | 102     | _        | 60      | _        | ns   |

| 50       | E valid chip-select delay time                                                                   | t <sub>ECSD</sub>                | —       | 40       |         | 40       | _       | 40       | ns   |

| 51       | E valid chip-select access time <sup>(3)</sup><br>$t_{ECSA} = PW_{EH} - t_{ECSD} - t_{DSR}$      | t <sub>ECSA</sub>                | 155     | _        | 72      | _        | 40      | _        | ns   |

| 52       | Chip select hold time                                                                            | t <sub>CH</sub>                  | 0       | 20       | 0       | 20       | 0       | 20       | ns   |

| 54       | Address valid chip-select delay time $t_{ACSD} = 1/4 t_{cyc} + 40 \text{ ns}$                    | t <sub>ACSD</sub>                | -       | 165      |         | 123      | _       | 103      | ns   |

| 55       | Address valid chip-select access time<br>$t_{ACSA} = t_{cyc} - t_{f} - t_{DSR} - t_{ACSD}^{(3)}$ | t <sub>ACSA</sub>                | 285     | _        | 162     | _        | 113     | _        | ns   |

| 56       | Address valid to chip-select time                                                                | t <sub>AVCS</sub>                | 10      | -        | 10      | _        | 10      | _        | ns   |

| 57       | Address valid to data three-state time                                                           | t <sub>AVDZ</sub>                | —       | 10       |         | 10       | _       | 10       | ns   |

1.  $V_{DD}$  = 5.0 ± 10%,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted All timing measurements refer to 20%  $V_{DD}$  and 70%  $V_{DD}$ , unless otherwise noted.

2. Input clocks with duty cycles other than 50% affect bus performance.

3. This parameter is affected by clock stretching. Add n(t<sub>cvc</sub>) to parameter value, where n = 1, 2, or 3 depending on values written to CSCSTR register or n = 1 for STRCH = 1 on KS parts.

M68HC11K Family

# **Section 14. Ordering Information**

Use Table 14-1 to determine part numbers when placing an order.

| Device<br>Number                                | ROM<br>or EPROM | RAM               | EEPROM          | I/O            | Chip<br>Select    | Slow<br>Mode   | Packages                                                     |

|-------------------------------------------------|-----------------|-------------------|-----------------|----------------|-------------------|----------------|--------------------------------------------------------------|

| MC68HC(L)11K0<br>MC68HC(L)11K1<br>MC68HC(L)11K4 | 0<br>0<br>24 K  | 768<br>768<br>768 | 0<br>640<br>640 | 37<br>37<br>62 | Yes<br>Yes<br>Yes | No<br>No<br>No | 84-pin PLCC <sup>(1)</sup><br>80-pin QFP <sup>(2)</sup>      |

| MC68HC711K4                                     | 24 K            | 768               | 640             | 62             | Yes               | No             | 84-pin J-cerquad <sup>(3)</sup><br>84-pin PLCC<br>80-pin QFP |

| MC68HC11KS2                                     | 32 K            | 1 K               | 640             | 51             | No                | Yes            | 68-pin PLCC<br>80-pin LQFP <sup>(4)</sup>                    |

| MC68HC711KS2                                    | 32 K            | 1 K               | 640             | 51             | No                | Yes            | 68-pin PLCC<br>80-pin LQFP<br>68-pin J-cerquad               |

Table 14-1. M68HC11K Family Devices

2. QFP = Quad flat pack

3. J-cerquad = Ceramic windowed version of PLCC

4. LQFP = Low-profile quad flat pack

M68HC11K Family