Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | HC11                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 4MHz                                                                    |

| Connectivity               | SCI, SPI                                                                |

| Peripherals                | POR, PWM, WDT                                                           |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | 640 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                             |

| Data Converters            | A/D 8x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 68-LCC (J-Lead)                                                         |

| Supplier Device Package    | 68-PLCC (24.21x24.21)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchc711ks2cfne4 |

## Technical Data — M68HC11K Family

## **Table of Contents**

# **Section 1. General Description**

| 1.1  | Contents                                                                                                |

|------|---------------------------------------------------------------------------------------------------------|

| 1.2  | Introduction                                                                                            |

| 1.3  | M68HC11K Family Members                                                                                 |

| 1.4  | Features                                                                                                |

| 1.5  | Structure                                                                                               |

|      | Section 2. Pin Description                                                                              |

| 2.1  | Contents                                                                                                |

| 2.2  | Introduction31                                                                                          |

| 2.3  | Power Supply (V <sub>DD</sub> , V <sub>SS</sub> , AV <sub>DD</sub> , and AV <sub>SS</sub> )             |

| 2.4  | Reset (RESET)                                                                                           |

| 2.5  | Crystal Driver and External Clock Input (XTAL and EXTAL) 37                                             |

| 2.6  | XOUT                                                                                                    |

| 2.7  | E-Clock Output (E)                                                                                      |

| 2.8  | Interrupt Request (IRQ) and Non-Maskable Interrupt (XIRQ) .38                                           |

| 2.9  | Mode Selection, Instruction Cycle Reference, and Standby Power (MODA/LIR and MODB/V <sub>STBY</sub> )39 |

| 2.10 | V <sub>RH</sub> and V <sub>RL</sub> 41                                                                  |

| 2 11 | Port Signals 41                                                                                         |

**Table of Contents**

| 11.4 Chip Selects                                                                                                       | 238 |

|-------------------------------------------------------------------------------------------------------------------------|-----|

| 11.4.1 Program Chip Select                                                                                              |     |

| 11.4.2 Input/Output Chip Select                                                                                         |     |

| 11.4.3 General-Purpose Chip Selects                                                                                     |     |

| <ul><li>11.4.3.1 Memory Mapping Size Register</li><li>11.4.3.2 General-Purpose Chip Select 1 Address Register</li></ul> |     |

| 11.4.3.3 General-Purpose Chip Select 1 Control Register                                                                 |     |

| 11.4.3.4 General-Purpose Chip Select 2 Address Register                                                                 |     |

| 11.4.3.5 General-Purpose Chip Select 2 Control Register                                                                 | 245 |

| 11.4.4 One Chip Select Driving Another                                                                                  |     |

| 11.4.4.1 General-Purpose Chip Select 1 Control Register                                                                 |     |

| 11.4.4.2 General-Purpose Chip Select 2 Control Register                                                                 |     |

| 11.4.5 Clock Stretching                                                                                                 |     |

| 11.5 Memory Expansion Examples                                                                                          | 249 |

| Continu 42 Floatwing Characteristics                                                                                    |     |

| Section 12. Electrical Characteristics                                                                                  |     |

| 12.1 Contents                                                                                                           | 253 |

| 12.2 Introduction                                                                                                       | 254 |

| 12.3 Maximum Ratings for Standard Devices                                                                               | 254 |

| 12.4 Functional Operating Range                                                                                         | 255 |

| 12.5 Thermal Characteristics                                                                                            | 255 |

| 12.6 Electrical Characteristics                                                                                         | 256 |

| 12.7 Power Dissipation Characteristics                                                                                  | 257 |

| 12.8 Control Timing                                                                                                     | 259 |

| 12.9 Peripheral Port Timing                                                                                             | 263 |

| 12.10 Analog-to-Digital Converter Characteristics                                                                       | 265 |

| 12.11 Expansion Bus Timing                                                                                              | 267 |

| 12.12 Serial Peripheral Interface Timing                                                                                | 269 |

| 12.13 EEPROM Characteristics                                                                                            | 272 |

## **Table of Contents**

| Section  | 13. | Mechan | ical  | Data |

|----------|-----|--------|-------|------|

| OCCLIOIT |     | MCCHAI | IIVAI |      |

| 13.1 | Contents                                                         |

|------|------------------------------------------------------------------|

| 13.2 | Introduction                                                     |

| 13.3 | 84-Pin Plastic-Leaded Chip Carrier (Case 780)                    |

| 13.4 | 84-Pin J-Cerquad (Case 780A)                                     |

| 13.5 | 80-Pin Quad Flat Pack (Case 841B)277                             |

| 13.6 | 80-Pin Low-Profile Quad Flat Pack (Case 917A)                    |

| 13.7 | 68-Pin Plastic Leaded Chip Carrier (Case 779)                    |

| 13.8 | 68-Pin J-Cerquad (Case 779A)                                     |

|      | Section 14. Ordering Information Section 15. Development Support |

|      |                                                                  |

Index

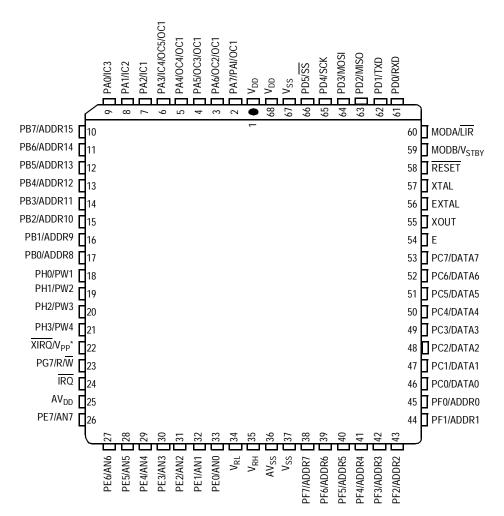

## **Pin Description**

<sup>\*</sup> V<sub>PP</sub> applies only to EPROM devices.

Figure 2-3. Pin Assignments for M6811KS 68-Pin PLCC/J-Cerquad

Technical Data M68HC11K Family

Go to: www.freescale.com

## **Central Processor Unit (CPU)**

Table 3-1. Instruction Set (Sheet 5 of 7)

|            |                                    |                                     | Addressing     | lı          | nstruction  |        | Condition Codes |              |    |          |   |   |   |                    |

|------------|------------------------------------|-------------------------------------|----------------|-------------|-------------|--------|-----------------|--------------|----|----------|---|---|---|--------------------|

| Mnemonic   | Operation                          | Description                         | Mode           | Opcode      | Operand     | Cycles | S               | Х            | ТН | I        | N | Z | ٧ | С                  |

| LSRD       | Logical Shift                      |                                     | INH            | 04          |             | 3      | Ť               | <u> </u>     |    | <u>'</u> | 0 | Δ | Δ | $\frac{1}{\Delta}$ |

|            | Right Double                       | 0                                   |                |             |             |        |                 |              |    |          |   |   |   |                    |

| MUL        | Multiply 8 by 8                    | $A * B \Rightarrow D$               | INH            | 3D          | _           | 10     | _               | _            | _  | _        | _ | _ | _ | Δ                  |

| NEG (opr)  | Two's                              | $0 - M \Rightarrow M$               | EXT            | 70          | hh II       | 6      | _               | _            | _  | _        | Δ | Δ | Δ | Δ                  |

|            | Complement<br>Memory Byte          |                                     | IND,X<br>IND,Y | 60<br>18 60 | ff<br>ff    | 6 7    |                 |              |    |          |   |   |   |                    |

| NEGA       | Two's                              | 0 − A ⇒ A                           | A INH          | 40          | _           | 2      | _               | _            | _  |          | Δ | Δ | Δ |                    |

|            | Complement<br>A                    |                                     |                |             |             |        |                 |              |    |          |   |   |   |                    |

| NEGB       | Two's<br>Complement<br>B           | 0 − B ⇒ B                           | B INH          | 50          | _           | 2      | _               | _            | _  | _        | Δ | Δ | Δ | 2                  |

| NOP        | No operation                       | No Operation                        | INH            | 01          | _           | 2      | _               | _            | _  | _        | _ | _ | _ | _                  |

| ORAA (opr) | OR                                 | $A + M \Rightarrow A$               | A IMM          | 8A          | ii          | 2      | _               | _            | _  | _        | Δ | Δ | 0 | -                  |

|            | Accumulator<br>A (Inclusive)       |                                     | A DIR<br>A EXT | 9A<br>BA    | dd<br>hh II | 3 4    |                 |              |    |          |   |   |   |                    |

|            | / (moldsive)                       |                                     | A IND,X        | AA          | ff          | 4      |                 |              |    |          |   |   |   |                    |

|            |                                    |                                     | A IND,Y        | 18 AA       | ff          | 5      |                 |              |    |          |   |   |   |                    |

| ORAB (opr) | OR                                 | $B + M \Rightarrow B$               | B IMM          | CA          | ii          | 2      | _               | _            | _  | _        | Δ | Δ | 0 | -                  |

|            | Accumulator<br>B (Inclusive)       |                                     | B DIR<br>B EXT | DA<br>FA    | dd<br>hh II | 3 4    |                 |              |    |          |   |   |   |                    |

|            | B (Inclusive)                      |                                     | B IND,X        | EA          | ff          | 4      |                 |              |    |          |   |   |   |                    |

|            |                                    |                                     | B IND,Y        | 18 EA       | ff          | 5      |                 |              |    |          |   |   |   |                    |

| PSHA       | Push A onto<br>Stack               | $A \Rightarrow Stk, SP = SP - 1$    |                | 36          | _           | 3      | _               | _            | _  | _        | _ | _ | _ | -                  |

| PSHB       | Push B onto<br>Stack               | $B \Rightarrow Stk, SP = SP - 1$    |                | 37          | _           | 3      |                 | _            | _  | _        | _ | _ | _ | -                  |

| PSHX       | Push X onto<br>Stack (Lo<br>First) | $  IX \Rightarrow Stk, SP = SP - 2$ | INH            | 3C          | _           | 4      | _               | _            | _  | _        | _ | _ | _ | -                  |

| PSHY       | Push Y onto<br>Stack (Lo<br>First) | $IY \Rightarrow Stk, SP = SP - 2$   | INH            | 18 3C       | _           | 5      | _               | _            | _  | _        | _ | _ | _ | -                  |

| PULA       | Pull A from<br>Stack               | SP = SP + 1, A ← Stk                | A INH          | 32          | _           | 4      |                 | _            | _  | _        | _ | _ | _ | -                  |

| PULB       | Pull B from<br>Stack               | $SP = SP + 1, B \Leftarrow Stk$     |                | 33          | _           | 4      | _               | _            | _  | _        | _ | _ | _ |                    |

| PULX       | Pull X From<br>Stack (Hi<br>First) | $SP = SP + 2$ , $IX \Leftarrow Stk$ | INH            | 38          | _           | 5      | _               | _            | _  | _        | _ | _ | _ |                    |

| PULY       | Pull Y from<br>Stack (Hi<br>First) | $SP = SP + 2$ , $IY \Leftarrow Stk$ | INH            | 18 38       | _           | 6      | _               | _            | _  | _        | _ | _ | _ | -                  |

| ROL (opr)  | Rotate Left                        |                                     | EXT            | 79          | hh II       | 6      | -               | _            |    |          | Δ | Δ | Δ |                    |

| - \=F:/    |                                    | 414111114                           | IND,X          | 69          | ff          | 6      |                 |              |    |          |   | _ | _ |                    |

|            |                                    | C b7 b0                             | IND,Y          | 18 69       | ff          | 7      |                 |              |    |          |   |   |   |                    |

| ROLA       | Rotate Left A                      | C b7 b0                             | A INH          | 49          | _           | 2      |                 | _            | _  | _        | Δ | Δ | Δ |                    |

| ROLB       | Rotate Left B                      | C b/ b0                             | B INH          | 59          |             | 2      | _               |              |    |          | Δ | Δ | Δ |                    |

| NOLD       | Notate Left B                      | C b7 b0                             | D IIVII        | 39          | _           |        |                 | _            | _  | _        | Δ | Δ | Δ |                    |

| ROR (opr)  | Rotate Right                       |                                     | EXT            | 76          | hh II       | 6      | <b> </b>        | _            |    | _        | Δ | Δ | Δ |                    |

|            |                                    |                                     | IND,X          | 66          | ff          | 6      |                 |              |    |          |   |   |   |                    |

| DOD 4      | Datata Di Li i                     | b7 b0 C                             | IND,Y          | 18 66       | ff          | 7      |                 |              |    |          |   |   |   |                    |

| RORA       | Rotate Right A                     |                                     | A INH          | 46          | _           | 2      | -               | _            | _  | _        | Δ | Δ | Δ |                    |

|            |                                    | b7 b0 C                             |                |             |             |        |                 |              |    |          |   |   |   |                    |

| RORB       | Rotate Right B                     |                                     | B INH          | 56          | _           | 2      | _               | _            | _  | _        | Δ | Δ | Δ |                    |

|            |                                    | b7 b0 C                             |                |             |             |        |                 |              |    |          |   |   |   |                    |

| RTI        | Return from                        | See Figure 3-2                      | INH            | 3B          | <u> </u>    | 12     | Δ               | $\downarrow$ | Δ  | Δ        | Δ | Δ | Δ |                    |

|            | Interrupt                          |                                     |                |             |             |        |                 |              |    |          |   |   |   |                    |

| RTS        | Return from                        | See Figure 3-2                      | INH            | 39          | _           | 5      | -               | _            | _  | _        | - | _ | _ |                    |

|            | Subroutine                         | I                                   |                |             |             |        |                 |              |    |          | 1 |   |   |                    |

## **Operating Modes and On-Chip Memory**

#### 4.2 Introduction

This section presents the elements involved in configuring the M68HC11K/KS Family microcontrollers (MCUs), including:

- A list of the control registers, see 4.3 Control Registers

- Special registers that control system initialization, see 4.4 System Initialization

- Description of the four operating modes and how they're selected, see 4.5 Operating Modes

- Memory maps of the K Family, see 4.6 Memory Map

- Information on programming EPROM (erasable, programmable read-only memory) and EEPROM (electrically erasable, programmable read-only memory), see 4.7 EPROM/OTPROM (M68HC711K4 and M68HC711KS2) and 4.8 EEPROM and the CONFIG Register

## 4.3 Control Registers

The heart of the M68HC11 Family of MCUs is a special register block which controls the peripheral functions. In the K Family, this block is 128 bytes. The default location of this block is the first 128 bytes of memory, but software can map it to any 4-Kbyte boundary (see **4.6.1 Control Registers and RAM**).

Certain bits and registers that control initialization and the basic operation of the MCU are protected against writes in normal operating modes except under special circumstances. Some bits cannot be written at all; others can be written only once and/or within the first 64 bus cycles after any reset. The special operating modes override these restrictions. These bits and registers are discussed in **4.4 System Initialization**.

Normal and special operating modes are discussed in **4.5 Operating Modes**. The write-restricted registers and bits are summarized in **Table 4-1**.

**Figure 4-1** lists the entire 128-byte register block in ascending order by address, using the default memory block assignment \$0000–\$007F.

## **Operating Modes and On-Chip Memory**

| Addr.  | Register Name                                                     |                 | Bit 7 | 6                     | 5      | 4     | 3          | 2     | 1           | Bit 0 |

|--------|-------------------------------------------------------------------|-----------------|-------|-----------------------|--------|-------|------------|-------|-------------|-------|

| \$006C | Pulse Width Modulation Timer Duty Cycle 1                         | Read:<br>Write: | Bit 7 | Bit 6                 | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|        | Register (PWDTY1) See page 219.                                   | Reset:          | 0     | 0                     | 0      | 0     | 0          | 0     | 0           | 0     |

| \$006D | Pulse Width Modulation<br>Timer Duty Cycle 2<br>Register (PWDTY2) | Read:<br>Write: | Bit 7 | Bit 6                 | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|        | See page 219.                                                     | Reset:          | 0     | 0                     | 0      | 0     | 0          | 0     | 0           | 0     |

| \$006E | Pulse Width Modulation<br>Timer Duty Cycle 3<br>Register (PWDTY3) | Read:<br>Write: | Bit 7 | Bit 6                 | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|        | See page 219.                                                     | Reset:          | 0     | 0                     | 0      | 0     | 0          | 0     | 0           | 0     |

| \$006F | Pulse Width Modulation<br>Timer Duty Cycle 4<br>Register (PWDTY4) | Read:<br>Write: | Bit 7 | Bit 6                 | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1       | Bit 0 |

|        | See page 219.                                                     | Reset:          | 0     | 0                     | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0070 | SCI Baud Rate Control<br>Register High (SCBDH)                    | Read:<br>Write: | BTST  | BSPL                  | 0      | SBR12 | SBR11      | SBR10 | SBR9        | SBR8  |

|        | See page 158.                                                     | Reset:          | 0     | 0                     | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0071 | SCI Baud Rate Control<br>Register Low (SCBDL)                     | Read:<br>Write: | SBR7  | SBR6                  | SBR5   | SBR4  | SBR3       | SBR2  | SBR1        | SBR0  |

|        | See page 158.                                                     | Reset:          | 0     | 0                     | 0      | 0     | 0          | 1     | 0           | 0     |

| \$0072 | SCI Control Register 1<br>(SCCR1)                                 | Read:<br>Write: | LOOPS | WOMS                  | 0      | M     | WAKE       | ILT   | PE          | PT    |

|        | See page 160.                                                     | Reset:          | U     | U                     | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0073 | SCI Control Register 2<br>(SCCR2)                                 | Read:<br>Write: | TIE   | TCIE                  | RIE    | ILIE  | TE         | RE    | RWU         | SBK   |

|        | See page 161.                                                     | Reset:          | 0     | 0                     | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0074 | SCI Status Register 1<br>(SCSR1)                                  | Read:<br>Write: | TDRE  | TC                    | RDRF   | IDLE  | OR         | NF    | FE          | PF    |

|        | See page 162.                                                     | Reset:          | 0     | 0                     | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0075 | SCI Status Register 2<br>(SCSR2)                                  | Read:<br>Write: | 0     | 0                     | 0      | 0     | 0          | 0     | 0           | RAF   |

|        | See page 164.                                                     | Reset:          | 1     | 1                     | 0      | 0     | 0          | 0     | 0           | 0     |

| \$0076 | SCI Data Register<br>(SCDR)                                       | Read:<br>Write: | R8    | Т8                    | 0      | 0     | 0          | 0     | 0           | 0     |

|        | See page 165.                                                     | Reset:          |       | Undefined after reset |        |       |            |       |             |       |

|        |                                                                   |                 |       | = Unimplen            | nented | R     | = Reserved |       | U = Undefir | ned   |

Figure 4-1. Register and Control Bit Assignments (Sheet 10 of 11)

Operating Modes and On-Chip Memory EPROM/OTPROM (M68HC711K4 and M68HC711KS2)

registers to default values, then receives data from an external host and programs it into the EPROM. The value in the X index register determines programming delay time. The value in the Y index register is a pointer to the first address in EPROM to be programmed. The default starting address is \$8000 for the M68HC11KS2.

When the utility program is ready to receive programming data, it sends the host a \$FF character and waits for a reply. When the host sees the \$FF character, it sends the EPROM programming data, starting with the first location in the EPROM array. After the MCU receives the last byte to be programmed and returns the corresponding verification data, it terminates the programming operation by initiating a reset. Refer to the Motorola application note entitled *MC68HC11 Bootstrap Mode*, document order number AN1060/D.

#### 4.7.2 Programming the EPROM from Memory

In this method, software programs the EPROM one byte at a time. Each byte is read from memory, then latched and programmed into the EPROM using the EPROM programming control register (EPROG). This procedure can be done in any operating mode.

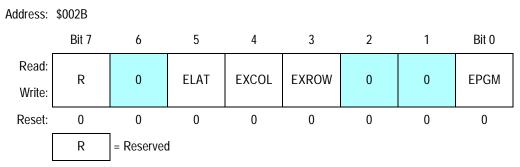

Figure 4-8. EPROM Programming Control Register (EPROG)

MBE — Multiple-Byte Program Enable Bit

MBE is for factory use only and is accessible only in special test mode. When MBE is set, the MCU ignores address bit 5, so that bytes with ADDR5 = 0 and ADDR5 = 1 both get programmed with the same data.

0 = Normal programming

1 = Multiple-byte programming enabled

## **Operating Modes and On-Chip Memory**

The procedures for both writing and erasing involve these five steps:

- 1. **Set the EELAT bit in PPROG**. If erasing, also set the ERASE bit and the appropriate BYTE and ROW bits.

- Write data to the appropriate EEPROM address. If erasing, any data will work. To erase a row, write to any location in the row. To erase the entire EEPROM, write to any location in the array. This step is done before applying the programming voltage because setting the EEPGM bit inhibits writes to EEPROM addresses.

- 3. **Set the EEPGM bit in PPROG,** keeping EELAT set. If erasing, also set the ERASE bit and the appropriate BYTE and ROW bits.

- 4. Delay for 10 ms.

- Clear the PPROG register to turn off the high voltage and reconfigure the EEPROM address and data buses for normal operation.

The following examples demonstrate programming a single EEPROM byte, erasing the entire EEPROM, erasing a row (16 bytes), and erasing a single byte.

#### 4.8.2.1 EEPROM Programming

On entry, accumulator A contains the data to be written and X points to the address to be programmed.

| EE | PROG | LDAB | #\$02  |                                      |

|----|------|------|--------|--------------------------------------|

|    |      | STAB | \$003B | Set EELAT bit to enable EEPROM       |

|    |      |      |        | latches.                             |

|    |      | STAA | \$0,X  | Store data to EPROM address          |

|    |      | LDAB | #\$03  |                                      |

|    |      | STAB | \$002B | Set EPGM bit with ELAT=1             |

|    |      |      |        | to enable EEPROM programming voltage |

|    |      | JSR  | DLY10  | Delay 10 ms                          |

|    |      | CLR  | \$003B | Turn off programming voltage and set |

|    |      |      |        | to READ mode                         |

## **Operating Modes and On-Chip Memory**

#### 4.8.3 CONFIG Register Programming

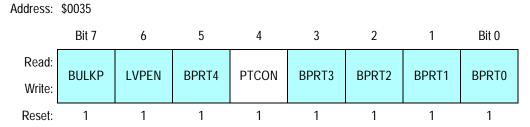

The CONFIG register is implemented with EEPROM cells, so EEPROM procedures are required to change it. CONFIG can be programmed or erased (including byte erase) while the MCU is operating in any mode, provided that PTCON in BPROT is clear.

Figure 4-12. Block Protect Register (BPROT)

PTCON — Protect for CONFIG Bit

0 = CONFIG register can be programmed or erased normally.

1 = CONFIG register cannot be programmed or erased.

To change the value in the CONFIG register, complete this procedure. Do not initiate a reset until the procedure is complete.

- Erase the CONFIG register.

- Program the new value to the CONFIG address.

- Initiate reset.

### 4.8.4 RAM and EEPROM Security

The NOSEC bit in the CONFIG register enables and disables an optional security feature which protects the contents of EEPROM and RAM from unauthorized access. This is done by restricting operation to single-chip modes, preventing the memory locations from being monitored externally. Single-chip modes do not allow visibility of the internal address and data buses. Resident programs, however, have unlimited access to the internal EEPROM and RAM and can read, write, or transfer the contents of these memories.

Resets and Interrupts

## Technical Data — M68HC11K Family

# **Section 7. Serial Communications Interface (SCI)**

#### 7.1 Contents

| 7.2          | Introduction149                              |

|--------------|----------------------------------------------|

| 7.3          | Data Format                                  |

| 7.4          | Transmit Operation151                        |

| 7.5          | Receive Operation                            |

| 7.6          | Wakeup Feature                               |

| 7.7          | Short Mode Idle Line Detection               |

| 7.8          | Baud Rate Selection157                       |

| 7.9<br>7.9.1 | SCI Registers                                |

| 7.9.2        | Serial Communications Control Register 1     |

| 7.9.3        | Serial Communications Control Register 2 161 |

| 7.9.4        | Serial Communication Status Register 1       |

| 7.9.5        | Serial Communication Status Register 2       |

| 7.9.6        | Serial Communications Data Register          |

### 7.2 Introduction

The serial communications interface (SCI) is a universal asynchronous receiver transmitter (UART) employing a standard non-return-to-zero (NRZ) format. Several baud rates are available. The SCI transmitter and receiver are independent, but they use the same data format and baud rate.

## **Serial Peripheral Interface (SPI)**

CPOL selects an active high or low clock edge. CPHA selects one of two transfer formats. When CPHA is cleared, the shift clock is ORed with  $\overline{SS}$ . Each slave's  $\overline{SS}$  pin must be pulled high before it writes the next output byte to its data register. If a slave writes to its data register while  $\overline{SS}$  is low, a write collision error occurs. When CPHA is set,  $\overline{SS}$  may be left low for several SPI characters. When there is only one SPI slave MCU, its  $\overline{SS}$  line may be tied to  $V_{SS}$  if CPHA = 1 at all times.

The SPI configuration determines the characteristics of a transfer in progress. For a master, a transfer begins when data is written to SPDR and ends when SPIF is set. For a slave with CPHA cleared, a transfer starts when SS goes low and ends when SS returns high. In this case, SPIF is set at the middle of the eighth SCK cycle when data is transferred from the shifter to the parallel data register, but the transfer is still in progress until SS goes high. For a slave with CPHA set, transfer begins when the SCK line goes to its active level, which is the edge at the beginning of the first SCK cycle. The transfer ends when SPIF is set. SCK in a slave must be inactive for at least two E-clock cycles between byte transfers.

## 8.5 SPI System Errors

Two types of errors can be detected by the SPI system:

- A mode fault error can occur when multiple devices attempt to act in master mode simultaneously.

- A write collision error results from an attempt to write data to the SPDR while a transmission is in progress.

#### 8.5.1 Mode Fault Error

A mode fault error occurs when the SS input line of an SPI system configured as a master goes to active low, usually because two devices have attempted to act as master at the same time. The resulting contention between push-pull CMOS pin drivers can cause them permanent damage. The mode fault disables the drivers in an attempt to protect them. The MSTR control bit in the SPCR and all four DDRD

Serial Peripheral Interface (SPI)

SPI Registers

#### CPOL — Clock Polarity Bit

When the clock polarity bit is cleared and data is not being transferred, the SCK pin of the master device has a steady state low value. When CPOL is set, SCK idles high.

#### CPHA — Clock Phase Bit

The clock phase bit, in conjunction with the CPOL bit, controls the clock-data relationship between master and slave. The CPHA bit selects one of two different clocking protocols.

#### SPR[1:0] — SPI Clock Rate Select Bits

On a master device, these two bits in conjunction with SPR2 in the OPT2 register select the baud rate to be used as SCK. See **Table 8-1**. These bits have no effect in slave mode.

Table 8-1. SPI+ Baud Rates

| EXTAL Frequencies        |          |                      |          |           |           |             |  |  |

|--------------------------|----------|----------------------|----------|-----------|-----------|-------------|--|--|

| EXTAL Freq.              | 8.0 MHz  | 12.0 MHz             | 16.0 MHz | 20.0 MHz  | 24.0 MHz  | Other EXTAL |  |  |

| E Clock Freq.            | 2.0 MHz  | 3.0 MHz              | 4.0 MHz  | 5.0 MHz   | 6.0 MHz   | EXTAL ÷ 4   |  |  |

| Control Bits<br>SPR[2:0] |          | E Clock<br>Divide by |          |           |           |             |  |  |

| 0 0 0                    | 1.0 MHz  | 1.5 MHz              | 2.0 MHz  | 2.5 MHz   | 3.0 MHz   | 2           |  |  |

| 0 0 1                    | 500 kHz  | 750 kHz              | 1.0 MHz  | 1.3 kHz   | 1.5 MHz   | 4           |  |  |

| 010                      | 125 kHz  | 187.5 kHz            | 250 kHz  | 312.5 kHz | 375.0 kHz | 16          |  |  |

| 0 1 1                    | 62.5 kHz | 93.8 kHz             | 125 kHz  | 156.3 kHz | 187.5 kHz | 32          |  |  |

| 100                      | 250 kHz  | 375 kHz              | 500 kHz  | 625 kHz   | 750.0 kHz | 8           |  |  |

| 1 0 1                    | 125 kHz  | 187.5 kHz            | 250 kHz  | 312.5 kHz | 375.0 kHz | 16          |  |  |

| 110                      | 31.3 kHz | 46.9 kHz             | 62.5 kHz | 78.1 kHz  | 93.8 kHz  | 64          |  |  |

| 111                      | 15.6 kHz | 23.4 kHz             | 31.3 kHz | 39.1 kHz  | 46.9 kHz  | 128         |  |  |

Serial Peripheral Interface (SPI)

M68HC11K Family

**Technical Data**

Timing System Input Capture and Output Compare Overview

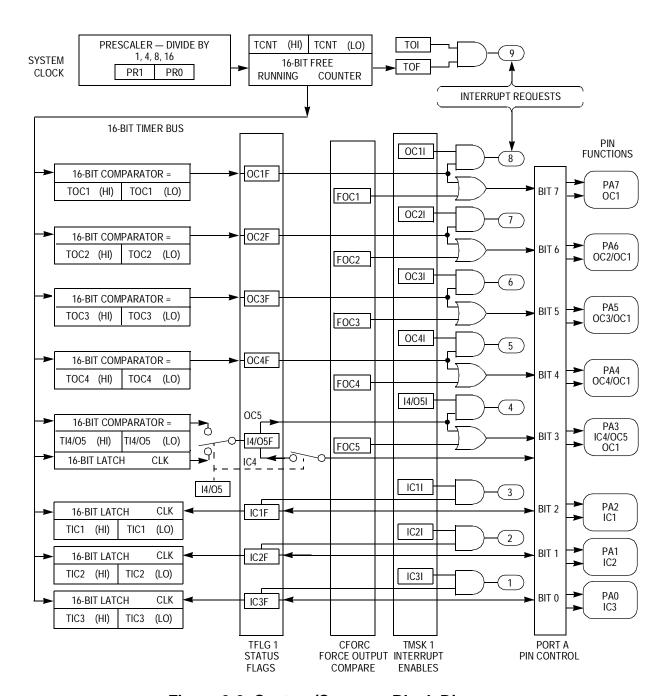

Figure 9-2. Capture/Compare Block Diagram

M68HC11K Family Technical Data

Go to: www.freescale.com

187

## **Timing System**

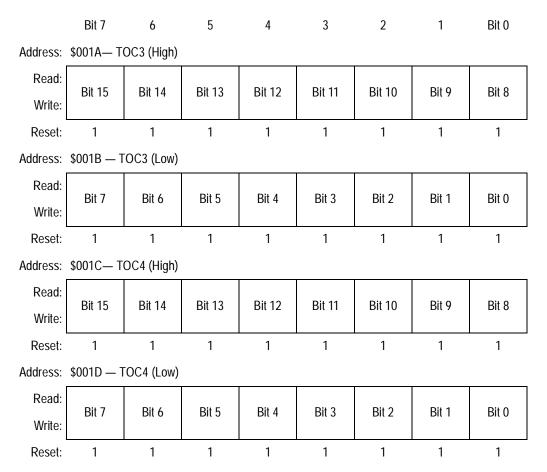

Figure 9-13. Timer Output Compare Registers (TOC1–TOC4) (Continued)

All output compare registers are 16-bit read-write. Any of these registers can be used as a storage location if it is not used for output compare or input capture.

Technical Data M68HC11K Family

Go to: www.freescale.com

## **Electrical Characteristics**

#### 12.2 Introduction

This section contains electrical parameters for standard and extended voltage devices. When applicable, extended voltage parameters are shown separately. Diagrams apply to both standard and extended voltage devices.

## 12.3 Maximum Ratings for Standard Devices

Maximum ratings are the extreme limits to which the MCU can be exposed without permanently damaging it.

NOTE:

This device is not guaranteed to operate properly at the maximum ratings. Refer to **12.6 Electrical Characteristics** for guaranteed operating conditions.

| Rating                                                                                            | Symbol           | Value        | Unit |

|---------------------------------------------------------------------------------------------------|------------------|--------------|------|

| Supply voltage                                                                                    | $V_{DD}$         | -0.3 to +7.0 | V    |

| Input voltage                                                                                     | V <sub>In</sub>  | -0.3 to +7.0 | V    |

| Current drain per $pin^{(1)}$ excluding $V_{DD}$ , $V_{SS}$ , $AV_{DD}$ , $V_{RH}$ , and $V_{RL}$ | I <sub>D</sub>   | 25           | mA   |

| Storage temperature                                                                               | T <sub>STG</sub> | -55 to +150  | °C   |

<sup>1.</sup> One pin at a time, observing maximum power dissipation limits

#### NOTE:

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. For proper operation, it is recommended that  $V_{ln}$  and  $V_{Out}$  be constrained to the range  $V_{SS} \leq (V_{ln} \text{ or } V_{Out}) \leq V_{DD}$ . Reliability of operation is enhanced if unused inputs are connected to an appropriate logic voltage level (for example, either  $V_{SS}$  or  $V_{DD}$ ).

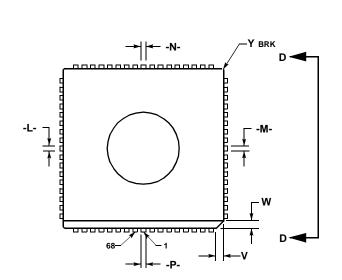

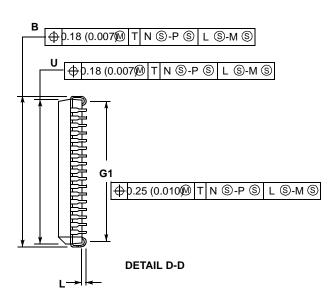

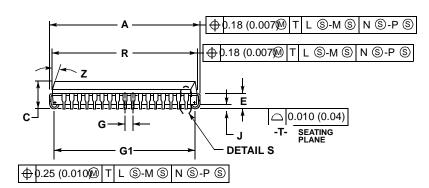

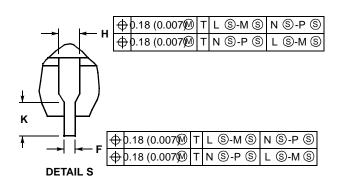

### **Mechanical Data**

## 13.8 68-Pin J-Cerquad (Case 779A)

#### NOTES:

- DATUMS -L-, -M-, -N-, AND -P- DETERMINED WHERE TOP OF LEAD SHOULDER EXITS PLASTIC BODY AT MOLD PARTING LINE.

- 2. DIMENSION G1, TRUE POSITION TO BE MEASURED AT DATUM -T-, SEATING PLANE

- DIMENSIONS R AND U DO NOT INCLUDE MOLD FLASH. ALLOWABLE MOLD FLASH IS 0.25 (0.010) PER SIDE.

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- 5. CONTROLLING DIMENSION: INCH.

|     | INC   | HES   | MILLIN | ETERS |

|-----|-------|-------|--------|-------|

| DIM | MIN   | MAX   | MIN    | MAX   |

| Α   | 0.985 | 0.995 | 25.02  | 25.27 |

| В   | 0.985 | 0.995 | 25.02  | 25.27 |

| С   | 0.155 | 0.200 | 3.94   | 5.08  |

| Е   | 0.090 | 0.120 | 2.29   | 3.05  |

| F   | 0.017 | 0.021 | 0.43   | 0.48  |

| G   | 0.050 | BSC   | 1.27   | BSC   |

| Н   | 0.026 | 0.032 | 0.66   | 0.81  |

| J   | 0.020 |       | 0.51   | -     |

| K   | 0.050 | ) REF | 1.27   | REF   |

| L   | 0.003 |       | 0.08   | -     |

| R   | 0.930 | 0.958 | 23.62  | 24.33 |

| U   | 0.930 | 0.958 | 23.62  | 24.33 |

| ٧   | 0.036 | 0.044 | 0.91   | 1.12  |

| W   | 0.036 | 0.044 | 0.91   | 1.12  |

| G1  | 0.890 | 0.930 | 22.61  | 23.62 |

Index

| OPTION System Configuration Options             |     |

|-------------------------------------------------|-----|

| CME Clock Monitor Enable                        | 111 |

| CR[1:0] COP Timer Rate Select Bits              | 109 |

| DLY Enable Oscillator Startup Delay             | 132 |

| IRQE Configure IRQ for Edge-Sensitive Operation | 121 |

|                                                 |     |

| Р                                               |     |

| PACTL Pulse Accumulator Control                 |     |

| I4/O5 Input Capture 4/Output Compare 5          | 191 |

| PAEN Pulse Accumulator System Enable            | 205 |

| PAMOD Pulse Accumulator Mode                    |     |

| RTR[1:0] Real Time Interrupt Rate Select        | 210 |

| PPROG EPROM Programming Control                 |     |

| ELAT PROM Latch Control                         | 93  |

|                                                 |     |

| S                                               |     |

| SCCR1 SCI Control Register 1                    |     |

| M Mode (SCI Word Size)                          | 160 |

| WAKE Wakeup mode                                | 160 |

| SCCR2 SCI Control Register 2                    |     |

| ILIE Idle Line Interrupt Enable                 | 161 |

| RE Receiver Enable                              | 162 |

| RIE Receiver Interrupt Enable                   | 161 |

| RWU Receiver Wakeup Control                     | 162 |

| · ' '                                           | 161 |

| TE Transmitter Enable                           | 162 |

| TIE Transmit Interrupt Enable                   | 161 |

| SCI Control Register 2                          |     |

| SBK Send Break                                  | 162 |

| SCSR SCI Status Register                        |     |

| FE Framing Error Flag                           | 164 |

| IDLE Idle Line Detected Flag                    | 163 |

| NF Noise Error Flag                             | 163 |

| OR Overrun Error Flag                           | 163 |

| RDRF Receive Data Register Full Flag            | 163 |

| TC Transmit Complete Flag                       | 163 |

| TDRE Transmit Data Register Empty Flag          | 163 |