Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2420-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name             | Pin Number |           |         | Pin    | Buffer | Description                                                                                       |

|----------------------|------------|-----------|---------|--------|--------|---------------------------------------------------------------------------------------------------|

|                      | PDIP       | QFN       | TQFP    | Туре   | Туре   | Description                                                                                       |

| MCLR/VPP/RE3         | 1          | 18        | 18      |        |        | Master Clear (input) or programming voltage (input).                                              |

| MCLR                 |            |           |         | I      | ST     | Master Clear (Reset) input. This pin is an active-low Reset to the device.                        |

| VPP                  |            |           |         | Р      |        | Programming voltage input.                                                                        |

| RE3                  |            |           |         | Ι      | ST     | Digital input.                                                                                    |

| OSC1/CLKI/RA7        | 13         | 32        | 30      |        |        | Oscillator crystal or external clock input.                                                       |

| OSC1                 |            |           |         | I      | ST     | Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode; |

|                      |            |           |         |        |        | analog otherwise.                                                                                 |

| CLKI                 |            |           |         | Ι      | CMOS   | External clock source input. Always associated with                                               |

|                      |            |           |         |        |        | pin function, OSC1. (See related OSC1/CLKI,                                                       |

| RA7                  |            |           |         | I/O    | TTL    | OSC2/CLKO pins.)<br>General purpose I/O pin.                                                      |

| OSC2/CLKO/RA6        | 14         | 33        | 31      |        |        | Oscillator crystal or clock output.                                                               |

| OSC2                 |            | 00        | 01      | 0      |        | Oscillator crystal output. Connects to crystal                                                    |

|                      |            |           |         |        |        | or resonator in Crystal Oscillator mode.                                                          |

| CLKO                 |            |           |         | 0      |        | In RC mode, OSC2 pin outputs CLKO which                                                           |

|                      |            |           |         |        |        | has 1/4 the frequency of OSC1 and denotes the instruction cycle rate.                             |

| RA6                  |            |           |         | I/O    | TTL    | General purpose I/O pin.                                                                          |

| Legend: TTL = TTL co | ompatibl   | e input   |         |        | . (    | CMOS = CMOS compatible input or output                                                            |

|                      | tt Trigge  | r input v | with CM | OS lev |        | = Input                                                                                           |

| O = Output           | t          |           |         |        | F      | P = Power                                                                                         |

#### TABLE 1-3: PIC18F4420/4520 PINOUT I/O DESCRIPTIONS

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

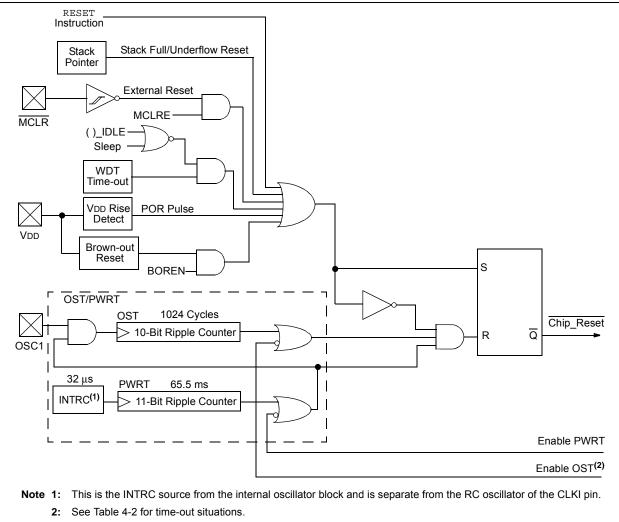

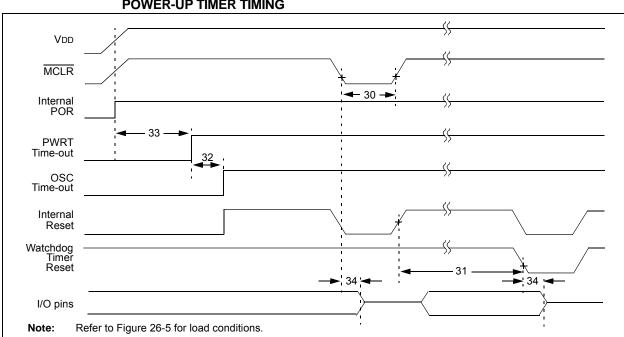

### 4.0 RESET

The PIC18F2420/2520/4420/4520 devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during power-managed modes

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Programmable Brown-out Reset (BOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

This section discusses Resets generated by MCLR, POR and BOR and covers the operation of the various start-up timers. Stack Reset events are covered in Section 5.1.2.4 "Stack Full and Underflow Resets". WDT Resets are covered in Section 23.2 "Watchdog Timer (WDT)". A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 4-1.

### 4.1 RCON Register

Device Reset events are tracked through the RCON register (Register 4-1). The lower five bits of the register indicate that a specific Reset event has occurred. In most cases, these bits can only be cleared by the event and must be set by the application after the event. The state of these flag bits, taken together, can be read to indicate the type of Reset that just occurred. This is described in more detail in **Section 4.6 "Reset State of Registers"**.

The RCON register also has control bits for setting interrupt priority (IPEN) and software control of the BOR (SBOREN). Interrupt priority is discussed in Section 9.0 "Interrupts". BOR is covered in Section 4.4 "Brown-out Reset (BOR)".

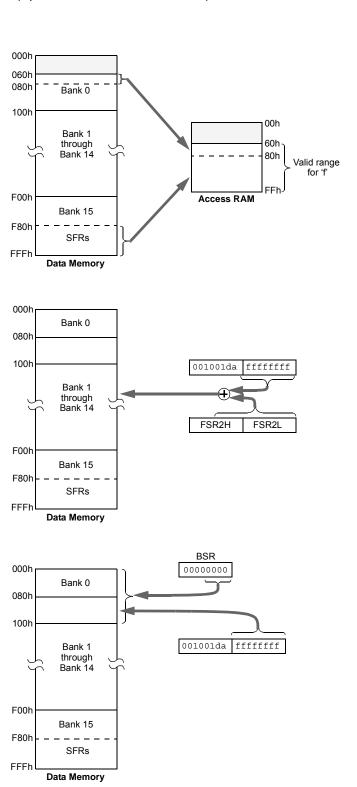

#### FIGURE 5-9: COMPARING ADDRESSING OPTIONS FOR BIT-ORIENTED AND BYTE-ORIENTED INSTRUCTIONS (EXTENDED INSTRUCTION SET ENABLED)

**EXAMPLE INSTRUCTION:** ADDWF, f, d, a (Opcode: 0010 01da ffff ffff)

#### When 'a' = 0 and $f \ge 60h$ :

The instruction executes in Direct Forced mode. 'f' is interpreted as a location in the Access RAM between 060h and 0FFh. This is the same as locations 060h to 07Fh (Bank 0) and F80h to FFFh (Bank 15) of data memory.

Locations below 60h are not available in this addressing mode.

Indexed Literal Offset mode. 'f' is interpreted as an offset to the address value in FSR2. The two are added together to obtain the address of the target register for the instruction. The address can be anywhere in the data memory space.

Note that in this mode, the correct syntax is now: ADDWF [k], dwhere 'k' is the same as 'f'.

#### When 'a' = 1 (all values of f):

The instruction executes in Direct mode (also known as Direct Long mode). 'f' is interpreted as a location in one of the 16 banks of the data memory space. The bank is designated by the Bank Select Register (BSR). The address can be in any implemented bank in the data memory space.

#### 5.5.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

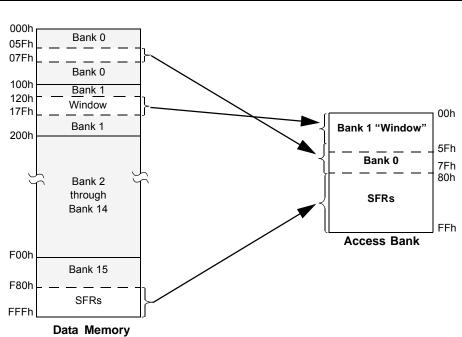

The use of Indexed Literal Offset Addressing mode effectively changes how the first 96 locations of Access RAM (00h to 5Fh) are mapped. Rather than containing just the contents of the bottom half of Bank 0, this mode maps the contents from Bank 0 and a user-defined "window" that can be located anywhere in the data memory space. The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described (see **Section 5.3.2 "Access Bank**"). An example of Access Bank remapping in this addressing mode is shown in Figure 5-10. Remapping of the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit is '1') will continue to use Direct Addressing as before.

## 5.6 PIC18 Instruction Execution and the Extended Instruction Set

Enabling the extended instruction set adds eight additional commands to the existing PIC18 instruction set. These instructions are executed as described in **Section 24.2 "Extended Instruction Set"**.

#### FIGURE 5-10: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

## Example Situation:

ADDWF f, d, a FSR2H:FSR2L = 120h

Locations in the region from the FSR2 Pointer (120h) to the pointer plus 05Fh (17Fh) are mapped to the bottom of the Access RAM (000h-05Fh).

Locations in Bank 0 from 060h to 07Fh are mapped, as usual, to the middle half of the Access Bank.

Special Function Registers at F80h through FFFh are mapped to 80h through FFh, as usual.

Bank 0 addresses below 5Fh can still be addressed by using the BSR.

#### 6.2.2 TABLAT – TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

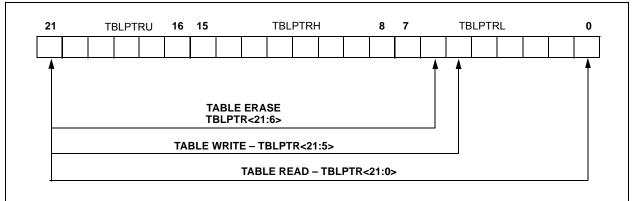

#### 6.2.3 TBLPTR – TABLE POINTER REGISTER

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the device ID, the user ID and the Configuration bits.

The Table Pointer register, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations are shown in Table 6-1. These operations on the TBLPTR only affect the low-order 21 bits.

#### 6.2.4 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory into TABLAT.

When a TBLWT is executed, the five LSbs of the Table Pointer register (TBLPTR<4:0>) determine which of the 32 program memory holding registers is written to. When the timed write to program memory begins (via the WR bit), the 16 MSbs of the TBLPTR (TBLPTR<21:6>) determine which program memory block of 32 bytes is written to. For more detail, see **Section 6.5 "Writing to Flash Program Memory"**.

When an erase of program memory is executed, the 16 MSbs of the Table Pointer register (TBLPTR<21:6>) point to the 64-byte block that will be erased. The Least Significant bits (TBLPTR<5:0>) are ignored.

Figure 6-3 describes the relevant boundaries of TBLPTR based on Flash program memory operations.

#### TABLE 6-1: TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS

| Example            | Operation on Table Pointer                  |

|--------------------|---------------------------------------------|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |

#### FIGURE 6-3:

#### TABLE POINTER BOUNDARIES BASED ON OPERATION

| TABLE 10-7:  | PORTD I/O SUMMARY |                 |     |             |                                                                                                                                                   |  |  |  |  |  |  |  |

|--------------|-------------------|-----------------|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin          | Function          | TRIS<br>Setting | I/O | l/O<br>Type | Description                                                                                                                                       |  |  |  |  |  |  |  |

| RD0/PSP0     | RD0               | 0               | 0   | DIG         | LATD<0> data output.                                                                                                                              |  |  |  |  |  |  |  |

|              |                   | 1               | Ι   | ST          | PORTD<0> data input.                                                                                                                              |  |  |  |  |  |  |  |

|              | PSP0              | x               | 0   | DIG         | PSP read data output (LATD<0>); takes priority over port data.                                                                                    |  |  |  |  |  |  |  |

|              |                   | x               | Ι   | TTL         | PSP write data input.                                                                                                                             |  |  |  |  |  |  |  |

| RD1/PSP1     | RD1               | 0               | 0   | DIG         | LATD<1> data output.                                                                                                                              |  |  |  |  |  |  |  |

|              |                   | 1               | -   | ST          | PORTD<1> data input.                                                                                                                              |  |  |  |  |  |  |  |

|              | PSP1              | x               | 0   | DIG         | PSP read data output (LATD<1>); takes priority over port data.                                                                                    |  |  |  |  |  |  |  |

|              |                   | x               | -   | TTL         | PSP write data input.                                                                                                                             |  |  |  |  |  |  |  |

| RD2/PSP2     | RD2               | 0               | 0   | DIG         | LATD<2> data output.                                                                                                                              |  |  |  |  |  |  |  |

|              |                   | 1               | I   | ST          | PORTD<2> data input.                                                                                                                              |  |  |  |  |  |  |  |

|              | PSP2              | x               | 0   | DIG         | PSP read data output (LATD<2>); takes priority over port data.                                                                                    |  |  |  |  |  |  |  |

|              |                   | x               | Ι   | TTL         | PSP write data input.                                                                                                                             |  |  |  |  |  |  |  |

| RD3/PSP3     | RD3               | 0               | 0   | DIG         | LATD<3> data output.                                                                                                                              |  |  |  |  |  |  |  |

|              |                   | 1               | Ι   | ST          | PORTD<3> data input.                                                                                                                              |  |  |  |  |  |  |  |

|              | PSP3              | x               | 0   | DIG         | PSP read data output (LATD<3>); takes priority over port data.                                                                                    |  |  |  |  |  |  |  |

|              |                   | x               | I   | TTL         | PSP write data input.                                                                                                                             |  |  |  |  |  |  |  |

| RD4/PSP4     | RD4               | 0               | 0   | DIG         | LATD<4> data output.                                                                                                                              |  |  |  |  |  |  |  |

|              |                   | 1               | Ι   | ST          | PORTD<4> data input.                                                                                                                              |  |  |  |  |  |  |  |

|              | PSP4              | x               | 0   | DIG         | PSP read data output (LATD<4>); takes priority over port data.                                                                                    |  |  |  |  |  |  |  |

|              |                   | x               | -   | TTL         | PSP write data input.                                                                                                                             |  |  |  |  |  |  |  |

| RD5/PSP5/P1B | RD5               | 0               | 0   | DIG         | LATD<5> data output.                                                                                                                              |  |  |  |  |  |  |  |

|              |                   | 1               | I   | ST          | PORTD<5> data input.                                                                                                                              |  |  |  |  |  |  |  |

|              | PSP5              | x               | 0   | DIG         | PSP read data output (LATD<5>); takes priority over port data.                                                                                    |  |  |  |  |  |  |  |

|              |                   | x               | Ι   | TTL         | PSP write data input.                                                                                                                             |  |  |  |  |  |  |  |

|              | P1B               | 0               | 0   | DIG         | ECCP1 Enhanced PWM output, channel B; takes priority over port and PSP data. May be configured for tri-state during Enhanced PWM shutdown events. |  |  |  |  |  |  |  |

| RD6/PSP6/P1C | RD6               | 0               | 0   | DIG         | LATD<6> data output.                                                                                                                              |  |  |  |  |  |  |  |

|              |                   | 1               | Ι   | ST          | PORTD<6> data input.                                                                                                                              |  |  |  |  |  |  |  |

|              | PSP6              | x               | 0   | DIG         | PSP read data output (LATD<6>); takes priority over port data.                                                                                    |  |  |  |  |  |  |  |

|              |                   | x               | -   | TTL         | PSP write data input.                                                                                                                             |  |  |  |  |  |  |  |

|              | P1C               | 0               | 0   | DIG         | ECCP1 Enhanced PWM output, channel C; takes priority over port and PSP data. May be configured for tri-state during Enhanced PWM shutdown events. |  |  |  |  |  |  |  |

| RD7/PSP7/P1D | RD7               | 0               | 0   | DIG         | LATD<7> data output.                                                                                                                              |  |  |  |  |  |  |  |

|              |                   | 1               | -   | ST          | PORTD<7> data input.                                                                                                                              |  |  |  |  |  |  |  |

|              | PSP7              | x               | 0   | DIG         | PSP read data output (LATD<7>); takes priority over port data.                                                                                    |  |  |  |  |  |  |  |

|              |                   | x               | I   | TTL         | PSP write data input.                                                                                                                             |  |  |  |  |  |  |  |

|              | P1D               | 0               | 0   | DIG         | ECCP1 Enhanced PWM output, channel D; takes priority over port and PSP data. May be configured for tri-state during Enhanced PWM shutdown events. |  |  |  |  |  |  |  |

| TABLE 10-7: | PORTD I/O SUMMARY |

|-------------|-------------------|

|             |                   |

Legend: DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

# PIC18F2420/2520/4420/4520

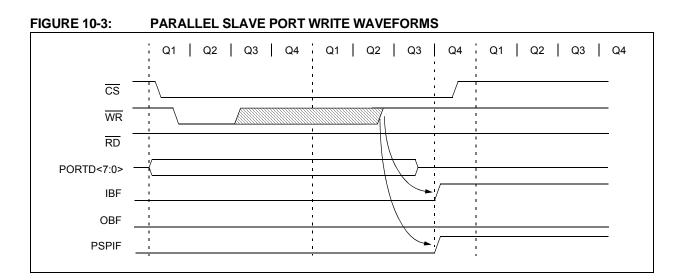

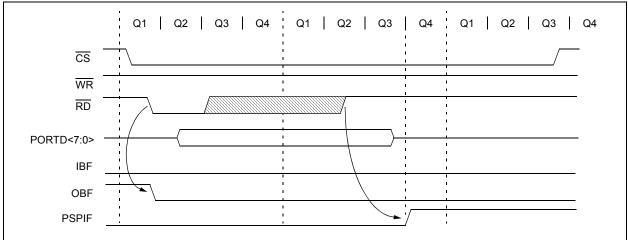

#### FIGURE 10-4: PARALLEL SLAVE PORT READ WAVEFORMS

#### TABLE 10-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Name   | Bit 7    | Bit 6          | Bit 5        | Bit 4        | Bit 3      | Bit 2     | Bit 1       | Bit 0  | Reset<br>Values<br>on page |

|--------|----------|----------------|--------------|--------------|------------|-----------|-------------|--------|----------------------------|

| PORTD  | RD7      | RD6            | RD5          | RD4          | RD3        | RD2       | RD1         | RD0    | 52                         |

| LATD   | PORTD Da | ita Latch Reg  | jister (Read | and Write to | Data Latch | )         |             |        | 52                         |

| TRISD  | PORTD Da | ta Direction I | Register     |              |            |           |             |        | 52                         |

| PORTE  | —        | —              | —            | _            | RE3        | RE2       | RE1         | RE0    | 52                         |

| LATE   | —        | _              | _            | _            | _          | LATE Data | Latch Regis | ster   | 52                         |

| TRISE  | IBF      | OBF            | IBOV         | PSPMODE      | —          | TRISE2    | TRISE1      | TRISE0 | 52                         |

| INTCON | GIE/GIEH | PEIE/GIEL      | TMR0IF       | INTOIE       | RBIE       | TMR0IF    | INT0IF      | RBIF   | 49                         |

| PIR1   | PSPIF    | ADIF           | RCIF         | TXIF         | SSPIF      | CCP1IF    | TMR2IF      | TMR1IF | 52                         |

| PIE1   | PSPIE    | ADIE           | RCIE         | TXIE         | SSPIE      | CCP1IE    | TMR2IE      | TMR1IE | 52                         |

| IPR1   | PSPIP    | ADIP           | RCIP         | TXIP         | SSPIP      | CCP1IP    | TMR2IP      | TMR1IP | 52                         |

| ADCON1 | —        | —              | VCFG1        | VCFG0        | PCFG3      | PCFG2     | PCFG1       | PCFG0  | 51                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

#### 11.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS<2:0> bits (T0CON<3:0>) which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256 in power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count but will not change the prescaler     |

|       | assignment.                                 |

#### 11.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

### 11.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before reenabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| Name   | Bit 7                      | Bit 6              | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on page |  |  |  |  |  |

|--------|----------------------------|--------------------|--------|--------|-------|--------|--------|-------|----------------------------|--|--|--|--|--|

| TMR0L  | L Timer0 Register Low Byte |                    |        |        |       |        |        |       |                            |  |  |  |  |  |

| TMR0H  | Timer0 Reg                 | ister High By      | /te    |        |       |        |        |       | 50                         |  |  |  |  |  |

| INTCON | GIE/GIEH                   | PEIE/GIEL          | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  | 49                         |  |  |  |  |  |

| TOCON  | TMR0ON                     | T08BIT             | TOCS   | T0SE   | PSA   | T0PS2  | T0PS1  | T0PS0 | 50                         |  |  |  |  |  |

| TRISA  | RA7 <sup>(1)</sup>         | RA6 <sup>(1)</sup> | RA5    | RA4    | RA3   | RA2    | RA1    | RA0   | 52                         |  |  |  |  |  |

TABLE 11-1:

REGISTERS ASSOCIATED WITH TIMER0

Legend: Shaded cells are not used by Timer0.

**Note 1:** PORTA<7:6> and their direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

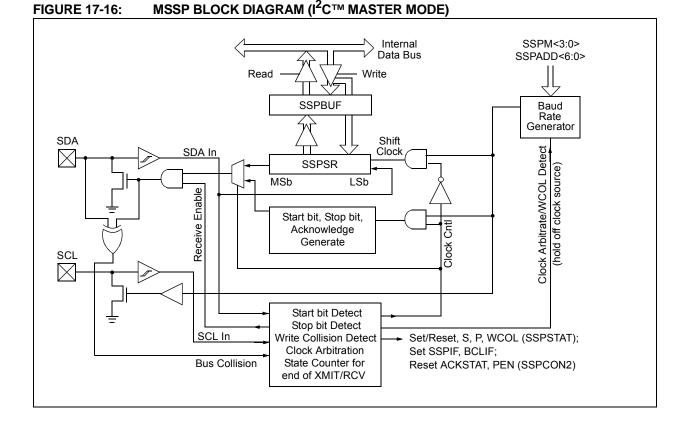

#### 17.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause the MSSP Interrupt Flag bit, SSPIF, to be set (MSSP interrupt, if enabled):

- Start condition

- Stop condition

- · Data transfer byte transmitted/received

- · Acknowledge transmit

- Repeated Start

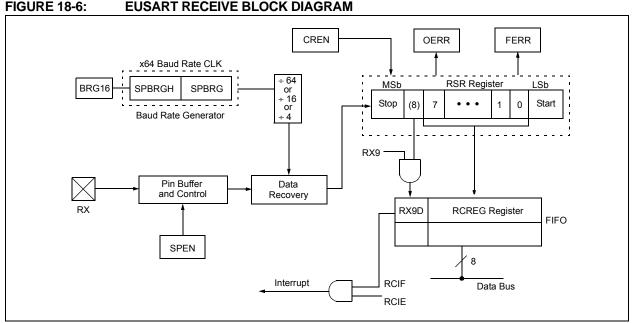

#### EUSART ASYNCHRONOUS 18.2.2 RECEIVER

The receiver block diagram is shown in Figure 18-6. The data is received on the RX pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- Initialize the SPBRGH:SPBRG registers for the 1. appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, RCIE.

- If 9-bit reception is desired, set bit, RX9. 4

- 5. Enable the reception by setting bit, CREN.

- 6. Flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if enable bit, RCIE, was set.

- 7. Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit, CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### **FIGURE 18-6:**

#### SETTING UP 9-BIT MODE WITH 18.2.3 ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH:SPBRG registers for the 1. appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- If interrupts are required, set the RCEN bit and 3. select the desired priority level with the RCIP bit.

- Set the RX9 bit to enable 9-bit reception. 4.

- 5. Set the ADDEN bit to enable address detect.

- Enable reception by setting the CREN bit. 6.

- 7. The RCIF bit will be set when reception is complete. The interrupt will be Acknowledged if the RCIE and GIE bits are set.

- Read the RCSTA register to determine if any 8. error occurred during reception, as well as read bit 9 of data (if applicable).

- Read RCREG to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

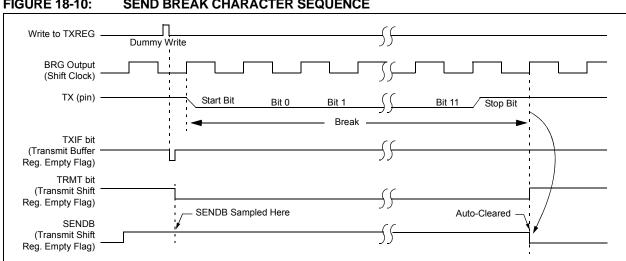

#### 18.2.5 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift register is loaded with data. Note that the value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

Note that the data value written to the TXREG for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 18-10 for the timing of the Break character sequence.

#### 18.2.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN bus master.

- Configure the EUSART for the desired mode. 1.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- Write '55h' to TXREG to load the Sync character 4. into the transmit FIFO buffer.

- After the Break has been sent, the SENDB bit is 5. reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### 18.2.6 **RECEIVING A BREAK CHARACTER**

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in Section 18.2.4 "Auto-Wake-up on Sync Break Character". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABD bit once the TXIF interrupt is observed.

#### **FIGURE 18-10:** SEND BREAK CHARACTER SEQUENCE

#### 18.3 EUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTA<4>). In addition, enable bit, SPEN (RCSTA<7>), is set in order to configure the TX and RX pins to CK (clock) and DT (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK line. Clock polarity is selected with the TXCKP bit (BAUDCON<4>); setting TXCKP sets the Idle state on CK as high, while clearing the bit sets the Idle state as low. This option is provided to support Microwire devices with this module.

#### 18.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 18-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available).

Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG is empty and the TXIF flag bit (PIR1<4>) is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF is set regardless of the state of enable bit, TXIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREG register.

While flag bit, TXIF, indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

|                            | Q1Q2Q      | 23Q4 Q1Q2   | Q3Q4 Q1Q2   | Q3Q4 Q1Q2  | Q3Q4Q1Q   | 2 Q3 Q4     | Q3Q4 C       | 1Q2Q3Q4 | Q1Q2Q30          | 24 Q1 Q2Q3Q4      | Q1Q2Q3Q4    | Q1 Q2 Q3 Q4   | Q1Q2Q3      | Q4      |

|----------------------------|------------|-------------|-------------|------------|-----------|-------------|--------------|---------|------------------|-------------------|-------------|---------------|-------------|---------|

| RC7/RX/DT                  |            |             | bit 0       | bit 1      |           | 2           | ->- <u>+</u> | bit 7   | bit 0 X          | bit 1 X           | <u> </u>    |               | bit 7       |         |

| RC6/TX/CK (<br>(TXCKP = 0) | ; <u> </u> |             |             |            |           |             | ;            |         |                  |                   | <u>-</u>    | <u> </u>      |             |         |

| RC6/TX/CK<br>(TXCKP = 1)   |            |             |             |            | ╶┊┚       | <u></u>     | -Ļ           |         |                  | ļ                 | Ļ.          |               |             |         |

| Write to<br>TXREG Reg      |            | Write W     | ord 1       | Write Wor  | d 2       |             | 1<br>1<br>1  |         | 1<br>1<br>1      | <u> </u><br> <br> | 1<br>1<br>1 | -55           | 1<br>1<br>1 | -'      |

| TXIF bit<br>(Interrupt Fla | g)         | <br>        |             |            | <u>∼¦</u> |             |              |         | :ſ               |                   | <br> <br>   | <u></u>       | ;<br>;      | _;<br>; |

| TRMT bit                   |            | 1           | 1<br>1<br>1 |            |           |             |              |         | ,<br>1<br>1<br>1 | <br> <br> <br>    | 1<br>1<br>1 | <del>}}</del> | ļ           |         |

| TXEN bit                   | <u>'1'</u> | 1<br>1<br>1 | 1<br>1<br>1 |            |           | <u>{</u> }  |              |         | 1<br>1           | •<br>•            | 1<br>1<br>1 | <u>}</u>      | ۱ ،<br>۱    | 1'      |

| Note: Syn                  | c Maste    | r mode, S   | PBRG = 0,   | continuous | transmis  | sion of two | 8-bit woi    | rds.    |                  |                   |             |               |             |         |

FIGURE 18-11: SYNCHRONOUS TRANSMISSION

#### 19.4 Operation in Power-Managed Modes

The selection of the automatic acquisition time and A/D conversion clock is determined in part by the clock source and frequency while in a power-managed mode.

If the A/D is expected to operate while the device is in a power-managed mode, the ACQT<2:0> and ADCS<2:0> bits in ADCON2 should be updated in accordance with the clock source to be used in that mode. After entering the mode, an A/D acquisition or conversion may be started. Once started, the device should continue to be clocked by the same clock source until the conversion has been completed.

If desired, the device may be placed into the corresponding Idle mode during the conversion. If the device clock frequency is less than 1 MHz, the A/D RC clock source should be selected.

Operation in Sleep mode requires the A/D FRC clock to be selected. If the ACQT<2:0> bits are set to '000' and a conversion is started, the conversion will be delayed one instruction cycle to allow execution of the SLEEP instruction and entry to Sleep mode. The IDLEN bit (OSCCON<7>) must have already been cleared prior to starting the conversion.

### 19.5 Configuring Analog Port Pins

The ADCON1, TRISA, TRISB and TRISE registers all configure the A/D port pins. The port pins needed as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<3:0> bits and the TRIS bits.

- Note 1: When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert as analog inputs. Analog levels on a digitally configured input will be accurately converted.

- 2: Analog levels on any pin defined as a digital input may cause the digital input buffer to consume current out of the device's specification limits.

- 3: The PBADEN bit, in Configuration Register 3H, configures PORTB pins to reset as analog or digital pins by controlling how the PCFG bits in ADCON1 are reset.

| REGISTER 23-4: CON | NFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h) |

|--------------------|--------------------------------------------------------------|

|--------------------|--------------------------------------------------------------|

| R/P-1          | U-0                       | U-0               | U-0              | U-0          | R/P-0            | R/P-1      | R/P-1  |

|----------------|---------------------------|-------------------|------------------|--------------|------------------|------------|--------|

| MCLRE          | —                         | —                 | _                | _            | LPT1OSC          | PBADEN     | CCP2MX |

| bit 7          | •                         |                   |                  |              |                  |            | bit 0  |

|                |                           |                   |                  |              |                  |            |        |

| Legend:        |                           |                   |                  |              |                  |            |        |

| R = Readable b | bit                       | P = Programm      | nable bit        | U = Unimpler | mented bit, read | as '0'     |        |

| -n = Value whe | n device is unp           | programmed        |                  | u = Unchang  | ed from progran  | nmed state |        |

|                |                           |                   |                  |              |                  |            |        |

| bit 7          | MCLRE: MCL                | R Pin Enable      | bit              |              |                  |            |        |

|                | $1 = \overline{MCLR}$ pin | enabled; RE3      | input pin disa   | bled         |                  |            |        |

|                | 0 = RE3 input             | pin enabled; N    | ICLR disable     | d            |                  |            |        |

| bit 6-3        | Unimplement               | ted: Read as '    | o'               |              |                  |            |        |

| bit 2          | LPT1OSC: Lo               | ow-Power Time     | er1 Oscillator E | Enable bit   |                  |            |        |

|                |                           | onfigured for lov |                  |              |                  |            |        |

|                | 0 = Timer1 co             | onfigured for hig | gher power op    | eration      |                  |            |        |

| bit 1          | /                         | RTB A/D Enat      |                  |              |                  |            |        |

|                | •                         |                   |                  |              | B<4:0> pin confi | •          |        |

|                |                           | •                 | •                | • •          | annels on Rese   | t          |        |

| <b>h</b> # 0   |                           | 1:0> pins are co  | Singuleu as u    |              | esei             |            |        |

| bit 0          | CCP2MX: CC                |                   |                  | 504          |                  |            |        |

|                |                           | ut/output is mu   |                  |              |                  |            |        |

|                | $0 = CCP2 \ln p$          | ut/output is mu   | inplexed with    | RDJ          |                  |            |        |

### REGISTER 23-5: CONFIG4L: CONFIGURATION REGISTER 4 LOW (BYTE ADDRESS 300006h)

| R/P-1 | R/P-0 | U-0 | U-0 | U-0 | R/P-1 | U-0 | R/P-1  |

|-------|-------|-----|-----|-----|-------|-----|--------|

| DEBUG | XINST | —   | _   | _   | LVP   | _   | STVREN |

| bit 7 |       |     |     |     |       |     | bit 0  |

| Legend:                   |                      |                                     |

|---------------------------|----------------------|-------------------------------------|

| R = Readable bit          | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device is | unprogrammed         | u = Unchanged from programmed state |

|                           |                      |                                     |

| DEBUG: Background Debugger Enable bit                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1 = Background debugger disabled, RB6 and RB7 configured as general purpose I/O pins</li> <li>0 = Background debugger enabled, RB6 and RB7 are dedicated to In-Circuit Debug</li> </ul> |

| XINST: Extended Instruction Set Enable bit                                                                                                                                                       |

| <ul> <li>1 = Instruction set extension and Indexed Addressing mode enabled</li> <li>0 = Instruction set extension and Indexed Addressing mode disabled (Legacy mode)</li> </ul>                  |

| Unimplemented: Read as '0'                                                                                                                                                                       |

| LVP: Single-Supply ICSP™ Enable bit<br>1 = Single-Supply ICSP enabled<br>0 = Single-Supply ICSP disabled                                                                                         |

| Unimplemented: Read as '0'                                                                                                                                                                       |

| <b>STVREN:</b> Stack Full/Underflow Reset Enable bit<br>1 = Stack full/underflow will cause Reset<br>0 = Stack full/underflow will not cause Reset                                               |

|                                                                                                                                                                                                  |

# PIC18F2420/2520/4420/4520

| RET         | URN                          | Return fro                                                                                  | om Subrouti                                                                                                                                             | ne                                                                         | RL         | CF                               | Rotate Le                                                                                                                                  | ft f through                                                                                                                   | Carry                                                                                              |

|-------------|------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Synta       | ax:                          | RETURN {s}                                                                                  |                                                                                                                                                         | Syn                                                                        | tax:       | RLCF f {,d {,a}}                 |                                                                                                                                            |                                                                                                                                |                                                                                                    |

| Oper        | ands:                        | s ∈ [0,1]                                                                                   |                                                                                                                                                         |                                                                            | Ope        | rands:                           | $0 \leq f \leq 255$                                                                                                                        |                                                                                                                                |                                                                                                    |

| Oper        | ation:                       | $(TOS) \rightarrow PO$                                                                      | С;                                                                                                                                                      |                                                                            |            |                                  | d ∈ [0,1]                                                                                                                                  |                                                                                                                                |                                                                                                    |

|             |                              | $(BSRS) \rightarrow I$                                                                      | $\rightarrow$ STATUS,<br>BSR,<br>CLATH are un                                                                                                           | changed                                                                    | ·          | ration:<br>us Affected:          | $a \in [0,1]$<br>(f <n>) → de<br/>(f&lt;7&gt;) → C<br/>(C) → dest<br/>C, N, Z</n>                                                          | 3                                                                                                                              |                                                                                                    |

| Statu       | s Affected:                  | None                                                                                        |                                                                                                                                                         | Ū                                                                          |            |                                  |                                                                                                                                            | 0.1.1 5.5                                                                                                                      |                                                                                                    |

| Enco        | dina:                        | 0000                                                                                        | 0000 000                                                                                                                                                | 001s                                                                       |            | oding:<br>cription:              | 0011                                                                                                                                       | 01da ffi                                                                                                                       |                                                                                                    |

| Desc        | ription:                     | popped and<br>is loaded in<br>'s'= 1, the c<br>registers, W<br>are loaded i<br>registers, W | a subroutine. T<br>I the top of the<br>to the program<br>ontents of the<br>/S, STATUSS<br>into their corre<br>/, STATUS and<br>pdate of these<br>ault). | stack (TOS)<br>counter. If<br>shadow<br>and BSRS,<br>sponding<br>d BSR. If | Des        |                                  | one bit to th<br>flag. If 'd' is<br>W. If 'd' is '<br>in register '<br>If 'a' is 'o', t<br>selected. If<br>select the C<br>If 'a' is 'o' a | he left through<br>('0', the result<br>1', the result is<br>f' (default).<br>he Access Ba<br>(a' is '1', the B<br>GPR bank (de | the Carry<br>is placed in<br>s stored back<br>onk is<br>SR is used to<br>fault).<br>ed instruction |

| Word        | ls:                          | 1                                                                                           |                                                                                                                                                         |                                                                            |            |                                  | •                                                                                                                                          | Indexed Liter                                                                                                                  |                                                                                                    |

| Cycle       | es:                          | 2                                                                                           |                                                                                                                                                         |                                                                            |            |                                  | -                                                                                                                                          | mode whene<br>See <b>Section</b> .                                                                                             |                                                                                                    |

| QC          | ycle Activity:               |                                                                                             |                                                                                                                                                         |                                                                            |            |                                  | "Byte-Orie                                                                                                                                 | nted and Bit-                                                                                                                  | Oriented                                                                                           |

|             | Q1                           | Q2                                                                                          | Q3                                                                                                                                                      | Q4                                                                         |            |                                  | Instruction<br>Mode" for o                                                                                                                 |                                                                                                                                | Literal Offset                                                                                     |

|             | Decode                       | No<br>operation                                                                             | Process<br>Data                                                                                                                                         | POP PC<br>from stack                                                       |            |                                  |                                                                                                                                            | - registe                                                                                                                      | er f                                                                                               |

|             | No<br>operation              | No<br>operation                                                                             | No<br>operation                                                                                                                                         | No<br>operation                                                            | Wor        | ds:                              | 1                                                                                                                                          |                                                                                                                                |                                                                                                    |

|             |                              |                                                                                             |                                                                                                                                                         |                                                                            | Сус        | les:                             | 1                                                                                                                                          |                                                                                                                                |                                                                                                    |

| _           |                              |                                                                                             |                                                                                                                                                         |                                                                            | Q(         | Cycle Activity:                  |                                                                                                                                            |                                                                                                                                |                                                                                                    |

| <u>Exan</u> |                              | RETURN                                                                                      |                                                                                                                                                         |                                                                            |            | Q1                               | Q2                                                                                                                                         | Q3                                                                                                                             | Q4                                                                                                 |

|             | After Instruction<br>PC = To |                                                                                             |                                                                                                                                                         |                                                                            |            | Decode                           | Read<br>register 'f'                                                                                                                       | Process<br>Data                                                                                                                | Write to destination                                                                               |

|             |                              |                                                                                             |                                                                                                                                                         |                                                                            | <u>Exa</u> | mple:                            | RLCF                                                                                                                                       | REG, 0,                                                                                                                        | 0                                                                                                  |

|             |                              |                                                                                             |                                                                                                                                                         |                                                                            |            | Before Instru<br>REG<br>C        | ction<br>= 1110 0<br>= 0                                                                                                                   | 110                                                                                                                            |                                                                                                    |

|             |                              |                                                                                             |                                                                                                                                                         |                                                                            |            | After Instructi<br>REG<br>W<br>C | ion<br>= 1110 0<br>= 1100 1<br>= 1                                                                                                         |                                                                                                                                |                                                                                                    |

|             |                              |                                                                                             |                                                                                                                                                         |                                                                            |            |                                  |                                                                                                                                            |                                                                                                                                |                                                                                                    |

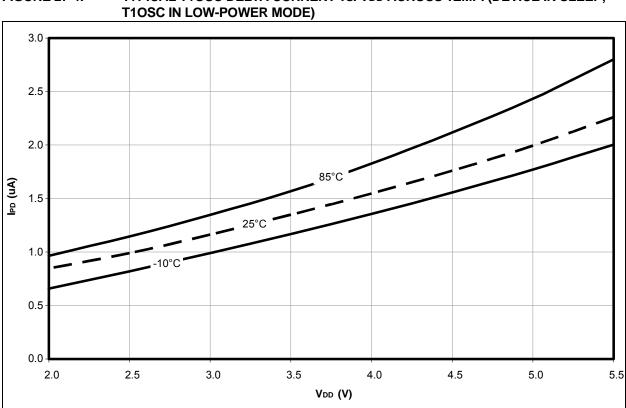

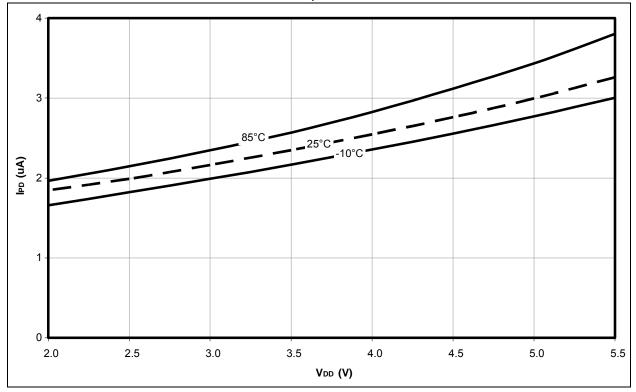

#### 26.2 DC Characteristics: Power-Down and Supply Current PIC18F2420/2520/4420/4520 (Industrial) PIC18LF2420/2520/4420/4520 (Industrial) (Continued)

| PIC18LF2420/2520/4420/4520<br>(Industrial)<br>PIC18F2420/2520/4420/4520<br>(Industrial, Extended)<br>Param<br>No. Device |                       | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrialStandard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for extended |                                     |    |        |             |                                      |  |  |     |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----|--------|-------------|--------------------------------------|--|--|-----|

|                                                                                                                          |                       |                                                                                                                                                                                                                                                                                                                                     |                                     |    |        |             |                                      |  |  | Тур |

|                                                                                                                          |                       |                                                                                                                                                                                                                                                                                                                                     | Supply Current (IDD) <sup>(2)</sup> |    |        |             |                                      |  |  |     |

|                                                                                                                          | PIC18LF2X2X/4X20      | 250                                                                                                                                                                                                                                                                                                                                 | 350                                 | μA | -40°C  |             |                                      |  |  |     |

|                                                                                                                          |                       | 260                                                                                                                                                                                                                                                                                                                                 | 350                                 | μΑ | +25°C  | VDD = 2.0V  |                                      |  |  |     |

|                                                                                                                          |                       | 250                                                                                                                                                                                                                                                                                                                                 | 350                                 | μΑ | +85°C  | ]           |                                      |  |  |     |

|                                                                                                                          | PIC18LF2X2X/4X20      | 550                                                                                                                                                                                                                                                                                                                                 | 650                                 | μΑ | -40°C  |             |                                      |  |  |     |

|                                                                                                                          |                       | 480                                                                                                                                                                                                                                                                                                                                 | 640                                 | μΑ | +25°C  | VDD = 3.0V  | Fosc = 1 MHz                         |  |  |     |

|                                                                                                                          |                       | 460                                                                                                                                                                                                                                                                                                                                 | 600                                 | μΑ | +85°C  |             | ( <b>PRI_RUN</b> ,<br>EC oscillator) |  |  |     |

|                                                                                                                          | All devices           | 1.2                                                                                                                                                                                                                                                                                                                                 | 1.5                                 | mA | -40°C  |             |                                      |  |  |     |

|                                                                                                                          |                       | 1.1                                                                                                                                                                                                                                                                                                                                 | 1.4                                 | mA | +25°C  | VDD = 5.0V  |                                      |  |  |     |

|                                                                                                                          |                       | 1.0                                                                                                                                                                                                                                                                                                                                 | 1.3                                 | mA | +85°C  | י0.0 – 5.00 |                                      |  |  |     |

|                                                                                                                          | Extended devices only | 1.0                                                                                                                                                                                                                                                                                                                                 | 3.0                                 | mA | +125°C |             |                                      |  |  |     |

|                                                                                                                          | PIC18LF2X2X/4X20      | 0.72                                                                                                                                                                                                                                                                                                                                | 1.0                                 | mA | -40°C  |             |                                      |  |  |     |

|                                                                                                                          |                       | 0.74                                                                                                                                                                                                                                                                                                                                | 1.0                                 | mA | +25°C  | VDD = 2.0V  |                                      |  |  |     |

|                                                                                                                          |                       | 0.74                                                                                                                                                                                                                                                                                                                                | 1.0                                 | mA | +85°C  |             |                                      |  |  |     |