Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2420-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                       | Pin Nu         | ımber | Dim               | Buffer             |                                                                                                                                          |

|-------------------------------------------------------|----------------|-------|-------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                              | SPDIP,<br>SOIC | QFN   | Pin<br>Type       |                    | Description                                                                                                                              |

|                                                       |                |       |                   |                    | PORTC is a bidirectional I/O port.                                                                                                       |

| RC0/T1OSO/T13CKI<br>RC0<br>T1OSO<br>T13CKI            | 11             | 8     | I/O<br>O<br>I     | ST<br>—<br>ST      | Digital I/O.<br>Timer1 oscillator output.<br>Timer1/Timer3 external clock input.                                                         |

| RC1/T1OSI/CCP2<br>RC1<br>T1OSI<br>CCP2 <sup>(2)</sup> | 12             | 9     | I/O<br>I<br>I/O   | ST<br>Analog<br>ST | Digital I/O.<br>Timer1 oscillator input.<br>Capture 2 input/Compare 2 output/PWM2 output.                                                |

| RC2/CCP1<br>RC2<br>CCP1                               | 13             | 10    | I/O<br>I/O        | ST<br>ST           | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM1 output.                                                                            |

| RC3/SCK/SCL<br>RC3<br>SCK<br>SCL                      | 14             | 11    | I/O<br>I/O<br>I/O | ST<br>ST<br>ST     | Digital I/O.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C™ mode. |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA                      | 15             | 12    | I/O<br>I<br>I/O   | ST<br>ST<br>ST     | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                                                                               |

| RC5/SDO<br>RC5<br>SDO                                 | 16             | 13    | I/O<br>O          | ST<br>—            | Digital I/O.<br>SPI data out.                                                                                                            |

| RC6/TX/CK<br>RC6<br>TX<br>CK                          | 17             | 14    | I/O<br>O<br>I/O   | ST<br>—<br>ST      | Digital I/O.<br>EUSART asynchronous transmit.<br>EUSART synchronous clock (see related RX/DT).                                           |

| RC7/RX/DT<br>RC7<br>RX<br>DT                          | 18             | 15    | I/O<br>I<br>I/O   | ST<br>ST<br>ST     | Digital I/O.<br>EUSART asynchronous receive.<br>EUSART synchronous data (see related TX/CK).                                             |

| RE3                                                   | —              |       |                   |                    | See MCLR/VPP/RE3 pin.                                                                                                                    |

| Vss                                                   | 8, 19          | 5, 16 | Р                 | _                  | Ground reference for logic and I/O pins.                                                                                                 |

| Vdd                                                   | 20             | 17    | Р                 | _                  | Positive supply for logic and I/O pins.                                                                                                  |

= Power

### TABLE 1-2: PIC18F2420/2520 PINOUT I/O DESCRIPTIONS (CONTINUED)

O = Output P

**Note 1:** Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

### 4.5 Device Reset Timers

PIC18F2420/2520/4420/4520 devices incorporate three separate on-chip timers that help regulate the Power-on Reset process. Their main function is to ensure that the device clock is stable before code is executed. These timers are:

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- PLL Lock Time-out

### 4.5.1 POWER-UP TIMER (PWRT)

The Power-up Timer (PWRT) of PIC18F2420/2520/ 4420/4520 devices is an 11-bit counter which uses the INTRC source as the clock input. This yields an approximate time interval of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip to chip due to temperature and process variation. See DC parameter 33 for details.

The PWRT is enabled by clearing the PWRTEN Configuration bit.

### 4.5.2 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter 33). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP, HS and HSPLL modes and only on Power-on Reset, or on exit from most power-managed modes.

### 4.5.3 PLL LOCK TIME-OUT

With the PLL enabled in its PLL mode, the time-out sequence following a Power-on Reset is slightly different from other oscillator modes. A separate timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

### 4.5.4 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows:

- 1. After the POR pulse has cleared, PWRT time-out is invoked (if enabled).

- 2. Then, the OST is activated.

The total time-out will vary based on oscillator configuration and the status of the PWRT. Figure 4-3, Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7 all depict time-out sequences on power-up, with the Power-up Timer enabled and the device operating in HS Oscillator mode. Figure 4-3 through Figure 4-6 also apply to devices operating in XT or LP modes. For devices in RC mode and with the PWRT disabled, on the other hand, there will be no time-out at all.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, all time-outs will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 4-5). This is useful for testing purposes or to synchronize more than one PIC18FXXXX device operating in parallel.

| Oscillator     | Power-up <sup>(2)</sup> a                              | Exit from                       |                                 |  |

|----------------|--------------------------------------------------------|---------------------------------|---------------------------------|--|

| Configuration  | <b>PWRTEN</b> = 0                                      | <b>PWRTEN =</b> 1               | Power-Managed Mode              |  |

| HSPLL          | 66 ms <sup>(1)</sup> + 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> |  |

| HS, XT, LP     | 66 ms <sup>(1)</sup> + 1024 Tosc                       | 1024 Tosc                       | 1024 Tosc                       |  |

| EC, ECIO       | 66 ms <sup>(1)</sup>                                   | —                               | —                               |  |

| RC, RCIO       | 66 ms <sup>(1)</sup>                                   | _                               | —                               |  |

| INTIO1, INTIO2 | 66 ms <sup>(1)</sup>                                   | _                               | —                               |  |

TABLE 4-2:TIME-OUT IN VARIOUS SITUATIONS

**Note 1:** 66 ms (65.5 ms) is the nominal Power-up Timer (PWRT) delay.

2: 2 ms is the nominal time required for the PLL to lock.

### 5.1.1 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and is contained in three separate 8-bit registers. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits; it is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCH register. Updates to the PCU register are performed through the PCLATH register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the program counter by any operation that writes PCL. Similarly, the upper two bytes of the program counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 5.1.4.1 "Computed GOTO"**).

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

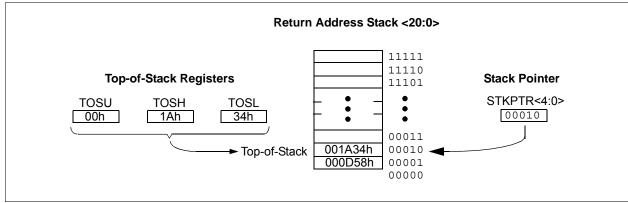

### 5.1.2 RETURN ADDRESS STACK

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC is pushed onto the stack when a CALL or RCALL instruction is executed or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the Top-of-Stack (TOS) Special Function Registers. Data can also be pushed to, or popped from the stack, using these registers.

A CALL type instruction causes a push onto the stack; the Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack; the contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full, or has overflowed or underflowed.

### 5.1.2.1 Top-of-Stack Access

Only the top of the return address stack (TOS) is readable and writable. A set of three registers, TOSU:TOSH:TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 5-2). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

The user must disable the global interrupt enable bits while accessing the stack to prevent inadvertent stack corruption.

### FIGURE 5-2: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

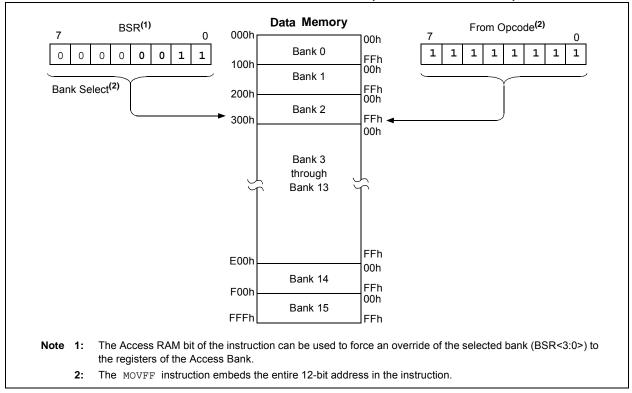

### FIGURE 5-7: USE OF THE BANK SELECT REGISTER (DIRECT ADDRESSING)

### 5.3.2 ACCESS BANK

While the use of the BSR with an embedded 8-bit address allows users to address the entire range of data memory, it also means that the user must always ensure that the correct bank is selected. Otherwise, data may be read from or written to the wrong location. This can be disastrous if a GPR is the intended target of an operation, but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 128 bytes of memory (00h-7Fh) in Bank 0 and the last 128 bytes of memory (80h-FFh) in Block 15. The lower half is known as the "Access RAM" and is composed of GPRs. This upper half is also where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figure 5-5).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0',

however, the instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle, without updating the BSR first. For 8-bit addresses of 80h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 80h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 5.5.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

### 5.3.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM, which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

# REGISTER 9-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

| R/W-0         | R/W-0                                                                                                                                                          | U-0                                                                                                                                 | R/W-0           | R/W-0                    | R/W-0            | R/W-0           | R/W-0    |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------|------------------|-----------------|----------|--|--|--|

| OSCFIF        | CMIF                                                                                                                                                           |                                                                                                                                     | EEIF            | BCLIF                    | HLVDIF           | TMR3IF          | CCP2IF   |  |  |  |

| bit 7         |                                                                                                                                                                |                                                                                                                                     |                 | ·                        | ·                |                 | bit (    |  |  |  |

| Legend:       |                                                                                                                                                                |                                                                                                                                     |                 |                          |                  |                 |          |  |  |  |

| R = Readabl   | le bit                                                                                                                                                         | W = Writable                                                                                                                        | bit             | U = Unimplen             | nented bit, read | d as '0'        |          |  |  |  |

| -n = Value at | POR                                                                                                                                                            | '1' = Bit is set                                                                                                                    |                 | '0' = Bit is clea        | ared             | x = Bit is unkr | nown     |  |  |  |

| bit 7         | OSCFIF: Osc                                                                                                                                                    | illator Fail Inter                                                                                                                  | rupt Flag bit   |                          |                  |                 |          |  |  |  |

|               | 1 = Device os<br>0 = Device cl                                                                                                                                 |                                                                                                                                     | clock input has | changed to IN            | TOSC (must b     | e cleared in so | ftware)  |  |  |  |

| bit 6         | CMIF: Compa                                                                                                                                                    | arator Interrupt                                                                                                                    | Flag bit        |                          |                  |                 |          |  |  |  |

|               |                                                                                                                                                                | tor input has cl<br>tor input has n                                                                                                 |                 | be cleared in so         | oftware)         |                 |          |  |  |  |

| bit 5         | Unimplement                                                                                                                                                    | ted: Read as '                                                                                                                      | )'              |                          |                  |                 |          |  |  |  |

| bit 4         | EEIF: Data EEPROM/Flash Write Operation Interrupt Flag bit                                                                                                     |                                                                                                                                     |                 |                          |                  |                 |          |  |  |  |

|               | <ul> <li>1 = The write operation is complete (must be cleared in software)</li> <li>0 = The write operation is not complete or has not been started</li> </ul> |                                                                                                                                     |                 |                          |                  |                 |          |  |  |  |

| bit 3         | BCLIF: Bus C                                                                                                                                                   | BCLIF: Bus Collision Interrupt Flag bit                                                                                             |                 |                          |                  |                 |          |  |  |  |

|               |                                                                                                                                                                | llision occurred<br>ollision occurre                                                                                                | •               | red in software          | )                |                 |          |  |  |  |

| bit 2         | HLVDIF: High/Low-Voltage Detect Interrupt Flag bit                                                                                                             |                                                                                                                                     |                 |                          |                  |                 |          |  |  |  |

|               |                                                                                                                                                                | w-voltage cond<br>w-voltage cond                                                                                                    |                 |                          | mined by VDIF    | RMAG bit, HLVI  | DCON<7>) |  |  |  |

| bit 1         | TMR3IF: TMR3 Overflow Interrupt Flag bit                                                                                                                       |                                                                                                                                     |                 |                          |                  |                 |          |  |  |  |

|               |                                                                                                                                                                | gister overflowe<br>gister did not o                                                                                                |                 | eared in softwar         | re)              |                 |          |  |  |  |

| bit 0         | CCP2IF: CCF                                                                                                                                                    | 2 Interrupt Fla                                                                                                                     | g bit           |                          |                  |                 |          |  |  |  |

|               | 1 = A TMR1                                                                                                                                                     | <u>Capture mode:</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred |                 |                          |                  |                 |          |  |  |  |

|               | Compare mod<br>1 = A TMR1                                                                                                                                      | de:                                                                                                                                 | re match occur  | rred (must be c<br>urred | leared in softw  | vare)           |          |  |  |  |

|               | <u>PWM mode:</u><br>Unused in this                                                                                                                             | s mode.                                                                                                                             |                 |                          |                  |                 |          |  |  |  |

| Pin                     | Function | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                                       |

|-------------------------|----------|-----------------|-----|-------------|-------------------------------------------------------------------------------------------------------------------|

| RA0/AN0                 | RA0      | 0               | 0   | DIG         | LATA<0> data output; not affected by analog input.                                                                |

|                         |          | 1               | -   | TTL         | PORTA<0> data input; disabled when analog input enabled.                                                          |

|                         | AN0      | 1               | Ι   | ANA         | A/D input channel 0 and comparator C1- input. Default input configuration on POR; does not affect digital output. |

| RA1/AN1                 | RA1      | 0               | 0   | DIG         | LATA<1> data output; not affected by analog input.                                                                |

|                         |          | 1               | -   | TTL         | PORTA<1> data input; disabled when analog input enabled.                                                          |

|                         | AN1      | 1               | -   | ANA         | A/D input channel 1 and comparator C2- input. Default input configuration on POR; does not affect digital output. |

| RA2/AN2/<br>Vref-/CVref | RA2      | 0               | 0   | DIG         | LATA<2> data output; not affected by analog input. Disabled when CVREF output enabled.                            |

|                         |          | 1               | I   | TTL         | PORTA<2> data input. Disabled when analog functions enabled; disabled when CVREF output enabled.                  |

|                         | AN2      | 1               | -   | ANA         | A/D input channel 2 and comparator C2+ input. Default input configuration on POR; not affected by analog output.  |

|                         | VREF-    | 1               | -   | ANA         | A/D and comparator voltage reference low input.                                                                   |

|                         | CVREF    | x               | 0   | ANA         | Comparator voltage reference output. Enabling this feature disables digital I/O.                                  |

| RA3/AN3/VREF+           | RA3      | 0               | 0   | DIG         | LATA<3> data output; not affected by analog input.                                                                |

|                         |          | 1               | Ι   | TTL         | PORTA<3> data input; disabled when analog input enabled.                                                          |

|                         | AN3      | 1               | I   | ANA         | A/D input channel 3 and comparator C1+ input. Default input configuration on POR.                                 |

|                         | VREF+    | 1               | Ι   | ANA         | A/D and comparator voltage reference high input.                                                                  |

| RA4/T0CKI/C1OUT         | RA4      | 0               | 0   | DIG         | LATA<4> data output.                                                                                              |

|                         |          | 1               | Ι   | ST          | PORTA<4> data input; default configuration on POR.                                                                |

|                         | TOCKI    | 1               | Ι   | ST          | Timer0 clock input.                                                                                               |

|                         | C10UT    | 0               | 0   | DIG         | Comparator 1 output; takes priority over port data.                                                               |

| RA5/AN4/SS/             | RA5      | 0               | 0   | DIG         | LATA<5> data output; not affected by analog input.                                                                |

| HLVDIN/C2OUT            |          | 1               | Ι   | TTL         | PORTA<5> data input; disabled when analog input enabled.                                                          |

|                         | AN4      | 1               | -   | ANA         | A/D input channel 4. Default configuration on POR.                                                                |

|                         | SS       | 1               | I   | TTL         | Slave select input for MSSP module.                                                                               |

|                         | HLVDIN   | 1               | Ι   | ANA         | High/Low-Voltage Detect external trip point input.                                                                |

|                         | C2OUT    | 0               | 0   | DIG         | Comparator 2 output; takes priority over port data.                                                               |

| OSC2/CLKO/RA6           | RA6      | 0               | 0   | DIG         | LATA<6> data output. Enabled in RCIO, INTIO2 and ECIO modes only.                                                 |

|                         |          | 1               | I   | TTL         | PORTA<6> data input. Enabled in RCIO, INTIO2 and ECIO modes only.                                                 |

|                         | OSC2     | x               | 0   | ANA         | Main oscillator feedback output connection (XT, HS and LP modes).                                                 |

|                         | CLKO     | x               | 0   | DIG         | System cycle clock output (Fosc/4) in RC, INTIO1 and EC Oscillator modes.                                         |

| OSC1/CLKI/RA7           | RA7      | 0               | 0   | DIG         | LATA<7> data output. Disabled in external oscillator modes.                                                       |

|                         |          | 1               | Ι   | TTL         | PORTA<7> data input. Disabled in external oscillator modes.                                                       |

|                         | OSC1     | x               | Ι   | ANA         | Main oscillator input connection.                                                                                 |

|                         | CLKI     | x               | Ι   | ANA         | Main clock input connection.                                                                                      |

# TABLE 10-1: PORTA I/O SUMMARY

Legend: DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

| R-0          | R-0                                                                    | R/W-0                                   | R/W-0                         | U-0              | R/W-1           | R/W-1            | R/W-1    |  |  |  |

|--------------|------------------------------------------------------------------------|-----------------------------------------|-------------------------------|------------------|-----------------|------------------|----------|--|--|--|

| IBF          | OBF                                                                    | IBOV                                    | PSPMODE                       | —                | TRISE2          | TRISE1           | TRISE0   |  |  |  |

| bit 7        | L                                                                      |                                         |                               |                  |                 |                  | bit      |  |  |  |

| Legend:      |                                                                        |                                         |                               |                  |                 |                  |          |  |  |  |

| R = Readab   | le hit                                                                 | W = Writable                            | bit                           | II = Unimplen    | nented bit, rea | d as '0'         |          |  |  |  |

| -n = Value a |                                                                        | '1' = Bit is se                         |                               | '0' = Bit is cle |                 | x = Bit is unkr  | nown     |  |  |  |

|              |                                                                        |                                         |                               |                  |                 |                  |          |  |  |  |

| bit 7        | IBF: Input B                                                           | uffer Full Status                       | bit                           |                  |                 |                  |          |  |  |  |

|              |                                                                        | has been receiv<br>has been rece        | ed and waiting i<br>ived      | to be read by t  | he CPU          |                  |          |  |  |  |

| bit 6        | OBF: Output                                                            | t Buffer Full Sta                       | tus bit                       |                  |                 |                  |          |  |  |  |

|              |                                                                        | out buffer still ho<br>out buffer has b | olds a previously<br>een read | y written word   |                 |                  |          |  |  |  |

| bit 5        | <b>IBOV:</b> Input Buffer Overflow Detect bit (in Microprocessor mode) |                                         |                               |                  |                 |                  |          |  |  |  |

|              |                                                                        | ccurred when a<br>low occurred          | previously input              | word has not b   | een read (must  | be cleared in so | oftware) |  |  |  |

| bit 4        | PSPMODE:                                                               | Parallel Slave I                        | Port Mode Sele                | ct bit           |                 |                  |          |  |  |  |

|              |                                                                        | Slave Port mod<br>purpose I/O mo        |                               |                  |                 |                  |          |  |  |  |

| bit 3        | Unimpleme                                                              | nted: Read as                           | ʻ0 <b>'</b>                   |                  |                 |                  |          |  |  |  |

| bit 2        | TRISE2: RE                                                             | RISE2: RE2 Direction Control bit        |                               |                  |                 |                  |          |  |  |  |

|              | 1 = Input                                                              |                                         |                               |                  |                 |                  |          |  |  |  |

|              | 0 = Output                                                             |                                         |                               |                  |                 |                  |          |  |  |  |

| bit 1        | TRISE1: RE1 Direction Control bit                                      |                                         |                               |                  |                 |                  |          |  |  |  |

|              | 1 = Input<br>0 = Output                                                |                                         |                               |                  |                 |                  |          |  |  |  |

| bit 0        | TRISE0: RE0 Direction Control bit                                      |                                         |                               |                  |                 |                  |          |  |  |  |

|              | 1 = Input                                                              |                                         |                               |                  |                 |                  |          |  |  |  |

# REGISTER 10-1: TRISE REGISTER (40/44-PIN DEVICES ONLY)

# 15.0 CAPTURE/COMPARE/PWM (CCP) MODULES

PIC18F2420/2520/4420/4520 devices all have two CCP (Capture/Compare/PWM) modules. Each module contains a 16-bit register which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register.

In 28-pin devices, the two standard CCP modules (CCP1 and CCP2) operate as described in this chapter. In 40/ 44-pin devices, CCP1 is implemented as an Enhanced CCP module with standard Capture and Compare modes and Enhanced PWM modes. The ECCP implementation is discussed in **Section 16.0 "Enhanced Capture/Compare/PWM (ECCP) Module"**. The capture and compare operations described in this chapter apply to all standard and Enhanced CCP modules.

Note: Throughout this section and Section 16.0 "Enhanced Capture/Compare/PWM (ECCP) Module", references to the register and bit names for CCP modules are referred to generically by the use of 'x' or 'y' in place of the specific module number. Thus, "CCPxCON" might refer to the control register for CCP1, CCP2 or ECCP1. "CCPxCON" is used throughout these sections to refer to the module control register, regardless of whether the CCP module is a standard or enhanced implementation.

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| —     | —   | DCxB1 | DCxB0 | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

### bit 7-6 **Unimplemented:** Read as '0'

bit 5-4 DCxB<1:0>: PWM Duty Cycle bit 1 and bit 0 for CCPx Module

Capture mode: Unused.

Compare mode:

Unused.

### PWM mode:

These bits are the two LSbs (bit 1 and bit 0) of the 10-bit PWM duty cycle. The eight MSbs (DCxB<9:2>) of the duty cycle are found in CCPRxL.

### bit 3-0 CCPxM<3:0>: CCPx Module Mode Select bits

- 0000 = Capture/Compare/PWM disabled (resets CCPx module)

- 0001 = Reserved

- 0010 = Compare mode, toggle output on match (CCPxIF bit is set)

- 0011 = Reserved

- 0100 = Capture mode, every falling edge

- 0101 = Capture mode, every rising edge

- 0110 = Capture mode, every 4th rising edge

- 0111 = Capture mode, every 16th rising edge

- 1000 = Compare mode, initialize CCPx pin low; on compare match, force CCPx pin high (CCPxIF bit is set)

- 1001 = Compare mode, initialize CCPx pin high; on compare match, force CCPx pin low (CCPxIF bit is set)

- 1010 = Compare mode, generate software interrupt on compare match (CCPxIF bit is set, CCPx pin reflects I/O state)

- 1011 = Compare mode, trigger special event; reset timer; CCP2 match starts A/D conversion (CCPxIF bit is set)

- 11xx = PWM mode

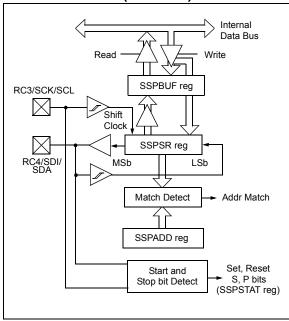

# 17.4 I<sup>2</sup>C Mode

The MSSP module in  $I^2C$  mode fully implements all master and slave functions (including general call support) and provides interrupts on Start and Stop bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-Bit and 10-Bit Addressing modes.

Two pins are used for data transfer:

- Serial clock (SCL) RC3/SCK/SCL

- Serial data (SDA) RC4/SDI/SDA

The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

#### FIGURE 17-7: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

# 17.4.1 REGISTERS

The MSSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are:

- MSSP Control Register 1 (SSPCON1)

- MSSP Control Register 2 (SSPCON2)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

- MSSP Address Register (SSPADD)

SSPCON1, SSPCON2 and SSPSTAT are the control and status registers in  $I^2C$  mode operation. The SSPCON1 and SSPCON2 registers are readable and writable. The lower 6 bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

SSPADD register holds the slave device address when the MSSP is configured in I<sup>2</sup>C Slave mode. When the MSSP is configured in Master mode, the lower seven bits of SSPADD act as the Baud Rate Generator reload value.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

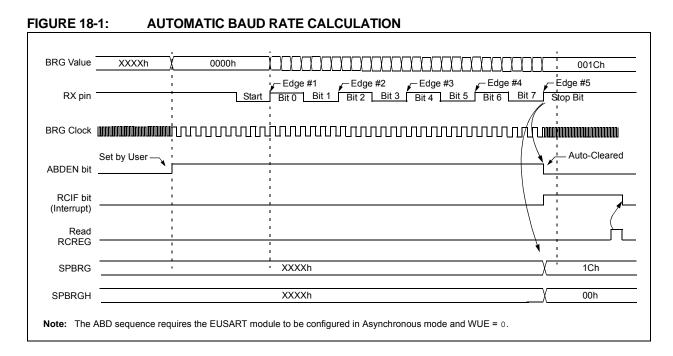

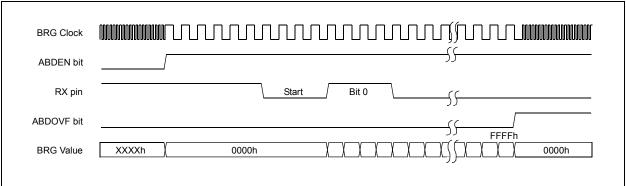

### FIGURE 18-2: BRG OVERFLOW SEQUENCE

### 20.2 Comparator Operation

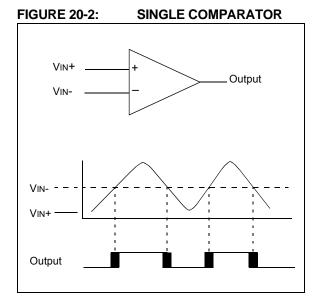

A single comparator is shown in Figure 20-2, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 20-2 represent the uncertainty, due to input offsets and response time.

### 20.3 Comparator Reference

Depending on the comparator operating mode, either an external or internal voltage reference may be used. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly (Figure 20-2).

### 20.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSS and VDD and can be applied to either pin of the comparator(s).

### 20.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference from the comparator voltage reference module. This module is described in more detail in **Section 21.0 "Comparator Voltage Reference Module"**.

The internal reference is only available in the mode where four inputs are multiplexed to two comparators (CM<2:0> = 110). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

# 20.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (see Section 26.0 "Electrical Characteristics").

### 20.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read-only. The comparator outputs may also be directly output to the RA4 and RA5 I/O pins. When enabled, multiplexers in the output path of the RA4 and RA5 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 20-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA4 and RA5 pins while in this mode.

The polarity of the comparator outputs can be changed using the C2INV and C1INV bits (CMCON<4:5>).

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- Analog levels on any pin defined as a digital input may cause the input buffer to consume more current than is specified.

### 22.5 Applications

In many applications, the ability to detect a drop below, or rise above, a particular threshold is desirable. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a high-voltage detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

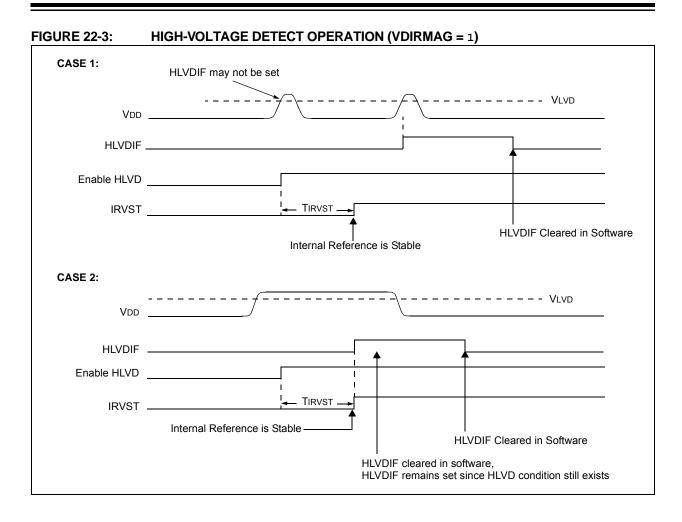

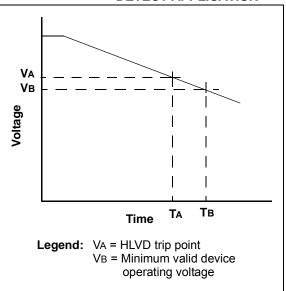

For general battery applications, Figure 22-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage, VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "house-keeping tasks" and perform a controlled shutdown before the device voltage exits the valid operating range at TB. The HLVD, thus, would give the application a time window, represented by the difference between TA and TB, to safely exit.

### TYPICAL LOW-VOLTAGE DETECT APPLICATION

# 23.0 SPECIAL FEATURES OF THE CPU

PIC18F2420/2520/4420/4520 devices include several features intended to maximize reliability and minimize cost through elimination of external components. These are:

- Oscillator Selection

- Resets:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- · Fail-Safe Clock Monitor

- Two-Speed Start-up

- Code Protection

- ID Locations

- In-Circuit Serial Programming

The oscillator can be configured for the application depending on frequency, power, accuracy and cost. All of the options are discussed in detail in **Section 2.0 "Oscillator Configurations"**.

A complete discussion of device Resets and interrupts is available in previous sections of this data sheet.

In addition to their Power-up and Oscillator Start-up Timers provided for Resets, PIC18F2420/2520/4420/ 4520 devices have a Watchdog Timer, which is either permanently enabled via the Configuration bits or software controlled (if configured as disabled). The inclusion of an internal RC oscillator also provides the additional benefits of a Fail-Safe Clock Monitor (FSCM) and Two-Speed Start-up. FSCM provides for background monitoring of the peripheral clock and automatic switchover in the event of its failure. Two-Speed Start-up enables code to be executed almost immediately on start-up, while the primary clock source completes its start-up delays.

All of these features are enabled and configured by setting the appropriate Configuration register bits.

# 23.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped starting at program memory location, 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h-3FFFFFh), which can only be accessed using table reads and table writes.

Programming the Configuration registers is done in a manner similar to programming the Flash memory. The WR bit in the EECON1 register starts a self-timed write to the Configuration register. In normal operation mode, a TBLWT instruction with the TBLPTR pointing to the Configuration register sets up the address and the data for the Configuration register write. Setting the WR bit starts a long write to the Configuration registers are written a byte at a time. To write or erase a configuration cell, a TBLWT instruction can write a '1' or a '0' into the cell. For additional details on Flash programming, refer to Section 6.5 "Writing to Flash Program Memory".

| File    | Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3                | Bit 2                | Bit 1  | Bit 0  | Default/<br>Unprogrammed<br>Value |

|---------|----------|-------|-------|-------|--------|----------------------|----------------------|--------|--------|-----------------------------------|

| 300001h | CONFIG1H | IESO  | FCMEN | _     | _      | FOSC3                | FOSC2                | FOSC1  | FOSC0  | 00 0111                           |

| 300002h | CONFIG2L | _     | _     | _     | BORV1  | BORV0                | BOREN1               | BOREN0 | PWRTEN | 1 1111                            |

| 300003h | CONFIG2H | _     | _     | _     | WDTPS3 | WDTPS2               | WDTPS1               | WDTPS0 | WDTEN  | 1 1111                            |

| 300005h | CONFIG3H | MCLRE | _     | _     | _      | _                    | LPT10SC              | PBADEN | CCP2MX | 1011                              |

| 300006h | CONFIG4L | DEBUG | XINST | _     |        |                      | LVP                  |        | STVREN | 101-1                             |

| 300008h | CONFIG5L | _     | —     | _     | —      | CP3 <sup>(1)</sup>   | CP2 <sup>(1)</sup>   | CP1    | CP0    | 1111                              |

| 300009h | CONFIG5H | CPD   | CPB   |       | _      | _                    | —                    | _      | —      | 11                                |

| 30000Ah | CONFIG6L |       | _     | _     | _      | WRT3 <sup>(1)</sup>  | WRT2 <sup>(1)</sup>  | WRT1   | WRT0   | 1111                              |

| 30000Bh | CONFIG6H | WRTD  | WRTB  | WRTC  |        | —                    | —                    | _      | —      | 111                               |

| 30000Ch | CONFIG7L | _     | _     | _     | _      | EBTR3 <sup>(1)</sup> | EBTR2 <sup>(1)</sup> | EBTR1  | EBTR0  | 1111                              |

| 30000Dh | CONFIG7H | _     | EBTRB |       |        |                      | _                    | _      | —      | -1                                |

| 3FFFFEh | DEVID1   | DEV2  | DEV1  | DEV0  | REV4   | REV3                 | REV2                 | REV1   | REV0   | xxxx xxxx <sup>(2)</sup>          |

| 3FFFFFh | DEVID2   | DEV10 | DEV9  | DEV8  | DEV7   | DEV6                 | DEV5                 | DEV4   | DEV3   | xxxx xxxx <sup>(2)</sup>          |

TABLE 23-1: CONFIGURATION BITS AND DEVICE IDs

**Legend:** x = unknown, u = unchanged, — = unimplemented, q = value depends on condition.

Shaded cells are unimplemented, read as '0'.

**Note 1:** Unimplemented in PIC18F2420/4420 devices; maintain this bit set.

2: See Register 23-12 for DEVID1 values. DEVID registers are read-only and cannot be programmed by the user.

| MOVFF                                                | Move f to                                                               | o f              |              |                                        |  |  |  |

|------------------------------------------------------|-------------------------------------------------------------------------|------------------|--------------|----------------------------------------|--|--|--|

| Syntax:                                              | MOVFF f                                                                 | s,f <sub>d</sub> |              |                                        |  |  |  |

| Operands:                                            | $\begin{array}{l} 0 \leq f_s \leq 40 \\ 0 \leq f_d \leq 40 \end{array}$ |                  |              |                                        |  |  |  |

| Operation:                                           | $(f_{s}) \to f_{d}$                                                     |                  |              |                                        |  |  |  |

| Status Affected:                                     | None                                                                    |                  |              |                                        |  |  |  |

| Encoding:<br>1st word (source)<br>2nd word (destin.) | 1100<br>1111                                                            | ffff<br>ffff     | ffff<br>ffff | ffff <sub>s</sub><br>ffff <sub>d</sub> |  |  |  |

| Description:                                         |                                                                         |                  |              |                                        |  |  |  |

| Words:                                               | 2                                                                       |                  |              |                                        |  |  |  |

| Cycles:                                              | 2 (3)                                                                   |                  |              |                                        |  |  |  |

| Q Cycle Activity:                                    |                                                                         |                  |              |                                        |  |  |  |

| Q1                                                   | Q2                                                                      | Q3               | 3            | Q4                                     |  |  |  |

| MOVLB                                         | Move Lite              | eral to L                                                                                                                                                      | ow Nib | ble in BSF                  |  |  |  |

|-----------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------|--|--|--|

| Syntax:                                       | MOVLW                  | ĸ                                                                                                                                                              |        |                             |  |  |  |

| Operands:                                     | $0 \le k \le 255$      | 5                                                                                                                                                              |        |                             |  |  |  |

| Operation:                                    | $k \to BSR$            |                                                                                                                                                                |        |                             |  |  |  |

| Status Affected:                              | None                   |                                                                                                                                                                |        |                             |  |  |  |

| Encoding:                                     | 0000                   | 0001                                                                                                                                                           | kkkk   | kkkk                        |  |  |  |

| Description:                                  | Bank Sele<br>of BSR<7: | The 8-bit literal 'k' is loaded into the<br>Bank Select Register (BSR). The value<br>of BSR<7:4> always remains '0',<br>regardless of the value of $k_7:k_4$ . |        |                             |  |  |  |

| Words:                                        | 1                      |                                                                                                                                                                |        |                             |  |  |  |

| Cycles:                                       | 1                      |                                                                                                                                                                |        |                             |  |  |  |

| Q Cycle Activity:                             |                        |                                                                                                                                                                |        |                             |  |  |  |

| Q1                                            | Q2                     | Q3                                                                                                                                                             | 3      | Q4                          |  |  |  |

| Decode                                        | Read<br>literal 'k'    | Proce<br>Dat                                                                                                                                                   |        | Write literal<br>'k' to BSR |  |  |  |

| Example:                                      | MOVLB                  | 5                                                                                                                                                              |        |                             |  |  |  |

| Before Instruc<br>BSR Reg<br>After Instructio | jister = 02            | 2h                                                                                                                                                             |        |                             |  |  |  |

|                                               |                        |                                                                                                                                                                |        |                             |  |  |  |

BSR Register = 05h

| Q1     | Q2                                  | Q3              | Q4                              |  |

|--------|-------------------------------------|-----------------|---------------------------------|--|

| Decode | Read<br>register 'f'<br>(src)       | Process<br>Data | No<br>operation                 |  |

| Decode | No<br>operation<br>No dummy<br>read | No<br>operation | Write<br>register 'f'<br>(dest) |  |

| Example:           | MOVFF | REG1, | REG2 |

|--------------------|-------|-------|------|

| Before Instruction | on    |       |      |

| REG1               | =     | 33h   |      |

| = | 11h |

|---|-----|

|   |     |

| = | 33h |

| = | 33h |

|   | =   |

| MUL          | _LW                            | Multiply I                                                                                                           | Literal with                                                                                                                                                    | W                                                                 |                                                                     |   | MULW               |

|--------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------|---|--------------------|

| Synta        | ax:                            | MULLW                                                                                                                | k                                                                                                                                                               |                                                                   |                                                                     |   | Syntax:            |

| Oper         | rands:                         | $0 \le k \le 255$                                                                                                    | ;                                                                                                                                                               |                                                                   |                                                                     |   | Operan             |

| Oper         | ration:                        | (W) x k $\rightarrow$                                                                                                | PRODH:PRO                                                                                                                                                       | DDL                                                               |                                                                     |   |                    |

| Statu        | is Affected:                   | None                                                                                                                 |                                                                                                                                                                 |                                                                   |                                                                     |   | Operati            |

| Enco         | oding:                         | 0000                                                                                                                 | 1101 kl                                                                                                                                                         | kkk                                                               | kkkk                                                                |   | Status /           |

| Description: |                                | out betwee<br>8-bit literal<br>placed in th<br>pair. PROE<br>W is uncha<br>None of the<br>Note that n<br>possible in | ed multiplicati<br>in the conten<br>'k'. The 16-b<br>ne PRODH:P<br>OH contains t<br>inged.<br>e Status flags<br>either Overfl<br>this operatio<br>but not deter | ts of V<br>it resu<br>RODL<br>he hig<br>are a<br>ow no<br>n. A ze | V and the<br>lt is<br>register<br>h byte.<br>ffected.<br>r Carry is |   | Encodir<br>Descrip |

| Word         | ds:                            | 1                                                                                                                    |                                                                                                                                                                 |                                                                   |                                                                     |   |                    |

| Cycle        | es:                            | 1                                                                                                                    |                                                                                                                                                                 |                                                                   |                                                                     |   |                    |

| QC           | ycle Activity:                 |                                                                                                                      |                                                                                                                                                                 |                                                                   |                                                                     |   |                    |

|              | Q1                             | Q2                                                                                                                   | Q3                                                                                                                                                              |                                                                   | Q4                                                                  | _ |                    |

|              | Decode                         | Read<br>literal 'k'                                                                                                  | Process<br>Data                                                                                                                                                 | re<br>P                                                           | Write<br>egisters<br>RODH:<br>PRODL                                 |   |                    |

| <u>Exar</u>  | <u>nple:</u><br>Before Instruc | MULLW                                                                                                                | 0C4h                                                                                                                                                            |                                                                   |                                                                     |   |                    |

|              | W                              | = E2                                                                                                                 | 2h                                                                                                                                                              |                                                                   |                                                                     |   | Words:             |

|              | PRODH<br>PRODL                 | = ?<br>= ?                                                                                                           |                                                                                                                                                                 |                                                                   |                                                                     |   | Cycles:            |

|              | After Instruction              | -                                                                                                                    |                                                                                                                                                                 |                                                                   |                                                                     |   | Q Cyc              |

|              | W<br>PRODH<br>PRODL            | = E2<br>= AE<br>= 08                                                                                                 | Dh                                                                                                                                                              |                                                                   |                                                                     |   |                    |

| Description:An unsigned multiplication is carrie<br>out between the contents of W and<br>register file location 'f'. The 16-bit<br>result is stored in the PRODH:PRO<br>register pair. PRODH contains the<br>high byte. Both W and 'f' are<br>unchanged.<br>None of the Status flags are affect<br>Note that neither Overflow nor Car<br>possible in this operation. A zero<br>result is possible but not detected.<br>If 'a' is '0', the Access Bank is<br>selected. If 'a' is '1', the BSR is us<br>to select the GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>operates in Indexed Literal Offset<br>Addressing mode whenever<br>f ≤ 95 (5Fh). See Section 24.2.3<br>"Byte-Oriented and Bit-Oriented<br>Instructions in Indexed Literal Off<br>Mode" for details.Words:1Cycles:1QQ2Q3Q1Q2Q3Q4ProcessWrite<br>register 'f'DecodeRead<br>register 'f'ProcessWirte<br>register 'f'ProcessWrite<br>registe                                        | MULWF            | Multiply                                                                                                                                                                                                                                                                                                          | W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                                     |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------|--|

| a ∈ [0,1]Operation:(W) x (f) → PRODH:PRODLStatus Affected:NoneEncoding:0000 001a fffff fffDescription:An unsigned multiplication is carrie<br>out between the contents of W and<br>register file location 'f'. The 16-bit<br>result is stored in the PRODH:PRO<br>register pair. PRODH contains the<br>high byte. Both W and 'f' are<br>unchanged.<br>None of the Status flags are affect<br>Note that neither Overflow nor Car<br>possible in this operation. A zero<br>result is possible but not detected.<br>If 'a' is '0', the Access Bank is<br>selected. If 'a' is '1', the BSR is us<br>to select the GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>operates in Indexed Literal Offset<br>Addressing mode whenever<br>f ≤ 95 (5Fh). See Section 24.2.3<br>"Byte-Oriented and Bit-Oriented<br>Instructions in Indexed Literal Off<br>Mode" for details.Words:1Q1Q2Q3Q4DecodeRead<br>register 'f'DataProcess<br>Virite<br>registe<br>PRODI | Syntax:          | MULWF                                                                                                                                                                                                                                                                                                             | MULWF f {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |                                     |  |