Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1.5K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2520-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                               | Pin Number  |     |         | Pin Buffer      |                |                                                                                                                                                                                   |  |  |  |

|-----------------------------------------------|-------------|-----|---------|-----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                                      | PDIP        | QFN | TQFP    | Туре            | Туре           | Description                                                                                                                                                                       |  |  |  |

|                                               |             |     |         |                 |                | PORTD is a bidirectional I/O port or a Parallel Slave<br>Port (PSP) for interfacing to a microprocessor port.<br>These pins have TTL input buffers when PSP module<br>is enabled. |  |  |  |

| RD0/PSP0<br>RD0<br>PSP0                       | 19          | 38  | 38      | I/O<br>I/O      | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                         |  |  |  |

| RD1/PSP1<br>RD1<br>PSP1                       | 20          | 39  | 39      | I/O<br>I/O      | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                         |  |  |  |

| RD2/PSP2<br>RD2<br>PSP2                       | 21          | 40  | 40      | I/O<br>I/O      | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                         |  |  |  |

| RD3/PSP3<br>RD3<br>PSP3                       | 22          | 41  | 41      | I/O<br>I/O      | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                         |  |  |  |

| RD4/PSP4<br>RD4<br>PSP4                       | 27          | 2   | 2       | I/O<br>I/O      | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                         |  |  |  |

| RD5/PSP5/P1B<br>RD5<br>PSP5<br>P1B            | 28          | 3   | 3       | I/O<br>I/O<br>O | ST<br>TTL<br>— | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                                |  |  |  |

| RD6/PSP6/P1C<br>RD6<br>PSP6<br>P1C            | 29          | 4   | 4       | I/O<br>I/O<br>O | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                                |  |  |  |

| RD7/PSP7/P1D<br>RD7<br>PSP7<br>P1D            | 30          | 5   | 5       | I/O<br>I/O<br>O | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                                |  |  |  |

| Legend: TTL = TTL c<br>ST = Schm<br>O = Outpu | nitt Trigge |     | with CM | OS lev          | els l          | CMOS = CMOS compatible input or output<br>= Input<br>P = Power                                                                                                                    |  |  |  |

## TABLE 1-3: PIC18F4420/4520 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

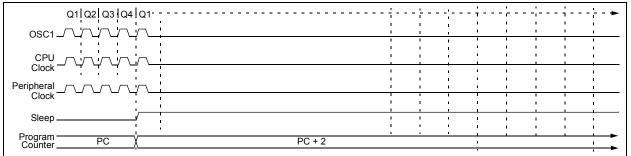

## 3.3 Sleep Mode

The power-managed Sleep mode in the PIC18F2420/ 2520/4420/4520 devices is identical to the legacy Sleep mode offered in all other PIC devices. It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 3-5). All clock source status bits are cleared.

Entering the Sleep mode from any other mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep. If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

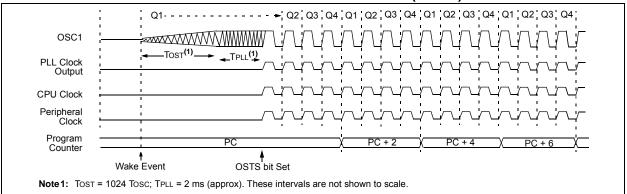

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS<1:0> bits becomes ready (see Figure 3-6), or it will be clocked from the internal oscillator block if either the Two-Speed Start-up or the Fail-Safe Clock Monitor are enabled (see **Section 23.0 "Special Features of the CPU"**). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

## 3.4 Idle Modes

The Idle modes allow the controller's CPU to be selectively shut down while the peripherals continue to operate. Selecting a particular Idle mode allows users to further manage power consumption.

If the IDLEN bit is set to '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected using the SCS<1:0> bits; however, the CPU will not be clocked. The clock source status bits are not affected. Setting IDLEN and executing a SLEEP instruction provides a quick method of switching from a given Run mode to its corresponding Idle mode.

If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out or a Reset. When a wake event occurs, CPU execution is delayed by an interval of TcsD (parameter 38, Table 26-10) while it becomes ready to execute code. When the CPU begins executing code, it resumes with the same clock source for the current Idle mode. For example, when waking from RC\_IDLE mode, the internal oscillator block will clock the CPU and peripherals (in other words, RC\_RUN mode). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or the Sleep mode, a WDT time-out will result in a WDT wake-up to the Run mode currently specified by the SCS1:SCS0 bits.

### 5.2.3 INSTRUCTIONS IN PROGRAM MEMORY

The program memory is addressed in bytes. Instructions are stored as two bytes or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSb = 0). To maintain alignment with instruction boundaries, the PC increments in steps of 2 and the LSb will always read '0' (see Section 5.1.1 "Program Counter").

Figure 5-4 shows an example of how instruction words are stored in the program memory.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 5-4 shows how the instruction GOTO 0006h is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. **Section 24.0 "Instruction Set Summary"** provides further details of the instruction set.

|                |            |                     | LSB = 1 | LSB = 0 | Word Address $\downarrow$ |

|----------------|------------|---------------------|---------|---------|---------------------------|

|                | Program M  | lemory              |         |         | 000000h                   |

|                | Byte Locat | tions $\rightarrow$ |         |         | 000002h                   |

|                |            |                     |         |         | 000004h                   |

|                |            |                     |         |         | 000006h                   |

| Instruction 1: | MOVLW      | 055h                | 0Fh     | 55h     | 000008h                   |

| Instruction 2: | GOTO       | 0006h               | EFh     | 03h     | 00000Ah                   |

|                |            |                     | F0h     | 00h     | 00000Ch                   |

| Instruction 3: | MOVFF      | 123h, 456           | n C1h   | 23h     | 00000Eh                   |

|                |            |                     | F4h     | 56h     | 000010h                   |

|                |            |                     |         |         | 000012h                   |

|                |            |                     |         |         | 000014h                   |

## FIGURE 5-4: INSTRUCTIONS IN PROGRAM MEMORY

## 5.2.4 TWO-WORD INSTRUCTIONS

The standard PIC18 instruction set has four two-word instructions: CALL, MOVFF, GOTO and LSFR. In all cases, the second word of the instructions always has '1111' as its four Most Significant bits; the other 12 bits are literal data, usually a data memory address.

The use of '1111' in the 4 MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence – immediately after the first word – the data in the second word is accessed and used by the instruction sequence. If the first word is skipped for some reason and the second word is executed by itself, a NOP is executed instead. This is necessary for cases when the two-word instruction is preceded by a conditional instruction that changes the PC. Example 5-4 shows how this works.

| Note: | See Section 5.6 "PIC18 Instruction            |

|-------|-----------------------------------------------|

|       | Execution and the Extended Instruc-           |

|       | tion Set" for information on two-word         |

|       | instructions in the extended instruction set. |

| CASE 1:             |                  |                              |  |  |  |  |  |  |

|---------------------|------------------|------------------------------|--|--|--|--|--|--|

| Object Code         | Source Code      |                              |  |  |  |  |  |  |

| 0110 0110 0000 0000 | TSTFSZ REG1      | ; is RAM location 0?         |  |  |  |  |  |  |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 | ; No, skip this word         |  |  |  |  |  |  |

| 1111 0100 0101 0110 |                  | ; Execute this word as a NOP |  |  |  |  |  |  |

| 0010 0100 0000 0000 | ADDWF REG3       | ; continue code              |  |  |  |  |  |  |

| CASE 2:             |                  |                              |  |  |  |  |  |  |

| Object Code         | Source Code      |                              |  |  |  |  |  |  |

| 0110 0110 0000 0000 | TSTFSZ REG1      | ; is RAM location 0?         |  |  |  |  |  |  |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 | ; Yes, execute this word     |  |  |  |  |  |  |

| 1111 0100 0101 0110 |                  | ; 2nd word of instruction    |  |  |  |  |  |  |

| 0010 0100 0000 0000 | ADDWF REG3       | ; continue code              |  |  |  |  |  |  |

## EXAMPLE 5-4: TWO-WORD INSTRUCTIONS

CASE 1.

| R-0          | R-0                                                             | R/W-0                                   | R/W-0                         | U-0              | R/W-1           | R/W-1            | R/W-1    |  |  |  |  |  |

|--------------|-----------------------------------------------------------------|-----------------------------------------|-------------------------------|------------------|-----------------|------------------|----------|--|--|--|--|--|

| IBF          | OBF                                                             | IBOV                                    | PSPMODE                       | —                | TRISE2          | TRISE1           | TRISE0   |  |  |  |  |  |

| bit 7        | L                                                               |                                         |                               |                  |                 |                  | bit      |  |  |  |  |  |

| Legend:      |                                                                 |                                         |                               |                  |                 |                  |          |  |  |  |  |  |

| R = Readab   | le hit                                                          | W = Writable                            | bit                           | II = Unimplen    | nented bit, rea | d as '0'         |          |  |  |  |  |  |

| -n = Value a |                                                                 | '1' = Bit is se                         |                               | '0' = Bit is cle |                 | x = Bit is unkr  | nown     |  |  |  |  |  |

|              |                                                                 |                                         |                               |                  |                 |                  |          |  |  |  |  |  |

| bit 7        | IBF: Input B                                                    | uffer Full Status                       | bit                           |                  |                 |                  |          |  |  |  |  |  |

|              |                                                                 | has been receiv<br>has been rece        | ed and waiting i<br>ived      | to be read by t  | he CPU          |                  |          |  |  |  |  |  |

| bit 6        | OBF: Output                                                     | t Buffer Full Sta                       | tus bit                       |                  |                 |                  |          |  |  |  |  |  |

|              |                                                                 | out buffer still ho<br>out buffer has b | olds a previously<br>een read | y written word   |                 |                  |          |  |  |  |  |  |

| bit 5        | IBOV: Input Buffer Overflow Detect bit (in Microprocessor mode) |                                         |                               |                  |                 |                  |          |  |  |  |  |  |

|              |                                                                 | ccurred when a<br>low occurred          | previously input              | word has not b   | een read (must  | be cleared in so | oftware) |  |  |  |  |  |

| bit 4        | PSPMODE: Parallel Slave Port Mode Select bit                    |                                         |                               |                  |                 |                  |          |  |  |  |  |  |

|              |                                                                 | Slave Port mod<br>purpose I/O mo        |                               |                  |                 |                  |          |  |  |  |  |  |

| bit 3        | Unimpleme                                                       | nted: Read as                           | ʻ0 <b>'</b>                   |                  |                 |                  |          |  |  |  |  |  |

| bit 2        | TRISE2: RE                                                      | 2 Direction Cor                         | ntrol bit                     |                  |                 |                  |          |  |  |  |  |  |

|              | 1 = Input                                                       |                                         |                               |                  |                 |                  |          |  |  |  |  |  |

|              | 0 = Output                                                      |                                         |                               |                  |                 |                  |          |  |  |  |  |  |

| bit 1        | TRISE1: RE1 Direction Control bit                               |                                         |                               |                  |                 |                  |          |  |  |  |  |  |

|              | 1 = Input<br>0 = Output                                         |                                         |                               |                  |                 |                  |          |  |  |  |  |  |

| bit 0        | •                                                               | 0 Direction Cor                         | ntrol bit                     |                  |                 |                  |          |  |  |  |  |  |

|              | 1 = Input                                                       |                                         |                               |                  |                 |                  |          |  |  |  |  |  |

## REGISTER 10-1: TRISE REGISTER (40/44-PIN DEVICES ONLY)

| Pin                         | Function | TRIS<br>Setting | I/O | l/O<br>Type | Description                                                                                           |

|-----------------------------|----------|-----------------|-----|-------------|-------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5                  | RE0      | 0               | 0   | DIG         | LATE<0> data output; not affected by analog input.                                                    |

|                             |          | 1               | Ι   | ST          | PORTE<0> data input; disabled when analog input enabled.                                              |

|                             | RD       | 1               | Ι   | TTL         | PSP read enable input (PSP enabled).                                                                  |

|                             | AN5      | 1               | I   | ANA         | A/D input channel 5; default input configuration on POR.                                              |

| RE1/WR/AN6                  | RE1      | 0               | 0   | DIG         | LATE<1> data output; not affected by analog input.                                                    |

|                             |          | 1               | I   | ST          | PORTE<1> data input; disabled when analog input enabled.                                              |

|                             | WR       | 1               | Ι   | TTL         | PSP write enable input (PSP enabled).                                                                 |

|                             | AN6      | 1               | I   | ANA         | A/D input channel 6; default input configuration on POR.                                              |

| RE2/CS/AN7                  | RE2      | 0               | 0   | DIG         | LATE<2> data output; not affected by analog input.                                                    |

|                             |          | 1               | I   | ST          | PORTE<2> data input; disabled when analog input enabled.                                              |

|                             | CS       | 1               | Ι   | TTL         | PSP write enable input (PSP enabled).                                                                 |

|                             | AN7      | 1               | I   | ANA         | A/D input channel 7; default input configuration on POR.                                              |

| MCLR/VPP/RE3 <sup>(1)</sup> | MCLR     | —               | I   | ST          | External Master Clear input; enabled when MCLRE Configuration bit is set.                             |

|                             | Vpp      | —               | Ι   | ANA         | High-voltage detection; used for ICSP™ mode entry detection. Always available regardless of pin mode. |

|                             | RE3      | (2)             | Ι   | ST          | PORTE<3> data input; enabled when MCLRE Configuration bit is clear.                                   |

## TABLE 10-9: PORTE I/O SUMMARY

Legend: DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: RE3 is available on both 28-pin and 40/44-pin devices. All other PORTE pins are only implemented on 40/44-pin devices.

2: RE3 does not have a corresponding TRIS bit to control data direction.

| Name                | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3                | Bit 2                    | Bit 1  | Bit 0  | Reset<br>Values<br>on page |  |  |  |  |

|---------------------|-------|-------|-------|---------|----------------------|--------------------------|--------|--------|----------------------------|--|--|--|--|

| PORTE               | —     | _     | _     | —       | RE3 <sup>(1,2)</sup> | RE2                      | RE1    | RE0    | 52                         |  |  |  |  |

| LATE <sup>(2)</sup> | _     | —     | —     | —       | _                    | LATE Data Latch Register |        |        | 52                         |  |  |  |  |

| TRISE               | IBF   | OBF   | IBOV  | PSPMODE | _                    | TRISE2                   | TRISE1 | TRISE0 | 52                         |  |  |  |  |

| ADCON1              | _     | _     | VCFG1 | VCFG0   | PCFG3                | PCFG2                    | PCFG1  | PCFG0  | 51                         |  |  |  |  |

### TABLE 10-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTE.

Note 1: Implemented only when Master Clear functionality is disabled (MCLRE Configuration bit = 0).

2: RE3 is the only PORTE bit implemented on both 28-pin and 40/44-pin devices. All other bits are implemented only when PORTE is implemented (i.e., 40/44-pin devices).

## 11.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS<2:0> bits (T0CON<3:0>) which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256 in power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count but will not change the prescaler     |

|       | assignment.                                 |

## 11.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

## 11.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before reenabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| Name   | Bit 7                     | Bit 6              | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on page |  |  |

|--------|---------------------------|--------------------|--------|--------|-------|--------|--------|-------|----------------------------|--|--|

| TMR0L  | Timer0 Register Low Byte  |                    |        |        |       |        |        |       |                            |  |  |

| TMR0H  | Timer0 Register High Byte |                    |        |        |       |        |        |       |                            |  |  |

| INTCON | GIE/GIEH                  | PEIE/GIEL          | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  | 49                         |  |  |

| TOCON  | TMR0ON                    | T08BIT             | TOCS   | T0SE   | PSA   | T0PS2  | T0PS1  | T0PS0 | 50                         |  |  |

| TRISA  | RA7 <sup>(1)</sup>        | RA6 <sup>(1)</sup> | RA5    | RA4    | RA3   | RA2    | RA1    | RA0   | 52                         |  |  |

TABLE 11-1:

REGISTERS ASSOCIATED WITH TIMER0

Legend: Shaded cells are not used by Timer0.

**Note 1:** PORTA<7:6> and their direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

| TABLE 12-2: | <b>REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER</b> |

|-------------|------------------------------------------------------------|

|-------------|------------------------------------------------------------|

| Name   | Bit 7                     | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |  |

|--------|---------------------------|-----------|---------|---------|---------|--------|--------|--------|----------------------------|--|

| INTCON | GIE/GIEH                  | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 49                         |  |

| PIR1   | PSPIF <sup>(1)</sup>      | ADIF      | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 52                         |  |

| PIE1   | PSPIE <sup>(1)</sup>      | ADIE      | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 52                         |  |

| IPR1   | PSPIP <sup>(1)</sup>      | ADIP      | RCIP    | TXIP    | SSPIP   | CCP1IP | TMR2IP | TMR1IP | 52                         |  |

| TMR1L  | Timer1 Register Low Byte  |           |         |         |         |        |        |        |                            |  |

| TMR1H  | Timer1 Register High Byte |           |         |         |         |        |        |        |                            |  |

| T1CON  | RD16                      | T1RUN     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 50                         |  |

**Legend:** Shaded cells are not used by the Timer1 module.

Note 1: These bits are unimplemented on 28-pin devices; always maintain these bits clear.

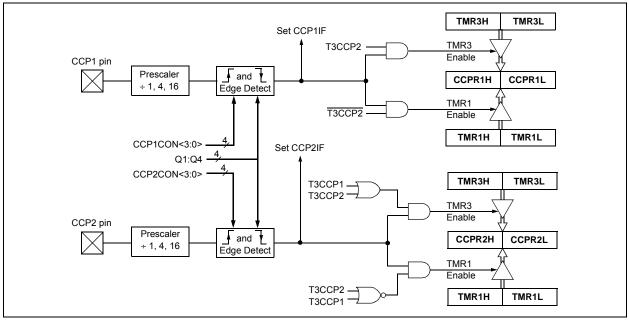

## 15.2 Capture Mode

In Capture mode, the CCPRxH:CCPRxL register pair captures the 16-bit value of the TMR1 or TMR3 register when an event occurs on the corresponding CCPx pin. An event is defined as one of the following:

- · every falling edge

- · every rising edge

- every 4th rising edge

- · every 16th rising edge

The event is selected by the mode select bits, CCPxM<3:0> (CCPxCON<3:0>). When a capture is made, the interrupt request flag bit, CCPxIF, is set; it must be cleared in software. If another capture occurs before the value in register CCPRx is read, the old captured value is overwritten by the new captured value.

### 15.2.1 CCP PIN CONFIGURATION

In Capture mode, the appropriate CCPx pin should be configured as an input by setting the corresponding TRIS direction bit.

| Note: | If RB3/CCP2 or RC1/CCP2 is configured       |

|-------|---------------------------------------------|

|       | as an output, a write to the port can cause |

|       | a capture condition.                        |

### 15.2.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation will not work. The timer to be used with each CCP module is selected in the T3CON register (see Section 15.1.1 "CCP Modules and Timer Resources").

## 15.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit clear to avoid false interrupts. The interrupt flag bit, CCPxIF, should also be cleared following any such change in operating mode.

## 15.2.4 CCP PRESCALER

There are four prescaler settings in Capture mode; they are specified as part of the operating mode selected by the mode select bits (CCPxM<3:0>). Whenever the CCP module is turned off, or Capture mode is disabled, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 15-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

## EXAMPLE 15-1: CHANGING BETWEEN CAPTURE PRESCALERS (CCP2 SHOWN)

|        | CCP2CON<br>NEW CAPT PS |   | Turn CCP module off<br>Load WREG with the |

|--------|------------------------|---|-------------------------------------------|

| NO VEW | NUM_CALI_ID            |   | new prescaler mode                        |

|        |                        |   | value and CCP ON                          |

| MOVWF  | CCP2CON                | ; | Load CCP2CON with                         |

|        |                        | ; | this value                                |

## FIGURE 15-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

## 16.4.4 HALF-BRIDGE MODE

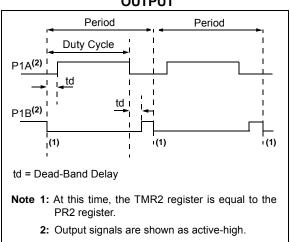

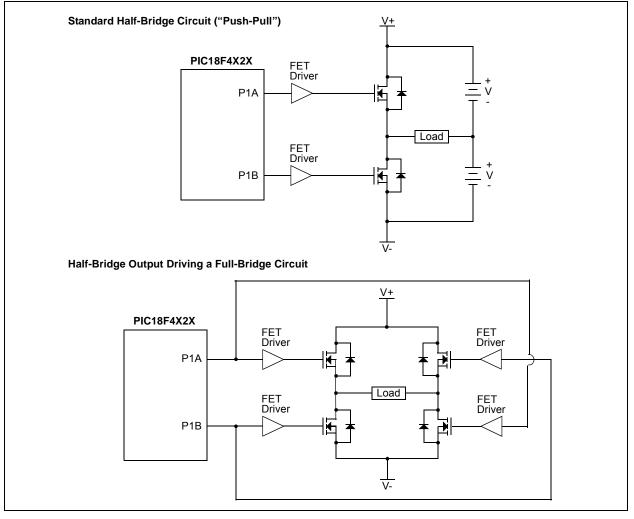

In the Half-Bridge Output mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the P1A pin, while the complementary PWM output signal is output on the P1B pin (Figure 16-4). This mode can be used for half-bridge applications, as shown in Figure 16-5, or for full-bridge applications where four power switches are being modulated with two PWM signals.

In Half-Bridge Output mode, the programmable deadband delay can be used to prevent shoot-through current in half-bridge power devices. The value of bits, PDC<6:0>, sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 16.4.6 "Programmable Dead-Band Delay"** for more details of the dead-band delay operations.

Since the P1A and P1B outputs are multiplexed with the PORTC<2> and PORTD<5> data latches, the TRISC<2> and TRISD<5> bits must be cleared to configure P1A and P1B as outputs.

### FIGURE 16-4: HALF-BRIDGE PWM OUTPUT

## FIGURE 16-5: EXAMPLES OF HALF-BRIDGE OUTPUT MODE APPLICATIONS

#### PROGRAMMABLE DEAD-BAND 16.4.6 DELAY

| Note: | Programmable |     |        |         |   |      |

|-------|--------------|-----|--------|---------|---|------|

|       | implemented  | in  | 28-pin | devices | ; | with |

|       | standard CCP | mod | dules. |         |   |      |

In half-bridge applications where all power switches are modulated at the PWM frequency at all times, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (shootthrough current) may flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In the Half-Bridge Output mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the nonactive state to the active state (see Figure 16-4 for illustration). Bits, PDC<6:0>, of the PWM1CON register (Register 16-2) set the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc). These bits are not available on 28-pin devices as the standard CCP module does not support half-bridge operation.

#### ENHANCED PWM AUTO-SHUTDOWN 16.4.7

When the CCP1 is programmed for any of the Enhanced PWM modes, the active output pins may be configured for auto-shutdown. Auto-shutdown immediately places the Enhanced PWM output pins into a defined shutdown state when a shutdown event occurs.

A shutdown event can be caused by either of the comparator modules, a low level on the Fault input pin (FLT0) or any combination of these three sources. The comparators may be used to monitor a voltage input proportional to a current being monitored in the bridge circuit. If the voltage exceeds a threshold, the comparator switches state and triggers a shutdown. Alternatively, a low digital signal on FLT0 can also trigger a shutdown. The auto-shutdown feature can be disabled by not selecting any auto-shutdown sources. The autoshutdown sources to be used are selected using the ECCPAS<2:0> bits (ECCP1AS<6:4>).

When a shutdown occurs, the output pins are asynchronously placed in their shutdown states, specified by the PSSAC<1:0> and PSSBD<1:0> bits (ECCPAS<2:0>). Each pin pair (P1A/P1C and P1B/ P1D) may be set to drive high, drive low or be tri-stated (not driving). The ECCPASE bit (ECCP1AS<7>) is also set to hold the Enhanced PWM outputs in their shutdown states.

The ECCPASE bit is set by hardware when a shutdown event occurs. If automatic restarts are not enabled, the ECCPASE bit is cleared by firmware when the cause of the shutdown clears. If automatic restarts are enabled, the ECCPASE bit is automatically cleared when the cause of the auto-shutdown has cleared.

If the ECCPASE bit is set when a PWM period begins, the PWM outputs remain in their shutdown state for that entire PWM period. When the ECCPASE bit is cleared, the PWM outputs will return to normal operation at the beginning of the next PWM period.

Writing to the ECCPASE bit is disabled Note: while a shutdown condition is active.

| R/W-0                                                                                                                                                                                                                                                                                   | R/W-0               | R/W-0                                          | R/W-0                                           | R/W-0               | R/W-0               | R/W-0               | R/W-0               |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------|-------------------------------------------------|---------------------|---------------------|---------------------|---------------------|--|--|--|

| PRSEN                                                                                                                                                                                                                                                                                   | PDC6 <sup>(1)</sup> | PDC5 <sup>(1)</sup>                            | PDC4 <sup>(1)</sup>                             | PDC3 <sup>(1)</sup> | PDC2 <sup>(1)</sup> | PDC1 <sup>(1)</sup> | PDC0 <sup>(1)</sup> |  |  |  |

| bit 7                                                                                                                                                                                                                                                                                   |                     |                                                |                                                 |                     |                     |                     | bit C               |  |  |  |

|                                                                                                                                                                                                                                                                                         |                     |                                                |                                                 |                     |                     |                     |                     |  |  |  |

| Legend:                                                                                                                                                                                                                                                                                 |                     |                                                |                                                 |                     |                     |                     |                     |  |  |  |

| R = Readable bit W = Writable bit                                                                                                                                                                                                                                                       |                     |                                                | /ritable bit U = Unimplemented bit, read as '0' |                     |                     |                     |                     |  |  |  |

| -n = Value at                                                                                                                                                                                                                                                                           | POR                 | '1' = Bit is set                               |                                                 | '0' = Bit is clea   | ared                | x = Bit is unknown  |                     |  |  |  |

| <ul> <li>bit 7 PRSEN: PWM Restart Enable bit</li> <li>1 = Upon auto-shutdown, the ECCPASE bit clears automatically once the shutdown event goes away, the PWM restarts automatically</li> <li>0 = Upon auto-shutdown, ECCPASE must be cleared in software to restart the PWM</li> </ul> |                     |                                                |                                                 |                     |                     |                     |                     |  |  |  |

| bit 6-0                                                                                                                                                                                                                                                                                 | PDC6:PDC0:          | PDC6:PDC0: PWM Delay Count bits <sup>(1)</sup> |                                                 |                     |                     |                     |                     |  |  |  |

#### REGISTER 16-2: PWM1CON: PWM DEAD-BAND DELAY REGISTER

#### DIT 6-0 **DCU:** PVVIVI Delay Count bits

Delay time, in number of Fosc/4 (4 \* Tosc) cycles, between the scheduled and actual time for a PWM signal to transition to active.

Note 1: Reserved on 28-pin devices; maintain these bits clear.

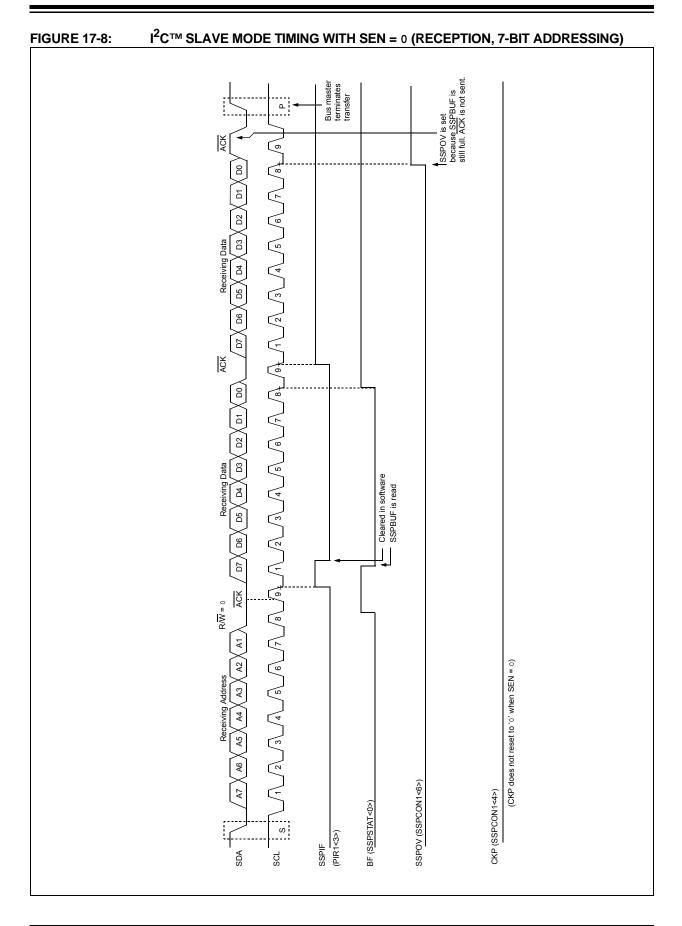

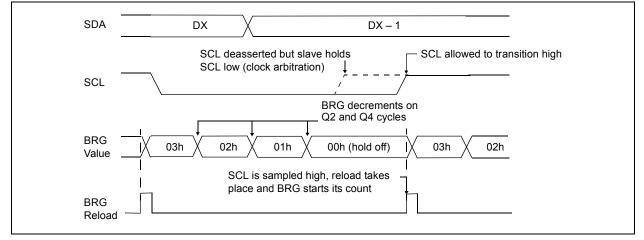

## 17.4.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 17-18).

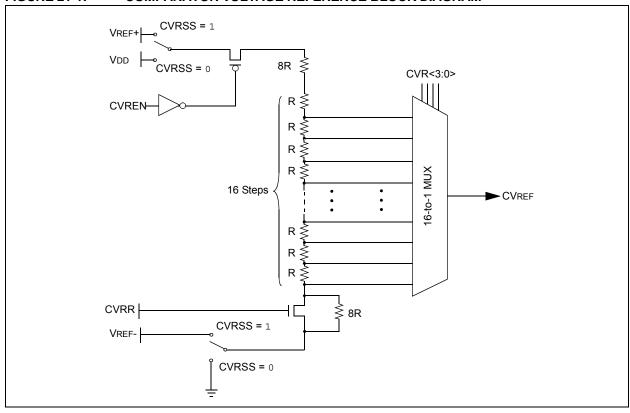

## FIGURE 21-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

## 21.2 Voltage Reference Accuracy/Error

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 21-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from the reference source; therefore, the CVREF output changes with fluctuations in that source. The tested absolute accuracy of the voltage reference can be found in **Section 26.0 "Electrical Characteristics"**.

## 21.3 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the CVRCON register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

## 21.4 Effects of a Reset

A device Reset disables the voltage reference by clearing bit, CVREN (CVRCON<7>). This Reset also disconnects the reference from the RA2 pin by clearing bit, CVROE (CVRCON<6>) and selects the high-voltage range by clearing bit, CVRR (CVRCON<5>). The CVR value select bits are also cleared.

## 21.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the CVROE bit is set. Enabling the voltage reference output onto RA2 when it is configured as a digital input will increase current consumption. Connecting RA2 as a digital output with CVRSS enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited current drive capability, a buffer must be used on the voltage reference output for external connections to VREF. Figure 21-2 shows an example buffering technique.

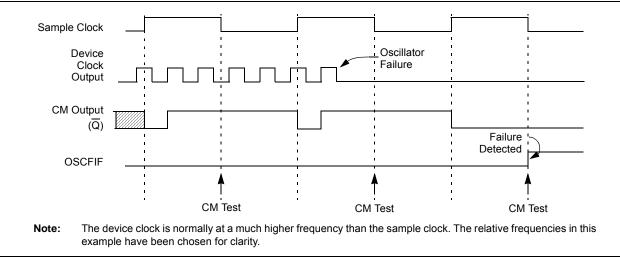

## 23.4.3 FSCM INTERRUPTS IN POWER-MANAGED MODES

By entering a power-managed mode, the clock multiplexer selects the clock source selected by the OSCCON register. Fail-Safe Clock Monitoring of the powermanaged clock source resumes in the power-managed mode.

If an oscillator failure occurs during power-managed operation, the subsequent events depend on whether or not the oscillator failure interrupt is enabled. If enabled (OSCFIF = 1), code execution will be clocked by the INTOSC multiplexer. An automatic transition back to the failed clock source will not occur.

If the interrupt is disabled, subsequent interrupts while in Idle mode will cause the CPU to begin executing instructions while being clocked by the INTOSC source.

## 23.4.4 POR OR WAKE FROM SLEEP

The FSCM is designed to detect oscillator failure at any point after the device has exited Power-on Reset (POR) or low-power Sleep mode. When the primary device clock is EC, RC or INTRC modes, monitoring can begin immediately following these events.

For oscillator modes involving a crystal or resonator (HS, HSPLL, LP or XT), the situation is somewhat different. Since the oscillator may require a start-up

time considerably longer than the FCSM sample clock time, a false clock failure may be detected. To prevent this, the internal oscillator block is automatically configured as the device clock and functions until the primary clock is stable (the OST and PLL timers have timed out). This is identical to Two-Speed Start-up mode. Once the primary clock is stable, the INTRC returns to its role as the FSCM source.

| Note: | The same logic that prevents false oscilla-<br>tor failure interrupts on POR, or wake from<br>Sleep, will also prevent the detection of<br>the oscillator's failure to start at all follow-<br>ing these events. This can be avoided by<br>monitoring the OSTS bit and using a<br>timing routine to determine if the oscillator<br>is taking too long to start. Even so, no |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | oscillator failure interrupt will be flagged.                                                                                                                                                                                                                                                                                                                               |

As noted in Section 23.3.1 "Special Considerations for Using Two-Speed Start-up", it is also possible to select another clock configuration and enter an alternate power-managed mode while waiting for the primary clock to become stable. When the new powermanaged mode is selected, the primary clock is disabled.

## 24.2.3 BYTE-ORIENTED AND BIT-ORIENTED INSTRUCTIONS IN INDEXED LITERAL OFFSET MODE

| Note: | Enabling  | the   | PIC18        | instruction   | set  |

|-------|-----------|-------|--------------|---------------|------|

|       | extension | may   | cause leg    | gacy applicat | ions |

|       | to behave | errat | ically or fa | ail entirely. |      |

In addition to eight new commands in the extended set, enabling the extended instruction set also enables Indexed Literal Offset Addressing mode (**Section 5.5.1 "Indexed Addressing with Literal Offset**"). This has a significant impact on the way that many commands of the standard PIC18 instruction set are interpreted.

When the extended set is disabled, addresses embedded in opcodes are treated as literal memory locations: either as a location in the Access Bank ('a' = 0), or in a GPR bank designated by the BSR ('a' = 1). When the extended instruction set is enabled and 'a' = 0, however, a file register argument of 5Fh or less is interpreted as an offset from the pointer value in FSR2 and not as a literal address. For practical purposes, this means that all instructions that use the Access RAM bit as an argument – that is, all byte-oriented and bitoriented instructions, or almost half of the core PIC18 instructions – may behave differently when the extended instruction set is enabled.

When the content of FSR2 is 00h, the boundaries of the Access RAM are essentially remapped to their original values. This may be useful in creating backward compatible code. If this technique is used, it may be necessary to save the value of FSR2 and restore it when moving back and forth between C and assembly routines in order to preserve the Stack Pointer. Users must also keep in mind the syntax requirements of the extended instruction set (see Section 24.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands").

Although the Indexed Literal Offset Addressing mode can be very useful for dynamic stack and pointer manipulation, it can also be very annoying if a simple arithmetic operation is carried out on the wrong register. Users who are accustomed to the PIC18 programming must keep in mind that, when the extended instruction set is enabled, register addresses of 5Fh or less are used for Indexed Literal Offset Addressing.

Representative examples of typical byte-oriented and bit-oriented instructions in the Indexed Literal Offset Addressing mode are provided on the following page to show how execution is affected. The operand conditions shown in the examples are applicable to all instructions of these types.

## 24.2.3.1 Extended Instruction Syntax with Standard PIC18 Commands

When the extended instruction set is enabled, the file register argument, 'f', in the standard byte-oriented and bit-oriented commands is replaced with the literal offset value, 'k'. As already noted, this occurs only when 'f' is less than or equal to 5Fh. When an offset value is used, it must be indicated by square brackets ("[]"). As with the extended instructions, the use of brackets indicates to the compiler that the value is to be interpreted as an index or an offset. Omitting the brackets, or using a value greater than 5Fh within brackets, will generate an error in the MPASM Assembler.

If the index argument is properly bracketed for Indexed Literal Offset Addressing, the Access RAM argument is never specified; it will automatically be assumed to be '0'. This is in contrast to standard operation (extended instruction set disabled) when 'a' is set on the basis of the target address. Declaring the Access RAM bit in this mode will also generate an error in the MPASM Assembler.

The destination argument, 'd', functions as before.

In the latest versions of the MPASM assembler, language support for the extended instruction set must be explicitly invoked. This is done with either the command line option,  $/_{Y}$ , or the PE directive in the source listing.

## 24.2.4 CONSIDERATIONS WHEN ENABLING THE EXTENDED INSTRUCTION SET

It is important to note that the extensions to the instruction set may not be beneficial to all users. In particular, users who are not writing code that uses a software stack may not benefit from using the extensions to the instruction set.

Additionally, the Indexed Literal Offset Addressing mode may create issues with legacy applications written to the PIC18 assembler. This is because instructions in the legacy code may attempt to address registers in the Access Bank below 5Fh. Since these addresses are interpreted as literal offsets to FSR2 when the instruction set extension is enabled, the application may read or write to the wrong data addresses.

When porting an application to the PIC18F2420/2520/ 4420/4520, it is very important to consider the type of code. A large, re-entrant application that is written in 'C' and would benefit from efficient compilation will do well when using the instruction set extensions. Legacy applications that heavily use the Access Bank will most likely not benefit from using the extended instruction set.

## 25.2 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

## 25.3 MPLAB C18 and MPLAB C30 C Compilers

The MPLAB C18 and MPLAB C30 Code Development Systems are complete ANSI C compilers for Microchip's PIC18 and PIC24 families of microcontrollers and the dsPIC30 and dsPIC33 family of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 25.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 25.5 MPLAB ASM30 Assembler, Linker and Librarian

MPLAB ASM30 Assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

## 25.6 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C18 and MPLAB C30 C Compilers, and the MPASM and MPLAB ASM30 Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 26.2 DC Characteristics: Power-Down and Supply Current PIC18F2420/2520/4420/4520 (Industrial) PIC18LF2420/2520/4420/4520 (Industrial)

| PIC18LF24<br>(Indust | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |     |     |                      |                                                                                                                              |                                    |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|

|                      | 20/2520/4420/4520<br>rial, Extended)                                                                                               |     |     | rating (<br>perature | Conditions (unless otherwise<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for ir<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for | ndustrial                          |  |  |  |

| Param<br>No.         | Device                                                                                                                             | Тур | Max | Units                | Conditions                                                                                                                   |                                    |  |  |  |

|                      | Power-Down Current (IPD)                                                                                                           | (1) |     |                      |                                                                                                                              |                                    |  |  |  |

|                      | PIC18LF2X2X/4X20                                                                                                                   | 0.1 | 0.5 | μΑ                   | -40°C                                                                                                                        |                                    |  |  |  |

|                      |                                                                                                                                    | 0.1 | 0.5 | μΑ                   | +25°C                                                                                                                        | VDD = 2.0V<br>( <b>Sleep</b> mode) |  |  |  |

|                      |                                                                                                                                    | 0.2 | 2.5 | μΑ                   | +85°C                                                                                                                        | (Sieep mode)                       |  |  |  |

|                      | PIC18LF2X2X/4X20                                                                                                                   | 0.1 | 0.7 | μΑ                   | -40°C                                                                                                                        | ) /== 0 0) /                       |  |  |  |

|                      |                                                                                                                                    | 0.1 | 0.7 | μΑ                   | +25°C                                                                                                                        | VDD = 3.0V<br>( <b>Sleep</b> mode) |  |  |  |

|                      |                                                                                                                                    | 0.3 | 3.5 | μΑ                   | +85°C                                                                                                                        | (Sieep mode)                       |  |  |  |

|                      | All devices                                                                                                                        | 0.1 | 1.0 | μΑ                   | -40°C                                                                                                                        |                                    |  |  |  |

|                      |                                                                                                                                    | 0.2 | 1.0 | μΑ                   | +25°C                                                                                                                        | VDD = 5.0V                         |  |  |  |

|                      |                                                                                                                                    | 0.7 | 10  | μΑ                   | +85°C                                                                                                                        | (Sleep mode)                       |  |  |  |

|                      | Extended devices only                                                                                                              | 10  | 100 | μA                   | +125°C                                                                                                                       |                                    |  |  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

- 2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD or VSS;

- $\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

- **3:** When operation below -10°C is expected, use T1OSC High-Power mode, where LPT1OSC (CONFIG3H<2>) = 0. When operation will always be above -10°C, then the low-power Timer1 oscillator may be selected.

- 4: BOR and HLVD enable internal band gap reference. With both modules enabled, current consumption will be less than the sum of both specifications.

| Param<br>No. | Sym             | Characteristic                | Min | Тур† | Max | Units | Conditions   |

|--------------|-----------------|-------------------------------|-----|------|-----|-------|--------------|

| F10          | Fosc            | Oscillator Frequency Range    | 4   | —    | 10  | MHz   | HS mode only |

| F11          | Fsys            | On-Chip VCO System Frequency  | 16  | —    | 40  | MHz   | HS mode only |

| F12          | t <sub>rc</sub> | PLL Start-up Time (Lock Time) | _   | —    | 2   | ms    |              |

| F13          | $\Delta$ CLK    | CLKO Stability (Jitter)       | -2  | —    | +2  | %     |              |

## TABLE 26-7: PLL CLOCK TIMING SPECIFICATIONS (VDD = 4.2V TO 5.5V)

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# TABLE 26-8:AC CHARACTERISTICS: INTERNAL RC ACCURACYPIC18F2420/2520/4420/4520 (INDUSTRIAL)PIC18LF2420/2520/4420/4520 (INDUSTRIAL)

|                                           | F2420/2520/4420/4520<br>ustrial) | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                                                                                                    |        |       |                |                |  |  |

|-------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------|-------|----------------|----------------|--|--|

| PIC18F2420/2520/4420/4520<br>(Industrial) |                                  |                                                                                                                                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |        |       |                |                |  |  |

| Param<br>No.                              | Device                           | Min                                                                                                                                | Тур                                                                                                                                | Max    | Units | Conditions     |                |  |  |

|                                           | INTOSC Accuracy @ Freq = 8 MHz   | , 4 MHz, 1                                                                                                                         | 4 MHz, 2 MHz, 1 MHz, 500 kHz, 250 kHz, 125 kHz, 31 kHz <sup>(1)</sup>                                                              |        |       |                |                |  |  |

|                                           | PIC18LF2420/2520/4420/4520       | -2                                                                                                                                 | +/-1                                                                                                                               | 2      | %     | +25°C          | VDD = 2.7-3.3V |  |  |

|                                           |                                  | -5                                                                                                                                 | +/-1                                                                                                                               | 5      | %     | -40°C to +85°C | VDD = 2.7-3.3V |  |  |

|                                           | PIC18F2420/2520/4420/4520        | -2                                                                                                                                 | +/-1                                                                                                                               | 2      | %     | +25°C          | VDD = 4.5-5.5V |  |  |

|                                           |                                  | -5                                                                                                                                 | +/-1                                                                                                                               | 5      | %     | -40°C to +85°C | VDD = 4.5-5.5V |  |  |

|                                           | INTRC Accuracy @ Freq = 31 kHz   |                                                                                                                                    |                                                                                                                                    |        |       |                |                |  |  |

|                                           | PIC18LF2420/2520/4420/4520       | 26.562                                                                                                                             | _                                                                                                                                  | 35.938 | kHz   | -40°C to +85°C | VDD = 2.7-3.3V |  |  |

|                                           | PIC18F2420/2520/4420/4520        | 26.562                                                                                                                             | _                                                                                                                                  | 35.938 | kHz   | -40°C to +85°C | VDD = 4.5-5.5V |  |  |

Legend: Shading of rows is to assist in readability of the table.

Note 1: Frequency calibrated at 25°C. OSCTUNE register can be used to compensate for temperature drift.

**FIGURE 27-8:** TYPICAL BOR DELTA CURRENT vs. VDD ACROSS TEMP.

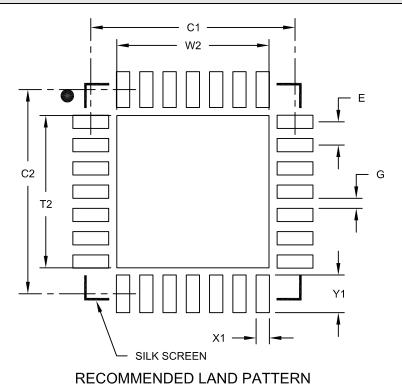

## 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS      |      |          |      |

|----------------------------|------------------|------|----------|------|

| Dimensio                   | Dimension Limits |      |          | MAX  |

| Contact Pitch              | E                |      | 0.65 BSC |      |

| Optional Center Pad Width  | W2               |      |          | 4.25 |

| Optional Center Pad Length | T2               |      |          | 4.25 |

| Contact Pad Spacing        | C1               |      | 5.70     |      |

| Contact Pad Spacing        | C2               |      | 5.70     |      |

| Contact Pad Width (X28)    | X1               |      |          | 0.37 |

| Contact Pad Length (X28)   | Y1               |      |          | 1.00 |

| Distance Between Pads      | G                | 0.20 |          |      |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A