Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1.5K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2520-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.4 Brown-out Reset (BOR)

PIC18F2420/2520/4420/4520 devices implement a BOR circuit that provides the user with a number of configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> Configuration bits. There are a total of four BOR configurations which are summarized in Table 4-1.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below VBOR (parameter D005) for greater than TBOR (parameter 35) will reset the device. A Reset may or may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR.

If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay, TPWRT (parameter 33). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay.

BOR and the Power-up Timer (PWRT) are independently configured. Enabling the Brown-out Reset does not automatically enable the PWRT.

### 4.4.1 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<6>). Setting SBOREN enables the BOR to function as previously described. Clearing SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise it is read as '0'. Placing the BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change BOR configuration. It also allows the user to tailor device power consumption in software by eliminating the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

| Note: | Even when BOR is under software control,   |

|-------|--------------------------------------------|

|       | the Brown-out Reset voltage level is still |

|       | set by the BORV<1:0> Configuration bits;   |

|       | it cannot be changed in software.          |

### 4.4.2 DETECTING BOR

When BOR is enabled, the BOR bit always resets to '0' on any BOR or POR event. This makes it difficult to determine if a BOR event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR bit is reset to '1' in software immediately after any POR event. If BOR is '0' while POR is '1', it can be reliably assumed that a BOR event has occurred.

### 4.4.3 DISABLING BOR IN SLEEP MODE

When BOREN<1:0> = 10, the BOR remains under hardware control and operates as previously described. Whenever the device enters Sleep mode, however, the BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code, when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

| BOR Con | figuration    | Status of           |                                                                                    |

|---------|---------------|---------------------|------------------------------------------------------------------------------------|

| BOREN1  | BOREN0        | SBOREN<br>(RCON<6>) | BOR Operation                                                                      |

| 0       | 0 Unavailable |                     | BOR disabled; must be enabled by reprogramming the Configuration bits.             |

| 0       | 1             | Available           | BOR enabled in software; operation controlled by SBOREN.                           |

| 1       | 0             | Unavailable         | BOR enabled in hardware in Run and Idle modes, disabled during Sleep mode.         |

| 1       |               |                     | BOR enabled in hardware; must be disabled by reprogramming the Configuration bits. |

TABLE 4-1: BOR CONFIGURATIONS

### 6.3 Reading the Flash Program Memory

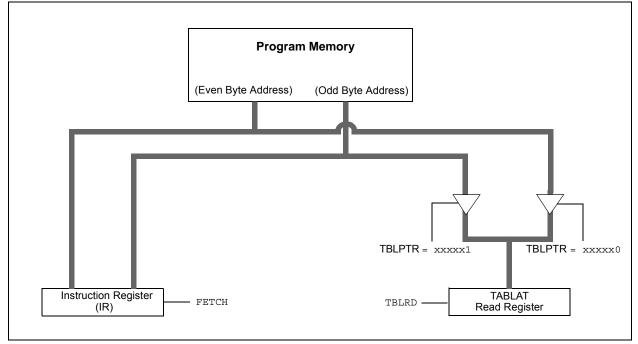

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

### FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

### EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

| MOVLW<br>MOVWF<br>MOVLW<br>MOVLW<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW       |                                                                                                                                                                              | Load TBLPTR with the base<br>address of the word                                                                                                                                       |

|-------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 110 V W1                                  |                                                                                |                                                                                                                                                                              |                                                                                                                                                                                        |

| TBLRD*+                                   | -                                                                              | ;                                                                                                                                                                            | read into TABLAT and increment                                                                                                                                                         |

| MOVF                                      | TABLAT, W                                                                      | ;                                                                                                                                                                            | get data                                                                                                                                                                               |

| MOVWF                                     | WORD EVEN                                                                      |                                                                                                                                                                              |                                                                                                                                                                                        |

| TBLRD*+                                   |                                                                                | ;                                                                                                                                                                            | read into TABLAT and increment                                                                                                                                                         |

| MOVFW                                     | TABLAT, W                                                                      | ;                                                                                                                                                                            | get data                                                                                                                                                                               |

| MOVF                                      | WORD_ODD                                                                       |                                                                                                                                                                              |                                                                                                                                                                                        |

|                                           | MOVWF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVF<br>MOVVF<br>TBLRD*4<br>MOVFW | MOVWF TBLPTRU<br>MOVLW CODE_ADDR_HIGH<br>MOVWF TBLPTRH<br>MOVLW CODE_ADDR_LOW<br>MOVWF TBLPTRL<br>TBLRD*+<br>MOVF TABLAT, W<br>MOVWF WORD_EVEN<br>TBLRD*+<br>MOVFW TABLAT, W | MOVWF TBLPTRU ;<br>MOVUW CODE_ADDR_HIGH<br>MOVWF TBLPTRH<br>MOVLW CODE_ADDR_LOW<br>MOVWF TBLPTRL<br>TBLRD*+ ;<br>MOVF TABLAT, W ;<br>MOVWF WORD_EVEN<br>TBLRD*+ ;<br>MOVFW TABLAT, W ; |

| R/W-x                                                                                                                                                                                              | R/W-x               | U-0                                                     | R/W-0                             | R/W-x                              | R/W-0           | R/S-0            | R/S-0          |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------|-----------------------------------|------------------------------------|-----------------|------------------|----------------|--|--|--|

| EEPGD                                                                                                                                                                                              | CFGS                | —                                                       | FREE                              | WRERR <sup>(1)</sup>               | WREN            | WR               | RD             |  |  |  |

| bit 7                                                                                                                                                                                              |                     |                                                         |                                   |                                    |                 |                  | bit 0          |  |  |  |

| Legend:                                                                                                                                                                                            |                     | S = Settable                                            | bit (cannot be                    | cleared in softwa                  | are)            |                  |                |  |  |  |

| R = Readab                                                                                                                                                                                         | le bit              | W = Writable                                            |                                   | U = Unimplem                       | -               | d as '0'         |                |  |  |  |

| -n = Value a                                                                                                                                                                                       | t POR               | '1' = Bit is se                                         | t                                 | ʻ0' = Bit is clea                  |                 | x = Bit is unkr  | iown           |  |  |  |

| bit 7                                                                                                                                                                                              | 1 = Access          | Flash program                                           | memory                            | I Memory Select                    | bit             |                  |                |  |  |  |

| <ul> <li>bit 6</li> <li>CFGS: Flash Program/Data EEPROM or Configuration Select bit</li> <li>1 = Access Configuration registers</li> <li>0 = Access Flash program or data EEPROM memory</li> </ul> |                     |                                                         |                                   |                                    |                 |                  |                |  |  |  |

| bit 5                                                                                                                                                                                              | Unimpleme           | nted: Read as                                           | 0'                                |                                    |                 |                  |                |  |  |  |

| bit 4                                                                                                                                                                                              | FREE: Flash         | n Row Erase Er                                          | able bit                          |                                    |                 |                  |                |  |  |  |

|                                                                                                                                                                                                    |                     | ion of erase op                                         |                                   | ressed by TBLP                     | TR on the ne    | ext WR comman    | nd (cleared by |  |  |  |

| bit 3                                                                                                                                                                                              | WRERR: Fla          | ash Program/Data EEPROM Error Flag bit <sup>(1)</sup>   |                                   |                                    |                 |                  |                |  |  |  |

|                                                                                                                                                                                                    | operatio            | operation is pre<br>on, or an improp<br>e operation cor | er write attemp                   | inated (any Rese<br>ot)            | et during self- | timed programr   | ning in norma  |  |  |  |

| bit 2                                                                                                                                                                                              |                     | h Program/Data                                          | •                                 | rite Enable bit                    |                 |                  |                |  |  |  |

| 0.112                                                                                                                                                                                              | 1 = Allows v        | vrite cycles to F<br>write cycles to F                  | lash program/o                    | data EEPROM                        |                 |                  |                |  |  |  |

| bit 1                                                                                                                                                                                              | WR: Write C         | ontrol bit                                              |                                   |                                    |                 |                  |                |  |  |  |

|                                                                                                                                                                                                    | (The op<br>can only |                                                         | med and the bi<br>ared) in softwa |                                    |                 |                  |                |  |  |  |

| bit 0                                                                                                                                                                                              | RD: Read C          |                                                         | ŗ.                                |                                    |                 |                  |                |  |  |  |

|                                                                                                                                                                                                    | be set (r           |                                                         | oftware. RD bit                   | s one cycle. RD<br>cannot be set w |                 |                  |                |  |  |  |

| Note 1. V                                                                                                                                                                                          |                     |                                                         |                                   | GS bits are not cl                 | leared This a   | llows tracing of | the error      |  |  |  |

### REGISTER 7-1: EECON1: EEPROM CONTROL REGISTER 1

**Note 1:** When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error condition.

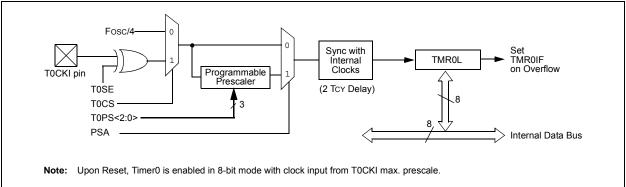

# 11.1 Timer0 Operation

Timer0 can operate as either a timer or a counter; the mode is selected with the TOCS bit (TOCON<5>). In Timer mode (TOCS = 0), the module increments on every clock by default unless a different prescaler value is selected (see **Section 11.3 "Prescaler"**). If the TMR0 register is written to, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

The Counter mode is selected by setting the T0CS bit (= 1). In this mode, Timer0 increments either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (T0CON<4>); clearing this bit selects the rising edge. Restrictions on the external clock input are discussed below.

An external clock source can be used to drive Timer0; however, it must meet certain requirements to ensure that the external clock can be synchronized with the internal phase clock (Tosc). There is a delay between synchronization and the onset of incrementing the timer/counter.

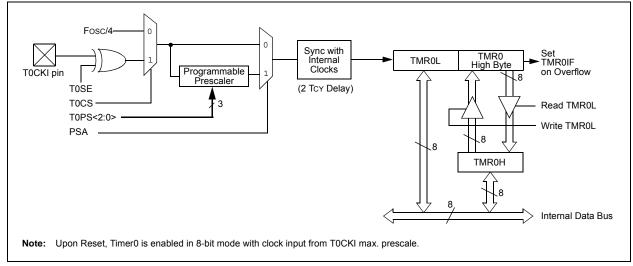

### 11.2 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode; it is actually a buffered version of the real high byte of Timer0 which is not directly readable nor writable (refer to Figure 11-2). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte were valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

### FIGURE 11-1: TIMER0 BLOCK DIAGRAM (8-BIT MODE)

### FIGURE 11-2: TIMER0 BLOCK DIAGRAM (16-BIT MODE)

| TABLE 12-2: | <b>REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER</b> |

|-------------|------------------------------------------------------------|

|-------------|------------------------------------------------------------|

| Name   | Bit 7                         | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|-------------------------------|-----------|---------|---------|---------|--------|--------|--------|----------------------------|

| INTCON | GIE/GIEH                      | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 49                         |

| PIR1   | PSPIF <sup>(1)</sup>          | ADIF      | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 52                         |

| PIE1   | PSPIE <sup>(1)</sup>          | ADIE      | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 52                         |

| IPR1   | PSPIP <sup>(1)</sup>          | ADIP      | RCIP    | TXIP    | SSPIP   | CCP1IP | TMR2IP | TMR1IP | 52                         |

| TMR1L  | IR1L Timer1 Register Low Byte |           |         |         |         |        |        |        |                            |

| TMR1H  | Timer1 Register High Byte     |           |         |         |         |        |        |        | 50                         |

| T1CON  | RD16                          | T1RUN     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 50                         |

**Legend:** Shaded cells are not used by the Timer1 module.

Note 1: These bits are unimplemented on 28-pin devices; always maintain these bits clear.

# 16.0 ENHANCED CAPTURE/ COMPARE/PWM (ECCP) MODULE

| Note: | The ECCP module is implemented only in |

|-------|----------------------------------------|

|       | 40/44-pin devices.                     |

In PIC18F4420/4520 devices, CCP1 is implemented as a standard CCP module with Enhanced PWM capabilities. These include the provision for 2 or 4 output channels, user-selectable polarity, dead-band control and automatic shutdown and restart. The enhanced features are discussed in detail in **Section 16.4 "Enhanced PWM Mode"**. Capture, Compare and single output PWM functions of the ECCP module are the same as described for the standard CCP module.

The control register for the Enhanced CCP module is shown in Register 16-2. It differs from the CCPxCON registers in PIC18F2420/2520 devices in that the two Most Significant bits are implemented to control PWM functionality.

### REGISTER 16-1: CCP1CON: ECCP CONTROL REGISTER (40/44-PIN DEVICES)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|--------|--------|--------|--------|

| P1M1  | P1M0  | DC1B1 | DC1B0 | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 |

| bit 7 |       |       |       |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-6 P1M<1:0>: Enhanced PWM Output Configuration bits If CCP1M3:CCP1M2 = 00, 01, 10: xx = P1A assigned as capture/compare input/output; P1B, P1C, P1D assigned as port pins If CCP1M3:CCP1M2 = 11: 00 = Single output, P1A modulated; P1B, P1C, P1D assigned as port pins 01 = Full-bridge output forward, P1D modulated; P1A active; P1B, P1C inactive 10 = Half-bridge output, P1A, P1B modulated with dead-band control; P1C, P1D assigned as port pins 11 = Full-bridge output reverse, P1B modulated; P1C active; P1A, P1D inactive DC1B<1:0>: PWM Duty Cycle bit 1 and bit 0 bit 5-4 Capture mode: Unused. Compare mode: Unused. PWM mode: These bits are the two LSbs of the 10-bit PWM duty cycle. The eight MSbs of the duty cycle are found in CCPR1L. bit 3-0 CCP1M<3:0>: Enhanced CCP Mode Select bits 0000 = Capture/Compare/PWM off (resets ECCP module) 0001 = Reserved 0010 = Compare mode, toggle output on match 0011 = Capture mode 0100 = Capture mode, every falling edge 0101 = Capture mode, every rising edge 0110 = Capture mode, every 4th rising edge 0111 = Capture mode, every 16th rising edge 1000 = Compare mode, initialize CCP1 pin low; set output on compare match (set CCP1IF) 1001 = Compare mode, initialize CCP1 pin high; clear output on compare match (set CCP1IF) 1010 = Compare mode, generate software interrupt only; CCP1 pin reverts to I/O state 1011 = Compare mode, trigger special event (ECCP resets TMR1 or TMR3, sets CCP1IF bit) 1100 = PWM mode, P1A, P1C active-high; P1B, P1D active-high 1101 = PWM mode, P1A, P1C active-high; P1B, P1D active-low 1110 = PWM mode, P1A, P1C active-low; P1B, P1D active-high 1111 = PWM mode, P1A, P1C active-low; P1B, P1D active-low

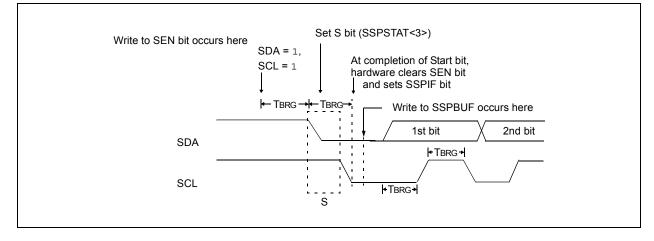

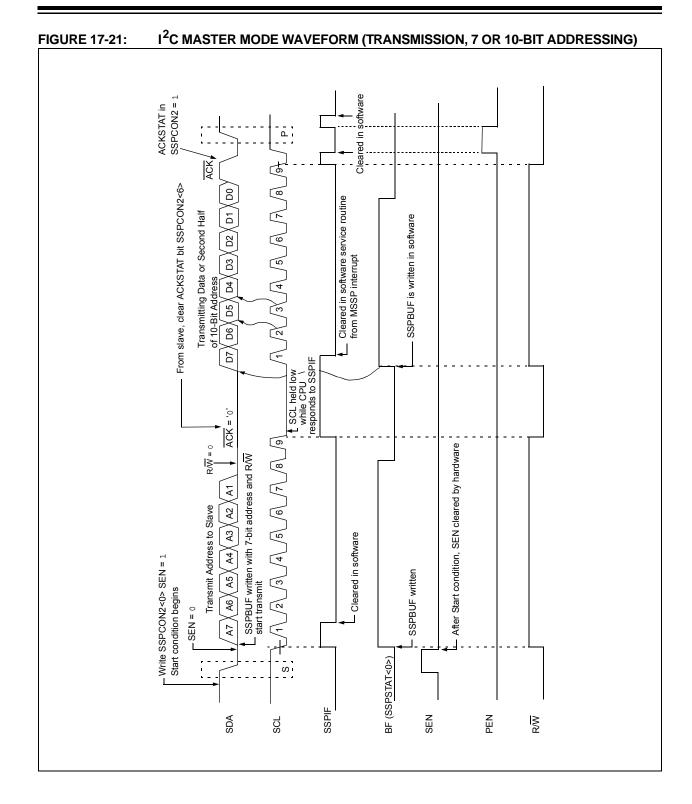

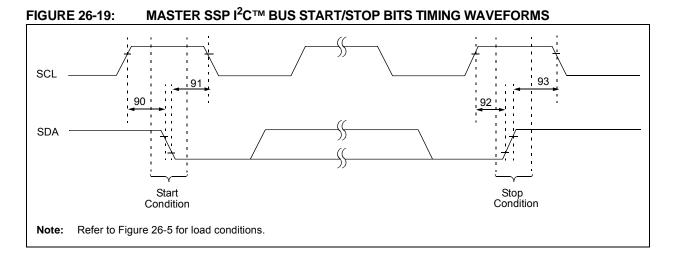

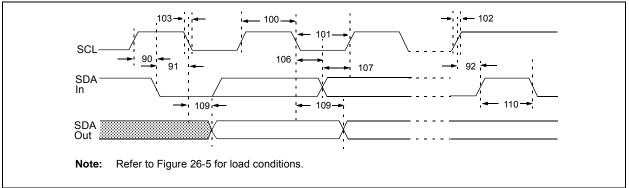

### 17.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware; the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

**Note:** If, at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

### 17.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

### FIGURE 17-19: FIRST START BIT TIMING

### 17.4.14 SLEEP OPERATION

While in Sleep mode, the  $I^2C$  module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

### 17.4.15 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 17.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit (SSPSTAT<4>) is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the MSSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- · Data Transfer

- · A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

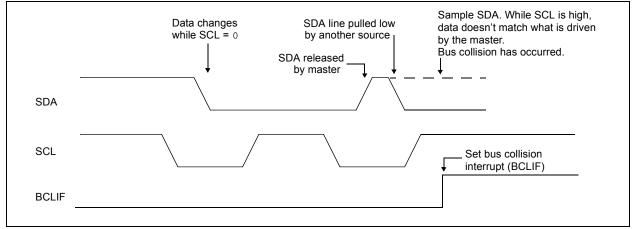

### 17.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the  $I^2C$  port to its Idle state (Figure 17-25).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

### FIGURE 17-25: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

### EXAMPLE 18-1: CALCULATING BAUD RATE ERROR

| l | For a device with Fost | c of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG: |

|---|------------------------|-----------------------------------------------------------------------|

| l | Desired Baud Rate      | = Fosc/(64 ([SPBRGH:SPBRG] + 1))                                      |

| l | Solving for SPBRGH:    | SPBRG:                                                                |

| l | Х                      | = ((Fosc/Desired Baud Rate)/64) – 1                                   |

| l |                        | = ((1600000/9600)/64) - 1                                             |

| l |                        | = [25.042] = 25                                                       |

| l | Calculated Baud Rate   | = 1600000/(64 (25 + 1))                                               |

| l |                        | = 9615                                                                |

| l | Error                  | = (Calculated Baud Rate – Desired Baud Rate)/Desired Baud Rate        |

| l |                        | = (9615 - 9600)/9600 = 0.16%                                          |

| н |                        |                                                                       |

### TABLE 18-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name    | Bit 7                                             | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset Values<br>on page |

|---------|---------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------------------------|

| TXSTA   | CSRC                                              | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 51                      |

| RCSTA   | SPEN                                              | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 51                      |

| BAUDCON | ABDOVF                                            | RCIDL | RXDTP | TXCKP | BRG16 | —     | WUE   | ABDEN | 51                      |

| SPBRGH  | EUSART Baud Rate Generator Register High Byte     |       |       |       |       |       |       |       | 51                      |

| SPBRG   | PBRG EUSART Baud Rate Generator Register Low Byte |       |       |       |       |       |       |       |                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the BRG.

| R/W-0        | U-0                                                                                                                                                                                      | R/W-0                     | R/W-0         | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------|--------------------------|------------------|-----------------|-------|

| ADFM         | _                                                                                                                                                                                        | ACQT2                     | ACQT1         | ACQT0                    | ADCS2            | ADCS1           | ADCS0 |

| bit 7        |                                                                                                                                                                                          | I                         | I             |                          |                  |                 | bit C |

| Legend:      |                                                                                                                                                                                          |                           |               |                          |                  |                 |       |

| R = Readab   | ole bit                                                                                                                                                                                  | W = Writable              | bit           | U = Unimplen             | nented bit, read | d as '0'        |       |

| -n = Value a | It POR                                                                                                                                                                                   | '1' = Bit is set          |               | '0' = Bit is cle         |                  | x = Bit is unkr | nown  |

| bit 7        | <b>ADFM:</b> A/D R<br>1 = Right justi<br>0 = Left justifie                                                                                                                               |                           | elect bit     |                          |                  |                 |       |

| bit 6        | Unimplement                                                                                                                                                                              | ted: Read as '            | כי            |                          |                  |                 |       |

| bit 5-3      | ACQT<2:0>:                                                                                                                                                                               | A/D Acquisition           | n Time Select | bits                     |                  |                 |       |

|              | $111 = 20 \text{ TAD}$ $110 = 16 \text{ TAD}$ $101 = 12 \text{ TAD}$ $100 = 8 \text{ TAD}$ $011 = 6 \text{ TAD}$ $010 = 4 \text{ TAD}$ $001 = 2 \text{ TAD}$ $000 = 0 \text{ TAD}^{(1)}$ |                           |               |                          |                  |                 |       |

| bit 2-0      | 111 = FRC (cl<br>110 = Fosc/6<br>101 = Fosc/1<br>100 = Fosc/4                                                                                                                            | 6<br>ock derived fro<br>2 | m A/D RC osc  | sillator) <sup>(1)</sup> |                  |                 |       |

### REGISTER 19-3: ADCON2: A/D CONTROL REGISTER 2

**Note 1:** If the A/D FRC clock source is selected, a delay of one TcY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

## **19.1** A/D Acquisition Requirements

For the A/D Converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 19-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . After the analog input channel is selected (changed), the channel must be sampled for at least the minimum acquisition time before starting a conversion.

Note: When the conversion is started, the holding capacitor is disconnected from the input pin.

EQUATION 19-1: ACQUISITION TIME

TACQ = Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient = TAMP + TC + TCOFF

### EQUATION 19-2: A/D MINIMUM CHARGING TIME

| VHOLD | = | $(\text{VREF} - (\text{VREF}/2048)) \bullet (1 - e^{(-\text{TC/CHOLD}(\text{Ric} + \text{Rss} + \text{Rs}))})$ |

|-------|---|----------------------------------------------------------------------------------------------------------------|

| or    |   |                                                                                                                |

| TC    | = | -(CHOLD)(RIC + RSS + RS) ln(1/2048)                                                                            |

### EQUATION 19-3: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME

| TACQ    | =       | TAMP + TC + TCOFF                                                                                                                                |

|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| TAMP    | =       | 0.2 μs                                                                                                                                           |

| TCOFF   | =       | (Temp – 25°C)(0.02 μs/°C)<br>(85°C – 25°C)(0.02 μs/°C)<br>1.2 μs                                                                                 |

| Tempera | ature c | oefficient is only required for temperatures > 25°C. Below 25°C, TCOFF = 0 $\mu$ s.                                                              |

| Тс      | =       | -(Chold)(Ric + Rss + Rs) $\ln(1/2047) \ \mu s$<br>-(25 pF) (1 k $\Omega$ + 2 k $\Omega$ + 2.5 k $\Omega$ ) ln(0.0004883) $\mu s$<br>1.05 $\mu s$ |

| TACQ    | =       | $0.2 \ \mu s + 1 \ \mu s + 1.2 \ \mu s$<br>2.4 \ \ \ \ \ \ \ \ s                                                                                 |

To calculate the minimum acquisition time, Equation 19-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

Example 19-3 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following application system assumptions:

| CHOLD            | =      | 25 pF                              |

|------------------|--------|------------------------------------|

| Rs               | =      | 2.5 kΩ                             |

| Conversion Error | $\leq$ | 1/2 LSb                            |

| Vdd              | =      | $5V  ightarrow Rss$ = 2 k $\Omega$ |

| Temperature      | =      | 85°C (system max.)                 |

### REGISTER 23-14: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0                 |

|-------|-----|-----|-----|-----|-----|-----|-----------------------|

| —     | —   |     |     |     | —   | —   | SWDTEN <sup>(1)</sup> |

| bit 7 |     |     |     |     |     |     | bit 0                 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7-1 | Unimplemented: Read as '0'                                           |

|---------|----------------------------------------------------------------------|

| bit 0   | SWDTEN: Software Controlled Watchdog Timer Enable bit <sup>(1)</sup> |

|         | 1 = Watchdog Timer is on                                             |

0 = Watchdog Timer is off

**Note 1:** This bit has no effect if the Configuration bit, WDTEN, is enabled.

### TABLE 23-2: SUMMARY OF WATCHDOG TIMER REGISTERS

| Name   | Bit 7 | Bit 6                 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0                 | Reset<br>Values<br>on page |

|--------|-------|-----------------------|-------|-------|-------|-------|-------|-----------------------|----------------------------|

| RCON   | IPEN  | SBOREN <sup>(1)</sup> | _     | RI    | TO    | PD    | POR   | BOR                   | 48                         |

| WDTCON |       | —                     |       |       | _     |       |       | SWDTEN <sup>(2)</sup> | 50                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

Note 1: The SBOREN bit is only available when the BOREN<1:0> Configuration bits = 01; otherwise, it is disabled and reads as '0'. See Section 4.4 "Brown-out Reset (BOR)".

**2:** This bit has no effect if the Configuration bit, WDTEN, is enabled.

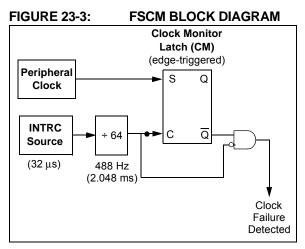

# 23.4 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the microcontroller to continue operation in the event of an external oscillator failure by automatically switching the device clock to the internal oscillator block. The FSCM function is enabled by setting the FCMEN Configuration bit.

When FSCM is enabled, the INTRC oscillator runs at all times to monitor clocks to peripherals and provide a backup clock in the event of a clock failure. Clock monitoring (shown in Figure 23-3) is accomplished by creating a sample clock signal, which is the INTRC output divided by 64. This allows ample time between FSCM sample clocks for a peripheral clock edge to occur. The peripheral device clock and the sample clock are presented as inputs to the Clock Monitor latch (CM). The CM is set on the falling edge of the device clock source, but cleared on the rising edge of the sample clock.

Clock failure is tested for on the falling edge of the sample clock. If a sample clock falling edge occurs while CM is still set, a clock failure has been detected (Figure 23-4). This causes the following:

- the FSCM generates an oscillator fail interrupt by setting bit, OSCFIF (PIR2<7>);

- the device clock source is switched to the internal oscillator block (OSCCON is not updated to show the current clock source – this is the fail-safe condition) and

- the WDT is reset.

During switchover, the postscaler frequency from the internal oscillator block may not be sufficiently stable for timing sensitive applications. In these cases, it may be desirable to select another clock configuration and enter an alternate power-managed mode. This can be done to attempt a partial recovery or execute a controlled shutdown. See Section 3.1.4 "Multiple Sleep Commands" and Section 23.3.1 "Special Considerations for Using Two-Speed Start-up" for more details.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF<2:0>, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF<2:0> bits prior to entering Sleep mode.

The FSCM will detect failures of the primary or secondary clock sources only. If the internal oscillator block fails, no failure would be detected, nor would any action be possible.

### 23.4.1 FSCM AND THE WATCHDOG TIMER

Both the FSCM and the WDT are clocked by the INTRC oscillator. Since the WDT operates with a separate divider and counter, disabling the WDT has no effect on the operation of the INTRC oscillator when the FSCM is enabled.

As already noted, the clock source is switched to the INTOSC clock when a clock failure is detected. Depending on the frequency selected by the IRCF<2:0> bits, this may mean a substantial change in the speed of code execution. If the WDT is enabled with a small prescale value, a decrease in clock speed allows a WDT time-out to occur and a subsequent device Reset. For this reason, fail-safe clock events also reset the WDT and postscaler, allowing it to start timing from when execution speed was changed and decreasing the likelihood of an erroneous time-out.

## 23.4.2 EXITING FAIL-SAFE OPERATION

The fail-safe condition is terminated by either a device Reset or by entering a power-managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 1H (with any required start-up delays that are required for the oscillator mode, such as the OST or PLL timer). The INTOSC multiplexer provides the device clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The Fail-Safe Clock Monitor then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTOSC multiplexer. The OSCCON register will remain in its Reset state until a power-managed mode is entered.

| COMF                     | Complem                           | ent f                                                            |                      | CPFSEQ                   | Compare                  | f with W, SI                         | kip if f = W             |

|--------------------------|-----------------------------------|------------------------------------------------------------------|----------------------|--------------------------|--------------------------|--------------------------------------|--------------------------|

| Syntax:                  | COMF f                            | {,d {,a}}                                                        |                      | Syntax:                  | CPFSEQ                   | f {,a}                               |                          |

| Operands:                | 0 ≤ f ≤ 255                       |                                                                  |                      | Operands:                | $0 \leq f \leq 255$      |                                      |                          |

|                          | d ∈ [0,1]                         |                                                                  |                      |                          | a ∈ [0,1]                |                                      |                          |

|                          | a ∈ [0,1]                         |                                                                  |                      | Operation:               | (f) - (W),               | (14.1)                               |                          |

| Operation:               | $(\overline{f}) \rightarrow dest$ |                                                                  |                      |                          | skip if (f) =            | (vv)<br>comparison)                  |                          |

| Status Affected:         | N, Z                              |                                                                  |                      | Status Affected:         | None                     | ompanoon)                            |                          |

| Encoding:                | 0001                              | 11da ff                                                          | ff ffff              | Encoding:                | 0110                     | 001a ff:                             | ff ffff                  |

| Description:             | complemer                         | ts of register 'f<br>nted. If 'd' is '0'<br>/. If 'd' is '1', th | , the result is      | Description:             | Compares<br>location 'f' | the contents of<br>to the contents   | f data memory<br>of W by |

|                          |                                   | k in register 'f'                                                |                      |                          |                          | an unsigned s<br>ien the fetched     |                          |

|                          |                                   | -                                                                | nk is selected.      |                          |                          | and a NOP is ex                      |                          |

|                          | ,                                 |                                                                  | d to select the      |                          |                          | aking this a two                     |                          |

|                          | GPR bank                          | (default).<br>Ind the extend                                     | ed instruction       |                          | instruction.             |                                      |                          |

|                          |                                   |                                                                  | ction operates       |                          |                          | he Access Bai<br>he BSR is use       |                          |

|                          | in Indexed                        | Literal Offset A                                                 | Addressing           |                          | GPR bank                 |                                      |                          |

|                          |                                   | never f ≤ 95 (5                                                  |                      |                          |                          | ind the extende                      | ed instruction           |

|                          |                                   | .2.3 "Byte-Or<br>ed Instruction                                  |                      |                          |                          | led, this instruc                    |                          |

|                          |                                   | set Mode" for                                                    |                      |                          |                          | Literal Offset A<br>never f ≤ 95 (5l |                          |

| Words:                   | 1                                 |                                                                  |                      |                          |                          | .2.3 "Byte-Or                        |                          |

| Cycles:                  | 1                                 |                                                                  |                      |                          | Bit-Oriente              | ed Instruction<br>set Mode" for      | s in Indexed             |

| Q Cycle Activity:        |                                   |                                                                  |                      | Words:                   | 1                        |                                      |                          |

| Q1                       | Q2                                | Q3                                                               | Q4                   | Cycles:                  | 1(2)                     |                                      |                          |

| Decode                   | Read<br>register 'f'              | Process<br>Data                                                  | Write to destination | ,                        | Note: 3 c                | ycles if skip ar<br>a 2-word instru  |                          |

|                          |                                   |                                                                  |                      | Q Cycle Activity:        |                          |                                      |                          |

| Example:                 | COMF                              | REG, 0, 0                                                        |                      | Q1                       | Q2                       | Q3                                   | Q4                       |

| Before Instruc           |                                   |                                                                  |                      | Decode                   | Read                     | Process                              | No                       |

| REG<br>After Instruction | = 13h                             |                                                                  |                      | 16 - 1-1                 | register 'f'             | Data                                 | operation                |

| After Instructio<br>REG  | = 13h                             |                                                                  |                      | If skip:                 | 02                       | 02                                   | 04                       |

| W                        | = ECh                             |                                                                  |                      | Q1<br>No                 | Q2<br>No                 | Q3<br>No                             | Q4<br>No                 |

|                          |                                   |                                                                  |                      | operation                | operation                | operation                            | operation                |

|                          |                                   |                                                                  |                      | If skip and followe      | ed by 2-word in          | struction:                           | • •                      |

|                          |                                   |                                                                  |                      | Q1                       | Q2                       | Q3                                   | Q4                       |

|                          |                                   |                                                                  |                      | No                       | No                       | No                                   | No                       |

|                          |                                   |                                                                  |                      | operation<br>No          | operation<br>No          | operation<br>No                      | operation<br>No          |

|                          |                                   |                                                                  |                      | operation                | operation                | operation                            | operation                |

|                          |                                   |                                                                  |                      | <u> </u>                 | • •                      | . ·                                  |                          |

|                          |                                   |                                                                  |                      | Example:                 | HERE<br>NEQUAL<br>EQUAL  | CPFSEQ REG<br>:<br>:                 | 3, 0                     |

|                          |                                   |                                                                  |                      | Before Instru            | ction                    |                                      |                          |

|                          |                                   |                                                                  |                      | PC Add                   |                          | IRE                                  |                          |

|                          |                                   |                                                                  |                      | W                        | = ?                      |                                      |                          |

|                          |                                   |                                                                  |                      | REG<br>After Instruct    | = ?                      |                                      |                          |

|                          |                                   |                                                                  |                      | After Instruct<br>If REG |                          |                                      |                          |

|                          |                                   |                                                                  |                      | IT REG<br>PC             | ••                       | ;<br>Idress (EQUA                    | L)                       |

### 26.2 DC Characteristics: Power-Down and Supply Current PIC18F2420/2520/4420/4520 (Industrial) PIC18LF2420/2520/4420/4520 (Industrial) (Continued)

| PIC18LF2420/2520/4420/4520<br>(Industrial)<br>PIC18F2420/2520/4420/4520<br>(Industrial, Extended) |                                     | Standard Operating Conditions (unless otherwise stated)         Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial         Standard Operating Conditions (unless otherwise stated)         Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +85^{\circ}C$ for extended |     |    |        |            |                                      |  |  |  |

|---------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|--------|------------|--------------------------------------|--|--|--|

|                                                                                                   |                                     |                                                                                                                                                                                                                                                                                                                                                                                                           |     |    |        |            |                                      |  |  |  |

|                                                                                                   | Supply Current (IDD) <sup>(2)</sup> |                                                                                                                                                                                                                                                                                                                                                                                                           |     |    |        |            |                                      |  |  |  |

|                                                                                                   | PIC18LF2X2X/4X20                    | 250                                                                                                                                                                                                                                                                                                                                                                                                       | 350 | μΑ | -40°C  |            |                                      |  |  |  |

|                                                                                                   |                                     | 260                                                                                                                                                                                                                                                                                                                                                                                                       | 350 | μΑ | +25°C  | VDD = 2.0V |                                      |  |  |  |

|                                                                                                   |                                     | 250                                                                                                                                                                                                                                                                                                                                                                                                       | 350 | μΑ | +85°C  |            |                                      |  |  |  |

|                                                                                                   | PIC18LF2X2X/4X20                    | 550                                                                                                                                                                                                                                                                                                                                                                                                       | 650 | μΑ | -40°C  |            |                                      |  |  |  |

|                                                                                                   |                                     | 480                                                                                                                                                                                                                                                                                                                                                                                                       | 640 | μΑ | +25°C  | VDD = 3.0V | Fosc = 1 MHz<br>( <b>PRI_RUN</b> ,   |  |  |  |

|                                                                                                   |                                     | 460                                                                                                                                                                                                                                                                                                                                                                                                       | 600 | μΑ | +85°C  |            | EC oscillator)                       |  |  |  |

|                                                                                                   | All devices                         | 1.2                                                                                                                                                                                                                                                                                                                                                                                                       | 1.5 | mA | -40°C  |            |                                      |  |  |  |

|                                                                                                   |                                     | 1.1                                                                                                                                                                                                                                                                                                                                                                                                       | 1.4 | mA | +25°C  | VDD = 5.0V |                                      |  |  |  |

|                                                                                                   |                                     | 1.0                                                                                                                                                                                                                                                                                                                                                                                                       | 1.3 | mA | +85°C  | VDD - 5.0V |                                      |  |  |  |

|                                                                                                   | Extended devices only               | 1.0                                                                                                                                                                                                                                                                                                                                                                                                       | 3.0 | mA | +125°C |            |                                      |  |  |  |

|                                                                                                   | PIC18LF2X2X/4X20                    | 0.72                                                                                                                                                                                                                                                                                                                                                                                                      | 1.0 | mA | -40°C  |            |                                      |  |  |  |

|                                                                                                   |                                     | 0.74                                                                                                                                                                                                                                                                                                                                                                                                      | 1.0 | mA | +25°C  | VDD = 2.0V | _                                    |  |  |  |

|                                                                                                   |                                     | 0.74                                                                                                                                                                                                                                                                                                                                                                                                      | 1.0 | mA | +85°C  |            |                                      |  |  |  |

|                                                                                                   | PIC18LF2X2X/4X20                    | 1.3                                                                                                                                                                                                                                                                                                                                                                                                       | 1.8 | mA | -40°C  |            |                                      |  |  |  |

|                                                                                                   |                                     | 1.3                                                                                                                                                                                                                                                                                                                                                                                                       | 1.8 | mA | +25°C  | VDD = 3.0V | Fosc = 4 MHz<br>( <b>PRI_RUN</b> ,   |  |  |  |

|                                                                                                   |                                     | 1.3                                                                                                                                                                                                                                                                                                                                                                                                       | 1.8 | mA | +85°C  |            | EC oscillator)                       |  |  |  |

|                                                                                                   | All devices                         | 2.7                                                                                                                                                                                                                                                                                                                                                                                                       | 4.0 | mA | -40°C  |            |                                      |  |  |  |

|                                                                                                   |                                     | 2.6                                                                                                                                                                                                                                                                                                                                                                                                       | 4.0 | mA | +25°C  |            |                                      |  |  |  |

|                                                                                                   |                                     | 2.5                                                                                                                                                                                                                                                                                                                                                                                                       | 4.0 | mA | +85°C  | VDD = 5.0V |                                      |  |  |  |

|                                                                                                   | Extended devices only               | 2.6                                                                                                                                                                                                                                                                                                                                                                                                       | 5.0 | mA | +125°C |            |                                      |  |  |  |

|                                                                                                   | Extended devices only               | 8.4                                                                                                                                                                                                                                                                                                                                                                                                       | 13  | mA | +125°C | VDD = 4.2V | Fosc = 25 MHz                        |  |  |  |