Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

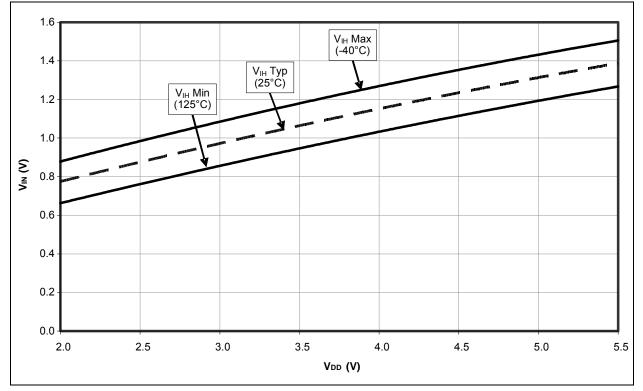

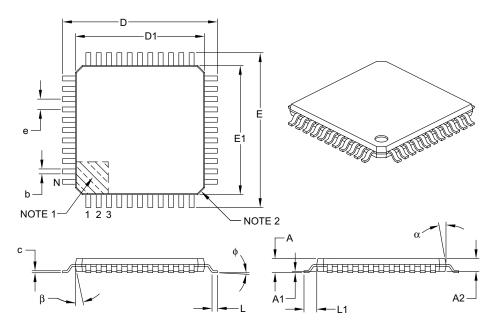

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2520t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

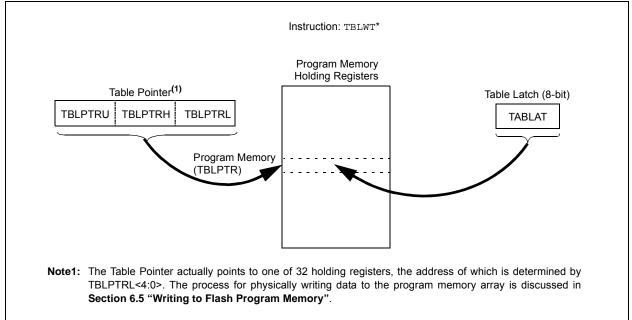

### FIGURE 6-2: TABLE WRITE OPERATION

# 6.2 Control Registers

Several control registers are used in conjunction with the  ${\tt TBLRD}$  and  ${\tt TBLWT}$  instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

#### 6.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 6-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The EEPGD control bit determines if the access will be a program or data EEPROM memory access. When clear, any subsequent operations will operate on the data EEPROM memory. When set, any subsequent operations will operate on the program memory.

The CFGS control bit determines if the access will be to the Configuration/Calibration registers or to program memory/data EEPROM memory. When set, subsequent operations will operate on Configuration registers regardless of EEPGD (see **Section 23.0 "Special Features of the CPU"**). When clear, memory selection access is determined by EEPGD. The FREE bit, when set, will allow a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR is       |

|-------|---------------------------------------------|

|       | read as '1'. This can indicate that a write |

|       | operation was prematurely terminated by     |

|       | a Reset, or a write operation was           |

|       | attempted improperly.                       |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation.

**Note:** The EEIF interrupt flag bit (PIR2<4>) is set when the write is complete. It must be cleared in software.

| Pin            | Function            | TRIS<br>Setting | I/O | l/O<br>Type          | Description                                                                                                                                     |

|----------------|---------------------|-----------------|-----|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/     | RC0                 | 0               | 0   | DIG                  | LATC<0> data output.                                                                                                                            |

| T13CKI         |                     | 1               | Ι   | ST                   | PORTC<0> data input.                                                                                                                            |

|                | T10S0               | x               | 0   | ANA                  | Timer1 oscillator output; enabled when Timer1 oscillator enabled.<br>Disables digital I/O.                                                      |

|                | T13CKI              | 1               | Ι   | ST                   | Timer1/Timer3 counter input.                                                                                                                    |

| RC1/T1OSI/CCP2 | RC1                 | 0               | 0   | DIG                  | LATC<1> data output.                                                                                                                            |

|                |                     | 1               | Ι   | ST                   | PORTC<1> data input.                                                                                                                            |

|                | T1OSI               | x               | I   | ANA                  | Timer1 oscillator input; enabled when Timer1 oscillator enabled.<br>Disables digital I/O.                                                       |

|                | CCP2 <sup>(1)</sup> | 0               | 0   | DIG                  | CCP2 compare and PWM output; takes priority over port data.                                                                                     |

|                |                     | 1               | Ι   | ST                   | CCP2 capture input.                                                                                                                             |

| RC2/CCP1/P1A   | RC2                 | 0               | 0   | DIG                  | LATC<2> data output.                                                                                                                            |

|                |                     | 1               | Ι   | ST                   | PORTC<2> data input.                                                                                                                            |

|                | CCP1                | 0               | 0   | DIG                  | ECCP1 compare or PWM output; takes priority over port data.                                                                                     |

|                |                     | 1               | Ι   | ST                   | ECCP1 capture input.                                                                                                                            |

|                | P1A <sup>(2)</sup>  | 0               | 0   | DIG                  | ECCP1 Enhanced PWM output, channel A. May be configured for<br>tri-state during Enhanced PWM shutdown events. Takes priority over<br>port data. |

| RC3/SCK/SCL    | RC3                 | 0               | 0   | DIG                  | LATC<3> data output.                                                                                                                            |

|                |                     | 1               | Ι   | ST                   | PORTC<3> data input.                                                                                                                            |

|                | SCK                 | 0               | 0   | DIG                  | SPI clock output (MSSP module); takes priority over port data.                                                                                  |

|                |                     | 1               | Ι   | ST                   | SPI clock input (MSSP module).                                                                                                                  |

|                | SCL                 | 0               | 0   | DIG                  | I <sup>2</sup> C <sup>™</sup> clock output (MSSP module); takes priority over port data.                                                        |

|                |                     | 1               | Ι   | I <sup>2</sup> C/SMB | I <sup>2</sup> C clock input (MSSP module); input type depends on module setting                                                                |

| RC4/SDI/SDA    | RC4                 | 0               | 0   | DIG                  | LATC<4> data output.                                                                                                                            |

|                |                     | 1               | Ι   | ST                   | PORTC<4> data input.                                                                                                                            |

|                | SDI                 | 1               | I   | ST                   | SPI data input (MSSP module).                                                                                                                   |

|                | SDA                 | 1               | 0   | DIG                  | I <sup>2</sup> C data output (MSSP module); takes priority over port data.                                                                      |

|                |                     | 1               | I   | I <sup>2</sup> C/SMB | I <sup>2</sup> C data input (MSSP module); input type depends on module setting.                                                                |

| RC5/SDO        | RC5                 | 0               | 0   | DIG                  | LATC<5> data output.                                                                                                                            |

|                |                     | 1               | Ι   | ST                   | PORTC<5> data input.                                                                                                                            |

|                | SDO                 | 0               | 0   | DIG                  | SPI data output (MSSP module); takes priority over port data.                                                                                   |

| RC6/TX/CK      | RC6                 | 0               | 0   | DIG                  | LATC<6> data output.                                                                                                                            |

|                |                     | 1               | I   | ST                   | PORTC<6> data input.                                                                                                                            |

|                | ТХ                  | 1               | 0   | DIG                  | Asynchronous serial transmit data output (EUSART module);<br>takes priority over port data. User must configure as output.                      |

|                | СК                  | 1               | 0   | DIG                  | Synchronous serial clock output (EUSART module); takes priority over port data.                                                                 |

|                |                     | 1               | I   | ST                   | Synchronous serial clock input (EUSART module).                                                                                                 |

| RC7/RX/DT      | RC7                 | 0               | 0   | DIG                  | LATC<7> data output.                                                                                                                            |

|                |                     | 1               | 1   | ST                   | PORTC<7> data input.                                                                                                                            |

|                | RX                  | 1               | I   | ST                   | Asynchronous serial receive data input (EUSART module).                                                                                         |

|                | DT                  | 1               | 0   | DIG                  | Synchronous serial data output (EUSART module); takes priority over port data.                                                                  |

|                |                     | 1               | Ι   | ST                   | Synchronous serial data input (EUSART module). User must configure as an input.                                                                 |

### TABLE 10-5: PORTC I/O SUMMARY

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output;  $I^2C/SMB = I^2C/SMB$  us input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Default assignment for CCP2 when the CCP2MX Configuration bit is set. Alternate assignment is RB3.

2: Enhanced PWM output is available only on PIC18F4520 devices.

| R-0               | R-0                     | R/W-0                                   | R/W-0                         | U-0              | R/W-1           | R/W-1              | R/W-1    |  |

|-------------------|-------------------------|-----------------------------------------|-------------------------------|------------------|-----------------|--------------------|----------|--|

| IBF               | OBF                     | IBOV                                    | PSPMODE                       | —                | TRISE2          | TRISE1             | TRISE0   |  |

| bit 7             | L                       |                                         |                               |                  |                 |                    | bit      |  |

| Legend:           |                         |                                         |                               |                  |                 |                    |          |  |

| R = Readab        | le hit                  | W = Writable                            | bit                           | II = Unimplen    | nented bit, rea | d as '0'           |          |  |

| -n = Value at POR |                         | '1' = Bit is se                         |                               | '0' = Bit is cle |                 | x = Bit is unknown |          |  |

|                   |                         |                                         |                               |                  |                 |                    |          |  |

| bit 7             | IBF: Input B            | uffer Full Status                       | bit                           |                  |                 |                    |          |  |

|                   |                         | has been receiv<br>has been rece        | ed and waiting i<br>ived      | to be read by t  | he CPU          |                    |          |  |

| bit 6             | OBF: Output             | t Buffer Full Sta                       | tus bit                       |                  |                 |                    |          |  |

|                   |                         | out buffer still ho<br>out buffer has b | olds a previously<br>een read | y written word   |                 |                    |          |  |

| bit 5             | IBOV: Input             | Buffer Overflow                         | Detect bit (in N              | /licroprocessor  | mode)           |                    |          |  |

|                   |                         | ccurred when a<br>low occurred          | previously input              | word has not b   | een read (must  | be cleared in so   | oftware) |  |

| bit 4             | PSPMODE:                | Parallel Slave I                        | Port Mode Sele                | ct bit           |                 |                    |          |  |

|                   |                         | Slave Port mod<br>purpose I/O mo        |                               |                  |                 |                    |          |  |

| bit 3             | Unimpleme               | nted: Read as                           | ʻ0 <b>'</b>                   |                  |                 |                    |          |  |

| bit 2             | TRISE2: RE              | 2 Direction Cor                         | ntrol bit                     |                  |                 |                    |          |  |

|                   | 1 = Input               |                                         |                               |                  |                 |                    |          |  |

|                   | 0 = Output              |                                         |                               |                  |                 |                    |          |  |

| bit 1             | -                       | 1 Direction Cor                         | ntrol bit                     |                  |                 |                    |          |  |

|                   | 1 = Input<br>0 = Output |                                         |                               |                  |                 |                    |          |  |

| bit 0             | •                       | 0 Direction Cor                         | ntrol bit                     |                  |                 |                    |          |  |

|                   | 1 = Input               |                                         |                               |                  |                 |                    |          |  |

# REGISTER 10-1: TRISE REGISTER (40/44-PIN DEVICES ONLY)

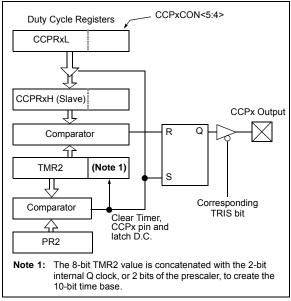

### 15.4 PWM Mode

In Pulse-Width Modulation (PWM) mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP2 pin is multiplexed with a PORTB or PORTC data latch, the appropriate TRIS bit must be cleared to make the CCP2 pin an output.

| Note: | Clearing the CCP2CON register will force  |

|-------|-------------------------------------------|

|       | the RB3 or RC1 output latch (depending on |

|       | device configuration) to the default low  |

|       | level. This is not the PORTB or PORTC I/O |

|       | data latch.                               |

Figure 15-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 15.4.4** "Setup for PWM Operation".

#### FIGURE 15-3: SIMPLIFIED PWM BLOCK DIAGRAM

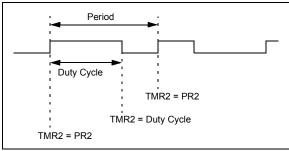

A PWM output (Figure 15-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

### 15.4.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

#### **EQUATION 15-1:**

$PWM Period = [(PR2) + 1] \bullet 4 \bullet TOSC \bullet$ (TMR2 Prescale Value)

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCPx pin is set (exception: if PWM duty cycle = 0%, the CCPx pin will not be set)

- The PWM duty cycle is latched from CCPRxL into CCPRxH

### 15.4.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPRxL register and to the CCPxCON<5:4> bits. Up to 10-bit resolution is available. The CCPRxL contains the eight MSbs and the CCPxCON<5:4> bits contain the two LSbs. This 10-bit value is represented by CCPRxL:CCPxCON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

#### **EQUATION 15-2:**

```

PWM Duty Cycle = (CCPRxL:CCPxCON<5:4>) •

Tosc • (TMR2 Prescale Value)

```

CCPRxL and CCPxCON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPRxH until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPRxH is a read-only register.

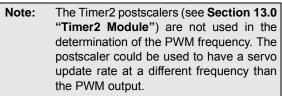

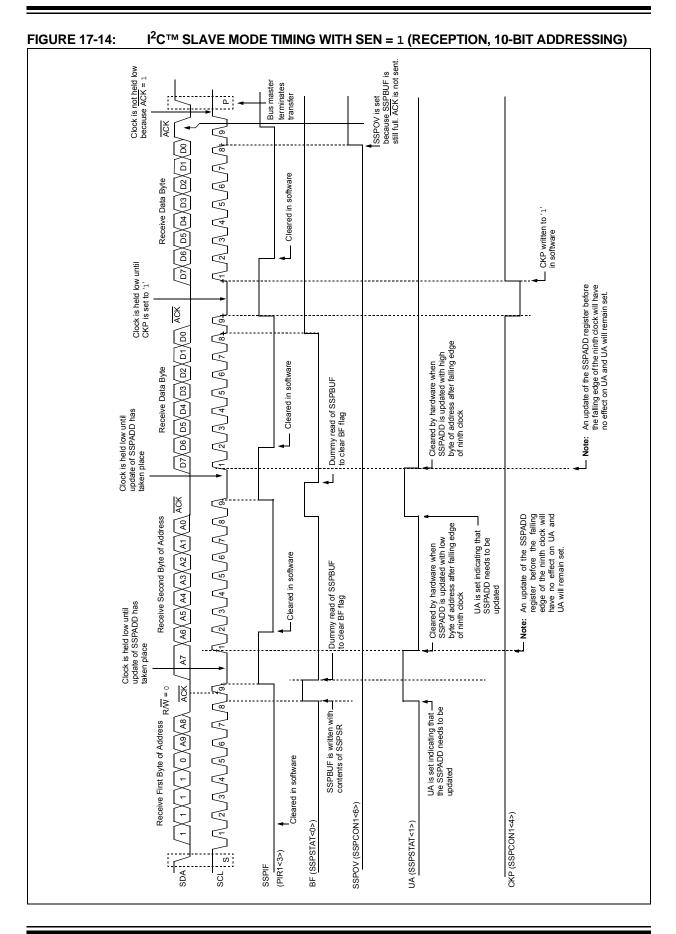

### 17.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

### 17.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

## FIGURE 17-20: REPEATED START CONDITION WAVEFORM

## **19.1** A/D Acquisition Requirements

For the A/D Converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 19-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . After the analog input channel is selected (changed), the channel must be sampled for at least the minimum acquisition time before starting a conversion.

Note: When the conversion is started, the holding capacitor is disconnected from the input pin.

EQUATION 19-1: ACQUISITION TIME

TACQ = Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient = TAMP + TC + TCOFF

#### EQUATION 19-2: A/D MINIMUM CHARGING TIME

| VHOLD | = | $(\text{VREF} - (\text{VREF}/2048)) \bullet (1 - e^{(-\text{TC/CHOLD}(\text{Ric} + \text{Rss} + \text{Rs}))})$ |

|-------|---|----------------------------------------------------------------------------------------------------------------|

| or    |   |                                                                                                                |

| TC    | = | -(CHOLD)(RIC + RSS + RS) ln(1/2048)                                                                            |

#### EQUATION 19-3: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME

| TACQ                                                                                          | = | TAMP + TC + TCOFF                                                                                                                                |  |  |

|-----------------------------------------------------------------------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TAMP                                                                                          | = | 0.2 µs                                                                                                                                           |  |  |

| TCOFF                                                                                         | = | (Temp – 25°C)(0.02 μs/°C)<br>(85°C – 25°C)(0.02 μs/°C)<br>1.2 μs                                                                                 |  |  |

| Temperature coefficient is only required for temperatures > 25°C. Below 25°C, TCOFF = 0 $\mu$ |   |                                                                                                                                                  |  |  |

| Тс                                                                                            | = | -(Chold)(Ric + Rss + Rs) $\ln(1/2047) \ \mu s$<br>-(25 pF) (1 k $\Omega$ + 2 k $\Omega$ + 2.5 k $\Omega$ ) ln(0.0004883) $\mu s$<br>1.05 $\mu s$ |  |  |

| TACQ                                                                                          | = | $0.2 \ \mu s + 1 \ \mu s + 1.2 \ \mu s$<br>2.4 \ \ \ \ \ \ \ \ s                                                                                 |  |  |

To calculate the minimum acquisition time, Equation 19-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

Example 19-3 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following application system assumptions:

| CHOLD            | =      | 25 pF                              |

|------------------|--------|------------------------------------|

| Rs               | =      | 2.5 kΩ                             |

| Conversion Error | $\leq$ | 1/2 LSb                            |

| Vdd              | =      | $5V  ightarrow Rss$ = 2 k $\Omega$ |

| Temperature      | =      | 85°C (system max.)                 |

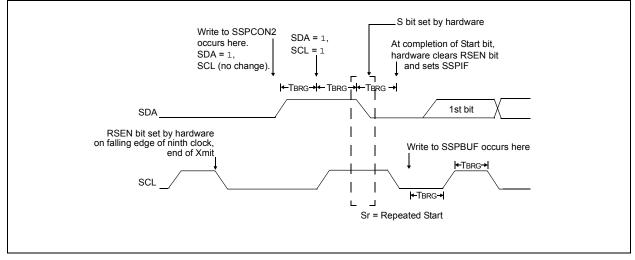

#### FIGURE 20-3: COMPARATOR OUTPUT BLOCK DIAGRAM

#### 20.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that occurred. The CMIF bit (PIR2<6>) is the Comparator Interrupt Flag. The CMIF bit must be reset by clearing it. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

Both the CMIE bit (PIE2<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit (INTCON<7>) must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | If a change in the CMCON register          |

|-------|--------------------------------------------|

|       | (C1OUT or C2OUT) should occur when a       |

|       | read operation is being executed (start of |

|       | the Q2 cycle), then the CMIF (PIR2<6>)     |

|       | interrupt flag may not get set.            |

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON will end the mismatch condition.

- b) Clear flag bit, CMIF.

A mismatch condition will continue to set flag bit, CMIF. Reading CMCON will end the mismatch condition and allow flag bit, CMIF, to be cleared.

## 20.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from Sleep mode when enabled. Each operational comparator will consume additional current, as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators (CM<2:0> = 111) before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

#### 20.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator modules to be turned off (CM<2:0> = 111). However, the input pins (RA0 through RA3) are configured as analog inputs by default on device Reset. The I/O configuration for these pins is determined by the setting of the PCFG<3:0> bits (ADCON1<3:0>). Therefore, device current is minimized when analog inputs are present at Reset time.

## 22.2 HLVD Setup

The following steps are needed to set up the HLVD module:

- 1. Write the value to the HLVDL<3:0> bits that selects the desired HLVD trip point.

- Set the VDIRMAG bit to detect high voltage (VDIRMAG = 1) or low voltage (VDIRMAG = 0).

- 3. Enable the HLVD module by setting the HLVDEN bit.

- 4. Clear the HLVD interrupt flag (PIR2<2>), which may have been set from a previous interrupt.

- Enable the HLVD interrupt, if interrupts are desired, by setting the HLVDIE and GIE bits (PIE2<2> and INTCON<7>). An interrupt will not be generated until the IRVST bit is set.

## 22.3 Current Consumption

When the module is enabled, the HLVD comparator and voltage divider are enabled and will consume static current. The total current consumption, when enabled, is specified in electrical specification parameter D022B. Depending on the application, the HLVD module does not need to be operating constantly. To decrease the current requirements, the HLVD circuitry may only need to be enabled for short periods where the voltage is checked. After doing the check, the HLVD module may be disabled.

## 22.4 HLVD Start-up Time

The internal reference voltage of the HLVD module, specified in electrical specification parameter D420, may be used by other internal circuitry, such as the programmable Brown-out Reset. If the HLVD or other circuits using the voltage reference are disabled to lower the device's current consumption, the reference voltage circuit will require time to become stable before a low or high-voltage condition can be reliably detected. This start-up time, TIRVST, is an interval that is independent of device clock speed. It is specified in electrical specification parameter 36.

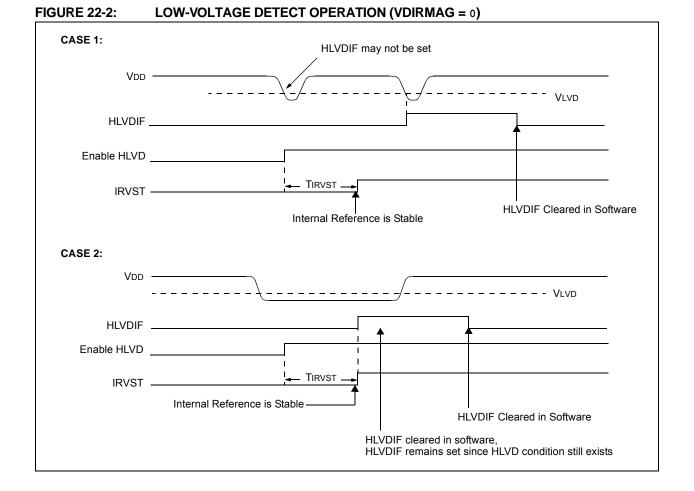

The HLVD interrupt flag is not enabled until TIRVST has expired and a stable reference voltage is reached. For this reason, brief excursions beyond the set point may not be detected during this interval (refer to Figure 22-2 or Figure 22-3).

| Mnemonic,<br>Operands |        | Description                     | Cycles | 16-Bit Instruction Word |      |      |      | Status          | Notes |

|-----------------------|--------|---------------------------------|--------|-------------------------|------|------|------|-----------------|-------|

|                       |        | Description                     | Cycles | MSb                     |      |      | LSb  | Affected        | Notes |

| LITERAL C             | OPERAT | TIONS                           |        |                         |      |      |      |                 |       |

| ADDLW                 | k      | Add Literal and WREG            | 1      | 0000                    | 1111 | kkkk | kkkk | C, DC, Z, OV, N |       |

| ANDLW                 | k      | AND Literal with WREG           | 1      | 0000                    | 1011 | kkkk | kkkk | Z, N            |       |

| IORLW                 | k      | Inclusive OR Literal with WREG  | 1      | 0000                    | 1001 | kkkk | kkkk | Z, N            |       |

| LFSR                  | f, k   | Move Literal (12-bit)2nd word   | 2      | 1110                    | 1110 | 00ff | kkkk | None            |       |

|                       |        | to FSR(f) 1st word              |        | 1111                    | 0000 | kkkk | kkkk |                 |       |

| MOVLB                 | k      | Move Literal to BSR<3:0>        | 1      | 0000                    | 0001 | 0000 | kkkk | None            |       |

| MOVLW                 | k      | Move Literal to WREG            | 1      | 0000                    | 1110 | kkkk | kkkk | None            |       |

| MULLW                 | k      | Multiply Literal with WREG      | 1      | 0000                    | 1101 | kkkk | kkkk | None            |       |

| RETLW                 | k      | Return with Literal in WREG     | 2      | 0000                    | 1100 | kkkk | kkkk | None            |       |

| SUBLW                 | k      | Subtract WREG from Literal      | 1      | 0000                    | 1000 | kkkk | kkkk | C, DC, Z, OV, N |       |

| XORLW                 | k      | Exclusive OR Literal with WREG  | 1      | 0000                    | 1010 | kkkk | kkkk | Z, N            |       |

| DATA MEN              | IORY ← | PROGRAM MEMORY OPERATION        | NS     |                         |      |      |      |                 |       |

| TBLRD*                |        | Table Read                      | 2      | 0000                    | 0000 | 0000 | 1000 | None            |       |

| TBLRD*+               |        | Table Read with Post-Increment  |        | 0000                    | 0000 | 0000 | 1001 | None            |       |

| TBLRD*-               |        | Table Read with Post-Decrement  |        | 0000                    | 0000 | 0000 | 1010 | None            |       |

| TBLRD+*               |        | Table Read with Pre-Increment   |        | 0000                    | 0000 | 0000 | 1011 | None            |       |

| TBLWT*                |        | Table Write                     | 2      | 0000                    | 0000 | 0000 | 1100 | None            |       |

| TBLWT*+               |        | Table Write with Post-Increment |        | 0000                    | 0000 | 0000 | 1101 | None            |       |

| TBLWT*-               |        | Table Write with Post-Decrement |        | 0000                    | 0000 | 0000 | 1110 | None            |       |

| TBLWT+*               |        | Table Write with Pre-Increment  |        | 0000                    | 0000 | 0000 | 1111 | None            |       |

#### TABLE 24-2: PIC18FXXXX INSTRUCTION SET (CONTINUED)

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| TG f, b {,a}<br>$\leq f \leq 255$<br>$\leq b < 7$<br>$\in [0,1]$<br>$\overline{\langle b \rangle} \rightarrow f < b >$<br>one<br>0111 bbba ffff ffff<br>it 'b' in data memory location 'f' is<br>iverted.<br>'a' is '0', the Access Bank is selected.<br>'a' is '0', the Access Bank is selected.<br>'a' is '1', the BSR is used to select the<br>iPR bank (default).<br>'a' is '0' and the extended instruction<br>et is enabled, this instruction operates<br>indexed Literal Offset Addressing<br>node whenever f $\leq 95$ (5Fh). See | Syntax:<br>Operands:<br>Operation:<br>Status Affected<br>Encoding:<br>Description:<br>Words: | 1110If the Over<br>program wThe 2's co<br>added to the<br>incrementer<br>instructionPC + 2 + 2<br>two-cycle1                                                                                                                             | bit is '1',<br>$2n \rightarrow PC$<br>0100 nm<br>flow bit is '1', th                                                                                                                                                                                                                                                                                                                                                 | hen the<br>ber, '2n', is<br>e PC will have<br>next<br>ess will be                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $ \leq b < 7 \\ \in [0,1] \\ \hline \\ $                                                                                                                                                                                                                                                                                                                                                                                                                  | Operation:<br>Status Affected<br>Encoding:<br>Description:<br>Words:                         | if Overflow<br>(PC) + 2 +<br>None<br>1110<br>If the Over<br>program w<br>The 2's co<br>added to th<br>increment<br>instruction<br>PC + 2 + 2<br>two-cycle<br>1                                                                           | y bit is '1',<br>$2n \rightarrow PC$<br>1000 nmm<br>flow bit is '1', th<br>ill branch.<br>mplement num<br>ne PC. Since the<br>ed to fetch the in<br>, the new addressed<br>2n. This instruct                                                                                                                                                                                                                         | hen the<br>ber, '2n', is<br>e PC will have<br>next<br>ess will be                                                                                                                                                                                                                                                                                        |

| $\begin{array}{c} \in [0,1] \\ \hline \\ $                                                                                                                                                                                                                                                                                                                                                                                                                | Status Affected<br>Encoding:<br>Description:<br>Words:                                       | (PC) + 2 +<br>None<br>1110<br>If the Over<br>program w<br>The 2's co<br>added to th<br>increment<br>instruction<br>PC + 2 + 2<br>two-cycle                                                                                               | $2n \rightarrow PC$<br>0100 nm<br>flow bit is '1', th<br>fill branch.<br>mplement num<br>he PC. Since the<br>ed to fetch the is<br>, the new address<br>2n. This instruct                                                                                                                                                                                                                                            | hen the<br>ber, '2n', is<br>e PC will have<br>next<br>ess will be                                                                                                                                                                                                                                                                                        |

| one<br>0111 bbba ffff ffff<br>it 'b' in data memory location 'f' is<br>iverted.<br>'a' is '0', the Access Bank is selected.<br>'a' is '1', the BSR is used to select the<br>PR bank (default).<br>'a' is '0' and the extended instruction<br>et is enabled, this instruction operates<br>Indexed Literal Offset Addressing                                                                                                                                                                                                                | Encoding:<br>Description:<br>Words:                                                          | 1110If the Over<br>program wThe 2's co<br>added to the<br>incrementer<br>instructionPC + 2 + 2<br>two-cycle1                                                                                                                             | flow bit is '1', th<br>rill branch.<br>mplement num<br>re PC. Since th<br>ed to fetch the i<br>, the new addre<br>2n. This instruct                                                                                                                                                                                                                                                                                  | hen the<br>ber, '2n', is<br>e PC will have<br>next<br>ess will be                                                                                                                                                                                                                                                                                        |

| 0111bbbaffffffffit 'b' in data memory location 'f' is<br>overted.'a' is '0', the Access Bank is selected.'a' is '0', the BSR is used to select the<br>iPR bank (default).'a' is '0' and the extended instruction<br>et is enabled, this instruction operates<br>Indexed Literal Offset Addressing                                                                                                                                                                                                                                         | Description:<br>Words:                                                                       | If the Over<br>program w<br>The 2's co<br>added to th<br>increment<br>instruction<br>PC + 2 + 2<br>two-cycle                                                                                                                             | flow bit is '1', th<br>rill branch.<br>mplement num<br>re PC. Since th<br>ed to fetch the i<br>, the new addre<br>2n. This instruct                                                                                                                                                                                                                                                                                  | hen the<br>ber, '2n', is<br>e PC will have<br>next<br>ess will be                                                                                                                                                                                                                                                                                        |

| it 'b' in data memory location 'f' is<br>werted.<br>'a' is '0', the Access Bank is selected.<br>'a' is '1', the BSR is used to select the<br>IPR bank (default).<br>'a' is '0' and the extended instruction<br>et is enabled, this instruction operates<br>Indexed Literal Offset Addressing                                                                                                                                                                                                                                              | Description:<br>Words:                                                                       | program w<br>The 2's co<br>added to th<br>incrementu<br>instruction<br>PC + 2 + 2<br>two-cycle                                                                                                                                           | flow bit is '1', th<br>rill branch.<br>mplement num<br>re PC. Since th<br>ed to fetch the i<br>, the new addre<br>2n. This instruct                                                                                                                                                                                                                                                                                  | ber, '2n', is<br>e PC will have<br>next<br>ess will be                                                                                                                                                                                                                                                                                                   |

| verted.<br>'a' is '0', the Access Bank is selected.<br>'a' is '1', the BSR is used to select the<br>PR bank (default).<br>'a' is '0' and the extended instruction<br>et is enabled, this instruction operates<br>Indexed Literal Offset Addressing                                                                                                                                                                                                                                                                                        | Words:                                                                                       | program w<br>The 2's co<br>added to th<br>incrementu<br>instruction<br>PC + 2 + 2<br>two-cycle                                                                                                                                           | vill branch.<br>mplement num<br>ne PC. Since th<br>ed to fetch the r<br>, the new addre<br>?n. This instruct                                                                                                                                                                                                                                                                                                         | ber, '2n', is<br>e PC will have<br>next<br>ess will be                                                                                                                                                                                                                                                                                                   |

| ection 24.2.3 "Byte-Oriented and<br>it-Oriented Instructions in Indexed<br>iteral Offset Mode" for details.                                                                                                                                                                                                                                                                                                                                                                                                                               | Cycles:<br>Q Cycle Activi<br>If Jump:                                                        | 1(2)<br>ity:                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              | 02                                                                                                                                                                                                                                       | 03                                                                                                                                                                                                                                                                                                                                                                                                                   | Q4                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |                                                                                                                                                                                                                                          | Process                                                                                                                                                                                                                                                                                                                                                                                                              | Write to PC                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              | 'n'                                                                                                                                                                                                                                      | Data                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                          |

| Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | No                                                                                           | No                                                                                                                                                                                                                                       | No                                                                                                                                                                                                                                                                                                                                                                                                                   | No                                                                                                                                                                                                                                                                                                                                                       |

| Read Process Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              | operation                                                                                                                                                                                                                                | operation                                                                                                                                                                                                                                                                                                                                                                                                            | operation                                                                                                                                                                                                                                                                                                                                                |

| gister 'f' Data register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                                                                                            | Q2                                                                                                                                                                                                                                       | Q3                                                                                                                                                                                                                                                                                                                                                                                                                   | Q4                                                                                                                                                                                                                                                                                                                                                       |

| IG PORTC, 4, 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                              |                                                                                                                                                                                                                                          | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                      | No<br>operation                                                                                                                                                                                                                                                                                                                                          |

| 0111 0101 <b>[75h]</b><br>0110 0101 <b>[65h]</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PC<br>After Instr<br>If Ov                                                                   | = a<br>ruction<br>verflow = 1<br>PC = a                                                                                                                                                                                                  | ddress (Jump                                                                                                                                                                                                                                                                                                                                                                                                         | )                                                                                                                                                                                                                                                                                                                                                        |

| g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | g PORTC, 4, 0<br>0111 0101 <b>[75h]</b>                                                      | Q2     Q3     Q4       Read process     Write register 'f'       Data     register 'f'       G     PORTC, 4, 0       0111     0101       0110     0101       0110     0101       [65h]         Example:       PC       After Instruction | Q2       Q3       Q4         Read       Process       Write         jister 'f'       Data       register 'f'         G       PORTC, 4, 0       If No Jump:         0111 0101 [75h]       Example:       HERE         0110 0101 [65h]       Example:       HERE         0110 0101 [65h]       PC       = aa         After Instruction       If Overflow       = 13         PC       = aa       If Overflow       = 03 | Q2     Q3     Q4       Read process lister 'f'     Write register 'f'       G     PORTC, 4, 0       0111 0101 [75h]     Example:       0110 0101 [65h]       Example:       HERE       Before Instruction       PC       address (HERE       After Instruction       If Overflow       If Overflow       If Overflow       If Overflow       If Overflow |

| Syntax:CLRF f {.a}Operands: $0 \le f \le 255$ $a \in [0,1]$ Operation:Operation: $000h \rightarrow f$ , $1 \rightarrow Z$ $1 \rightarrow Z$ Status Affected:ZEncoding: $0110$ $0110$ $101a$ f 'a' is 'o', the Access Bank is selected.If 'a' is 'o', and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f $\le 95$ (5Fh). SeeSection 24.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.Words:1Cycles:1Q Cycle Activity:Q 1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q2Q3Q4              | ,<br>,    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| $a \in [0,1]$ Operation: $000h \rightarrow f$ ,<br>$1 \rightarrow Z$ Operation: $000h \rightarrow WDT$ ,<br>$000h \rightarrow WDT postscalerStatus Affected:ZI \rightarrow \overline{TO},1 \rightarrow \overline{PD}I \rightarrow \overline{TO},1 \rightarrow \overline{PD}Status Affected:TO, \overline{PD}Description:Clears the contents of the specifiedregister.Status Affected:TO, \overline{PD}Encoding:0000  0000  000If 'a' is 'o', the Access Bank is selected.If 'a' is 'o', the Access Bank is selected.If 'a' is 'o' and the extended instructionset is enabled, this instruction operatesin Indexed Literal Offset Addressingmode whenever f \leq 95 (5Fh). SeeSection 24.2.3 "Byte-Oriented andBit-Oriented Instructions in IndexedLiteral Offset Mode" for details.Words:1Words:1Q1Q2Q3Q Cycle Activity:Q1Q2Q3DecodeNoProcessoperationDataData$ | ,         |

| Operation: $000h \rightarrow f,$<br>$1 \rightarrow Z$ $000h \rightarrow WDT$ postscalerStatus Affected:Z $1 \rightarrow \overline{D},$<br>$1 \rightarrow \overline{PD}$ Encoding: $0110$ $101a$ ffffDescription:Clears the contents of the specified<br>register.Status Affected: $\overline{TO}, \overline{PD}$ If 'a' is 'o', the Access Bank is selected.<br>If 'a' is 'o', the Access Bank is selected.<br>If 'a' is 'o' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f $\leq 95$ (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details.Words:1Words:1Q1Q2Q3Q Cycle Activity:Q1Q2Q3DecodeNoProcessoperationDataData                                                                             | 3         |

| $1 \rightarrow Z$ $1 \rightarrow \overline{TO}$ Status Affected:Z $1 \rightarrow \overline{TO}$ Encoding: $0110$ $101a$ ffffDescription:Clears the contents of the specified<br>register.<br>If 'a' is 'o', the Access Bank is selected.<br>If 'a' is 'o', the Access Bank is selected.<br>If 'a' is 'o' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details.Status Affected: $\overline{TO}, \overline{PD}$ Words:1CLRWDT instruction result<br>Words:Words:1Q Cycle Activity:Q1Q2Q3Q Cycle Activity:Q1Q2Q3DecodeNoProcessoperationDataDataQ Cycle Activity:Example:CLRWDTBefore InstructionExample:CLRWDT                               | ,         |

| Status Affected:Z $1 \rightarrow \overline{PD}$ Encoding:0110101affffffffDescription:Clears the contents of the specified<br>register.<br>If 'a' is 'o', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is 'o' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f $\leq$ 95 (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details.Uoto1Words:1Q2Q3Q Cycles:1Q2Q3DecodeNoProcess<br>OperationQ Cycle Activity:Example:CLRWDTQ Cycle Activity:Example:CLRWDT                                                                                                                                                                               |           |

| Status Affected:ZEncoding: $0110$ $101a$ ffffffffDescription:Clears the contents of the specified<br>register. $0000$ $0000$ $0000$ If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).Description:CLRWDT instruction result<br>Watchdog Timer. It also<br>scaler of the WDT. Statu<br>PD, are set.If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f $\leq$ 95 (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details.Words:1Words:1Q1Q2Q3DecodeNoProcess<br>operationQ Cycle Activity:1Example:CLRWDTQ cycle Activity:Example:CLRWDT                                                                                      |           |

| Encoding.0110101aIIIIIIIIDescription:Clears the contents of the specified<br>register.<br>If 'a' is 'o', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is 'o' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details.Encoding:00000000000Words:1Cycles:1Q cycle Activity:Q1Q2Q3DecodeNoProcess<br>operationQ cycle Activity:Example:CLRWDTQ cycle Activity:Example:CLRWDT                                                                                                                                                                                                    |           |

| Description:       Clears the contents of the specified         register.       If 'a' is 'o', the Access Bank is selected.         If 'a' is 'o', the Access Bank is selected.       Description:         If 'a' is 'o', the BSR is used to select the       Scaler of the WDT. Statu         GPR bank (default).       PD, are set.         If 'a' is 'o' and the extended instruction operates       No         in Indexed Literal Offset Addressing       Q1         mode whenever f ≤ 95 (5Fh). See       Q1         Section 24.2.3 "Byte-Oriented and       Decode         Bit-Oriented Instructions in Indexed       Decode         Literal Offset Mode" for details.       Decode         Words:       1         Cycles:       1         Q Cycle Activity:       Example:         CLRWDT       CLRWDT                                                   | 0.0       |

| If 'a' is 'o', the Access Bank is selected.       Watchdog Timer. It also scaler of the WDT. Statu PD, are set.         If 'a' is '1', the BSR is used to select the GPR bank (default).       Words:       1         If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See       Words:       1         Section 24.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.       Q1       Q2       Q3         Words:       1       Decode       No       Process operation       Data         Words:       1       Example:       CLRWDT       Example:       CLRWDT         Q Cycle Activity:       Before Instruction       Example:       CLRWDT       Before Instruction                                         |           |

| If 'a' is '1', the BSR is used to select the GPR bank (default).       scaler of the WDT. Statu PD, are set.         If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See       Words:       1         Section 24.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.       Q1       Q2       Q3         Words:       1       Decode       No       Process         Q Cycle Activity:       1       Decode       Data         Q Cycle Activity:       CLRWDT       Example:       CLRWDT         Q Cycle Activity:       Before Instruction       Example:       CLRWDT                                                                                                                                          |           |

| If 'a' is 'o' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See       Words:       1         Section 24.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.       Q Cycle Activity:       Q1       Q2       Q3         Words:       1       Decode       No       Process         Q Cycles:       1       Decode       No       Process         Q Cycle Activity:       CLRWDT       Example:       CLRWDT         Q Cycle Activity:       Before Instruction       Example:       CLRWDT                                                                                                                                                                                                                                   |           |

| set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details.     Cycles:     1       Words:     1     Q2     Q3       Decode     No     Process<br>operation       Vords:     1       Cycles:     1                                                                                                                                                                                                                                                                                                                                                           |           |

| in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See     Cycles:     1       Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details.     Q Cycle Activity:       Words:     1       Cycles:     1       Cycles:     1       Cycles:     1       Cycles:     1       Cycles:     1       Cycles:     1       Cycle Activity:     CLRWDT       Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                       |           |