Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 13x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4420-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 2-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq                               | Typical Capacitor Valu<br>Tested:        |                                          |  |

|----------|-----------------------------------------------|------------------------------------------|------------------------------------------|--|

|          | Fieq                                          | C1                                       | C2                                       |  |

| LP       | 32 kHz                                        | 30 pF                                    | 30 pF                                    |  |

| XT       | 1 MHz<br>4 MHz                                | 15 pF<br>15 pF                           | 15 pF<br>15 pF                           |  |

| HS       | 4 MHz<br>10 MHz<br>20 MHz<br>25 MHz<br>25 MHz | 15 pF<br>15 pF<br>15 pF<br>0 pF<br>15 pF | 15 pF<br>15 pF<br>15 pF<br>5 pF<br>15 pF |  |

Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. **These values are not optimized.**

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

| Crystals Used: |        |  |  |  |  |

|----------------|--------|--|--|--|--|

| 32 kHz         | 4 MHz  |  |  |  |  |

| 25 MHz         | 10 MHz |  |  |  |  |

| 1 MHz          | 20 MHz |  |  |  |  |

- **Note 1:** Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 2: When operating below 3V VDD, or when using certain ceramic resonators at any voltage, it may be necessary to use the HS mode or switch to a crystal oscillator.

- Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Rs may be required to avoid overdriving crystals with low drive level specification.

- 5: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

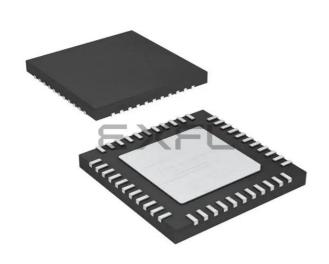

An external clock source may also be connected to the OSC1 pin in the HS mode, as shown in Figure 2-2.

#### EXTERNAL CLOCK INPUT OPERATION (HS OSC CONFIGURATION)

# 2.3 External Clock Input

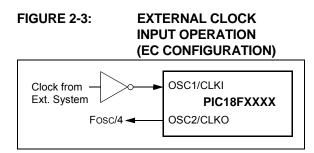

The EC and ECIO Oscillator modes require an external clock source to be connected to the OSC1 pin. There is no oscillator start-up time required after a Power-on Reset or after an exit from Sleep mode.

In the EC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 2-3 shows the pin connections for the EC Oscillator mode.

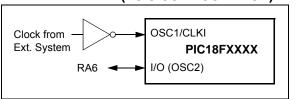

The ECIO Oscillator mode functions like the EC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 2-4 shows the pin connections for the ECIO Oscillator mode.

#### EXTERNAL CLOCK INPUT OPERATION (ECIO CONFIGURATION)

### 2.8 Effects of Power-Managed Modes on the Various Clock Sources

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin, if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_IDLE), the Timer1 oscillator is operating and providing the device clock. The Timer1 oscillator may also run in all power-managed modes if required to clock Timer1 or Timer3.

In internal oscillator modes (RC\_RUN and RC\_IDLE), the internal oscillator block provides the device clock source. The 31 kHz INTRC output can be used directly to provide the clock and may be enabled to support various special features, regardless of the powermanaged mode (see Section 23.2 "Watchdog Timer (WDT)", Section 23.3 "Two-Speed Start-up" and Section 23.4 "Fail-Safe Clock Monitor" for more information on WDT, Fail-Safe Clock Monitor and Two-Speed Start-up). The INTOSC output at 8 MHz may be used directly to clock the device or may be divided down by the postscaler. The INTOSC output is disabled if the clock is provided directly from the INTRC output.

If Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support a Real-Time Clock. Other features may be operating that do not require a device clock source (i.e., MSSP slave, PSP, INTx pins and others). Peripherals that may add significant current consumption are listed in **Section 26.2 "DC Characteristics".**

# 2.9 Power-up Delays

Power-up delays are controlled by two timers so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 4.5 "Device Reset Timers"**.

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on power-up (parameter 33, Table 26-10). It is enabled by clearing (= 0) the PWRTEN Configuration bit.

The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (LP, XT and HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

When the HSPLL Oscillator mode is selected, the device is kept in Reset for an additional 2 ms, following the HS mode OST delay, so the PLL can lock to the incoming clock frequency.

There is a delay of interval, TCSD (parameter 38, Table 26-10), following POR, while the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the EC, RC or INTIO modes are used as the primary clock source.

| OSC Mode      | OSC1 Pin                                              | OSC2 Pin                                              |

|---------------|-------------------------------------------------------|-------------------------------------------------------|

| RC, INTIO1    | Floating, external resistor should pull high          | At logic low (clock/4 output)                         |

| RCIO          | Floating, external resistor should pull high          | Configured as PORTA, bit 6                            |

| INTIO2        | Configured as PORTA, bit 7                            | Configured as PORTA, bit 6                            |

| ECIO          | Floating, pulled by external clock                    | Configured as PORTA, bit 6                            |

| EC            | Floating, pulled by external clock                    | At logic low (clock/4 output)                         |

| LP, XT and HS | Feedback inverter disabled at quiescent voltage level | Feedback inverter disabled at quiescent voltage level |

TABLE 2-3:OSC1 AND OSC2 PIN STATES IN SLEEP MODE

Note: See Table 4-2 in Section 4.0 "Reset" for time-outs due to Sleep and MCLR Reset.

| Register            | Register Applicable D |      | e Device | s    | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |

|---------------------|-----------------------|------|----------|------|------------------------------------|------------------------------------------------------------------|---------------------------------|--|

| FSR1H               | 2420                  | 2520 | 4420     | 4520 | 0000                               | 0000                                                             | uuuu                            |  |

| FSR1L               | 2420                  | 2520 | 4420     | 4520 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| BSR                 | 2420                  | 2520 | 4420     | 4520 | 0000                               | 0000                                                             | uuuu                            |  |

| INDF2               | 2420                  | 2520 | 4420     | 4520 | N/A                                | N/A                                                              | N/A                             |  |

| POSTINC2            | 2420                  | 2520 | 4420     | 4520 | N/A                                | N/A                                                              | N/A                             |  |

| POSTDEC2            | 2420                  | 2520 | 4420     | 4520 | N/A                                | N/A                                                              | N/A                             |  |

| PREINC2             | 2420                  | 2520 | 4420     | 4520 | N/A                                | N/A                                                              | N/A                             |  |

| PLUSW2              | 2420                  | 2520 | 4420     | 4520 | N/A                                | N/A                                                              | N/A                             |  |

| FSR2H               | 2420                  | 2520 | 4420     | 4520 | 0000                               | 0000                                                             | uuuu                            |  |

| FSR2L               | 2420                  | 2520 | 4420     | 4520 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| STATUS              | 2420                  | 2520 | 4420     | 4520 | x xxxx                             | u uuuu                                                           | u uuuu                          |  |

| TMR0H               | 2420                  | 2520 | 4420     | 4520 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

| TMR0L               | 2420                  | 2520 | 4420     | 4520 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| TOCON               | 2420                  | 2520 | 4420     | 4520 | 1111 1111                          | 1111 1111                                                        | uuuu uuuu                       |  |

| OSCCON              | 2420                  | 2520 | 4420     | 4520 | 0100 q000                          | 0100 q000                                                        | uuuu quuu                       |  |

| HLVDCON             | 2420                  | 2520 | 4420     | 4520 | 0-00 0101                          | 0-00 0101                                                        | u-uu uuuu                       |  |

| WDTCON              | 2420                  | 2520 | 4420     | 4520 | 0                                  | 0                                                                | u                               |  |

| RCON <sup>(4)</sup> | 2420                  | 2520 | 4420     | 4520 | 0q-1 11q0                          | 0q-q qquu                                                        | uq-u qquu                       |  |

| TMR1H               | 2420                  | 2520 | 4420     | 4520 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| TMR1L               | 2420                  | 2520 | 4420     | 4520 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| T1CON               | 2420                  | 2520 | 4420     | 4520 | 0000 0000                          | u0uu uuuu                                                        | uuuu uuuu                       |  |

| TMR2                | 2420                  | 2520 | 4420     | 4520 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

| PR2                 | 2420                  | 2520 | 4420     | 4520 | 1111 1111                          | 1111 1111                                                        | 1111 1111                       |  |

| T2CON               | 2420                  | 2520 | 4420     | 4520 | -000 0000                          | -000 0000                                                        | -uuu uuuu                       |  |

| SSPBUF              | 2420                  | 2520 | 4420     | 4520 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| SSPADD              | 2420                  | 2520 | 4420     | 4520 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

| SSPSTAT             | 2420                  | 2520 | 4420     | 4520 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

| SSPCON1             | 2420                  | 2520 | 4420     | 4520 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

| SSPCON2             | 2420                  | 2520 | 4420     | 4520 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

### TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 4-3 for Reset value for specific condition.

5: Bits 6 and 7 of PORTA, LATA and TRISA are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

**6:** The Reset value of the PCFG bits depends on the value of the PBADEN Configuration bit (CONFIG3H<1>). When PBADEN = 1, PCFG<2:0> = 000; when PBADEN = 0, PCFG<2:0> = 111.

# 7.0 DATA EEPROM MEMORY

The data EEPROM is a nonvolatile memory array, separate from the data RAM and program memory, that is used for long-term storage of program data. It is not directly mapped in either the register file or program memory space but is indirectly addressed through the Special Function Registers (SFRs). The EEPROM is readable and writable during normal operation over the entire VDD range.

Five SFRs are used to read and write to the data EEPROM as well as the program memory. They are:

- EECON1

- EECON2

- EEDATA

- EEADR

The data EEPROM allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and the EEADR register holds the address of the EEPROM location being accessed.

The EEPROM data memory is rated for high erase/write cycle endurance. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an on-chip timer; it will vary with voltage and temperature as well as from chip to chip. Please refer to parameter D122 (Table 26-1 in **Section 26.0 "Electrical Characteristics"**) for exact limits.

# 7.1 EEADR Register

The EEADR register is used to address the data EEPROM for read and write operations. The 8-bit range of the register can address a memory range of 256 bytes (00h to FFh).

#### 7.2 EECON1 and EECON2 Registers

Access to the data EEPROM is controlled by two registers: EECON1 and EECON2. These are the same registers which control access to the program memory and are used in a similar manner for the data EEPROM.

The EECON1 register (Register 7-1) is the control register for data and program memory access. Control bit EEPGD determines if the access will be to program or data EEPROM memory. When clear, operations will access the data EEPROM memory. When set, program memory is accessed.

Control bit, CFGS, determines if the access will be to the Configuration registers or to program memory/data EEPROM memory. When set, subsequent operations access Configuration registers. When CFGS is clear, the EEPGD bit selects either program Flash or data EEPROM memory.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR         |

|-------|--------------------------------------------|

|       | may read as '1'. This can indicate that a  |

|       | write operation was prematurely termi-     |

|       | nated by a Reset, or a write operation was |

|       | attempted improperly.                      |

The WR control bit initiates write operations. The bit can be set but not cleared in software. It is only cleared in hardware at the completion of the write operation.

**Note:** The EEIF interrupt flag bit (PIR2<4>) is set when the write is complete. It must be cleared in software.

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (EEPGD = 1). Program memory is read using table read instructions. See **Section 6.1 "Table Reads and Table Writes"** regarding table reads.

The EECON2 register is not a physical register. It is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

| OSCFIE          |                                                                                                    | U-0                | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|-----------------|----------------------------------------------------------------------------------------------------|--------------------|-----------------|------------------|------------------|-----------------|--------|

|                 | CMIE                                                                                               |                    | EEIE            | BCLIE            | HLVDIE           | TMR3IE          | CCP2IE |

| oit 7           |                                                                                                    |                    | I.              |                  |                  | I               | bit (  |

|                 |                                                                                                    |                    |                 |                  |                  |                 |        |

| Legend:         |                                                                                                    |                    |                 |                  |                  |                 |        |

| R = Readable b  | it                                                                                                 | W = Writable       | bit             | U = Unimpler     | nented bit, read | l as '0'        |        |

| n = Value at PO | OR                                                                                                 | '1' = Bit is set   |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| 1               | <b>DSCFIE:</b> Osc<br>= Enabled<br>= Disabled                                                      | illator Fail Inter | rupt Enable b   | it               |                  |                 |        |

| 1               | CMIE: Comparator Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled                               |                    |                 |                  |                  |                 |        |

| oit 5 L         | Jnimplement                                                                                        | ted: Read as '     | )'              |                  |                  |                 |        |

| 1               | <b>EEIE:</b> Data EEPROM/Flash Write Operation Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled |                    |                 |                  |                  |                 |        |

|                 |                                                                                                    | Collision Interru  | pt Enable bit   |                  |                  |                 |        |

| 1               | 1 = Enabled<br>0 = Disabled                                                                        |                    |                 |                  |                  |                 |        |

| oit 2 H         | ILVDIE: High                                                                                       | /Low-Voltage [     | Detect Interrup | t Enable bit     |                  |                 |        |

|                 | = Enabled<br>= Disabled                                                                            |                    |                 |                  |                  |                 |        |

| oit 1 <b>1</b>  | MR3IE: TMF                                                                                         | R3 Overflow Int    | errupt Enable   | bit              |                  |                 |        |

|                 | = Enabled<br>= Disabled                                                                            |                    |                 |                  |                  |                 |        |

| oit 0 C         | CP2IE: CCP                                                                                         | 2 Interrupt Ena    | able bit        |                  |                  |                 |        |

|                 | = Enabled<br>= Disabled                                                                            |                    |                 |                  |                  |                 |        |

#### REGISTER 9-7: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

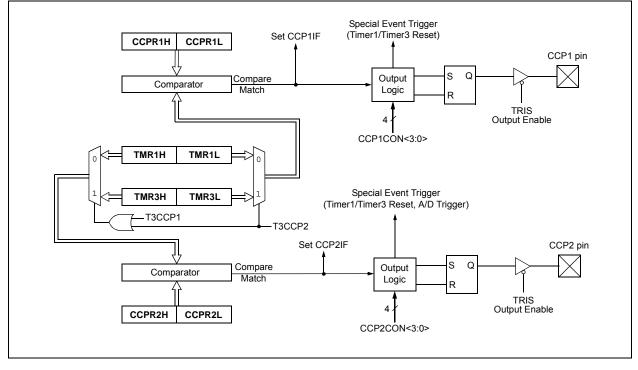

# 15.3 Compare Mode

In Compare mode, the 16-bit CCPRx register value is constantly compared against either the TMR1 or TMR3 register pair value. When a match occurs, the CCPx pin can be:

- · driven high

- · driven low

- toggled (high-to-low or low-to-high)

- remain unchanged (that is, reflects the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCPxM<3:0>). At the same time, the interrupt flag bit, CCPxIF, is set.

#### 15.3.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the appropriate TRIS bit.

| Note: | Clearing the CCP2CON register will force    |

|-------|---------------------------------------------|

|       | the RB3 or RC1 compare output latch         |

|       | (depending on device configuration) to the  |

|       | default low level. This is not the PORTB or |

|       | PORTC I/O data latch.                       |

### 15.3.2 TIMER1/TIMER3 MODE SELECTION

Timer1 and/or Timer3 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 15.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the corresponding CCPx pin is not affected. A CCP interrupt is generated when the CCPxIF interrupt flag is set while the CCPxIE bit is set.

#### 15.3.4 SPECIAL EVENT TRIGGER

Both CCP modules are equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode (CCPxM<3:0> = 1011).

For either CCP module, the Special Event Trigger resets the Timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPRx registers to serve as a programmable Period register for either timer.

The Special Event Trigger for CCP2 can also start an A/D conversion. In order to do this, the A/D Converter must already be enabled.

# FIGURE 15-2: COMPARE MODE OPERATION BLOCK DIAGRAM

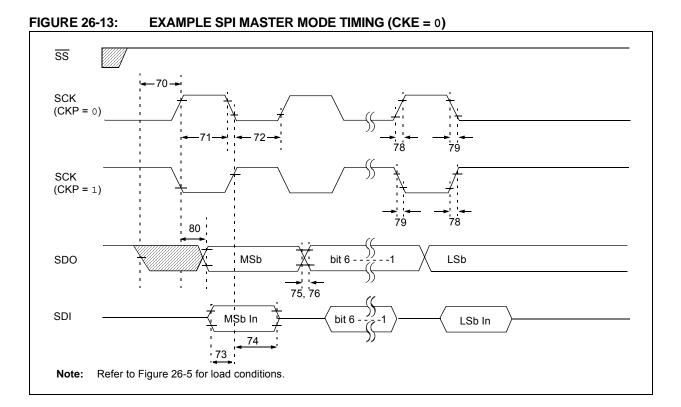

# 17.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON1<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- · Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

EVAMDI E 17-1.

· Slave Select mode (Slave mode only)

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full detect bit, BF (SSPSTAT<0>) and the interrupt flag bit, SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data

will be ignored and the write collision detect bit, WCOL (SSPCON1<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. The Buffer Full bit, BF (SSPSTAT<0>), indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 17-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP Status register (SSPSTAT) indicates the various status conditions.

Note: The SSPBUF register cannot be used with read-modify-write instructions such as BCF, BTFSC and COMF, etc.

|      |                      | . LOADING                        |                                                                                       |  |

|------|----------------------|----------------------------------|---------------------------------------------------------------------------------------|--|

| LOOP | BTFSS<br>BRA<br>MOVF | SSPSTAT, BF<br>LOOP<br>SSPBUF, W | ;Has data been received (transmit complete)?<br>;No<br>;WREG reg = contents of SSPBUF |  |

|      | MOVWF                | RXDATA                           | ;Save in user RAM, if data is meaningful                                              |  |

|      | MOVF<br>MOVWF        | TXDATA, W<br>SSPBUF              | ;W reg = contents of TXDATA<br>;New data to xmit                                      |  |

I OADING THE SODDIE (SODO) DECISTED

| Note: | To avoid lost data in Master mode, a read of the SSPBUF must be performed to clear |          |      |        |        |      |

|-------|------------------------------------------------------------------------------------|----------|------|--------|--------|------|

|       | the                                                                                | Buffer   | Full | (BF)   | detect | bit  |

|       | ``                                                                                 | PSTAT<0> | >)   | betwee | en     | each |

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 WCOL SSPOV SSPEN<sup>(1)</sup> CKP SSPM1 SSPM3 SSPM2 SSPM0 bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 7 WCOL: Write Collision Detect bit In Master Transmit mode: 1 = A write to the SSPBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started (must be cleared in software) 0 = No collision In Slave Transmit mode: 1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software) 0 = No collision In Receive mode (Master or Slave modes): This is a "don't care" bit. bit 6 SSPOV: Receive Overflow Indicator bit In Receive mode: 1 = A byte is received while the SSPBUF register is still holding the previous byte (must be cleared in software) 0 = No overflowIn Transmit mode: This is a "don't care" bit in Transmit mode. SSPEN: Master Synchronous Serial Port Enable bit<sup>(1)</sup> bit 5 1 = Enables the serial port and configures the SDA and SCL pins as the serial port pins 0 = Disables serial port and configures these pins as I/O port pins CKP: SCK Release Control bit bit 4 In Slave mode: 1 = Releases clock 0 = Holds clock low (clock stretch), used to ensure data setup time In Master mode: Unused in this mode. bit 3-0 SSPM<3:0>: Master Synchronous Serial Port Mode Select bits<sup>(2)</sup> 1111 = $I^2C$ Slave mode, 10-bit address with Start and Stop bit interrupts enabled 1110 = $I^2C$ Slave mode, 7-bit address with Start and Stop bit interrupts enabled $1011 = I^2C$ Firmware Controlled Master mode (Slave Idle) 1000 = I<sup>2</sup>C Master mode, clock = Fosc/(4 \* (SSPADD + 1)) $0111 = I^2C$ Slave mode, 10-bit address $0110 = I^2C$ Slave mode, 7-bit address Bit combinations not specifically listed here are either reserved or implemented in SPI mode only.

### REGISTER 17-4: SSPCON1: MSSP CONTROL REGISTER 1 (I<sup>2</sup>C™ MODE)

**Note 1:** When enabled, the SDA and SCL pins must be properly configured as inputs or outputs.

### 17.4.2 OPERATION

The MSSP module functions are enabled by setting the MSSP Enable bit, SSPEN (SSPCON1<5>).

The SSPCON1 register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON1<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Master mode, clock = (Fosc/4) x (SSPADD + 1)

- I<sup>2</sup>C Slave mode (7-bit addressing)

- I<sup>2</sup>C Slave mode (10-bit addressing)

- I<sup>2</sup>C Slave mode (7-bit addressing) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit addressing) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCL and SDA pins.

#### 17.4.3 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The I<sup>2</sup>C Slave mode hardware will always generate an interrupt on an address match. Through the mode select bits, the user can also choose to interrupt on Start and Stop bits

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the MSSP module not to give this ACK pulse:

- The Buffer Full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- The overflow bit, SSPOV (SSPCON2<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit, SSPIF (PIR1<3>), is set. The BF bit is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

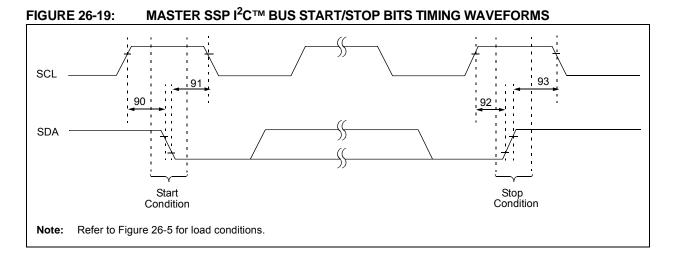

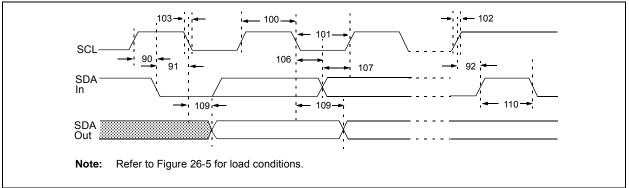

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing parameter 100 and parameter 101.

### 17.4.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- 1. The SSPSR register value is loaded into the SSPBUF register.

- 2. The Buffer Full bit, BF, is set.

- 3. An ACK pulse is generated.

- 4. MSSP Interrupt Flag bit, SSPIF (PIR1<3>), is set (interrupt is generated, if enabled) on the falling edge of the ninth SCL pulse.

In 10-Bit Addressing mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit, R/W (SSPSTAT<2>), must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-Bit Addressing mode is as follows, with steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of address (bits, SSPIF, BF and UA (SSPSTAT<1>), are set).

- Update the SSPADD register with second (low) byte of address (clears UA bit and releases the SCL line).

- 3. Read the SSPBUF register (clears BF bit) and clear flag bit, SSPIF.

- 4. Receive second (low) byte of address (bits, SSPIF, BF and UA, are set).

- 5. Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear bit, UA.

- 6. Read the SSPBUF register (clears BF bit) and clear flag bit, SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits, SSPIF and BF, are set).

- 9. Read the SSPBUF register (clears BF bit) and clear flag bit, SSPIF.

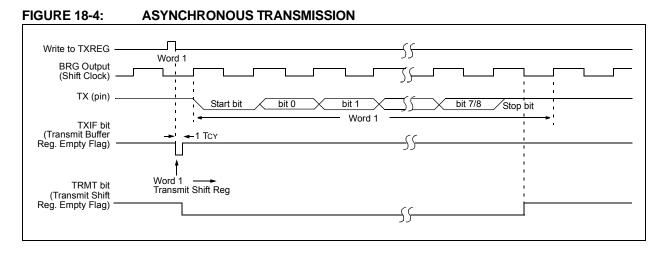

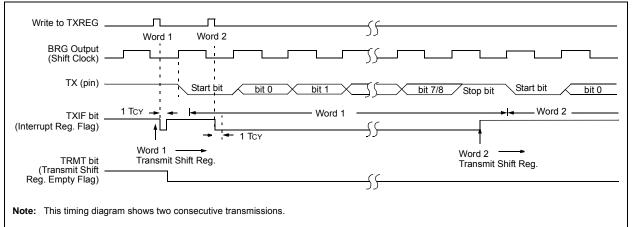

# FIGURE 18-5: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

#### TABLE 18-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name    | Bit 7                                                | Bit 6      | Bit 5       | Bit 4      | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|------------------------------------------------------|------------|-------------|------------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH                                             | PEIE/GIEL  | TMR0IE      | INT0IE     | RBIE  | TMR0IF | INT0IF | RBIF   | 49                         |

| PIR1    | PSPIF <sup>(1)</sup>                                 | ADIF       | RCIF        | TXIF       | SSPIF | CCP1IF | TMR2IF | TMR1IF | 52                         |

| PIE1    | PSPIE <sup>(1)</sup>                                 | ADIE       | RCIE        | TXIE       | SSPIE | CCP1IE | TMR2IE | TMR1IE | 52                         |

| IPR1    | PSPIP <sup>(1)</sup>                                 | ADIP       | RCIP        | TXIP       | SSPIP | CCP1IP | TMR2IP | TMR1IP | 52                         |

| RCSTA   | SPEN                                                 | RX9        | SREN        | CREN       | ADDEN | FERR   | OERR   | RX9D   | 51                         |

| TXREG   | EUSART Transmit Register                             |            |             |            |       |        |        |        | 51                         |

| TXSTA   | CSRC                                                 | TX9        | TXEN        | SYNC       | SENDB | BRGH   | TRMT   | TX9D   | 51                         |

| BAUDCON | ABDOVF                                               | RCIDL      | RXDTP       | TXCKP      | BRG16 | —      | WUE    | ABDEN  | 51                         |

| SPBRGH  | SPBRGH EUSART Baud Rate Generator Register High Byte |            |             |            |       |        |        |        | 51                         |

| SPBRG   | EUSART B                                             | aud Rate G | enerator Re | gister Low | Byte  |        |        |        | 51                         |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

**Note 1:** Reserved in 28-pin devices; always maintain these bits clear.

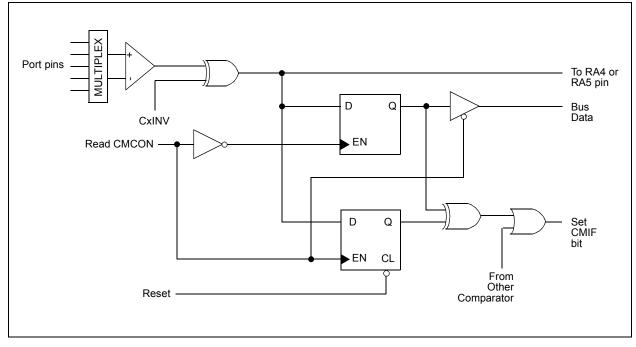

#### FIGURE 20-3: COMPARATOR OUTPUT BLOCK DIAGRAM

#### 20.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that occurred. The CMIF bit (PIR2<6>) is the Comparator Interrupt Flag. The CMIF bit must be reset by clearing it. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

Both the CMIE bit (PIE2<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit (INTCON<7>) must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | If a change in the CMCON register          |

|-------|--------------------------------------------|

|       | (C1OUT or C2OUT) should occur when a       |

|       | read operation is being executed (start of |

|       | the Q2 cycle), then the CMIF (PIR2<6>)     |

|       | interrupt flag may not get set.            |

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON will end the mismatch condition.

- b) Clear flag bit, CMIF.

A mismatch condition will continue to set flag bit, CMIF. Reading CMCON will end the mismatch condition and allow flag bit, CMIF, to be cleared.

# 20.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from Sleep mode when enabled. Each operational comparator will consume additional current, as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators (CM<2:0> = 111) before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

#### 20.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator modules to be turned off (CM<2:0> = 111). However, the input pins (RA0 through RA3) are configured as analog inputs by default on device Reset. The I/O configuration for these pins is determined by the setting of the PCFG<3:0> bits (ADCON1<3:0>). Therefore, device current is minimized when analog inputs are present at Reset time.

# 24.0 INSTRUCTION SET SUMMARY

PIC18F2420/2520/4420/4520 devices incorporate the standard set of 75 PIC18 core instructions, as well as an extended set of 8 new instructions, for the optimization of code that is recursive or that utilizes a software stack. The extended set is discussed later in this section.

### 24.1 Standard Instruction Set

The standard PIC18 instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from these PIC MCU instruction sets. Most instructions are a single program memory word (16 bits), but there are four instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- · Byte-oriented operations

- **Bit-oriented** operations

- · Literal operations

- Control operations

The PIC18 instruction set summary in Table 24-2 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 24-1 shows the opcode field descriptions.

Most byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator 'f' specifies which file register is to be used by the instruction. The destination designator 'd' specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All bit-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator 'b' selects the number of the bit affected by the operation, while the file register designator 'f' represents the number of the file in which the bit is located. The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the CALL or RETURN instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for four double-word instructions. These instructions were made double-word to contain the required information in 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 24-1 shows the general formats that the instructions can have. All examples use the convention 'nnh' to represent a hexadecimal number.

The Instruction Set Summary, shown in Table 24-2, lists the standard instructions recognized by the Microchip Assembler (MPASM<sup>TM</sup>).

Section 24.1.1 "Standard Instruction Set" provides a description of each instruction.

| POP                               | Рор Тор                                                                | of Return St                                                                                                                                                                                                                                                                               | ack             |  |  |  |  |  |

|-----------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| Syntax:                           | POP                                                                    |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |  |

| Operands:                         | None                                                                   |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |  |

| Operation:                        | $(TOS) \to b$                                                          | it bucket                                                                                                                                                                                                                                                                                  |                 |  |  |  |  |  |

| Status Affected:                  | None                                                                   | None                                                                                                                                                                                                                                                                                       |                 |  |  |  |  |  |

| Encoding:                         | 0000                                                                   | 0000 00                                                                                                                                                                                                                                                                                    | 00 0110         |  |  |  |  |  |

| Description:                      | stack and is<br>then becon<br>was pushe<br>This instruc<br>the user to | The TOS value is pulled off the return<br>stack and is discarded. The TOS value<br>then becomes the previous value that<br>was pushed onto the return stack.<br>This instruction is provided to enable<br>the user to properly manage the return<br>stack to incorporate a software stack. |                 |  |  |  |  |  |

| Words:                            | 1                                                                      |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |  |

| Cycles:                           | 1                                                                      |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |  |

| Q Cycle Activity:                 |                                                                        |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |  |

| Q1                                | Q2                                                                     | Q3                                                                                                                                                                                                                                                                                         | Q4              |  |  |  |  |  |

| Decode                            | No<br>operation                                                        | POP TOS<br>value                                                                                                                                                                                                                                                                           | No<br>operation |  |  |  |  |  |

| Example:                          | POP<br>GOTO                                                            | NEW                                                                                                                                                                                                                                                                                        |                 |  |  |  |  |  |

| Before Instruc<br>TOS<br>Stack (1 | tion<br>level down)                                                    | = 0031A<br>= 01433                                                                                                                                                                                                                                                                         |                 |  |  |  |  |  |

| After Instructio<br>TOS<br>PC     | on                                                                     | = 01433<br>= NEW                                                                                                                                                                                                                                                                           | 2h              |  |  |  |  |  |

| PUS                            | н                                          | Push Top                                                                                  | Push Top of Return Stack           |                                                |                               |                                     |  |  |  |

|--------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------------|-------------------------------|-------------------------------------|--|--|--|

| Synta                          | ax:                                        | PUSH                                                                                      | PUSH                               |                                                |                               |                                     |  |  |  |

| Oper                           | ands:                                      | None                                                                                      |                                    |                                                |                               |                                     |  |  |  |

| Oper                           | ation:                                     | (PC + 2) $\rightarrow$                                                                    | TOS                                |                                                |                               |                                     |  |  |  |

| Statu                          | is Affected:                               | None                                                                                      |                                    |                                                |                               |                                     |  |  |  |

| Enco                           | oding:                                     | 0000                                                                                      | 0000                               | 000                                            | 0                             | 0101                                |  |  |  |

| Desc                           | ription:                                   | The PC + 2<br>the return s<br>value is pus<br>This instruc<br>software sta<br>then pushin | tack.<br>hed d<br>tion a<br>ack by | The prev<br>lown on t<br>llows imp<br>modifyir | ious<br>the s<br>blem<br>ng T | TOS<br>stack.<br>enting a<br>OS and |  |  |  |

| Word                           | ls:                                        | 1                                                                                         | 1                                  |                                                |                               |                                     |  |  |  |

| Cycle                          | es:                                        | 1                                                                                         |                                    |                                                |                               |                                     |  |  |  |

| QC                             | ycle Activity:                             |                                                                                           |                                    |                                                |                               |                                     |  |  |  |

|                                | Q1                                         | Q2                                                                                        |                                    | Q3                                             |                               | Q4                                  |  |  |  |

|                                | Decode                                     | PUSH<br>PC + 2 onto<br>return stack                                                       | No<br>operation                    |                                                | oţ                            | No<br>peration                      |  |  |  |

| <u>Exan</u>                    | nple:                                      | PUSH                                                                                      |                                    |                                                |                               |                                     |  |  |  |

| Before Instructio<br>TOS<br>PC |                                            | tion                                                                                      | =<br>=                             | 345Ah<br>0124h                                 |                               |                                     |  |  |  |

|                                | After Instruction<br>PC<br>TOS<br>Stack (1 | on<br>level down)                                                                         | =<br>=                             | 0126h<br>0126h<br>345Ah                        |                               |                                     |  |  |  |

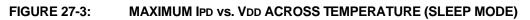

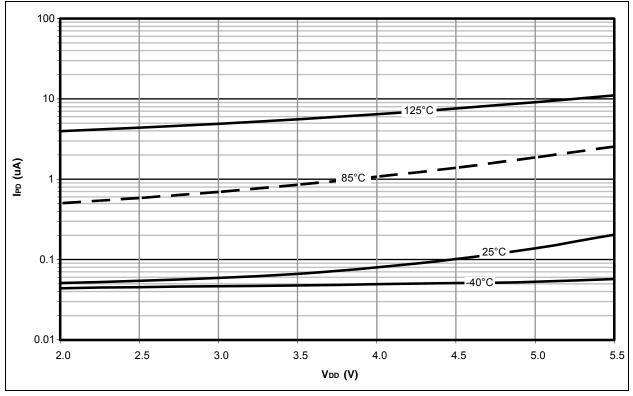

# 26.2 DC Characteristics: Power-Down and Supply Current PIC18F2420/2520/4420/4520 (Industrial) PIC18LF2420/2520/4420/4520 (Industrial) (Continued)

| PIC18LF2<br>(Indust | <b>420/2520/4420/4520</b><br>:rial)                              | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial                                                      |     |       |                 |            |                        |  |  |  |

|---------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----------------|------------|------------------------|--|--|--|

|                     | 20/2520/4420/4520<br>rrial, Extended)                            | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |     |       |                 |            |                        |  |  |  |

| Param<br>No.        | Device                                                           | Тур                                                                                                                                                                                     | Max | Units | Conditions      |            |                        |  |  |  |

|                     | Module Differential Currents (AlwDT, AlBOR, AlLVD, AlOSCB, AlAD) |                                                                                                                                                                                         |     |       |                 |            |                        |  |  |  |

| D026                | A/D Converter                                                    | 0.2                                                                                                                                                                                     | 1.0 | μA    | -40°C to +85°C  | VDD = 2.0V |                        |  |  |  |

| ( $\Delta$ IAD)     |                                                                  | 0.2                                                                                                                                                                                     | 1.0 | μA    | -40°C to +85°C  | VDD = 3.0V |                        |  |  |  |

|                     |                                                                  | 0.2                                                                                                                                                                                     | 1.0 | μA    | -40°C to +85°C  |            | A/D on, not converting |  |  |  |

|                     |                                                                  | 0.5                                                                                                                                                                                     | 4.0 | μA    | -40°C to +125°C | VDD = 5.0V |                        |  |  |  |

| D022                | Watchdog Timer                                                   | 1.3                                                                                                                                                                                     | 2.2 | μΑ    | -40°C           |            |                        |  |  |  |

| (∆IWDT)             |                                                                  | 1.4                                                                                                                                                                                     | 2.2 | μΑ    | +25°C           | VDD = 2.0V |                        |  |  |  |

|                     |                                                                  | 1.6                                                                                                                                                                                     | 2.3 | μA    | +85°C           |            |                        |  |  |  |

|                     |                                                                  | 1.9                                                                                                                                                                                     | 3.5 | μA    | -40°C           | VDD = 3.0V |                        |  |  |  |

|                     |                                                                  | 2.0                                                                                                                                                                                     | 3.5 | μA    | +25°C           |            |                        |  |  |  |

|                     |                                                                  | 2.2                                                                                                                                                                                     | 3.5 | μA    | +85°C           |            |                        |  |  |  |

|                     |                                                                  | 3.0                                                                                                                                                                                     | 7.5 | μA    | -40°C           |            |                        |  |  |  |

|                     |                                                                  | 3.5                                                                                                                                                                                     | 7.5 | μA    | +25°C           |            |                        |  |  |  |

|                     |                                                                  | 3.5                                                                                                                                                                                     | 7.8 | μA    | +85°C           | VDD = 5.0V |                        |  |  |  |

|                     |                                                                  | 4.0                                                                                                                                                                                     | 10  | μA    | +125°C          |            |                        |  |  |  |

| D022A               | Brown-out Reset <sup>(4)</sup>                                   | 35                                                                                                                                                                                      | 50  | μA    | -40°C to +85°C  | VDD = 3.0V |                        |  |  |  |

| ( $\Delta$ Ibor)    |                                                                  | 40                                                                                                                                                                                      | 55  | μA    | -40°C to +85°C  |            |                        |  |  |  |

|                     |                                                                  | 55                                                                                                                                                                                      | 65  | μA    | -40°C to +125°C |            |                        |  |  |  |

|                     |                                                                  | 0                                                                                                                                                                                       | 2   | μΑ    | -40°C to +85°C  | VDD = 5.0V | Sleep mode,            |  |  |  |

|                     |                                                                  | 0                                                                                                                                                                                       | 5   | μΑ    | -40°C to +125°C |            | BOREN<1:0> = 10        |  |  |  |

| D022B               | High/Low-Voltage                                                 | 22                                                                                                                                                                                      | 38  | μΑ    | -40°C to +85°C  | VDD = 2.0V |                        |  |  |  |

| (∆ILVD)             | Detect <sup>(4)</sup>                                            | 25                                                                                                                                                                                      | 40  | μΑ    | -40°C to +85°C  | VDD = 3.0V |                        |  |  |  |

|                     |                                                                  | 29                                                                                                                                                                                      | 45  | μΑ    | -40°C to +85°C  | VDD = 5.0V |                        |  |  |  |

|                     |                                                                  | 30                                                                                                                                                                                      | 45  | μA    | -40°C to +125°C | VUU = 5.0V |                        |  |  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSs and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD or Vss;

MCLR = VDD; WDT enabled/disabled as specified.

- **3:** When operation below -10°C is expected, use T1OSC High-Power mode, where LPT1OSC (CONFIG3H<2>) = 0. When operation will always be above -10°C, then the low-power Timer1 oscillator may be selected.

- 4: BOR and HLVD enable internal band gap reference. With both modules enabled, current consumption will be less than the sum of both specifications.

# 26.4 AC (Timing) Characteristics

#### 26.4.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created using one of the following formats:

| 1. TppS2ppS                | 5                               | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|----------------------------|---------------------------------|-----------|----------------------------------------|

| 2. TppS                    |                                 | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                          |                                 |           |                                        |

| F                          | Frequency                       | Т         | Time                                   |

| Lowercase le               | etters (pp) and their meanings: |           |                                        |

| рр                         |                                 |           |                                        |

| сс                         | CCP1                            | osc       | OSC1                                   |

| ck                         | CLKO                            | rd        | RD                                     |

| cs                         | CS                              | rw        | RD or WR                               |

| di                         | SDI                             | sc        | SCK                                    |

| do                         | SDO                             | ss        | SS                                     |

| dt                         | Data in                         | tO        | TOCKI                                  |

| io                         | I/O port                        | t1        | T13CKI                                 |

| mc                         | MCLR                            | wr        | WR                                     |

| Uppercase le               | etters and their meanings:      |           |                                        |

| S                          |                                 |           |                                        |

| F                          | Fall                            | Р         | Period                                 |

| н                          | High                            | R         | Rise                                   |

| I                          | Invalid (High-impedance)        | V         | Valid                                  |

| L                          | Low                             | Z         | High-impedance                         |

| I <sup>2</sup> C only      |                                 |           |                                        |

| AA                         | output access                   | High      | High                                   |

| BUF                        | Bus free                        | Low       | Low                                    |

| TCC:ST (I <sup>2</sup> C s | specifications only)            |           |                                        |

| CC                         |                                 |           |                                        |

| HD                         | Hold                            | SU        | Setup                                  |

| ST                         |                                 |           |                                        |

| DAT                        | DATA input hold                 | STO       | Stop condition                         |

| STA                        | Start condition                 |           |                                        |

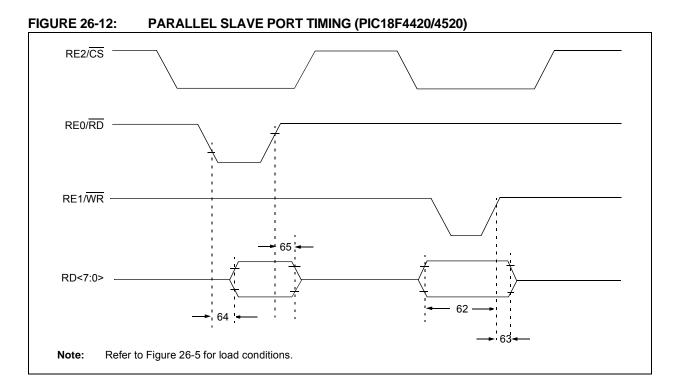

| Param.<br>No. | Symbol   | Characteristic                                                                                                    |                      |    | Max   | Units | Conditions |

|---------------|----------|-------------------------------------------------------------------------------------------------------------------|----------------------|----|-------|-------|------------|

| 62            | TdtV2wrH | Data In Valid before $\overline{WR} \uparrow or \overline{CS} \uparrow (setup time)$                              |                      | 20 |       | ns    |            |

| 63            | TwrH2dtI | $\overline{WR} \uparrow or \overline{CS} \uparrow to Data-In$                                                     | PIC18FXXXX           | 20 | _     | ns    |            |

|               |          | Invalid (hold time)                                                                                               | PIC18 <b>LF</b> XXXX | 35 | _     | ns    | VDD = 2.0V |

| 64            | TrdL2dtV | $\overline{RD}\downarrow$ and $\overline{CS}\downarrow$ to Data–Out Val                                           | id                   | _  | 80    | ns    |            |

| 65            | TrdH2dtl | $\overline{RD}$ $\uparrow$ or $\overline{CS}$ $\downarrow$ to Data–Out Invalid                                    |                      | 10 | 30    | ns    |            |

| 66            | TibfINH  | Inhibit of the IBF Flag bit being Cleared from $\overline{\rm WR} \uparrow {\rm or} \ \overline{\rm CS} \uparrow$ |                      |    | 3 Tcy |       |            |

#### TABLE 26-14: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 0)

| Param<br>No. | Symbol                | Characterist                                                           | Min                                   | Max | Units | Conditions |            |

|--------------|-----------------------|------------------------------------------------------------------------|---------------------------------------|-----|-------|------------|------------|

| 70           | TssL2scH,<br>TssL2scL | $\overline{SS} \downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ Input | Тсү                                   | —   | ns    |            |            |