Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                              |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 768 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 13x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4420-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 5.0 MEMORY ORGANIZATION

There are three types of memory in PIC18 enhanced microcontroller devices:

- Program Memory

- Data RAM

- Data EEPROM

As Harvard architecture devices, the data and program memories use separate busses; this allows for concurrent access of the two memory spaces. The data EEPROM, for practical purposes, can be regarded as a peripheral device, since it is addressed and accessed through a set of control registers.

Additional detailed information on the operation of the Flash program memory is provided in **Section 6.0 "Flash Program Memory"**. Data EEPROM is discussed separately in **Section 7.0 "Data EEPROM Memory"**.

## 5.1 Program Memory Organization

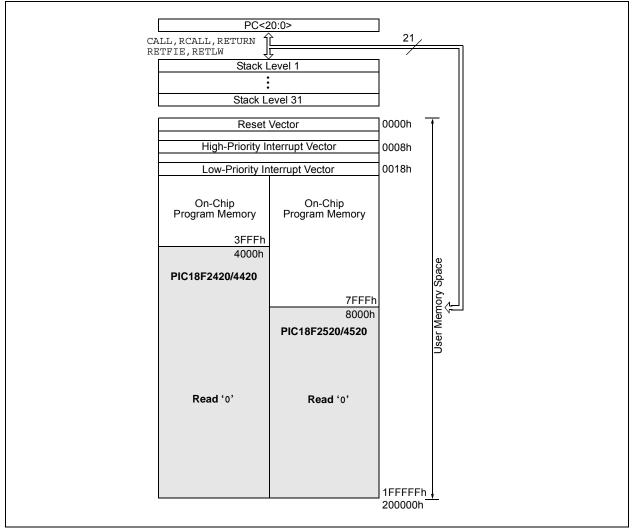

PIC18 microcontrollers implement a 21-bit program counter, which is capable of addressing a 2-Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address will return all '0's (a NOP instruction).

The PIC18F2420 and PIC18F4420 each have 16 Kbytes of Flash memory and can store up to 8,192 single-word instructions. The PIC18F2520 and PIC18F4520 each have 32 Kbytes of Flash memory and can store up to 16,384 single-word instructions.

PIC18 devices have two interrupt vectors. The Reset vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

The program memory map for PIC18F2420/2520/ 4420/4520 devices is shown in Figure 5-1.

#### FIGURE 5-1: PROGRAM MEMORY MAP AND STACK FOR PIC18F2420/2520/4420/4520 DEVICES

# PIC18F2420/2520/4420/4520

The PLUSW register can be used to implement a form of Indexed Addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

#### 5.4.3.3 Operations by FSRs on FSRs

Indirect Addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contains FE7h, the address of INDF1. Attempts to read the value of the INDF1 using INDF0 as an operand will return 00h. Attempts to write to INDF1 using INDF0 as the operand will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to INDF2 or POSTDEC2 will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses indirect addressing.

Similarly, operations by Indirect Addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

# 5.5 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different; this is due to the introduction of a new addressing mode for the data memory space.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect Addressing with FSR0 and FSR1 also remains unchanged.

## 5.5.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of Indirect Addressing using the FSR2 register pair within Access RAM. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of Indexed Addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset, or Indexed Literal Offset mode.

When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0) and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in direct addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer, specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

## 5.5.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use Direct Addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they do not use the Access Bank (Access RAM bit is '1'), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled in shown in Figure 5-9.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 24.2.1** "Extended Instruction Syntax".

## 9.0 INTERRUPTS

The PIC18F2420/2520/4420/4520 devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 0008h and the low-priority interrupt vector is at 0018h. High-priority interrupts will interrupt any low-priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2

- PIE1, PIE2

- IPR1. IPR2

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- **Priority bit** to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a lowpriority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

Note: Do not use the MOVFF instruction to modify any of the interrupt control registers while any interrupt is enabled. Doing so may cause erratic microcontroller behavior.

| Pin            | Function            | TRIS<br>Setting | I/O | l/O<br>Type          | Description                                                                                                                                     |

|----------------|---------------------|-----------------|-----|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/     | RC0                 | 0               | 0   | DIG                  | LATC<0> data output.                                                                                                                            |

| T13CKI         |                     | 1               | Ι   | ST                   | PORTC<0> data input.                                                                                                                            |

|                | T10S0               | x               | 0   | ANA                  | Timer1 oscillator output; enabled when Timer1 oscillator enabled.<br>Disables digital I/O.                                                      |

|                | T13CKI              | 1               | Ι   | ST                   | Timer1/Timer3 counter input.                                                                                                                    |

| RC1/T1OSI/CCP2 | RC1                 | 0               | 0   | DIG                  | LATC<1> data output.                                                                                                                            |

|                |                     | 1               | Ι   | ST                   | PORTC<1> data input.                                                                                                                            |

|                | T1OSI               | x               | I   | ANA                  | Timer1 oscillator input; enabled when Timer1 oscillator enabled.<br>Disables digital I/O.                                                       |

|                | CCP2 <sup>(1)</sup> | 0               | 0   | DIG                  | CCP2 compare and PWM output; takes priority over port data.                                                                                     |

|                |                     | 1               | Ι   | ST                   | CCP2 capture input.                                                                                                                             |

| RC2/CCP1/P1A   | RC2                 | 0               | 0   | DIG                  | LATC<2> data output.                                                                                                                            |

|                |                     | 1               | Ι   | ST                   | PORTC<2> data input.                                                                                                                            |

|                | CCP1                | 0               | 0   | DIG                  | ECCP1 compare or PWM output; takes priority over port data.                                                                                     |

|                |                     | 1               | Ι   | ST                   | ECCP1 capture input.                                                                                                                            |

|                | P1A <sup>(2)</sup>  | 0               | 0   | DIG                  | ECCP1 Enhanced PWM output, channel A. May be configured for<br>tri-state during Enhanced PWM shutdown events. Takes priority over<br>port data. |

| RC3/SCK/SCL    | RC3                 | 0               | 0   | DIG                  | LATC<3> data output.                                                                                                                            |

|                |                     | 1               | Ι   | ST                   | PORTC<3> data input.                                                                                                                            |

|                | SCK                 | 0               | 0   | DIG                  | SPI clock output (MSSP module); takes priority over port data.                                                                                  |

| -              |                     | 1               | Ι   | ST                   | SPI clock input (MSSP module).                                                                                                                  |

|                | SCL                 | 0               | 0   | DIG                  | I <sup>2</sup> C <sup>™</sup> clock output (MSSP module); takes priority over port data.                                                        |

|                |                     | 1               | Ι   | I <sup>2</sup> C/SMB | I <sup>2</sup> C clock input (MSSP module); input type depends on module setting                                                                |

| RC4/SDI/SDA    | RC4                 | 0               | 0   | DIG                  | LATC<4> data output.                                                                                                                            |

|                |                     | 1               | Ι   | ST                   | PORTC<4> data input.                                                                                                                            |

|                | SDI                 | 1               | I   | ST                   | SPI data input (MSSP module).                                                                                                                   |

|                | SDA                 | 1               | 0   | DIG                  | I <sup>2</sup> C data output (MSSP module); takes priority over port data.                                                                      |

|                |                     | 1               | I   | I <sup>2</sup> C/SMB | I <sup>2</sup> C data input (MSSP module); input type depends on module setting.                                                                |

| RC5/SDO        | RC5                 | 0               | 0   | DIG                  | LATC<5> data output.                                                                                                                            |

|                |                     | 1               | Ι   | ST                   | PORTC<5> data input.                                                                                                                            |

|                | SDO                 | 0               | 0   | DIG                  | SPI data output (MSSP module); takes priority over port data.                                                                                   |

| RC6/TX/CK      | RC6                 | 0               | 0   | DIG                  | LATC<6> data output.                                                                                                                            |

|                |                     | 1               | I   | ST                   | PORTC<6> data input.                                                                                                                            |

|                | ТХ                  | 1               | 0   | DIG                  | Asynchronous serial transmit data output (EUSART module);<br>takes priority over port data. User must configure as output.                      |

|                | СК                  | 1               | 0   | DIG                  | Synchronous serial clock output (EUSART module); takes priority over port data.                                                                 |

|                |                     | 1               | I   | ST                   | Synchronous serial clock input (EUSART module).                                                                                                 |

| RC7/RX/DT      | RC7                 | 0               | 0   | DIG                  | LATC<7> data output.                                                                                                                            |

|                |                     | 1               | 1   | ST                   | PORTC<7> data input.                                                                                                                            |

|                | RX                  | 1               | I   | ST                   | Asynchronous serial receive data input (EUSART module).                                                                                         |

|                | DT                  | 1               | 0   | DIG                  | Synchronous serial data output (EUSART module); takes priority over port data.                                                                  |

|                |                     | 1               | Ι   | ST                   | Synchronous serial data input (EUSART module). User must configure as an input.                                                                 |

### TABLE 10-5: PORTC I/O SUMMARY

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output;  $I^2C/SMB = I^2C/SMB$  us input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Default assignment for CCP2 when the CCP2MX Configuration bit is set. Alternate assignment is RB3.

2: Enhanced PWM output is available only on PIC18F4520 devices.

## 11.0 TIMER0 MODULE

The Timer0 module incorporates the following features:

- Software selectable operation as a timer or counter in both 8-bit or 16-bit modes

- · Readable and writable registers

- Dedicated 8-bit, software programmable

prescaler

- Selectable clock source (internal or external)

- Edge select for external clock

- · Interrupt-on-overflow

The T0CON register (Register 11-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

A simplified block diagram of the Timer0 module in 8-bit mode is shown in Figure 11-1. Figure 11-2 shows a simplified block diagram of the Timer0 module in 16-bit mode.

#### REGISTER 11-1: TOCON: TIMERO CONTROL REGISTER

| R/W-1       | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------------|--------|-------|-------|-------|-------|-------|-------|

| TMR00N      | T08BIT | TOCS  | TOSE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7 bit 0 |        |       |       |       |       |       |       |

| Legend:    |                            |                                                              |                               |                    |  |  |  |

|------------|----------------------------|--------------------------------------------------------------|-------------------------------|--------------------|--|--|--|

| R = Reada  | ble bit                    | W = Writable bit                                             | U = Unimplemented bit,        | read as '0'        |  |  |  |

| -n = Value | at POR                     | '1' = Bit is set                                             | '0' = Bit is cleared          | x = Bit is unknown |  |  |  |

|            |                            |                                                              |                               |                    |  |  |  |

| bit 7      |                            | I: Timer0 On/Off Control bit                                 |                               |                    |  |  |  |

|            |                            | les Timer0                                                   |                               |                    |  |  |  |

|            | 0 = Stops                  |                                                              |                               |                    |  |  |  |

| bit 6      | <b>T08BIT</b> : 1          | Fimer0 8-Bit/16-Bit Control bit                              | t                             |                    |  |  |  |

|            |                            | r0 is configured as an 8-bit tir                             |                               |                    |  |  |  |

|            | 0 = Timer                  | r0 is configured as a 16-bit tir                             | mer/counter                   |                    |  |  |  |

| bit 5      | TOCS: Tir                  | mer0 Clock Source Select bit                                 |                               |                    |  |  |  |

|            |                            | sition on T0CKI pin                                          |                               |                    |  |  |  |

|            | 0 = Intern                 | al instruction cycle clock (CL                               | KO)                           |                    |  |  |  |

| bit 4      | TOSE: Tir                  | mer0 Source Edge Select bit                                  |                               |                    |  |  |  |

|            | 1 = Increi                 | ment on high-to-low transitior                               | n on T0CKI pin                |                    |  |  |  |

|            | 0 = Increi                 | ment on low-to-high transitior                               | n on T0CKI pin                |                    |  |  |  |

| bit 3      | PSA: Tim                   | er0 Prescaler Assignment bi                                  | t                             |                    |  |  |  |

|            | 1 = TIme                   | r0 prescaler is not assigned.                                | Timer0 clock input bypasses p | orescaler.         |  |  |  |

|            | 0 = Timer                  | r0 prescaler is assigned. Time                               | er0 clock input comes from pr | escaler output.    |  |  |  |

| bit 2-0    | T0PS<2:                    | 0>: Timer0 Prescaler Select b                                | bits                          |                    |  |  |  |

|            | 111 = 1:256 Prescale value |                                                              |                               |                    |  |  |  |

|            |                            | 128 Prescale value                                           |                               |                    |  |  |  |

|            |                            | 64 Prescale value                                            |                               |                    |  |  |  |

|            |                            | 32 Prescale value                                            |                               |                    |  |  |  |

|            |                            | <ul><li>16 Prescale value</li><li>3 Prescale value</li></ul> |                               |                    |  |  |  |

|            |                            | Prescale value                                               |                               |                    |  |  |  |

|            | 001 = 1:2                  |                                                              |                               |                    |  |  |  |

# 12.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Reset on CCP Special Event Trigger

- Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 12-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 12-2.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 12-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

| R/W-0       | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------------|-------|---------|---------|---------|--------|--------|--------|

| RD16        | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 bit 0 |       |         |         |         |        |        |        |

#### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| Legend:       |                                                                        |                                                                |                                                              |                    |  |  |  |  |  |

|---------------|------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------|--------------------|--|--|--|--|--|

| R = Readabl   | e bit                                                                  | W = Writable bit                                               | U = Unimplemented bit,                                       | , read as '0'      |  |  |  |  |  |

| -n = Value at | POR                                                                    | '1' = Bit is set                                               | '0' = Bit is cleared                                         | x = Bit is unknown |  |  |  |  |  |

|               |                                                                        |                                                                |                                                              |                    |  |  |  |  |  |

| bit 7         |                                                                        | Bit Read/Write Mode Enable                                     |                                                              |                    |  |  |  |  |  |

|               |                                                                        | es register read/write of Thr<br>es register read/write of Tim | ner1 in one 16-bit operation<br>ner1 in two 8-bit operations |                    |  |  |  |  |  |

| bit 6         | T1RUN: Ti                                                              | mer1 System Clock Status                                       | bit                                                          |                    |  |  |  |  |  |

|               |                                                                        | e clock is derived from Time<br>e clock is derived from anot   |                                                              |                    |  |  |  |  |  |

| bit 5-4       |                                                                        | 1:0>: Timer1 Input Clock Pr                                    |                                                              |                    |  |  |  |  |  |

|               |                                                                        | rescale value                                                  |                                                              |                    |  |  |  |  |  |

|               |                                                                        | rescale value                                                  |                                                              |                    |  |  |  |  |  |

|               | 01 = 1:2 Prescale value                                                |                                                                |                                                              |                    |  |  |  |  |  |

|               | 00 = 1:1 P                                                             | 00 = 1:1 Prescale value                                        |                                                              |                    |  |  |  |  |  |

| bit 3         | T10SCEN                                                                | : Timer1 Oscillator Enable b                                   | pit                                                          |                    |  |  |  |  |  |

|               |                                                                        | oscillator is enabled                                          |                                                              |                    |  |  |  |  |  |

|               | • • • • • • •                                                          | oscillator is shut off                                         | esistor are turned off to elimina                            | to power drain     |  |  |  |  |  |

| bit 2         |                                                                        |                                                                | t Synchronization Select bit                                 |                    |  |  |  |  |  |

|               |                                                                        |                                                                | Synchronization Select bit                                   |                    |  |  |  |  |  |

|               | <u>When TMR1CS = 1:</u><br>1 = Do not synchronize external clock input |                                                                |                                                              |                    |  |  |  |  |  |

|               |                                                                        | ronize external clock input                                    |                                                              |                    |  |  |  |  |  |

|               | When TMR1CS = 0:                                                       |                                                                |                                                              |                    |  |  |  |  |  |

|               | This bit is i                                                          | gnored. Timer1 uses the inf                                    | ternal clock when TMR1CS =                                   | 0.                 |  |  |  |  |  |

| bit 1         | TMR1CS:                                                                | Timer1 Clock Source Selec                                      | t bit                                                        |                    |  |  |  |  |  |

|               |                                                                        |                                                                | SO/T13CKI (on the rising edge                                | e)                 |  |  |  |  |  |

|               |                                                                        | al clock (Fosc/4)                                              |                                                              |                    |  |  |  |  |  |

| bit 0         |                                                                        | Timer1 On bit                                                  |                                                              |                    |  |  |  |  |  |

|               | 1 = Enable                                                             |                                                                |                                                              |                    |  |  |  |  |  |

|               | 0 = Stops                                                              | limer1                                                         |                                                              |                    |  |  |  |  |  |

## 16.0 ENHANCED CAPTURE/ COMPARE/PWM (ECCP) MODULE

| Note: | The ECCP module is implemented only in |

|-------|----------------------------------------|

|       | 40/44-pin devices.                     |

In PIC18F4420/4520 devices, CCP1 is implemented as a standard CCP module with Enhanced PWM capabilities. These include the provision for 2 or 4 output channels, user-selectable polarity, dead-band control and automatic shutdown and restart. The enhanced features are discussed in detail in **Section 16.4 "Enhanced PWM Mode"**. Capture, Compare and single output PWM functions of the ECCP module are the same as described for the standard CCP module.

The control register for the Enhanced CCP module is shown in Register 16-2. It differs from the CCPxCON registers in PIC18F2420/2520 devices in that the two Most Significant bits are implemented to control PWM functionality.

## REGISTER 16-1: CCP1CON: ECCP CONTROL REGISTER (40/44-PIN DEVICES)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|--------|--------|--------|--------|

| P1M1  | P1M0  | DC1B1 | DC1B0 | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 |

| bit 7 |       |       |       |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-6 P1M<1:0>: Enhanced PWM Output Configuration bits If CCP1M3:CCP1M2 = 00, 01, 10: xx = P1A assigned as capture/compare input/output; P1B, P1C, P1D assigned as port pins If CCP1M3:CCP1M2 = 11: 00 = Single output, P1A modulated; P1B, P1C, P1D assigned as port pins 01 = Full-bridge output forward, P1D modulated; P1A active; P1B, P1C inactive 10 = Half-bridge output, P1A, P1B modulated with dead-band control; P1C, P1D assigned as port pins 11 = Full-bridge output reverse, P1B modulated; P1C active; P1A, P1D inactive DC1B<1:0>: PWM Duty Cycle bit 1 and bit 0 bit 5-4 Capture mode: Unused. Compare mode: Unused. PWM mode: These bits are the two LSbs of the 10-bit PWM duty cycle. The eight MSbs of the duty cycle are found in CCPR1L. bit 3-0 CCP1M<3:0>: Enhanced CCP Mode Select bits 0000 = Capture/Compare/PWM off (resets ECCP module) 0001 = Reserved 0010 = Compare mode, toggle output on match 0011 = Capture mode 0100 = Capture mode, every falling edge 0101 = Capture mode, every rising edge 0110 = Capture mode, every 4th rising edge 0111 = Capture mode, every 16th rising edge 1000 = Compare mode, initialize CCP1 pin low; set output on compare match (set CCP1IF) 1001 = Compare mode, initialize CCP1 pin high; clear output on compare match (set CCP1IF) 1010 = Compare mode, generate software interrupt only; CCP1 pin reverts to I/O state 1011 = Compare mode, trigger special event (ECCP resets TMR1 or TMR3, sets CCP1IF bit) 1100 = PWM mode, P1A, P1C active-high; P1B, P1D active-high 1101 = PWM mode, P1A, P1C active-high; P1B, P1D active-low 1110 = PWM mode, P1A, P1C active-low; P1B, P1D active-high 1111 = PWM mode, P1A, P1C active-low; P1B, P1D active-low

#### 16.4.7.1 Auto-Shutdown and Automatic Restart

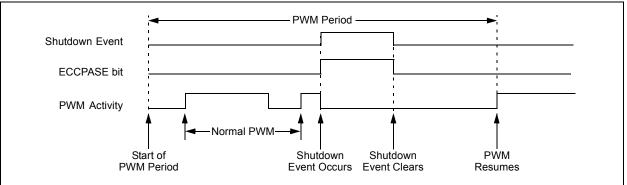

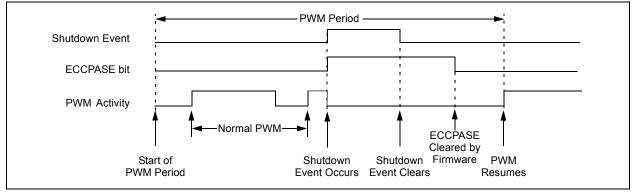

The auto-shutdown feature can be configured to allow automatic restarts of the module following a shutdown event. This is enabled by setting the PRSEN bit of the PWM1CON register (PWM1CON<7>).

In Shutdown mode with PRSEN = 1 (Figure 16-10), the ECCPASE bit will remain set for as long as the cause of the shutdown continues. When the shutdown condition clears, the ECCPASE bit is cleared. If PRSEN = 0 (Figure 16-11), once a shutdown condition occurs, the ECCPASE bit will remain set until it is cleared by firmware. Once ECCPASE is cleared, the Enhanced PWM will resume at the beginning of the next PWM period.

| Note: | Writing to the ECCPASE bit is disabled |

|-------|----------------------------------------|

|       | while a shutdown condition is active.  |

Independent of the PRSEN bit setting, if the autoshutdown source is one of the comparators, the shutdown condition is a level. The ECCPASE bit cannot be cleared as long as the cause of the shutdown persists.

The Auto-Shutdown mode can be forced by writing a '1' to the ECCPASE bit.

## 16.4.8 START-UP CONSIDERATIONS

When the ECCP module is used in the PWM mode, the application hardware must use the proper external pullup and/or pull-down resistors on the PWM output pins. When the microcontroller is released from Reset, all of the I/O pins are in the high-impedance state. The external circuits must keep the power switch devices in the OFF state until the microcontroller drives the I/O pins with the proper signal levels or activates the PWM output(s).

The CCP1M<1:0> bits (CCP1CON<1:0>) allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (P1A/P1C and P1B/P1D). The PWM output polarities must be selected before the PWM pins are configured as outputs. Changing the polarity configuration while the PWM pins are configured as outputs is not recommended, since it may result in damage to the application circuits.

The P1A, P1B, P1C and P1D output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pins for output at the same time as the ECCP module may cause damage to the application circuit. The ECCP module must be enabled in the proper output mode and complete a full PWM cycle before configuring the PWM pins as outputs. The completion of a full PWM cycle is indicated by the TMR2IF bit being set as the second PWM period begins.

#### FIGURE 16-10: PWM AUTO-SHUTDOWN (PRSEN = 1, AUTO-RESTART ENABLED)

#### FIGURE 16-11: PWM AUTO-SHUTDOWN (PRSEN = 0, AUTO-RESTART DISABLED)

## 17.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON1<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- · Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

EVAMDI E 17-1.

· Slave Select mode (Slave mode only)

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full detect bit, BF (SSPSTAT<0>) and the interrupt flag bit, SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data

will be ignored and the write collision detect bit, WCOL (SSPCON1<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. The Buffer Full bit, BF (SSPSTAT<0>), indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 17-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP Status register (SSPSTAT) indicates the various status conditions.

Note: The SSPBUF register cannot be used with read-modify-write instructions such as BCF, BTFSC and COMF, etc.

|      |                      | . LOADING                        |                                                                                       |  |

|------|----------------------|----------------------------------|---------------------------------------------------------------------------------------|--|

| LOOP | BTFSS<br>BRA<br>MOVF | SSPSTAT, BF<br>LOOP<br>SSPBUF, W | ;Has data been received (transmit complete)?<br>;No<br>;WREG reg = contents of SSPBUF |  |

|      | MOVWF                | RXDATA                           | ;Save in user RAM, if data is meaningful                                              |  |

|      | MOVF<br>MOVWF        | TXDATA, W<br>SSPBUF              | ;W reg = contents of TXDATA<br>;New data to xmit                                      |  |

I OADING THE SODDIE (SODO) DECISTED

| Note: |     | To avoid lost data in Master mode, a read<br>of the SSPBUF must be performed to clear |      |        |        |      |  |  |

|-------|-----|---------------------------------------------------------------------------------------|------|--------|--------|------|--|--|

|       | the | Buffer                                                                                | Full | (BF)   | detect | bit  |  |  |

|       | ``  | PSTAT<0>                                                                              | >)   | betwee | en     | each |  |  |

#### 17.4.3.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit, BF (SSPSTAT<0>), is set, or bit, SSPOV (SSPCON1<6>), is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit, SSPIF (PIR1<3>), must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPCON2<0> = 1), RC3/SCK/SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting bit, CKP (SSPCON<4>). See **Section 17.4.4** "**Clock Stretching**" for more details.

#### 17.4.3.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and the RC3/SCK/SCL pin is held low regardless of SEN (see Section 17.4.4 "Clock Stretching" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then the RC3/SCK/SCL pin should be enabled by setting bit, CKP (SSPCON1<4>). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 17-9).

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not ACK), then the data transfer is complete. In this case, when the ACK is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave monitors for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, the RC3/SCK/SCL pin must be enabled by setting bit, CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

## 17.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the  $R/\overline{W}$  bit. In this case, the  $R/\overline{W}$  bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

The Baud Rate Generator used for the SPI mode operation is used to set the SCL clock frequency for either 100 kHz, 400 kHz or 1 MHz I<sup>2</sup>C operation. See **Section 17.4.7 "Baud Rate"** for more detail.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start Enable bit, SEN (SSPCON2<0>).

- 2. SSPIF is set. The MSSP module will wait the required start time before any other operation takes place.

- 3. The user loads the SSPBUF with the slave address to transmit.

- 4. Address is shifted out the SDA pin until all 8 bits are transmitted.

- 5. The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 6. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 7. The user loads the SSPBUF with eight bits of data.

- 8. Data is shifted out the SDA pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 11. The user generates a Stop condition by setting the Stop Enable bit, PEN (SSPCON2<2>).

- 12. Interrupt is generated once the Stop condition is complete.

## 18.3 EUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTA<4>). In addition, enable bit, SPEN (RCSTA<7>), is set in order to configure the TX and RX pins to CK (clock) and DT (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK line. Clock polarity is selected with the TXCKP bit (BAUDCON<4>); setting TXCKP sets the Idle state on CK as high, while clearing the bit sets the Idle state as low. This option is provided to support Microwire devices with this module.

#### 18.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 18-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available).

Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG is empty and the TXIF flag bit (PIR1<4>) is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF is set regardless of the state of enable bit, TXIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREG register.

While flag bit, TXIF, indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

|                            | Q1Q2Q      | 3Q4 Q1 Q2   | Q3Q4Q1Q2  | Q3Q4 Q1Q2  | Q3Q4Q1C     | 2Q3Q4        | Q3Q4        | Q1Q2Q3Q | 4 Q1 Q2 Q | 3Q4 Q1 Q2                | Q3Q4 C      | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q    | 4Q1Q2Q      | 3 Q4        |

|----------------------------|------------|-------------|-----------|------------|-------------|--------------|-------------|---------|-----------|--------------------------|-------------|-------------|---------------|-------------|-------------|

| RC7/RX/DT                  |            |             | bit 0     | bit 1      | <u>bit</u>  | 2 ~          |             | bit 7   | bit 0     | X <u>bit 1</u><br>Word 2 | ׇ           |             |               | bit 7       |             |

| RC6/TX/CK (<br>(TXCKP = 0) | ; <u> </u> | 1<br>1<br>1 |           |            |             |              | ;           |         |           |                          | <br>!       |             | <br>          |             | ;           |

| RC6/TX/CK<br>(TXCKP = 1)   |            |             | ٦Ļ́ſ      |            |             | <u></u>      |             |         | ÷         | ŀ                        | <u>۔</u>    |             |               | ÷           |             |

| Write to<br>TXREG Reg      |            | Write W     | ord 1     | Write Wor  | d 2         |              | ו<br>י<br>י |         |           | <br> <br> <br>           | 1<br>       |             | <u></u>       | 1<br>1<br>1 | '           |

| TXIF bit<br>(Interrupt Fla | g)         | <br>        | <u>∼¦</u> | <u>;</u>   |             |              | 1<br>1<br>1 |         |           |                          |             |             | <u>}</u>      | -<br>-<br>- | ;<br>;      |

| TRMT bit                   |            | <u> </u>    |           |            | 1<br>1<br>1 |              |             |         | <u>.</u>  | 1<br>1<br>1<br>1         | 1<br>1<br>1 |             | <del>}}</del> | ÷           | 1<br>1<br>1 |

| TXEN bit                   | <u>'1'</u> | 1<br>1      | 1<br>1    | 1<br>      | 1<br>1      |              |             |         |           | <br>                     | 1<br>       |             | <u>}</u>      | <u>.</u>    | <u>'1'</u>  |

| Note: Syn                  | c Maste    | r mode, S   | PBRG = 0, | continuous | s transmis  | ssion of two | 8-bit w     | ords.   |           |                          |             |             |               |             |             |

FIGURE 18-11: SYNCHRONOUS TRANSMISSION

## 20.2 Comparator Operation

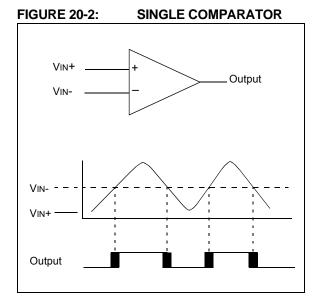

A single comparator is shown in Figure 20-2, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 20-2 represent the uncertainty, due to input offsets and response time.

### 20.3 Comparator Reference

Depending on the comparator operating mode, either an external or internal voltage reference may be used. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly (Figure 20-2).

#### 20.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSS and VDD and can be applied to either pin of the comparator(s).

#### 20.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference from the comparator voltage reference module. This module is described in more detail in **Section 21.0 "Comparator Voltage Reference Module"**.

The internal reference is only available in the mode where four inputs are multiplexed to two comparators (CM<2:0> = 110). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

## 20.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (see Section 26.0 "Electrical Characteristics").

## 20.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read-only. The comparator outputs may also be directly output to the RA4 and RA5 I/O pins. When enabled, multiplexers in the output path of the RA4 and RA5 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 20-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA4 and RA5 pins while in this mode.

The polarity of the comparator outputs can be changed using the C2INV and C1INV bits (CMCON<4:5>).

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin defined as a digital input may cause the input buffer to consume more current than is specified.

## 21.0 COMPARATOR VOLTAGE REFERENCE MODULE

The comparator voltage reference is a 16-tap resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it may also be used independently of them.

A block diagram of the module is shown in Figure 21-1. The resistor ladder is segmented to provide two ranges of CVREF values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference.

### 21.1 Configuring the Comparator Voltage Reference

The voltage reference module is controlled through the CVRCON register (Register 21-1). The comparator voltage reference provides two ranges of output voltage, each with 16 distinct levels. The range to be used

is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF Selection bits (CVR<3:0>), with one range offering finer resolution. The equations used to calculate the output of the comparator voltage reference are as follows:

If CVRR = 1:

CVREF = ((CVR<3:0>)/24) x CVRSRC

<u>If CVRR = 0:</u>

CVREF = (CVRSRC x 1/4) + (((CVR<3:0>)/32) x CVRSRC)

The comparator reference supply voltage can come from either VDD and Vss, or the external VREF+ and VREF- that are multiplexed with RA2 and RA3. The voltage source is selected by the CVRSS bit (CVRCON<4>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output (see Table 26-3 in **Section 26.0 "Electrical Characteristics"**).

#### REGISTER 21-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0        | R/W-0                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                   | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------|------------------|-----------------|-------|--|--|--|

| CVREN        | CVROE <sup>(1)</sup>                                                                                                                                                                                                                                                                            | CVRR                                                                                                                                                                                                                                    | CVRSS | CVR3              | CVR2             | CVR1            | CVR0  |  |  |  |

| bit 7        |                                                                                                                                                                                                                                                                                                 | ·                                                                                                                                                                                                                                       |       |                   |                  | •               | bit C |  |  |  |

| 1            |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                         |       |                   |                  |                 |       |  |  |  |

| Legend:      |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                         |       |                   |                  |                 |       |  |  |  |

| R = Readab   | le bit                                                                                                                                                                                                                                                                                          | W = Writable                                                                                                                                                                                                                            | bit   | U = Unimplem      | nented bit, read | l as '0'        |       |  |  |  |

| -n = Value a | t POR                                                                                                                                                                                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                                        |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |  |  |  |

| bit 6        | 0 = CVREF ci<br>CVROE: Com<br>1 = CVREF vo                                                                                                                                                                                                                                                      | <ul> <li>1 = CVREF circuit powered on</li> <li>0 = CVREF circuit powered down</li> <li>CVROE: Comparator VREF Output Enable bit<sup>(1)</sup></li> <li>1 = CVREF voltage level is also output on the RA2/AN2/VREF-/CVREF pin</li> </ul> |       |                   |                  |                 |       |  |  |  |

| bit 5        | <ul> <li>0 = CVREF voltage is disconnected from the RA2/AN2/VREF-/CVREF pin</li> <li>5 CVRR: Comparator VREF Range Selection bit</li> <li>1 = 0 to 0.667 CVRsRc, with CVRsRc/24 step size (low range)</li> <li>0 = 0.25 CVRsRc to 0.75 CVRsRc, with CVRsRc/32 step size (high range)</li> </ul> |                                                                                                                                                                                                                                         |       |                   |                  |                 |       |  |  |  |

| bit 4        |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                         |       |                   |                  |                 |       |  |  |  |

| bit 3-0      | •                                                                                                                                                                                                                                                                                               | <b>CVR3:CVR0:</b> Comparator VREF Value Selection bits ( $0 \le (CVR<3:0>) \le 15$ )                                                                                                                                                    |       |                   |                  |                 |       |  |  |  |

| <b>CVR3:CVR0:</b> Comparator VREF Value Selection bits ( $0 \le (CVR<3:0>) \le$ |

|---------------------------------------------------------------------------------|

| When CVRR = 1:                                                                  |

| $CVREF = ((CVR < 3:0 >)/24) \bullet (CVRSRC)$                                   |

| When CVRR = 0:                                                                  |

| CVREF = (CVRSRC/4) + ((CVR<3:0>)/32) • (CVRSRC)                                 |

|                                                                                 |

Note 1: CVROE overrides the TRISA<2> bit setting.

## 23.0 SPECIAL FEATURES OF THE CPU

PIC18F2420/2520/4420/4520 devices include several features intended to maximize reliability and minimize cost through elimination of external components. These are:

- Oscillator Selection

- Resets:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor

- Two-Speed Start-up

- Code Protection

- ID Locations

- In-Circuit Serial Programming

The oscillator can be configured for the application depending on frequency, power, accuracy and cost. All of the options are discussed in detail in **Section 2.0 "Oscillator Configurations"**.

A complete discussion of device Resets and interrupts is available in previous sections of this data sheet.

In addition to their Power-up and Oscillator Start-up Timers provided for Resets, PIC18F2420/2520/4420/ 4520 devices have a Watchdog Timer, which is either permanently enabled via the Configuration bits or software controlled (if configured as disabled). The inclusion of an internal RC oscillator also provides the additional benefits of a Fail-Safe Clock Monitor (FSCM) and Two-Speed Start-up. FSCM provides for background monitoring of the peripheral clock and automatic switchover in the event of its failure. Two-Speed Start-up enables code to be executed almost immediately on start-up, while the primary clock source completes its start-up delays.

All of these features are enabled and configured by setting the appropriate Configuration register bits.

## 23.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped starting at program memory location, 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h-3FFFFFh), which can only be accessed using table reads and table writes.

Programming the Configuration registers is done in a manner similar to programming the Flash memory. The WR bit in the EECON1 register starts a self-timed write to the Configuration register. In normal operation mode, a TBLWT instruction with the TBLPTR pointing to the Configuration register sets up the address and the data for the Configuration register write. Setting the WR bit starts a long write to the Configuration registers are written a byte at a time. To write or erase a configuration cell, a TBLWT instruction can write a '1' or a '0' into the cell. For additional details on Flash programming, refer to Section 6.5 "Writing to Flash Program Memory".

| File Name |          | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3                | Bit 2                | Bit 1  | Bit 0  | Default/<br>Unprogrammed<br>Value |

|-----------|----------|-------|-------|-------|--------|----------------------|----------------------|--------|--------|-----------------------------------|

| 300001h   | CONFIG1H | IESO  | FCMEN | _     | _      | FOSC3                | FOSC2                | FOSC1  | FOSC0  | 00 0111                           |

| 300002h   | CONFIG2L | _     | _     |       | BORV1  | BORV0                | BOREN1               | BOREN0 | PWRTEN | 1 1111                            |

| 300003h   | CONFIG2H | _     | _     |       | WDTPS3 | WDTPS2               | WDTPS1               | WDTPS0 | WDTEN  | 1 1111                            |

| 300005h   | CONFIG3H | MCLRE | _     |       | _      | _                    | LPT10SC              | PBADEN | CCP2MX | 1011                              |

| 300006h   | CONFIG4L | DEBUG | XINST |       |        |                      | LVP                  |        | STVREN | 101-1                             |

| 300008h   | CONFIG5L | _     | —     | _     | —      | CP3 <sup>(1)</sup>   | CP2 <sup>(1)</sup>   | CP1    | CP0    | 1111                              |

| 300009h   | CONFIG5H | CPD   | CPB   | _     | _      | _                    | —                    | _      | —      | 11                                |

| 30000Ah   | CONFIG6L |       | _     |       | _      | WRT3 <sup>(1)</sup>  | WRT2 <sup>(1)</sup>  | WRT1   | WRT0   | 1111                              |

| 30000Bh   | CONFIG6H | WRTD  | WRTB  | WRTC  |        | —                    | —                    | _      | —      | 111                               |

| 30000Ch   | CONFIG7L | _     | _     |       | _      | EBTR3 <sup>(1)</sup> | EBTR2 <sup>(1)</sup> | EBTR1  | EBTR0  | 1111                              |

| 30000Dh   | CONFIG7H | _     | EBTRB | _     |        |                      | _                    | _      | —      | -1                                |

| 3FFFFEh   | DEVID1   | DEV2  | DEV1  | DEV0  | REV4   | REV3                 | REV2                 | REV1   | REV0   | xxxx xxxx <sup>(2)</sup>          |

| 3FFFFFh   | DEVID2   | DEV10 | DEV9  | DEV8  | DEV7   | DEV6                 | DEV5                 | DEV4   | DEV3   | xxxx xxxx <sup>(2)</sup>          |

TABLE 23-1: CONFIGURATION BITS AND DEVICE IDs