Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4420t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name             | Pi        | n Numb    | ber     | Pin Buffer |      | Description                                                                                       |

|----------------------|-----------|-----------|---------|------------|------|---------------------------------------------------------------------------------------------------|

|                      | PDIP      | QFN       | TQFP    | Туре       | Туре | Description                                                                                       |

| MCLR/VPP/RE3         | 1         | 18        | 18      |            |      | Master Clear (input) or programming voltage (input).                                              |

| MCLR                 |           |           |         | I          | ST   | Master Clear (Reset) input. This pin is an active-low Reset to the device.                        |

| VPP                  |           |           |         | Р          |      | Programming voltage input.                                                                        |

| RE3                  |           |           |         | Ι          | ST   | Digital input.                                                                                    |

| OSC1/CLKI/RA7        | 13        | 32        | 30      |            |      | Oscillator crystal or external clock input.                                                       |

| OSC1                 |           |           |         | I          | ST   | Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode; |

|                      |           |           |         |            |      | analog otherwise.                                                                                 |

| CLKI                 |           |           |         | Ι          | CMOS | External clock source input. Always associated with                                               |

|                      |           |           |         |            |      | pin function, OSC1. (See related OSC1/CLKI,                                                       |

| RA7                  |           |           |         | I/O        | TTL  | OSC2/CLKO pins.)<br>General purpose I/O pin.                                                      |

| OSC2/CLKO/RA6        | 14        | 33        | 31      |            |      | Oscillator crystal or clock output.                                                               |

| OSC2                 |           | 00        | 01      | 0          |      | Oscillator crystal output. Connects to crystal                                                    |

|                      |           |           |         |            |      | or resonator in Crystal Oscillator mode.                                                          |

| CLKO                 |           |           |         | 0          |      | In RC mode, OSC2 pin outputs CLKO which                                                           |

|                      |           |           |         |            |      | has 1/4 the frequency of OSC1 and denotes the instruction cycle rate.                             |

| RA6                  |           |           |         | I/O        | TTL  | General purpose I/O pin.                                                                          |

| Legend: TTL = TTL co | ompatibl  | e input   |         |            | . (  | CMOS = CMOS compatible input or output                                                            |

|                      | tt Trigge | r input v | with CM | OS lev     |      | = Input                                                                                           |

| O = Output           | t         |           |         |            | F    | P = Power                                                                                         |

### TABLE 1-3: PIC18F4420/4520 PINOUT I/O DESCRIPTIONS

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

## 6.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 32 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

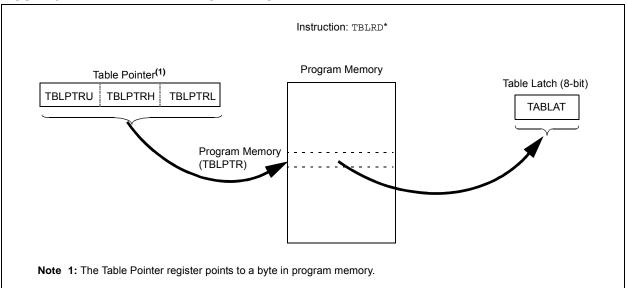

### 6.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and places it into the data RAM space. Figure 6-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 6.5** "**Writing to Flash Program Memory**". Figure 6-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

FIGURE 6-1:

## 6.2.2 TABLAT – TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

### 6.2.3 TBLPTR – TABLE POINTER REGISTER

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the device ID, the user ID and the Configuration bits.

The Table Pointer register, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations are shown in Table 6-1. These operations on the TBLPTR only affect the low-order 21 bits.

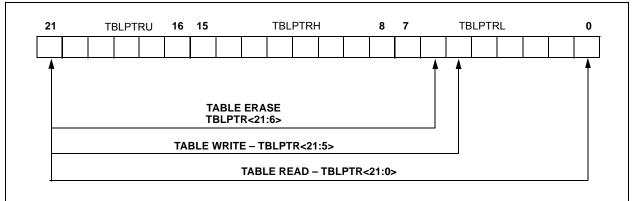

### 6.2.4 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory into TABLAT.

When a TBLWT is executed, the five LSbs of the Table Pointer register (TBLPTR<4:0>) determine which of the 32 program memory holding registers is written to. When the timed write to program memory begins (via the WR bit), the 16 MSbs of the TBLPTR (TBLPTR<21:6>) determine which program memory block of 32 bytes is written to. For more detail, see **Section 6.5 "Writing to Flash Program Memory"**.

When an erase of program memory is executed, the 16 MSbs of the Table Pointer register (TBLPTR<21:6>) point to the 64-byte block that will be erased. The Least Significant bits (TBLPTR<5:0>) are ignored.

Figure 6-3 describes the relevant boundaries of TBLPTR based on Flash program memory operations.

### TABLE 6-1: TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS

| Example            | Operation on Table Pointer                  |

|--------------------|---------------------------------------------|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |

#### FIGURE 6-3:

#### TABLE POINTER BOUNDARIES BASED ON OPERATION

## 7.0 DATA EEPROM MEMORY

The data EEPROM is a nonvolatile memory array, separate from the data RAM and program memory, that is used for long-term storage of program data. It is not directly mapped in either the register file or program memory space but is indirectly addressed through the Special Function Registers (SFRs). The EEPROM is readable and writable during normal operation over the entire VDD range.

Five SFRs are used to read and write to the data EEPROM as well as the program memory. They are:

- EECON1

- EECON2

- EEDATA

- EEADR

The data EEPROM allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and the EEADR register holds the address of the EEPROM location being accessed.

The EEPROM data memory is rated for high erase/write cycle endurance. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an on-chip timer; it will vary with voltage and temperature as well as from chip to chip. Please refer to parameter D122 (Table 26-1 in **Section 26.0 "Electrical Characteristics"**) for exact limits.

## 7.1 EEADR Register

The EEADR register is used to address the data EEPROM for read and write operations. The 8-bit range of the register can address a memory range of 256 bytes (00h to FFh).

### 7.2 EECON1 and EECON2 Registers

Access to the data EEPROM is controlled by two registers: EECON1 and EECON2. These are the same registers which control access to the program memory and are used in a similar manner for the data EEPROM.

The EECON1 register (Register 7-1) is the control register for data and program memory access. Control bit EEPGD determines if the access will be to program or data EEPROM memory. When clear, operations will access the data EEPROM memory. When set, program memory is accessed.

Control bit, CFGS, determines if the access will be to the Configuration registers or to program memory/data EEPROM memory. When set, subsequent operations access Configuration registers. When CFGS is clear, the EEPGD bit selects either program Flash or data EEPROM memory.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR         |

|-------|--------------------------------------------|

|       | may read as '1'. This can indicate that a  |

|       | write operation was prematurely termi-     |

|       | nated by a Reset, or a write operation was |

|       | attempted improperly.                      |

The WR control bit initiates write operations. The bit can be set but not cleared in software. It is only cleared in hardware at the completion of the write operation.

**Note:** The EEIF interrupt flag bit (PIR2<4>) is set when the write is complete. It must be cleared in software.

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (EEPGD = 1). Program memory is read using table read instructions. See **Section 6.1 "Table Reads and Table Writes"** regarding table reads.

The EECON2 register is not a physical register. It is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

# PIC18F2420/2520/4420/4520

NOTES:

### 15.1 CCP Module Configuration

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

#### 15.1.1 CCP MODULES AND TIMER RESOURCES

The CCP modules utilize Timers 1, 2 or 3, depending on the mode selected. Timer1 and Timer3 are available to modules in Capture or Compare modes, while Timer2 is available for modules in PWM mode.

# TABLE 15-1:CCP MODE – TIMER<br/>RESOURCE

| CCP/ECCP Mode | Timer Resource   |

|---------------|------------------|

| Capture       | Timer1 or Timer3 |

| Compare       | Timer1 or Timer3 |

| PWM           | Timer2           |

The assignment of a particular timer to a module is determined by the Timer to CCP enable bits in the T3CON register (Register 14-1). Both modules may be active at any given time and may share the same timer resource if they are configured to operate in the same mode (Capture/Compare or PWM) at the same time. The interactions between the two modules are summarized in Figure 15-1 and Figure 15-2. In Timer1 in Asynchronous Counter mode, the capture operation will not work.

### 15.1.2 CCP2 PIN ASSIGNMENT

The pin assignment for CCP2 (Capture input, Compare and PWM output) can change, based on device configuration. The CCP2MX Configuration bit determines which pin CCP2 is multiplexed to. By default, it is assigned to RC1 (CCP2MX = 1). If the Configuration bit is cleared, CCP2 is multiplexed with RB3.

Changing the pin assignment of CCP2 does not automatically change any requirements for configuring the port pin. Users must always verify that the appropriate TRIS register is configured correctly for CCP2 operation, regardless of where it is located.

### TABLE 15-2: INTERACTIONS BETWEEN CCP1 AND CCP2 FOR TIMER RESOURCES

| CCP1 Mode          | CCP2 Mode          | Interaction                                                                                                                                                                                                                                                         |

|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capture            | Capture            | Each module can use TMR1 or TMR3 as the time base. The time base can be different for each CCP.                                                                                                                                                                     |

| Capture            | Compare            | CCP2 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Automatic A/D conversions on trigger event can also be done. Operation of CCP1 could be affected if it is using the same timer as a time base. |

| Compare            | Capture            | CCP1 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Operation of CCP2 could be affected if it is using the same timer as a time base.                                                              |

| Compare            | Compare            | Either module can be configured for the Special Event Trigger to reset the time base.<br>Automatic A/D conversions on CCP2 trigger event can be done. Conflicts may occur if<br>both modules are using the same time base.                                          |

| Capture            | PWM <sup>(1)</sup> | None                                                                                                                                                                                                                                                                |

| Compare            | PWM <sup>(1)</sup> | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | Capture            | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | Compare            | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | PWM <sup>(1)</sup> | Both PWMs will have the same frequency and update rate (TMR2 interrupt).                                                                                                                                                                                            |

Note 1: Includes standard and Enhanced PWM operation.

# 17.3.8 OPERATION IN POWER-MANAGED MODES

In SPI Master mode, module clocks may be operating at a different speed than when in full-power mode; in the case of Sleep mode, all clocks are halted.

In most Idle modes, a clock is provided to the peripherals. That clock should be from the primary clock source, the secondary clock (Timer1 oscillator at 32.768 kHz) or the INTOSC source. See **Section 2.7 "Clock Sources and Oscillator Switching"** for additional information.

In most cases, the speed that the master clocks SPI data is not important; however, this should be evaluated for each system.

If MSSP interrupts are enabled, they can wake the controller from Sleep mode, or one of the Idle modes, when the master completes sending data. If an exit from Sleep or Idle mode is not desired, MSSP interrupts should be disabled.

If the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the devices wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in any power-managed mode and data to be shifted into the SPI Transmit/ Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set, and if enabled, will wake the device.

## 17.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

### 17.3.10 BUS MODE COMPATIBILITY

Table 17-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

| Standard SPI Mode | Control I | Bits State |

|-------------------|-----------|------------|

| Terminology       | СКР       | CKE        |

| 0, 0              | 0         | 1          |

| 0, 1              | 0         | 0          |

| 1, 0              | 1         | 1          |

| 1, 1              | 1         | 0          |

### TABLE 17-1: SPI BUS MODES

There is also an SMP bit which controls when the data is sampled.

| Name    | Bit 7                | Bit 6                 | Bit 5      | Bit 4        | Bit 3    | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------|-----------------------|------------|--------------|----------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH             | PEIE/GIEL             | TMR0IE     | INT0IE       | RBIE     | TMR0IF | INT0IF | RBIF   | 49                         |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF                  | RCIF       | TXIF         | SSPIF    | CCP1IF | TMR2IF | TMR1IF | 52                         |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE                  | RCIE       | TXIE         | SSPIE    | CCP1IE | TMR2IE | TMR1IE | 52                         |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP                  | RCIP       | TXIP         | SSPIP    | CCP1IP | TMR2IP | TMR1IP | 52                         |

| TRISA   | TRISA7(2)            | TRISA6 <sup>(2)</sup> | PORTA Da   | ta Direction | Register |        |        |        | 52                         |

| TRISC   | PORTC Da             | ta Direction          | Register   |              |          |        |        |        | 52                         |

| SSPBUF  | MSSP Rec             | eive Buffer/1         | ransmit Re | gister       |          |        |        |        | 50                         |

| SSPCON1 | WCOL                 | SSPOV                 | SSPEN      | CKP          | SSPM3    | SSPM2  | SSPM1  | SSPM0  | 50                         |

| SSPSTAT | SMP                  | CKE                   | D/Ā        | Р            | S        | R/W    | UA     | BF     | 50                         |

TABLE 17-2:

REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: Shaded cells are not used by the MSSP in SPI mode.

Note 1: These bits are unimplemented in 28-pin devices; always maintain these bits clear.

**2:** PORTA<7:6> and their direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

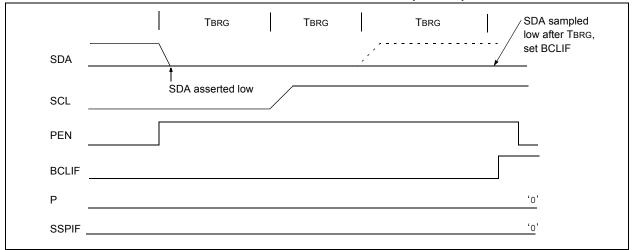

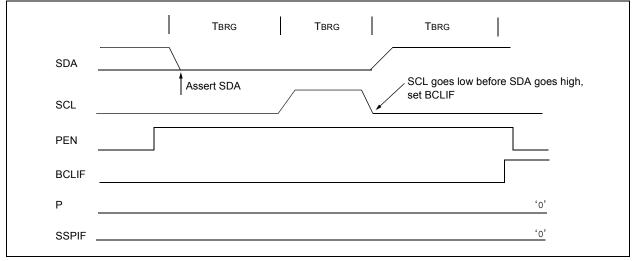

### 17.4.17.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high.

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 17-31). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 17-32).

### FIGURE 17-31: BUS COLLISION DURING A STOP CONDITION (CASE 1)

### FIGURE 17-32: BUS COLLISION DURING A STOP CONDITION (CASE 2)

# PIC18F2420/2520/4420/4520

NOTES:

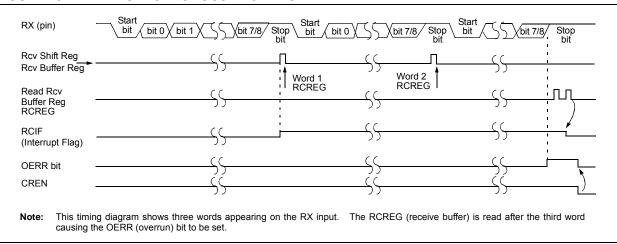

### FIGURE 18-7: ASYNCHRONOUS RECEPTION

| TABLE 18-6: | <b>REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION</b> |

|-------------|---------------------------------------------------------|

|-------------|---------------------------------------------------------|

|                      |                                                                          |                                                                                                                                                                                                                                                  |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                             | Bit 2                                                                                                                                                                                                                                                             | Bit 1                                                                                                                                                                                                                                                                      | Bit 0                                                                                                                                                                                                                                                                                                                                       | Values<br>on page                                                                                                                                                                                                                                                                    |

|----------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IE/GIEH              | PEIE/GIEL                                                                | TMR0IE                                                                                                                                                                                                                                           | INT0IE                                                                                                                                                             | RBIE                                                                                                                                                                                                                                                                                                                                                                                                        | TMR0IF                                                                                                                                                                                                                                                            | INT0IF                                                                                                                                                                                                                                                                     | RBIF                                                                                                                                                                                                                                                                                                                                        | 49                                                                                                                                                                                                                                                                                   |

| PSPIF <sup>(1)</sup> | ADIF                                                                     | RCIF                                                                                                                                                                                                                                             | TXIF                                                                                                                                                               | SSPIF                                                                                                                                                                                                                                                                                                                                                                                                       | CCP1IF                                                                                                                                                                                                                                                            | TMR2IF                                                                                                                                                                                                                                                                     | TMR1IF                                                                                                                                                                                                                                                                                                                                      | 52                                                                                                                                                                                                                                                                                   |

| SPIE <sup>(1)</sup>  | ADIE                                                                     | RCIE                                                                                                                                                                                                                                             | TXIE                                                                                                                                                               | SSPIE                                                                                                                                                                                                                                                                                                                                                                                                       | CCP1IE                                                                                                                                                                                                                                                            | TMR2IE                                                                                                                                                                                                                                                                     | TMR1IE                                                                                                                                                                                                                                                                                                                                      | 52                                                                                                                                                                                                                                                                                   |

| SPIP <sup>(1)</sup>  | ADIP                                                                     | RCIP                                                                                                                                                                                                                                             | TXIP                                                                                                                                                               | SSPIP                                                                                                                                                                                                                                                                                                                                                                                                       | CCP1IP                                                                                                                                                                                                                                                            | TMR2IP                                                                                                                                                                                                                                                                     | TMR1IP                                                                                                                                                                                                                                                                                                                                      | 52                                                                                                                                                                                                                                                                                   |

| SPEN                 | RX9                                                                      | SREN                                                                                                                                                                                                                                             | CREN                                                                                                                                                               | ADDEN                                                                                                                                                                                                                                                                                                                                                                                                       | FERR                                                                                                                                                                                                                                                              | OERR                                                                                                                                                                                                                                                                       | RX9D                                                                                                                                                                                                                                                                                                                                        | 51                                                                                                                                                                                                                                                                                   |

| USART R              | eceive Regis                                                             | ster                                                                                                                                                                                                                                             |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                             | 51                                                                                                                                                                                                                                                                                   |

| CSRC                 | TX9                                                                      | TXEN                                                                                                                                                                                                                                             | SYNC                                                                                                                                                               | SENDB                                                                                                                                                                                                                                                                                                                                                                                                       | BRGH                                                                                                                                                                                                                                                              | TRMT                                                                                                                                                                                                                                                                       | TX9D                                                                                                                                                                                                                                                                                                                                        | 51                                                                                                                                                                                                                                                                                   |

| BDOVF                | RCIDL                                                                    | RXDTP                                                                                                                                                                                                                                            | TXCKP                                                                                                                                                              | BRG16                                                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                 | WUE                                                                                                                                                                                                                                                                        | ABDEN                                                                                                                                                                                                                                                                                                                                       | 51                                                                                                                                                                                                                                                                                   |

| USART Ba             | aud Rate Ge                                                              | nerator Reg                                                                                                                                                                                                                                      | gister High I                                                                                                                                                      | Byte                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                             | 51                                                                                                                                                                                                                                                                                   |

| USART Ba             | aud Rate Ge                                                              | nerator Reg                                                                                                                                                                                                                                      | gister Low E                                                                                                                                                       | Byte                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                             | 51                                                                                                                                                                                                                                                                                   |

|                      | SPIE(1)<br>SPIP(1)<br>SPEN<br>SART R<br>SRC<br>SDOVF<br>SART B<br>SART B | SPIF <sup>(1)</sup> ADIF         SPIE <sup>(1)</sup> ADIE         SPIP <sup>(1)</sup> ADIP         SPEN       RX9         SART Receive Regis         SRC       TX9         BDOVF       RCIDL         SART Baud Rate Ge         SART Baud Rate Ge | SPIF(1)ADIFRCIFSPIE(1)ADIERCIESPIP(1)ADIPRCIPSPENRX9SRENSART Receive RegisterSRCCSRCTX9TXENBDOVFRCIDLRXDTPSART Baud Rate Generator RegSART Baud Rate Generator Reg | SPIF <sup>(1)</sup> ADIF       RCIF       TXIF         SPIE <sup>(1)</sup> ADIE       RCIE       TXIE         SPIP <sup>(1)</sup> ADIP       RCIP       TXIP         SPEN       RX9       SREN       CREN         SART Receive Register       CSRC       TX9       TXEN       SYNC         SDOVF       RCIDL       RXDTP       TXCKP         SART Baud Rate Generator Register High I       Ital       Ital | SPIF(1)ADIFRCIFTXIFSSPIFSPIE(1)ADIERCIETXIESSPIESPIP(1)ADIPRCIPTXIPSSPIPSPENRX9SRENCRENADDENSART Receive RegisterSSRCTX9TXENSYNCSRCTX9TXENSYNCSENDBBDOVFRCIDLRXDTPTXCKPBRG16SART Baud Rate Generator Register High ByteSART Baud Rate Generator Register Low Byte | SPIF(1)ADIFRCIFTXIFSSPIFCCP1IFSPIE(1)ADIERCIETXIESSPIECCP1IESPIP(1)ADIPRCIPTXIPSSPIPCCP1IPSPENRX9SRENCRENADDENFERRSART Receive RegisterSSRCTX9TXENSYNCSENDBSDOVFRCIDLRXDTPTXCKPBRG16—SART Baud Rate Generator Register High ByteSART Baud Rate Generator Register Low Byte | SPIF(1)ADIFRCIFTXIFSSPIFCCP1IFTMR2IFSPIE(1)ADIERCIETXIESSPIECCP1IETMR2IESPIP(1)ADIPRCIPTXIPSSPIPCCP1IPTMR2IPSPENRX9SRENCRENADDENFERROERRSART Receive RegisterSYNCSENDBBRGHTRMTSDOVFRCIDLRXDTPTXCKPBRG16—WUESART Baud Rate Generator Register High ByteSART Baud Rate Generator Register Low ByteStart Baud Rate Generator Register Low Byte | SPIF(1)ADIFRCIFTXIFSSPIFCCP1IFTMR2IFTMR1IFSPIE(1)ADIERCIETXIESSPIECCP1IETMR2IETMR1IESPIP(1)ADIPRCIPTXIPSSPIPCCP1IPTMR2IPTMR1IPSPENRX9SRENCRENADDENFERROERRRX9DSART Receive RegisterSYNCSENDBBRGHTRMTTX9DSDOVFRCIDLRXDTPTXCKPBRG16—WUEABDENSART Baud Rate Generator Register Low Byte |

Legend: — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: Reserved in 28-pin devices; always maintain these bits clear.

### 18.2.4 AUTO-WAKE-UP ON SYNC BREAK CHARACTER

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper byte reception cannot be performed. The auto-wake-up feature allows the controller to wake-up due to activity on the RX/DT line while the EUSART is operating in Asynchronous mode.

The auto-wake-up feature is enabled by setting the WUE bit (BAUDCON<1>). Once set, the typical receive sequence on RX/DT is disabled and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a Wake-up Signal character for the LIN protocol.)

Following a wake-up event, the module generates an RCIF interrupt. The interrupt is generated synchronously to the Q clocks in normal operating modes (Figure 18-8) and asynchronously, if the device is in Sleep mode (Figure 18-9). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared once a low-tohigh transition is observed on the RX line following the wake-up event. At this point, the EUSART module is in Idle mode and returns to normal operation. This signals to the user that the Sync Break event is over.

### 18.3 EUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTA<4>). In addition, enable bit, SPEN (RCSTA<7>), is set in order to configure the TX and RX pins to CK (clock) and DT (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK line. Clock polarity is selected with the TXCKP bit (BAUDCON<4>); setting TXCKP sets the Idle state on CK as high, while clearing the bit sets the Idle state as low. This option is provided to support Microwire devices with this module.

### 18.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 18-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available).

Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG is empty and the TXIF flag bit (PIR1<4>) is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF is set regardless of the state of enable bit, TXIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREG register.

While flag bit, TXIF, indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

|                            | Q1Q2Q      | 23Q4 Q1Q2   | Q3Q4 Q1Q2   | Q3Q4 Q1Q2  | Q3Q4Q1Q   | 2 Q3 Q4     | Q3Q4 C       | 1Q2Q3Q4 | Q1Q2Q30          | 24 Q1 Q2Q3Q4      | Q1Q2Q3Q4    | Q1 Q2 Q3 Q4   | Q1Q2Q3      | Q4      |

|----------------------------|------------|-------------|-------------|------------|-----------|-------------|--------------|---------|------------------|-------------------|-------------|---------------|-------------|---------|

| RC7/RX/DT                  |            |             | bit 0       | bit 1      |           | 2           | ->- <u>+</u> | bit 7   | bit 0 X          | bit 1 X           |             |               | bit 7       |         |

| RC6/TX/CK (<br>(TXCKP = 0) | ; <u> </u> |             |             |            |           |             | ;            |         |                  |                   | <u>-</u>    | <u> </u>      |             |         |

| RC6/TX/CK<br>(TXCKP = 1)   |            |             |             |            | ╶┊┚       | <u></u>     | -Ļ           |         |                  | ļ                 | Ļ.          |               |             |         |

| Write to<br>TXREG Reg      |            | Write W     | ord 1       | Write Wor  | d 2       |             | 1<br>1<br>1  |         | 1<br>1<br>1      | <u> </u><br> <br> | 1<br>1<br>1 | -55           | 1<br>1<br>1 | -'      |

| TXIF bit<br>(Interrupt Fla | g)         | <br>        |             |            | <u>∼¦</u> | <u>}</u>    |              |         | :ſ               |                   | <br> <br>   | <u></u>       | ;<br>;      | _;<br>; |

| TRMT bit                   |            | 1           | 1<br>1<br>1 |            |           |             |              |         | ,<br>1<br>1<br>1 | <br> <br> <br>    | 1<br>1<br>1 | <del>}}</del> | ļ           |         |

| TXEN bit                   | <u>'1'</u> | 1<br>1<br>1 | 1<br>1<br>1 |            |           | <u>{</u> }  |              |         | 1<br>1           | •<br>•            | 1<br>1<br>1 | <u>}</u>      | ۱ ،<br>۱    | 1'      |

| Note: Syn                  | c Maste    | r mode, S   | PBRG = 0,   | continuous | transmis  | sion of two | 8-bit woi    | rds.    |                  |                   |             |               |             |         |

FIGURE 18-11: SYNCHRONOUS TRANSMISSION

## 20.2 Comparator Operation

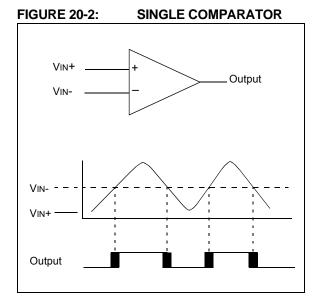

A single comparator is shown in Figure 20-2, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 20-2 represent the uncertainty, due to input offsets and response time.

### 20.3 Comparator Reference

Depending on the comparator operating mode, either an external or internal voltage reference may be used. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly (Figure 20-2).

### 20.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSS and VDD and can be applied to either pin of the comparator(s).

### 20.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference from the comparator voltage reference module. This module is described in more detail in **Section 21.0 "Comparator Voltage Reference Module"**.

The internal reference is only available in the mode where four inputs are multiplexed to two comparators (CM<2:0> = 110). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

## 20.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (see Section 26.0 "Electrical Characteristics").

## 20.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read-only. The comparator outputs may also be directly output to the RA4 and RA5 I/O pins. When enabled, multiplexers in the output path of the RA4 and RA5 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 20-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA4 and RA5 pins while in this mode.

The polarity of the comparator outputs can be changed using the C2INV and C1INV bits (CMCON<4:5>).

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin defined as a digital input may cause the input buffer to consume more current than is specified.

## 23.4 Fail-Safe Clock Monitor

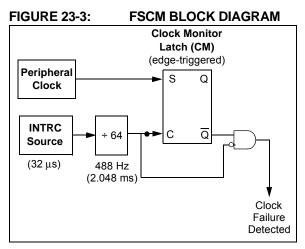

The Fail-Safe Clock Monitor (FSCM) allows the microcontroller to continue operation in the event of an external oscillator failure by automatically switching the device clock to the internal oscillator block. The FSCM function is enabled by setting the FCMEN Configuration bit.

When FSCM is enabled, the INTRC oscillator runs at all times to monitor clocks to peripherals and provide a backup clock in the event of a clock failure. Clock monitoring (shown in Figure 23-3) is accomplished by creating a sample clock signal, which is the INTRC output divided by 64. This allows ample time between FSCM sample clocks for a peripheral clock edge to occur. The peripheral device clock and the sample clock are presented as inputs to the Clock Monitor latch (CM). The CM is set on the falling edge of the device clock source, but cleared on the rising edge of the sample clock.

Clock failure is tested for on the falling edge of the sample clock. If a sample clock falling edge occurs while CM is still set, a clock failure has been detected (Figure 23-4). This causes the following:

- the FSCM generates an oscillator fail interrupt by setting bit, OSCFIF (PIR2<7>);

- the device clock source is switched to the internal oscillator block (OSCCON is not updated to show the current clock source – this is the fail-safe condition) and

- the WDT is reset.

During switchover, the postscaler frequency from the internal oscillator block may not be sufficiently stable for timing sensitive applications. In these cases, it may be desirable to select another clock configuration and enter an alternate power-managed mode. This can be done to attempt a partial recovery or execute a controlled shutdown. See Section 3.1.4 "Multiple Sleep Commands" and Section 23.3.1 "Special Considerations for Using Two-Speed Start-up" for more details.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF<2:0>, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF<2:0> bits prior to entering Sleep mode.

The FSCM will detect failures of the primary or secondary clock sources only. If the internal oscillator block fails, no failure would be detected, nor would any action be possible.

### 23.4.1 FSCM AND THE WATCHDOG TIMER

Both the FSCM and the WDT are clocked by the INTRC oscillator. Since the WDT operates with a separate divider and counter, disabling the WDT has no effect on the operation of the INTRC oscillator when the FSCM is enabled.

As already noted, the clock source is switched to the INTOSC clock when a clock failure is detected. Depending on the frequency selected by the IRCF<2:0> bits, this may mean a substantial change in the speed of code execution. If the WDT is enabled with a small prescale value, a decrease in clock speed allows a WDT time-out to occur and a subsequent device Reset. For this reason, fail-safe clock events also reset the WDT and postscaler, allowing it to start timing from when execution speed was changed and decreasing the likelihood of an erroneous time-out.

## 23.4.2 EXITING FAIL-SAFE OPERATION

The fail-safe condition is terminated by either a device Reset or by entering a power-managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 1H (with any required start-up delays that are required for the oscillator mode, such as the OST or PLL timer). The INTOSC multiplexer provides the device clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The Fail-Safe Clock Monitor then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTOSC multiplexer. The OSCCON register will remain in its Reset state until a power-managed mode is entered.

# 24.0 INSTRUCTION SET SUMMARY

PIC18F2420/2520/4420/4520 devices incorporate the standard set of 75 PIC18 core instructions, as well as an extended set of 8 new instructions, for the optimization of code that is recursive or that utilizes a software stack. The extended set is discussed later in this section.

## 24.1 Standard Instruction Set

The standard PIC18 instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from these PIC MCU instruction sets. Most instructions are a single program memory word (16 bits), but there are four instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- · Byte-oriented operations

- **Bit-oriented** operations

- · Literal operations

- Control operations

The PIC18 instruction set summary in Table 24-2 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 24-1 shows the opcode field descriptions.

Most byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator 'f' specifies which file register is to be used by the instruction. The destination designator 'd' specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All bit-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator 'b' selects the number of the bit affected by the operation, while the file register designator 'f' represents the number of the file in which the bit is located. The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the CALL or RETURN instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for four double-word instructions. These instructions were made double-word to contain the required information in 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 24-1 shows the general formats that the instructions can have. All examples use the convention 'nnh' to represent a hexadecimal number.

The Instruction Set Summary, shown in Table 24-2, lists the standard instructions recognized by the Microchip Assembler (MPASM<sup>TM</sup>).

Section 24.1.1 "Standard Instruction Set" provides a description of each instruction.

| Mnemonic, Description |        | Description                     | Cycles | 16   | -Bit Inst | truction \ | Status | Notes           |       |  |

|-----------------------|--------|---------------------------------|--------|------|-----------|------------|--------|-----------------|-------|--|

|                       |        | Description                     | Cycles | MSb  |           | LSI        |        | Affected        | Notes |  |

| LITERAL OPERATIONS    |        |                                 |        |      |           |            |        |                 |       |  |

| ADDLW                 | k      | Add Literal and WREG            | 1      | 0000 | 1111      | kkkk       | kkkk   | C, DC, Z, OV, N |       |  |

| ANDLW                 | k      | AND Literal with WREG           | 1      | 0000 | 1011      | kkkk       | kkkk   | Z, N            |       |  |

| IORLW                 | k      | Inclusive OR Literal with WREG  | 1      | 0000 | 1001      | kkkk       | kkkk   | Z, N            |       |  |

| LFSR                  | f, k   | Move Literal (12-bit)2nd word   | 2      | 1110 | 1110      | 00ff       | kkkk   | None            |       |  |

|                       |        | to FSR(f) 1st word              |        | 1111 | 0000      | kkkk       | kkkk   |                 |       |  |

| MOVLB                 | k      | Move Literal to BSR<3:0>        | 1      | 0000 | 0001      | 0000       | kkkk   | None            |       |  |

| MOVLW                 | k      | Move Literal to WREG            | 1      | 0000 | 1110      | kkkk       | kkkk   | None            |       |  |

| MULLW                 | k      | Multiply Literal with WREG      | 1      | 0000 | 1101      | kkkk       | kkkk   | None            |       |  |

| RETLW                 | k      | Return with Literal in WREG     | 2      | 0000 | 1100      | kkkk       | kkkk   | None            |       |  |

| SUBLW                 | k      | Subtract WREG from Literal      | 1      | 0000 | 1000      | kkkk       | kkkk   | C, DC, Z, OV, N |       |  |

| XORLW                 | k      | Exclusive OR Literal with WREG  | 1      | 0000 | 1010      | kkkk       | kkkk   | Z, N            |       |  |

| DATA MEN              | IORY ← | PROGRAM MEMORY OPERATION        | NS     |      |           |            |        |                 |       |  |

| TBLRD*                |        | Table Read                      | 2      | 0000 | 0000      | 0000       | 1000   | None            |       |  |

| TBLRD*+               |        | Table Read with Post-Increment  |        | 0000 | 0000      | 0000       | 1001   | None            |       |  |

| TBLRD*-               |        | Table Read with Post-Decrement  |        | 0000 | 0000      | 0000       | 1010   | None            |       |  |

| TBLRD+*               |        | Table Read with Pre-Increment   |        | 0000 | 0000      | 0000       | 1011   | None            |       |  |

| TBLWT*                |        | Table Write                     | 2      | 0000 | 0000      | 0000       | 1100   | None            |       |  |

| TBLWT*+               |        | Table Write with Post-Increment |        | 0000 | 0000      | 0000       | 1101   | None            |       |  |

| TBLWT*-               |        | Table Write with Post-Decrement |        | 0000 | 0000      | 0000       | 1110   | None            |       |  |

| TBLWT+*               |        | Table Write with Pre-Increment  |        | 0000 | 0000      | 0000       | 1111   | None            |       |  |

### TABLE 24-2: PIC18FXXXX INSTRUCTION SET (CONTINUED)

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

# PIC18F2420/2520/4420/4520

| RLNCF                                | Rotate Left f (No Carry)                                                                                                                                                                                                                                                                                                                                                                                                                                       | RI                                                                                                                                | RCF                                                                                                              | Rotate Ri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ght f throug    | Jh Carry             |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|--|