Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                              |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 1.5K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 13x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4520-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                                           | 7   |

|-------|---------------------------------------------------------------------------|-----|

| 2.0   | Oscillator Configurations                                                 |     |

| 3.0   | Power-Managed Modes                                                       | 33  |

| 4.0   | Reset                                                                     |     |

| 5.0   | Memory Organization                                                       | 53  |

| 6.0   | Flash Program Memory                                                      | 73  |

| 7.0   | Data EEPROM Memory                                                        | 83  |

| 8.0   | 8 x 8 Hardware Multiplier                                                 | 89  |

| 9.0   | Interrupts                                                                |     |

| 10.0  | I/O Ports                                                                 | 105 |

| 11.0  | Timer0 Module                                                             | 123 |

| 12.0  | Timer1 Module                                                             | 127 |

| 13.0  | Timer2 Module                                                             | 133 |

| 14.0  | Timer3 Module                                                             | 135 |

| 15.0  | Capture/Compare/PWM (CCP) Modules                                         | 139 |

| 16.0  | Enhanced Capture/Compare/PWM (ECCP) Module                                | 147 |

| 17.0  | Master Synchronous Serial Port (MSSP) Module                              |     |

| 18.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) |     |

| 19.0  | 10-Bit Analog-to-Digital Converter (A/D) Module                           | 223 |

| 20.0  | Comparator Module                                                         | 233 |

| 21.0  | Comparator Voltage Reference Module                                       |     |

| 22.0  | High/Low-Voltage Detect (HLVD)                                            |     |

| 23.0  | Special Features of the CPU                                               | 249 |

| 24.0  | Instruction Set Summary                                                   |     |

| 25.0  | Development Support                                                       |     |

| 26.0  | Electrical Characteristics                                                |     |

| 27.0  | DC and AC Characteristics Graphs and Tables                               |     |

|       | Packaging Information                                                     |     |

| Appe  | endix A: Revision History                                                 | 395 |

|       | andix B: Device Differences                                               |     |

|       | endix C: Migration from Mid-Range to Enhanced Devices                     |     |

|       | endix D: Migration from High-End to Enhanced Devices                      |     |

| Index | <                                                                         | 397 |

|       | Microchip Web Site                                                        |     |

|       | omer Change Notification Service                                          |     |

|       | omer Support                                                              |     |

|       | ler Response                                                              |     |

| PIC1  | 8F2420/2520/4420/4520 Product Identification System                       | 409 |

### 2.0 OSCILLATOR CONFIGURATIONS

#### 2.1 Oscillator Types

PIC18F2420/2520/4420/4520 devices can be operated in ten different oscillator modes. The user can program the Configuration bits, FOSC<3:0>, in Configuration Register 1H to select one of these ten modes:

- 1. LP Low-Power Crystal

- 2. XT Crystal/Resonator

- 3. HS High-Speed Crystal/Resonator

- 4. HSPLL High-Speed Crystal/Resonator with PLL Enabled

- 5. RC External Resistor/Capacitor with Fosc/4 Output on RA6

- 6. RCIO External Resistor/Capacitor with I/O on RA6

- 7. INTIO1 Internal Oscillator with Fosc/4 Output on RA6 and I/O on RA7

- 8. INTIO2 Internal Oscillator with I/O on RA6 and RA7

- 9. EC External Clock with Fosc/4 Output

- 10. ECIO External Clock with I/O on RA6

#### 2.2 Crystal Oscillator/Ceramic Resonators

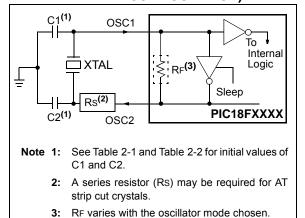

In XT, LP, HS or HSPLL Oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 2-1 shows the pin connections.

The oscillator design requires the use of a parallel cut crystal.

Note: Use of a series cut crystal may give a frequency out of the crystal manufacturer's specifications. FIGURE 2-1:

#### CRYSTAL/CERAMIC RESONATOR OPERATION (XT, LP, HS OR HSPLL CONFIGURATION)

### TABLE 2-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| Typical Capacitor Values Used: |          |       |       |  |  |  |  |  |

|--------------------------------|----------|-------|-------|--|--|--|--|--|

| Mode Freq OSC1 OSC             |          |       |       |  |  |  |  |  |

| XT                             | 3.58 MHz | 15 pF | 15 pF |  |  |  |  |  |

|                                | 4.19 MHz | 15 pF | 15 pF |  |  |  |  |  |

|                                | 4 MHz    | 30 pF | 30 pF |  |  |  |  |  |

|                                | 4 MHz    | 50 pF | 50 pF |  |  |  |  |  |

#### Capacitor values are for design guidance only.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following Table 2-2 for additional information.

Note: When using resonators with frequencies above 3.5 MHz, the use of HS mode, rather than XT mode, is recommended. HS mode may be used at any VDD for which the controller is rated. If HS is selected, it is possible that the gain of the oscillator will overdrive the resonator. Therefore, a series resistor should be placed between the OSC2 pin and the resonator. As a good starting point, the recommended value of Rs is 330Ω.

#### 3.4.1 PRI\_IDLE MODE

This mode is unique among the three low-power Idle modes in that it does not disable the primary device clock. For timing-sensitive applications, this allows for the fastest resumption of device operation with its more accurate primary clock source, since the clock source does not have to "warm-up" or transition from another oscillator.

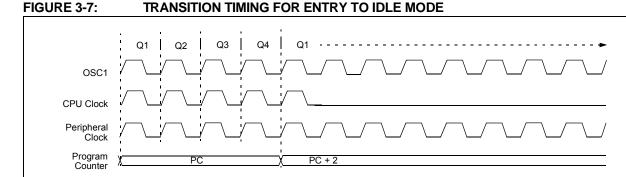

PRI\_IDLE mode is entered from PRI\_RUN mode by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, set IDLEN first, then clear the SCS bits and execute SLEEP. Although the CPU is disabled, the peripherals continue to be clocked from the primary clock source specified by the FOSC<3:0> Configuration bits. The OSTS bit remains set (see Figure 3-7).

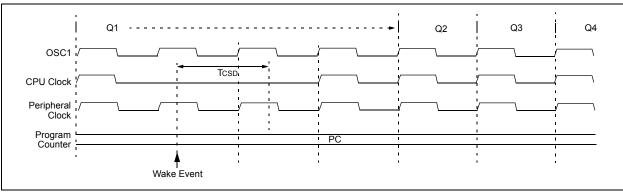

When a wake event occurs, the CPU is clocked from the primary clock source. A delay of interval TCSD is required between the wake event and when code execution starts. This is required to allow the CPU to become ready to execute instructions. After the wake-up, the OSTS bit remains set. The IDLEN and SCS bits are not affected by the wake-up (see Figure 3-8).

#### 3.4.2 SEC\_IDLE MODE

In SEC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the Timer1 oscillator. This mode is entered from SEC\_RUN by

setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, set the IDLEN bit first, then set the SCS<1:0> bits to '01' and execute SLEEP. When the clock source is switched to the Timer1 oscillator, the primary oscillator is shut down, the OSTS bit is cleared and the T1RUN bit is set.

When a wake event occurs, the peripherals continue to be clocked from the Timer1 oscillator. After an interval of TCSD, following the wake event, the CPU begins executing code being clocked by the Timer1 oscillator. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run (see Figure 3-8).

Note: The Timer1 oscillator should already be running prior to entering SEC\_IDLE mode. If the T1OSCEN bit is not set when the SLEEP instruction is executed, the SLEEP instruction will be ignored and entry to SEC\_IDLE mode will not occur. If the Timer1 oscillator is enabled but not yet running, peripheral clocks will be delayed until the oscillator has started. In such situations, initial oscillator operation is far from stable and unpredictable operation may result.

#### FIGURE 3-8: TRANSITION TIMING FOR WAKE FROM IDLE TO RUN MODE

#### 4.4 Brown-out Reset (BOR)

PIC18F2420/2520/4420/4520 devices implement a BOR circuit that provides the user with a number of configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> Configuration bits. There are a total of four BOR configurations which are summarized in Table 4-1.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below VBOR (parameter D005) for greater than TBOR (parameter 35) will reset the device. A Reset may or may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR.

If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay, TPWRT (parameter 33). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay.

BOR and the Power-up Timer (PWRT) are independently configured. Enabling the Brown-out Reset does not automatically enable the PWRT.

#### 4.4.1 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<6>). Setting SBOREN enables the BOR to function as previously described. Clearing SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise it is read as '0'. Placing the BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change BOR configuration. It also allows the user to tailor device power consumption in software by eliminating the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

| Note: | Even when BOR is under software control,   |

|-------|--------------------------------------------|

|       | the Brown-out Reset voltage level is still |

|       | set by the BORV<1:0> Configuration bits;   |

|       | it cannot be changed in software.          |

#### 4.4.2 DETECTING BOR

When BOR is enabled, the BOR bit always resets to '0' on any BOR or POR event. This makes it difficult to determine if a BOR event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR bit is reset to '1' in software immediately after any POR event. If BOR is '0' while POR is '1', it can be reliably assumed that a BOR event has occurred.

#### 4.4.3 DISABLING BOR IN SLEEP MODE

When BOREN<1:0> = 10, the BOR remains under hardware control and operates as previously described. Whenever the device enters Sleep mode, however, the BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code, when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

| BOR Con | BOR Configuration Status of |                     |                                                                                    |

|---------|-----------------------------|---------------------|------------------------------------------------------------------------------------|

| BOREN1  | BOREN0                      | SBOREN<br>(RCON<6>) | BOR Operation                                                                      |

| 0       | 0                           | Unavailable         | BOR disabled; must be enabled by reprogramming the Configuration bits.             |

| 0       | 1                           | Available           | BOR enabled in software; operation controlled by SBOREN.                           |

| 1       | 0                           | Unavailable         | BOR enabled in hardware in Run and Idle modes, disabled during Sleep mode.         |

| 1       | 1                           | Unavailable         | BOR enabled in hardware; must be disabled by reprogramming the Configuration bits. |

TABLE 4-1: BOR CONFIGURATIONS

#### EXAMPLE 6-3: WRITING TO FLASH PROGRAM MEMORY

| MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC                                                                                | OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVF<br>OVVF<br>OVVF<br>OVVF<br>OVLW<br>OVVF<br>OVLW<br>OVVF<br>OVLW<br>OVVF<br>OVLW<br>OVVF<br>OVLW | D'64<br>COUNTER<br>BUFFER_ADDR_HIGH<br>FSROH<br>BUFFER_ADDR_LOW<br>FSROL<br>CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL<br>TABLAT, W<br>POSTINCO<br>COUNTER<br>READ_BLOCK<br>DATA_ADDR_HIGH<br>FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | number of bytes in erase block<br>point to buffer<br>Load TBLPTR with the base<br>address of the memory block<br>read into TABLAT, and inc<br>get data<br>store data<br>done?<br>repeat<br>point to buffer<br>update buffer word |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>M                                                                   | OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVF<br>OVWF<br>OVVF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVVF<br>OVLW<br>OVVF                         | BUFFER_ADDR_HIGH<br>FSR0H<br>BUFFER_ADDR_LOW<br>FSR0L<br>CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL<br>TABLAT, W<br>POSTINCO<br>COUNTER<br>READ_BLOCK<br>DATA_ADDR_HIGH<br>FSR0H<br>DATA_ADDR_LOW<br>FSR0L<br>NEW_DATA_LOW<br>POSTINCO                    | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | Load TBLPTR with the base<br>address of the memory block<br>read into TABLAT, and inc<br>get data<br>store data<br>done?<br>repeat<br>point to buffer                                                                            |

| MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC                                                                                | OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVF<br>OVVF<br>OVVF<br>OVVF<br>OVLW<br>OVVF<br>OVLW<br>OVVF<br>OVLW<br>OVVF<br>OVLW<br>OVVF<br>OVLW                 | FSROH<br>BUFFER_ADDR_LOW<br>FSROL<br>CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL<br>TABLAT, W<br>POSTINCO<br>COUNTER<br>READ_BLOCK<br>DATA_ADDR_HIGH<br>FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                        | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | Load TBLPTR with the base<br>address of the memory block<br>read into TABLAT, and inc<br>get data<br>store data<br>done?<br>repeat<br>point to buffer                                                                            |

| MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC                                                                                | OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVWF<br>OVF<br>OVWF<br>OVWF<br>OVLW<br>OVVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW                                        | BUFFER_ADDR_LOW<br>FSROL<br>CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL<br>TABLAT, W<br>POSTINCO<br>COUNTER<br>READ_BLOCK<br>DATA_ADDR_HIGH<br>FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                 | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | address of the memory block<br>read into TABLAT, and inc<br>get data<br>store data<br>done?<br>repeat<br>point to buffer                                                                                                         |

| MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC                                                                                | OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVWF<br>OVF<br>OVWF<br>OVWF<br>OVLW<br>OVVF<br>OVLW<br>OVVF<br>OVLW<br>OVVF<br>OVLW                                                 | FSROL<br>CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL<br>TABLAT, W<br>POSTINCO<br>COUNTER<br>READ_BLOCK<br>DATA_ADDR_HIGH<br>FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                                    | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | address of the memory block<br>read into TABLAT, and inc<br>get data<br>store data<br>done?<br>repeat<br>point to buffer                                                                                                         |

| READ_BLOCK<br>READ_BLOCK<br>READ_BLOCK<br>TE<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC                                          | OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVWF<br>OVF<br>OVWF<br>ECFSZ<br>RA<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVVWF<br>OVLW                                                 | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL<br>TABLAT, W<br>POSTINCO<br>COUNTER<br>READ_BLOCK<br>DATA_ADDR_HIGH<br>FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                                             | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | address of the memory block<br>read into TABLAT, and inc<br>get data<br>store data<br>done?<br>repeat<br>point to buffer                                                                                                         |

| READ_BLOCK<br>READ_BLOCK<br>READ_BLOCK<br>READ_BLOCK<br>READ_BLOCK<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC  | OVWF<br>OVLW<br>OVWF<br>OVWF<br>OVF<br>OVWF<br>ECFSZ<br>RA<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW                                                          | TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL<br>TABLAT, W<br>POSTINCO<br>COUNTER<br>READ_BLOCK<br>DATA_ADDR_HIGH<br>FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                                                                | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | address of the memory block<br>read into TABLAT, and inc<br>get data<br>store data<br>done?<br>repeat<br>point to buffer                                                                                                         |

| MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC<br>MCC                                                                                | OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVF<br>OVWF<br>ECFSZ<br>RA<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW                                                          | CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL<br>TABLAT, W<br>POSTINCO<br>COUNTER<br>READ_BLOCK<br>DATA_ADDR_HIGH<br>FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                                                                           | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | read into TABLAT, and inc<br>get data<br>store data<br>done?<br>repeat<br>point to buffer                                                                                                                                        |

| MC<br>MC<br>MC<br>READ_BLOCK<br>TE<br>MC<br>DE<br>BR<br>MODIFY_WORD<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC | OVWF<br>OVLW<br>OVWF<br>BLRD*+<br>OVF<br>OVWF<br>ECFSZ<br>RA<br>OVLW<br>OVWF<br>OVLW<br>OVVF<br>OVLW<br>OVVF<br>OVLW                                                        | TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL<br>TABLAT, W<br>POSTINCO<br>COUNTER<br>READ_BLOCK<br>DATA_ADDR_HIGH<br>FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                                                                                             | ;;;;;;                                  | get data<br>store data<br>done?<br>repeat<br>point to buffer                                                                                                                                                                     |

| READ_BLOCK<br>READ_BLOCK<br>TH<br>MC<br>DE<br>BR<br>MODIFY_WORD<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC                       | OVLW<br>OVWF<br>BLRD*+<br>OVF<br>OVWF<br>ECFSZ<br>RA<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW                                                                | CODE_ADDR_LOW<br>TBLPTRL<br>TABLAT, W<br>POSTINCO<br>COUNTER<br>READ_BLOCK<br>DATA_ADDR_HIGH<br>FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                                                                                                        | ;;;;;;                                  | get data<br>store data<br>done?<br>repeat<br>point to buffer                                                                                                                                                                     |

| MC<br>READ_BLOCK<br>TH<br>MC<br>MC<br>BR<br>MODIFY_WORD<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC             | OVWF<br>BLRD*+<br>OVF<br>OVWF<br>ECFSZ<br>RA<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW                                                                        | TBLPTRL<br>TABLAT, W<br>POSTINCO<br>COUNTER<br>READ_BLOCK<br>DATA_ADDR_HIGH<br>FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                                                                                                                         | ;;;;;;                                  | get data<br>store data<br>done?<br>repeat<br>point to buffer                                                                                                                                                                     |

| READ_BLOCK<br>TE<br>MC<br>MC<br>DE<br>BR<br>MODIFY_WORD<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC             | BLRD*+<br>OVF<br>ECFSZ<br>RA<br>OVLW<br>OVWF<br>OVLW<br>OVVF<br>OVLW<br>OVWF<br>OVLW                                                                                        | TABLAT, W<br>POSTINCO<br>COUNTER<br>READ_BLOCK<br>DATA_ADDR_HIGH<br>FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                                                                                                                                    | ;;;;;;                                  | get data<br>store data<br>done?<br>repeat<br>point to buffer                                                                                                                                                                     |

| TE<br>MC<br>MC<br>DE<br>BR<br>MODIFY_WORD<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC                           | OVF<br>OVWF<br>ECFSZ<br>RA<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW                                                                                          | POSTINCO<br>COUNTER<br>READ_BLOCK<br>DATA_ADDR_HIGH<br>FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                                                                                                                                                 | ;;;;;;                                  | get data<br>store data<br>done?<br>repeat<br>point to buffer                                                                                                                                                                     |

| MC<br>MC<br>DE<br>BR<br>MODIFY_WORD<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC                                 | OVF<br>OVWF<br>ECFSZ<br>RA<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW                                                                                          | POSTINCO<br>COUNTER<br>READ_BLOCK<br>DATA_ADDR_HIGH<br>FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                                                                                                                                                 | ;;;;;;                                  | get data<br>store data<br>done?<br>repeat<br>point to buffer                                                                                                                                                                     |

| MC<br>DE<br>BR<br>MODIFY_WORD<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC                                       | OVWF<br>ECFSZ<br>RA<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW                                                                                                 | POSTINCO<br>COUNTER<br>READ_BLOCK<br>DATA_ADDR_HIGH<br>FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                                                                                                                                                 | ;;;                                     | store data<br>done?<br>repeat<br>point to buffer                                                                                                                                                                                 |

| DE<br>BR<br>MODIFY_WORD<br>MC<br>MC<br>MC<br>MC<br>MC<br>ERASE_BLOCK                                                                              | ECFSZ<br>RA<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVLW                                                                                                                 | COUNTER<br>READ_BLOCK<br>DATA_ADDR_HIGH<br>FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                                                                                                                                                             | ;;;                                     | done?<br>repeat<br>point to buffer                                                                                                                                                                                               |

| BR<br>MODIFY_WORD<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>ERASE_BLOCK                                                                              | RA<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVWF<br>OVLW                                                                                                                          | READ_BLOCK<br>DATA_ADDR_HIGH<br>FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                                                                                                                                                                        | ;                                       | repeat<br>point to buffer                                                                                                                                                                                                        |

| MODIFY_WORD<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>ERASE_BLOCK                                                                                    | OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVWF<br>OVWF<br>OVLW                                                                                                                        | DATA_ADDR_HIGH<br>FSR0H<br>DATA_ADDR_LOW<br>FSR0L<br>NEW_DATA_LOW<br>POSTINC0                                                                                                                                                                                                                      | ;                                       | point to buffer                                                                                                                                                                                                                  |

| ERASE_BLOCK                                                                                                                                       | OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW                                                                                                                                | FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                                                                                                                                                                                                        |                                         | -                                                                                                                                                                                                                                |

| MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>MC<br>ERASE_BLOCK                                                                                             | OVWF<br>OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW                                                                                                                                | FSROH<br>DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                                                                                                                                                                                                        |                                         | -                                                                                                                                                                                                                                |

| MC<br>MC<br>MC<br>MC<br>MC<br>ERASE_BLOCK                                                                                                         | OVLW<br>OVWF<br>OVLW<br>OVWF<br>OVLW                                                                                                                                        | DATA_ADDR_LOW<br>FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                                                                                                                                                                                                                 | ;                                       | update buffer word                                                                                                                                                                                                               |

| MC<br>MC<br>MC<br>ERASE_BLOCK                                                                                                                     | OVWF<br>OVLW<br>OVWF<br>OVLW                                                                                                                                                | FSROL<br>NEW_DATA_LOW<br>POSTINCO                                                                                                                                                                                                                                                                  | ;                                       | update buffer word                                                                                                                                                                                                               |

| MC<br>MC<br>ERASE_BLOCK                                                                                                                           | OVWF<br>OVLW                                                                                                                                                                | POSTINCO                                                                                                                                                                                                                                                                                           | ;                                       | update buffer word                                                                                                                                                                                                               |

| MC<br>MC<br>ERASE_BLOCK                                                                                                                           | OVWF<br>OVLW                                                                                                                                                                | POSTINCO                                                                                                                                                                                                                                                                                           |                                         |                                                                                                                                                                                                                                  |

| MC<br>ERASE_BLOCK                                                                                                                                 |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                    |                                         |                                                                                                                                                                                                                                  |

| ERASE_BLOCK                                                                                                                                       | OVWF                                                                                                                                                                        | NEW DATA HIGH                                                                                                                                                                                                                                                                                      |                                         |                                                                                                                                                                                                                                  |

|                                                                                                                                                   | 0111                                                                                                                                                                        | INDF0                                                                                                                                                                                                                                                                                              |                                         |                                                                                                                                                                                                                                  |

| MC                                                                                                                                                |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                    |                                         |                                                                                                                                                                                                                                  |

|                                                                                                                                                   | OVLW                                                                                                                                                                        | CODE_ADDR_UPPER                                                                                                                                                                                                                                                                                    | ;                                       | load TBLPTR with the base                                                                                                                                                                                                        |

| MC                                                                                                                                                | OVWF                                                                                                                                                                        | TBLPTRU                                                                                                                                                                                                                                                                                            | ;                                       | address of the memory block                                                                                                                                                                                                      |

| MC                                                                                                                                                | OVLW                                                                                                                                                                        | CODE_ADDR_HIGH                                                                                                                                                                                                                                                                                     |                                         |                                                                                                                                                                                                                                  |

| MC                                                                                                                                                | OVWF                                                                                                                                                                        | TBLPTRH                                                                                                                                                                                                                                                                                            |                                         |                                                                                                                                                                                                                                  |

| MC                                                                                                                                                | OVLW                                                                                                                                                                        | CODE_ADDR_LOW                                                                                                                                                                                                                                                                                      |                                         |                                                                                                                                                                                                                                  |

| MC                                                                                                                                                | OVWF                                                                                                                                                                        | TBLPTRL                                                                                                                                                                                                                                                                                            |                                         |                                                                                                                                                                                                                                  |

| BS                                                                                                                                                |                                                                                                                                                                             | EECON1, EEPGD                                                                                                                                                                                                                                                                                      | ;                                       | point to Flash program memory                                                                                                                                                                                                    |

|                                                                                                                                                   |                                                                                                                                                                             | EECON1, CFGS                                                                                                                                                                                                                                                                                       |                                         | access Flash program memory                                                                                                                                                                                                      |

|                                                                                                                                                   |                                                                                                                                                                             | EECON1, WREN                                                                                                                                                                                                                                                                                       |                                         | enable write to memory                                                                                                                                                                                                           |

|                                                                                                                                                   |                                                                                                                                                                             | EECON1, FREE                                                                                                                                                                                                                                                                                       |                                         | enable Row Erase operation                                                                                                                                                                                                       |

|                                                                                                                                                   |                                                                                                                                                                             | INTCON, GIE                                                                                                                                                                                                                                                                                        | ;                                       | disable interrupts                                                                                                                                                                                                               |

|                                                                                                                                                   |                                                                                                                                                                             | 55h                                                                                                                                                                                                                                                                                                |                                         |                                                                                                                                                                                                                                  |

| -                                                                                                                                                 |                                                                                                                                                                             | EECON2                                                                                                                                                                                                                                                                                             | ;                                       | write 55h                                                                                                                                                                                                                        |

| -                                                                                                                                                 |                                                                                                                                                                             | 0AAh                                                                                                                                                                                                                                                                                               |                                         | wite ozzh                                                                                                                                                                                                                        |

|                                                                                                                                                   |                                                                                                                                                                             | EECON2                                                                                                                                                                                                                                                                                             |                                         | write 0AAh                                                                                                                                                                                                                       |

|                                                                                                                                                   |                                                                                                                                                                             | EECON1, WR                                                                                                                                                                                                                                                                                         |                                         | start erase (CPU stall)                                                                                                                                                                                                          |

|                                                                                                                                                   | SF<br>BLRD*-                                                                                                                                                                | INTCON, GIE                                                                                                                                                                                                                                                                                        |                                         | re-enable interrupts<br>dummy read decrement                                                                                                                                                                                     |

|                                                                                                                                                   |                                                                                                                                                                             | BUFFER ADDR HIGH                                                                                                                                                                                                                                                                                   |                                         | point to buffer                                                                                                                                                                                                                  |

|                                                                                                                                                   |                                                                                                                                                                             | FSROH                                                                                                                                                                                                                                                                                              | '                                       | Point to built                                                                                                                                                                                                                   |

|                                                                                                                                                   |                                                                                                                                                                             | BUFFER ADDR LOW                                                                                                                                                                                                                                                                                    |                                         |                                                                                                                                                                                                                                  |

|                                                                                                                                                   |                                                                                                                                                                             | FSROL                                                                                                                                                                                                                                                                                              |                                         |                                                                                                                                                                                                                                  |

| WRITE BUFFER BACK                                                                                                                                 |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                    |                                         |                                                                                                                                                                                                                                  |

|                                                                                                                                                   |                                                                                                                                                                             | D'32                                                                                                                                                                                                                                                                                               | ;                                       | number of bytes in holding register                                                                                                                                                                                              |

|                                                                                                                                                   |                                                                                                                                                                             | COUNTER                                                                                                                                                                                                                                                                                            | ,                                       |                                                                                                                                                                                                                                  |

| WRITE BYTE TO HRE                                                                                                                                 |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                    |                                         |                                                                                                                                                                                                                                  |

|                                                                                                                                                   |                                                                                                                                                                             | POSTINCO, WREG                                                                                                                                                                                                                                                                                     | ;                                       | get low byte of buffer data                                                                                                                                                                                                      |

|                                                                                                                                                   |                                                                                                                                                                             | TABLAT                                                                                                                                                                                                                                                                                             |                                         | present data to table latch                                                                                                                                                                                                      |

|                                                                                                                                                   | BLWT+*                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                    |                                         | write data, perform a short write                                                                                                                                                                                                |

|                                                                                                                                                   |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                    |                                         | to internal TBLWT holding register.                                                                                                                                                                                              |

| DE                                                                                                                                                | ECFSZ                                                                                                                                                                       | COUNTER                                                                                                                                                                                                                                                                                            |                                         | loop until buffers are full                                                                                                                                                                                                      |

| BR                                                                                                                                                | RA                                                                                                                                                                          | WRITE_WORD_TO_HREGS                                                                                                                                                                                                                                                                                |                                         |                                                                                                                                                                                                                                  |

| EXAMPLE 6-3:   | WR    | TING TO | FLASH PR | 00 | GRAM MEMORY (CONTINUED)       |

|----------------|-------|---------|----------|----|-------------------------------|

| PROGRAM_MEMORY |       |         |          |    |                               |

|                | BSF   | EECON1, | EEPGD    | ;  | point to Flash program memory |

|                | BCF   | EECON1, | CFGS     | ;  | access Flash program memory   |

|                | BSF   | EECON1, | WREN     | ;  | enable write to memory        |

|                | BCF   | INTCON, | GIE      | ;  | disable interrupts            |

|                | MOVLW | 55h     |          |    |                               |

| Required       | MOVWF | EECON2  |          | ;  | write 55h                     |

| Sequence       | MOVLW | 0AAh    |          |    |                               |

|                | MOVWF | EECON2  |          | ;  | write OAAh                    |

|                | BSF   | EECON1, | WR       | ;  | start program (CPU stall)     |

|                | BSF   | INTCON, | GIE      | ;  | re-enable interrupts          |

|                | BCF   | EECON1, | WREN     | ;  | disable write to memory       |

#### 6.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

### 6.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. If the write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

#### 6.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See **Section 23.0** "**Special Features of the CPU**" for more detail.

#### 6.6 Flash Program Operation During Code Protection

See Section 23.5 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| Name    | Bit 7                                                              | Bit 6                                                 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values on<br>page |  |  |

|---------|--------------------------------------------------------------------|-------------------------------------------------------|-------|-------|-------|--------|--------|--------|----------------------------|--|--|

| TBLPTRU | — — bit 21 Program Memory Table Pointer Upper Byte (TBLPTR<20:16>) |                                                       |       |       |       |        |        |        |                            |  |  |

| TBLPTRH | Program M                                                          | Program Memory Table Pointer High Byte (TBLPTR<15:8>) |       |       |       |        |        |        |                            |  |  |

| TBLPTRL | Program Memory Table Pointer Low Byte (TBLPTR<7:0>)                |                                                       |       |       |       |        |        |        |                            |  |  |

| TABLAT  | Program Memory Table Latch                                         |                                                       |       |       |       |        |        |        |                            |  |  |

| INTCON  | GIE/GIEH PEIE/GIEL TMROIE INTOIE RBIE TMROIF INTOIF RBIF           |                                                       |       |       |       |        |        |        |                            |  |  |

| EECON2  | EEPROM Control Register 2 (not a physical register)                |                                                       |       |       |       |        |        |        |                            |  |  |

| EECON1  | EEPGD                                                              | CFGS                                                  | _     | FREE  | WRERR | WREN   | WR     | RD     | 51                         |  |  |

| IPR2    | OSCFIP                                                             | CMIP                                                  | _     | EEIP  | BCLIP | HLVDIP | TMR3IP | CCP2IP | 52                         |  |  |

| PIR2    | OSCFIF                                                             | CMIF                                                  | _     | EEIF  | BCLIF | HLVDIF | TMR3IF | CCP2IF | 52                         |  |  |

| PIE2    | OSCFIE                                                             | CMIE                                                  | _     | EEIE  | BCLIE | HLVDIE | TMR3IE | CCP2IE | 52                         |  |  |

#### TABLE 6-2: REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

NOTES:

#### 9.2 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Request Flag registers (PIR1 and PIR2).

- Note 1: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>).

- 2: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt and after servicing that interrupt.

#### REGISTER 9-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

| R/W-0                | R/W-0 | R-0  | R-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|------|------|-------|--------|--------|--------|

| PSPIF <sup>(1)</sup> | ADIF  | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| bit 7                |       |      |      |       |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

|                   |                  |                       |                    |

. .. (1)

. ---

| bit 7 | PSPIF: Parallel Slave Port Read/Write Interrupt Flag bit <sup>(1)</sup>                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = A read or a write operation has taken place (must be cleared in software)</li> <li>0 = No read or write has occurred</li> </ul>                                |

| bit 6 | ADIF: A/D Converter Interrupt Flag bit                                                                                                                                      |

|       | <ul> <li>1 = An A/D conversion completed (must be cleared in software)</li> <li>0 = The A/D conversion is not complete</li> </ul>                                           |

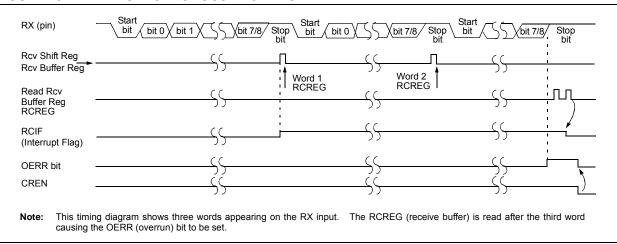

| bit 5 | RCIF: EUSART Receive Interrupt Flag bit                                                                                                                                     |

|       | <ul> <li>1 = The EUSART receive buffer, RCREG, is full (cleared when RCREG is read)</li> <li>0 = The EUSART receive buffer is empty</li> </ul>                              |

| bit 4 | TXIF: EUSART Transmit Interrupt Flag bit                                                                                                                                    |

|       | <ul> <li>1 = The EUSART transmit buffer, TXREG, is empty (cleared when TXREG is written)</li> <li>0 = The EUSART transmit buffer is full</li> </ul>                         |

| bit 3 | SSPIF: Master Synchronous Serial Port Interrupt Flag bit                                                                                                                    |

|       | <ul> <li>1 = The transmission/reception is complete (must be cleared in software)</li> <li>0 = Waiting to transmit/receive</li> </ul>                                       |

| bit 2 | CCP1IF: CCP1 Interrupt Flag bit                                                                                                                                             |

|       | <u>Capture mode:</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred                                         |

|       | Compare mode:                                                                                                                                                               |