Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2420t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.2 Other Special Features

- **Memory Endurance:** The Enhanced Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles – up to 100,000 for program memory and 1,000,000 for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

- Self-Programmability: These devices can write to their own program memory spaces under internal software control. By using a bootloader routine located in the protected Boot Block at the top of program memory, it becomes possible to create an application that can update itself in the field.

- Extended Instruction Set: The PIC18F2420/ 2520/4420/4520 family introduces an optional extension to the PIC18 instruction set, which adds 8 new instructions and an Indexed Addressing mode. This extension, enabled as a device configuration option, has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as C.

- Enhanced CCP Module: In PWM mode, this module provides 1, 2 or 4 modulated outputs for controlling half-bridge and full-bridge drivers. Other features include auto-shutdown, for disabling PWM outputs on interrupt, or other select conditions, and auto-restart to reactivate outputs once the condition has cleared.

- Enhanced Addressable USART: This serial communication module is capable of standard RS-232 operation and provides support for the LIN bus protocol. Other enhancements include automatic baud rate detection and a 16-bit Baud Rate Generator for improved resolution. When the microcontroller is using the internal oscillator block, the EUSART provides stable operation for applications that talk to the outside world without using an external crystal (or its accompanying power requirement).

- **10-Bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reducing code overhead.

- Extended Watchdog Timer (WDT): This enhanced version incorporates a 16-bit prescaler, allowing an extended time-out range that is stable across operating voltage and temperature. See Section 26.0 "Electrical Characteristics" for time-out periods.

### 1.3 Details on Individual Family Members

Devices in the PIC18F2420/2520/4420/4520 family are available in 28-pin and 40/44-pin packages. Block diagrams for the two groups are shown in Figure 1-1 and Figure 1-2.

The devices are differentiated from each other in five ways:

- 1. Flash program memory (16 Kbytes for PIC18F2420/4420 devices and 32 Kbytes for PIC18F2520/4520 devices).

- A/D channels (10 for 28-pin devices, 13 for 40/44-pin devices).

- 3. I/O ports (3 bidirectional ports on 28-pin devices, 5 bidirectional ports on 40/44-pin devices).

- CCP and Enhanced CCP implementation (28-pin devices have 2 standard CCP modules, 40/44-pin devices have one standard CCP module and one ECCP module).

- 5. Parallel Slave Port (present only on 40/44-pin devices).

All other features for devices in this family are identical. These are summarized in Table 1-1.

The pinouts for all devices are listed in Table 1-2 and Table 1-3.

Like all Microchip PIC18 devices, members of the PIC18F2420/2520/4420/4520 family are available as both standard and low-voltage devices. Standard devices with Enhanced Flash memory, designated with an "F" in the part number (such as PIC18F2420), accommodate an operating VDD range of 4.2V to 5.5V. Low-voltage parts, designated by "LF" (such as PIC18LF2420), function over an extended VDD range of 2.0V to 5.5V.

NOTES:

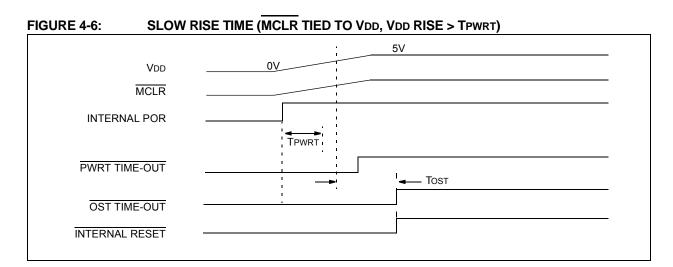

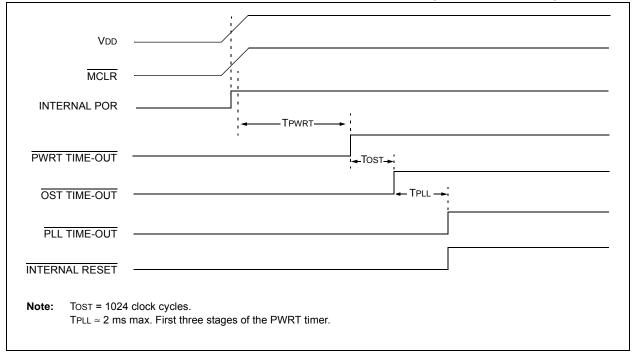

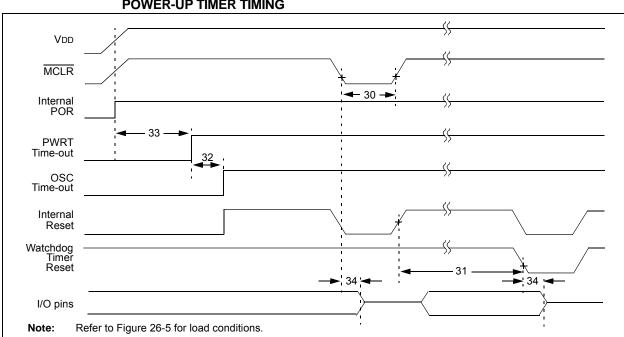

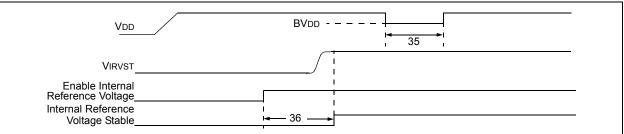

#### FIGURE 4-7: TIME-OUT SEQUENCE ON POR W/PLL ENABLED (MCLR TIED TO VDD)

The PLUSW register can be used to implement a form of Indexed Addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

#### 5.4.3.3 Operations by FSRs on FSRs

Indirect Addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contains FE7h, the address of INDF1. Attempts to read the value of the INDF1 using INDF0 as an operand will return 00h. Attempts to write to INDF1 using INDF0 as the operand will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to INDF2 or POSTDEC2 will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses indirect addressing.

Similarly, operations by Indirect Addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

# 5.5 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different; this is due to the introduction of a new addressing mode for the data memory space.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect Addressing with FSR0 and FSR1 also remains unchanged.

### 5.5.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of Indirect Addressing using the FSR2 register pair within Access RAM. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of Indexed Addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset, or Indexed Literal Offset mode.

When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0) and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in direct addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer, specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

### 5.5.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use Direct Addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they do not use the Access Bank (Access RAM bit is '1'), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled in shown in Figure 5-9.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 24.2.1** "Extended Instruction Syntax".

NOTES:

#### 10.5 PORTE, TRISE and LATE Registers

Depending on the particular PIC18F2420/2520/4420/ 4520 device selected, PORTE is implemented in two different ways.

For 40/44-pin devices, PORTE is a 4-bit wide port. Three pins (RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/ AN7) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as an analog input, these pins will read as '0's.

The corresponding Data Direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

| Note: | On a |      | Power-on    | Reset,   | RE<2:0> | are |

|-------|------|------|-------------|----------|---------|-----|

|       | cont | figu | red as anal | og input | 5.      |     |

The upper four bits of the TRISE register also control the operation of the Parallel Slave Port. Their operation is explained in Register 10-1.

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register, read and write the latched output value for PORTE.

The fourth pin of PORTE ( $\overline{\text{MCLR}}/\text{VPP}/\text{RE3}$ ) is an input only pin. Its operation is controlled by the MCLRE Configuration bit. When selected as a port pin (MCLRE = 0), it functions as a digital input only pin; as such, it does not have TRIS or LAT bits associated with its operation. Otherwise, it functions as the device's Master Clear input. In either configuration, RE3 also functions as the programming voltage input during programming.

| Note: | On a Power-on Reset, RE3 is enabled as |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|

|       | a digital input only if Master Clear   |  |  |  |  |  |

|       | functionality is disabled.             |  |  |  |  |  |

#### EXAMPLE 10-5: INITIALIZING PORTE

| CLRF  | PORTE  | ; | Initialize PORTE by |

|-------|--------|---|---------------------|

|       |        | ; | clearing output     |

|       |        | ; | data latches        |

| CLRF  | LATE   | ; | Alternate method    |

|       |        | ; | to clear output     |

|       |        | ; | data latches        |

| MOVLW | 0Ah    | ; | Configure A/D       |

| MOVWF | ADCON1 | ; | for digital inputs  |

| MOVLW | 03h    | ; | Value used to       |

|       |        | ; | initialize data     |

|       |        | ; | direction           |

| MOVWF | TRISE  | ; | Set RE<0> as inputs |

|       |        | ; | RE<1> as outputs    |

|       |        | ; | RE<2> as inputs     |

|       |        |   |                     |

### 10.5.1 PORTE IN 28-PIN DEVICES

For 28-pin devices, PORTE is only available when Master Clear functionality is disabled (MCLRE = 0). In these cases, PORTE is a single bit, input only port comprised of RE3 only. The pin operates as previously described.

NOTES:

#### EXAMPLE 18-1: CALCULATING BAUD RATE ERROR

| l | For a device with Fost | c of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG: |

|---|------------------------|-----------------------------------------------------------------------|

| l | Desired Baud Rate      | = Fosc/(64 ([SPBRGH:SPBRG] + 1))                                      |

| l | Solving for SPBRGH:    | SPBRG:                                                                |

| l | Х                      | = ((Fosc/Desired Baud Rate)/64) – 1                                   |

| l |                        | = ((1600000/9600)/64) - 1                                             |

| l |                        | = [25.042] = 25                                                       |

| l | Calculated Baud Rate   | = 1600000/(64 (25 + 1))                                               |

| l |                        | = 9615                                                                |

| l | Error                  | = (Calculated Baud Rate – Desired Baud Rate)/Desired Baud Rate        |

| l |                        | = (9615 - 9600)/9600 = 0.16%                                          |

| н |                        |                                                                       |

#### TABLE 18-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name    | Bit 7                                         | Bit 6                                           | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset Values<br>on page |

|---------|-----------------------------------------------|-------------------------------------------------|-------|-------|-------|-------|-------|-------|-------------------------|

| TXSTA   | CSRC                                          | TX9                                             | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 51                      |

| RCSTA   | SPEN                                          | RX9                                             | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 51                      |

| BAUDCON | ABDOVF                                        | RCIDL                                           | RXDTP | TXCKP | BRG16 | —     | WUE   | ABDEN | 51                      |

| SPBRGH  | EUSART Baud Rate Generator Register High Byte |                                                 |       |       |       |       | 51    |       |                         |

| SPBRG   | EUSART E                                      | EUSART Baud Rate Generator Register Low Byte 51 |       |       |       |       |       |       |                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the BRG.

### 19.6 A/D Conversions

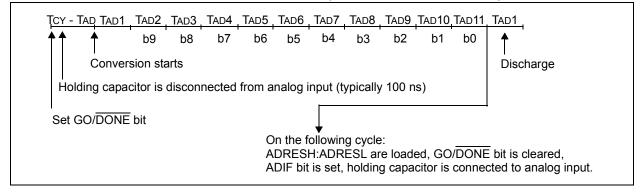

Figure 19-4 shows the operation of the A/D Converter after the GO/DONE bit has been set and the ACQT<2:0> bits are cleared. A conversion is started after the following instruction to allow entry into Sleep mode before the conversion begins.

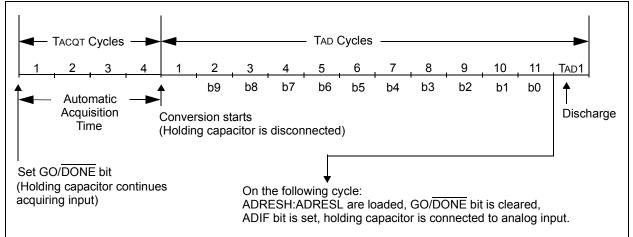

Figure 19-5 shows the operation of the A/D Converter after the GO/DONE bit has been set and the ACQT<2:0> bits are set to '010', and selecting a 4 TAD acquisition time before the conversion starts.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. This means the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is completed or aborted, a 2 TAD wait is required before the next acquisition can be started. After this wait, acquisition on the selected channel is automatically started.

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

#### 19.7 Discharge

The discharge phase is used to initialize the value of the capacitor array. The array is discharged before every sample. This feature helps to optimize the unitygain amplifier, as the circuit always needs to charge the capacitor array, rather than charge/discharge based on previous measure values.

#### FIGURE 19-4: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

#### FIGURE 19-5: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

| REGISTER 23-4: CON | NFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h) |

|--------------------|--------------------------------------------------------------|

|--------------------|--------------------------------------------------------------|

| R/P-1          | U-0                                             | U-0               | U-0            | U-0          | R/P-0            | R/P-1      | R/P-1  |

|----------------|-------------------------------------------------|-------------------|----------------|--------------|------------------|------------|--------|

| MCLRE          | —                                               | —                 | _              | _            | LPT1OSC          | PBADEN     | CCP2MX |

| bit 7          | •                                               |                   |                |              |                  |            | bit 0  |

|                |                                                 |                   |                |              |                  |            |        |

| Legend:        |                                                 |                   |                |              |                  |            |        |

| R = Readable b | bit                                             | P = Programm      | nable bit      | U = Unimpler | mented bit, read | as '0'     |        |

| -n = Value whe | n device is unp                                 | programmed        |                | u = Unchang  | ed from progran  | nmed state |        |

|                |                                                 |                   |                |              |                  |            |        |

| bit 7          | MCLRE: MCL                                      | R Pin Enable      | bit            |              |                  |            |        |

|                | $1 = \overline{MCLR}$ pin                       | enabled; RE3      | input pin disa | bled         |                  |            |        |

|                | 0 = RE3 input                                   | pin enabled; N    | ICLR disable   | d            |                  |            |        |

| bit 6-3        | Unimplement                                     | ted: Read as '    | o'             |              |                  |            |        |

| bit 2          | LPT1OSC: Low-Power Timer1 Oscillator Enable bit |                   |                |              |                  |            |        |

|                |                                                 | onfigured for lov |                |              |                  |            |        |

|                | 0 = Timer1 co                                   | onfigured for hig | gher power op  | eration      |                  |            |        |

| bit 1          | /                                               | RTB A/D Enat      |                |              |                  |            |        |

|                | •                                               |                   |                |              | B<4:0> pin confi | •          |        |

|                |                                                 | •                 | •              | • •          | annels on Rese   | t          |        |

| <b>h</b> # 0   |                                                 | 1:0> pins are co  | Singuleu as u  |              | esei             |            |        |

| bit 0          | CCP2MX: CC                                      |                   |                | 504          |                  |            |        |

|                |                                                 | ut/output is mu   |                |              |                  |            |        |

|                | $0 = CCP2 \ln p$                                | ut/output is mu   | inplexed with  | RDJ          |                  |            |        |

## REGISTER 23-5: CONFIG4L: CONFIGURATION REGISTER 4 LOW (BYTE ADDRESS 300006h)

| R/P-1 | R/P-0 | U-0 | U-0 | U-0 | R/P-1 | U-0 | R/P-1  |

|-------|-------|-----|-----|-----|-------|-----|--------|

| DEBUG | XINST | —   | _   | _   | LVP   | _   | STVREN |

| bit 7 |       |     |     |     |       |     | bit 0  |

| Legend:                                |                      |                                     |

|----------------------------------------|----------------------|-------------------------------------|

| R = Readable bit                       | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device is unprogrammed |                      | u = Unchanged from programmed state |

|                                        |                      |                                     |

| DEBUG: Background Debugger Enable bit                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1 = Background debugger disabled, RB6 and RB7 configured as general purpose I/O pins</li> <li>0 = Background debugger enabled, RB6 and RB7 are dedicated to In-Circuit Debug</li> </ul> |

| XINST: Extended Instruction Set Enable bit                                                                                                                                                       |

| <ul> <li>1 = Instruction set extension and Indexed Addressing mode enabled</li> <li>0 = Instruction set extension and Indexed Addressing mode disabled (Legacy mode)</li> </ul>                  |

| Unimplemented: Read as '0'                                                                                                                                                                       |

| LVP: Single-Supply ICSP™ Enable bit                                                                                                                                                              |

| <ul><li>1 = Single-Supply ICSP enabled</li><li>0 = Single-Supply ICSP disabled</li></ul>                                                                                                         |

| Unimplemented: Read as '0'                                                                                                                                                                       |

| STVREN: Stack Full/Underflow Reset Enable bit                                                                                                                                                    |

| 1 = Stack full/underflow will cause Reset                                                                                                                                                        |

| 0 = Stack full/underflow will not cause Reset                                                                                                                                                    |

|                                                                                                                                                                                                  |

#### 23.5.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits internal and external writes to data EEPROM. The CPU can always read data EEPROM under normal operation, regardless of the protection bit settings.

#### 23.5.3 CONFIGURATION REGISTER PROTECTION

The Configuration registers can be write-protected. The WRTC bit controls protection of the Configuration registers. In normal execution mode, the WRTC bit is read-only. WRTC can only be written via ICSP or an external programmer.

### 23.6 ID Locations

Eight memory locations (20000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are both readable and writable during normal execution through the TBLRD and TBLWT instructions, or during program/verify. The ID locations can be read when the device is code-protected.

## 23.7 In-Circuit Serial Programming

PIC18F2420/2520/4420/4520 devices can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

### 23.8 In-Circuit Debugger

When the DEBUG Configuration bit is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some resources are not available for general use. Table 23-4 shows which resources are required by the background debugger.

| I/O pins:       | RB6, RB7  |

|-----------------|-----------|

| Stack:          | 2 levels  |

| Program Memory: | 512 bytes |

| Data Memory:    | 10 bytes  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP/RE3, VDD, Vss, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip or one of the third party development tool companies.

## 23.9 Single-Supply ICSP Programming

The LVP Configuration bit enables Single-Supply ICSP Programming (formerly known as Low-Voltage ICSP Programming or LVP). When Single-Supply Programming is enabled, the microcontroller can be programmed without requiring high voltage being applied to the MCLR/VPP/RE3 pin, but the RB5/KBI1/PGM pin is then dedicated to controlling Program mode entry and is not available as a general purpose I/O pin.

While programming, using Single-Supply Programming mode, VDD is applied to the MCLR/VPP/RE3 pin as in normal execution mode. To enter Programming mode, VDD is applied to the PGM pin.

- Note 1: High-voltage programming is always available, regardless of the state of the LVP bit or the PGM pin, by applying VIHH to the MCLR pin.

- 2: By default, Single-Supply ICSP is enabled in unprogrammed devices (as supplied from Microchip) and erased devices.

- **3:** When Single-Supply Programming is enabled, the RB5 pin can no longer be used as a general purpose I/O pin.

- 4: When LVP is enabled, externally pull the PGM pin to Vss to allow normal program execution.

If Single-Supply ICSP Programming mode will not be used, the LVP bit can be cleared. RB5/KBI1/PGM then becomes available as the digital I/O pin, RB5. The LVP bit may be set or cleared only when using standard high-voltage programming (VIHH applied to the MCLR/ VPP/RE3 pin). Once LVP has been disabled, only the standard high-voltage programming is available and must be used to program the device.

Memory that is not code-protected can be erased using either a block erase, or erased row by row, then written at any specified VDD. If code-protected memory is to be erased, a block erase is required. If a block erase is to be performed when using Low-Voltage Programming, the device must be supplied with VDD of 4.5V to 5.5V.

# 24.0 INSTRUCTION SET SUMMARY

PIC18F2420/2520/4420/4520 devices incorporate the standard set of 75 PIC18 core instructions, as well as an extended set of 8 new instructions, for the optimization of code that is recursive or that utilizes a software stack. The extended set is discussed later in this section.

### 24.1 Standard Instruction Set

The standard PIC18 instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from these PIC MCU instruction sets. Most instructions are a single program memory word (16 bits), but there are four instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- · Byte-oriented operations

- **Bit-oriented** operations

- · Literal operations

- Control operations

The PIC18 instruction set summary in Table 24-2 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 24-1 shows the opcode field descriptions.

Most byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator 'f' specifies which file register is to be used by the instruction. The destination designator 'd' specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All bit-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator 'b' selects the number of the bit affected by the operation, while the file register designator 'f' represents the number of the file in which the bit is located. The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the CALL or RETURN instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for four double-word instructions. These instructions were made double-word to contain the required information in 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 24-1 shows the general formats that the instructions can have. All examples use the convention 'nnh' to represent a hexadecimal number.

The Instruction Set Summary, shown in Table 24-2, lists the standard instructions recognized by the Microchip Assembler (MPASM<sup>TM</sup>).

Section 24.1.1 "Standard Instruction Set" provides a description of each instruction.

#### TABLE 24-2: PIC18FXXXX INSTRUCTION SET

| Mnemo    | onic.                           |                                          |            | 16-Bit Instruction Word |      |      |      | Status           |            |

|----------|---------------------------------|------------------------------------------|------------|-------------------------|------|------|------|------------------|------------|

| Opera    | •                               | Description                              | Cycles     | MSb                     |      |      | LSb  | Affected         | Notes      |

| BYTE-ORI | ENTED (                         | OPERATIONS                               |            |                         |      |      |      |                  |            |

| ADDWF    | f, d, a                         | Add WREG and f                           | 1          | 0010                    | 01da | ffff | ffff | C, DC, Z, OV, N  | 1, 2       |

| ADDWFC   | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010                    | 00da | ffff | ffff | C, DC, Z, OV, N  | 1, 2       |

| ANDWF    | f, d, a                         | AND WREG with f                          | 1          | 0001                    | 01da | ffff | ffff | Z, N             | 1,2        |

| CLRF     | f, a                            | Clear f                                  | 1          | 0110                    | 101a | ffff | ffff | Z                | 2          |

| COMF     | f, d, a                         | Complement f                             | 1          | 0001                    | 11da | ffff | ffff | Z, N             | 1, 2       |

| CPFSEQ   | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110                    | 001a | ffff | ffff | None             | 4          |

| CPFSGT   | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110                    | 010a | ffff | ffff | None             | 4          |

| CPFSLT   | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110                    | 000a | ffff | ffff | None             | 1, 2       |

| DECF     | f, d, a                         | Decrement f                              | 1          | 0000                    | 01da | ffff | ffff | C, DC, Z, OV, N  | 1, 2, 3, 4 |

| DECFSZ   | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010                    | 11da | ffff | ffff | None             | 1, 2, 3, 4 |

| DCFSNZ   | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 11da | ffff | ffff | None             | 1, 2       |

| INCF     | f, d, a                         | Increment f                              | 1          | 0010                    | 10da | ffff | ffff | C, DC, Z, OV, N  | 1, 2, 3, 4 |

| INCFSZ   | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011                    | 11da | ffff | ffff | None             | 4          |

| INFSNZ   | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 10da | ffff | ffff | None             | 1, 2       |

| IORWF    | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001                    | 00da | ffff | ffff | Z, N             | 1, 2       |

| MOVF     | f, d, a                         | Move f                                   | 1          | 0101                    | 00da | ffff | ffff | Z, N             | 1          |

| MOVFF    | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100                    | ffff | ffff | ffff | None             |            |

|          | 0 u                             | f <sub>d</sub> (destination) 2nd word    |            | 1111                    | ffff | ffff | ffff |                  |            |

| MOVWF    | f, a                            | Move WREG to f                           | 1          | 0110                    | 111a | ffff | ffff | None             |            |

| MULWF    | f, a                            | Multiply WREG with f                     | 1          | 0000                    | 001a | ffff | ffff | None             | 1, 2       |

| NEGF     | f, a                            | Negate f                                 | 1          | 0110                    | 110a | ffff | ffff | C, DC, Z, OV, N  |            |

| RLCF     | f, d, a                         | Rotate Left f through Carry              | 1          | 0011                    | 01da | ffff | ffff | C, Z, N          | 1, 2       |

| RLNCF    | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100                    | 01da | ffff | ffff | Z, N             |            |

| RRCF     | f, d, a                         | Rotate Right f through Carry             | 1          | 0011                    | 00da | ffff | ffff | C, Z, N          |            |

| RRNCF    | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100                    | 00da | ffff | ffff | Z, N             |            |

| SETF     | f, a                            | Set f                                    | 1          | 0110                    | 100a | ffff | ffff | None             | 1, 2       |

| SUBFWB   | f, d, a                         | Subtract f from WREG with<br>Borrow      | 1          | 0101                    | 01da | ffff | ffff | C, DC, Z, OV, N  |            |

| SUBWF    | f, d, a                         | Subtract WREG from f                     | 1          | 0101                    | 11da | ffff | ffff | C, DC, Z, OV, N  | 1, 2       |

| SUBWFB   | f, d, a                         | Subtract WREG from f with                | 1          | 0101                    | 10da | ffff | ffff | C, DC, Z, OV, N  | · ·        |

|          | , . , .                         | Borrow                                   |            |                         |      |      |      | , _, , _ , _ , _ |            |

| SWAPF    | f, d, a                         | Swap Nibbles in f                        | 1          | 0011                    | 10da | ffff | ffff | None             | 4          |

| TSTFSZ   | f, a                            | Test f, Skip if 0                        | 1 (2 or 3) | 0110                    | 011a | ffff | ffff | None             | 1, 2       |

| XORWF    | f, d, a                         | Exclusive OR WREG with f                 | 1          | 0001                    | 10da | ffff | ffff | Z, N             | l í        |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| Mnemo     | onic,  | Description                     | Cycles | 16-Bit Instruction Word |      |      |      | Status          | Notes |

|-----------|--------|---------------------------------|--------|-------------------------|------|------|------|-----------------|-------|

| Operands  |        | Description                     | Cycles | MSb                     |      | LSb  |      | Affected        | Notes |

| LITERAL C | OPERAT | TIONS                           |        |                         |      |      |      |                 |       |

| ADDLW     | k      | Add Literal and WREG            | 1      | 0000                    | 1111 | kkkk | kkkk | C, DC, Z, OV, N |       |

| ANDLW     | k      | AND Literal with WREG           | 1      | 0000                    | 1011 | kkkk | kkkk | Z, N            |       |

| IORLW     | k      | Inclusive OR Literal with WREG  | 1      | 0000                    | 1001 | kkkk | kkkk | Z, N            |       |

| LFSR      | f, k   | Move Literal (12-bit)2nd word   | 2      | 1110                    | 1110 | 00ff | kkkk | None            |       |

|           |        | to FSR(f) 1st word              |        | 1111                    | 0000 | kkkk | kkkk |                 |       |

| MOVLB     | k      | Move Literal to BSR<3:0>        | 1      | 0000                    | 0001 | 0000 | kkkk | None            |       |

| MOVLW     | k      | Move Literal to WREG            | 1      | 0000                    | 1110 | kkkk | kkkk | None            |       |

| MULLW     | k      | Multiply Literal with WREG      | 1      | 0000                    | 1101 | kkkk | kkkk | None            |       |

| RETLW     | k      | Return with Literal in WREG     | 2      | 0000                    | 1100 | kkkk | kkkk | None            |       |

| SUBLW     | k      | Subtract WREG from Literal      | 1      | 0000                    | 1000 | kkkk | kkkk | C, DC, Z, OV, N |       |

| XORLW     | k      | Exclusive OR Literal with WREG  | 1      | 0000                    | 1010 | kkkk | kkkk | Z, N            |       |

| DATA MEN  | IORY ← | PROGRAM MEMORY OPERATION        | NS     |                         |      |      |      |                 |       |

| TBLRD*    |        | Table Read                      | 2      | 0000                    | 0000 | 0000 | 1000 | None            |       |

| TBLRD*+   |        | Table Read with Post-Increment  |        | 0000                    | 0000 | 0000 | 1001 | None            |       |

| TBLRD*-   |        | Table Read with Post-Decrement  |        | 0000                    | 0000 | 0000 | 1010 | None            |       |

| TBLRD+*   |        | Table Read with Pre-Increment   |        | 0000                    | 0000 | 0000 | 1011 | None            |       |

| TBLWT*    |        | Table Write                     | 2      | 0000                    | 0000 | 0000 | 1100 | None            |       |

| TBLWT*+   |        | Table Write with Post-Increment |        | 0000                    | 0000 | 0000 | 1101 | None            |       |

| TBLWT*-   |        | Table Write with Post-Decrement |        | 0000                    | 0000 | 0000 | 1110 | None            |       |

| TBLWT+*   |        | Table Write with Pre-Increment  |        | 0000                    | 0000 | 0000 | 1111 | None            |       |

#### TABLE 24-2: PIC18FXXXX INSTRUCTION SET (CONTINUED)

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| ADDWFC                        | ADD W a                                                                                                                                      | ADD W and Carry bit to f                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |  |  |  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|--|--|

| Syntax:                       | ADDWFC                                                                                                                                       | f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |  |  |  |  |  |  |

| Operands:                     | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                          | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |  |  |  |  |  |  |

| Operation:                    | (W) + (f) +                                                                                                                                  | $(C) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |  |  |  |  |  |  |

| Status Affected:              | N,OV, C, D                                                                                                                                   | C, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      |  |  |  |  |  |  |

| Encoding:                     | 0010                                                                                                                                         | 00da ff                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ff ffff              |  |  |  |  |  |  |

|                               | I placed in d<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank<br>If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode wher<br>Section 24 | placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed |                      |  |  |  |  |  |  |

| Words:                        | 1                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |  |  |  |  |  |  |

| Cycles:                       | 1                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |  |  |  |  |  |  |

| Q Cycle Activity:             |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |  |  |  |  |  |  |

| Q1                            | Q2                                                                                                                                           | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Q4                   |  |  |  |  |  |  |

| Decode                        | Read<br>register 'f'                                                                                                                         | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                               | Write to destination |  |  |  |  |  |  |

| Example:                      | ADDWFC                                                                                                                                       | REG, 0,                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                    |  |  |  |  |  |  |

| Before Instruc                |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |  |  |  |  |  |  |

| Carry bit<br>REG<br>W         | = 1<br>= 02h<br>= 4Dh                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |  |  |  |  |  |  |

| After Instructio<br>Carry bit | on<br>= 0                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |  |  |  |  |  |  |

| REG<br>W                      | = 0<br>= 02h<br>= 50h                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |  |  |  |  |  |  |

| ANC                      | DLW            | AND                                                                               | AND Literal with W |                 |     |    |           |  |  |  |  |  |

|--------------------------|----------------|-----------------------------------------------------------------------------------|--------------------|-----------------|-----|----|-----------|--|--|--|--|--|

| Synta                    | ax:            | ANDL                                                                              | N I                | k               |     |    |           |  |  |  |  |  |

| Oper                     | ands:          | 0 ≤ k ≤                                                                           | 255                |                 |     |    |           |  |  |  |  |  |

| Oper                     | ation:         | (W) .AND. $k \rightarrow W$                                                       |                    |                 |     |    |           |  |  |  |  |  |

| Statu                    | is Affected:   | N, Z                                                                              |                    |                 |     |    |           |  |  |  |  |  |

| Enco                     | oding:         | 000                                                                               | 0                  | 1011            | kkk | k  | kkkk      |  |  |  |  |  |

| Desc                     | cription:      | The contents of W are ANDed with the 8-bit literal 'k'. The result is placed in V |                    |                 |     |    |           |  |  |  |  |  |

| Word                     | ls:            | 1                                                                                 |                    |                 |     |    |           |  |  |  |  |  |

| Cycle                    | es:            | 1                                                                                 |                    |                 |     |    |           |  |  |  |  |  |

| QC                       | ycle Activity: |                                                                                   |                    |                 |     |    |           |  |  |  |  |  |

|                          | Q1             | Q2                                                                                |                    | Q3              |     |    | Q4        |  |  |  |  |  |

|                          | Decode         | Read lit<br>'k'                                                                   | eral               | Process<br>Data |     | Wi | rite to W |  |  |  |  |  |

| <u>Exan</u>              | nple:          | ANDLW                                                                             | 1                  | 05Fh            |     |    |           |  |  |  |  |  |

|                          | Before Instruc | tion                                                                              |                    |                 |     |    |           |  |  |  |  |  |

| W =<br>After Instruction |                | = A3                                                                              | h                  |                 |     |    |           |  |  |  |  |  |

|                          |                | on                                                                                |                    |                 |     |    |           |  |  |  |  |  |

|                          |                |                                                                                   |                    |                 |     |    |           |  |  |  |  |  |

| RLNCF                     | Rotate Left f (No Carry)                                                                                                                                                                                                                                                                                                                                                                                                                                       | RI                                                                                                                                | RCF                           | Rotate Ri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ght f throug    | jh Carry             |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|--|

| Syntax:                   | RLNCF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                              | Sy                                                                                                                                | ntax:                         | RRCF f{,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | d {,a}}         |                      |  |

| Operands:                 | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                          | Oţ                                                                                                                                | perands:                      | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |                      |  |

| Operation:                | $(f < n >) \rightarrow dest < n + 1 >,$<br>$(f < 7 >) \rightarrow dest < 0 >$                                                                                                                                                                                                                                                                                                                                                                                  | Oţ                                                                                                                                | peration:                     | $(f < n >) \rightarrow de$<br>$(f < 0 >) \rightarrow C$<br>$(C) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ,               |                      |  |

| Status Affected:          | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Sta                                                                                                                               | atus Affected:                | (c) v soor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                      |  |

| Encoding:<br>Description: | 0100 01da ffff<br>The contents of register 'f' are                                                                                                                                                                                                                                                                                                                                                                                                             | <u> </u>                                                                                                                          | icoding:                      | 0011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 00da ff         | ff ffff              |  |

|                           | one bit to the left. If 'd' is '0', t<br>is placed in W. If 'd' is '1', the<br>stored back in register 'f' (def<br>If 'a' is '0', the Access Bank is<br>If 'a' is '1', the BSR is used to<br>GPR bank (default).<br>If 'a' is '0' and the extended in<br>set is enabled, this instruction<br>in Indexed Literal Offset Addr<br>mode whenever $f \le 95$ (5Fh).<br>Section 24.2.3 "Byte-Orient<br>Bit-Oriented Instructions in<br>Literal Offset Mode" for deta | the result De<br>result is<br>ault).<br>selected.<br>select the<br>nstruction<br>operates<br>ressing<br>See<br>red and<br>Indexed | escription:                   | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in W<br>If 'd' is '1', the result is placed back in<br>register 'f' (default).<br>If 'a' is '0', the Access Bank is selected<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                 |                      |  |

| Words:                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                   |                               | <b>−</b> C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | - registe       | er f 🗕 🗕             |  |

| Cycles:                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ۱۸/                                                                                                                               | ords:                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                      |  |

| Q Cycle Activity:         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                   | vcles:                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                      |  |

| Q1                        | Q2 Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Q4 9                                                                                                                              | Cycle Activity:               | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                      |  |