Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I²C, SPI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2520-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name            | Pi         | Pin Number |                   |        | Buffer    | Description                                                       |

|---------------------|------------|------------|-------------------|--------|-----------|-------------------------------------------------------------------|

| Fill Name           | PDIP       | QFN        | TQFP              | Туре   | Туре      | Description                                                       |

|                     |            |            |                   |        |           | PORTE is a bidirectional I/O port.                                |

| RE0/RD/AN5          | 8          | 25         | 25                |        |           |                                                                   |

| RE0                 |            |            |                   | I/O    | ST        | Digital I/O.                                                      |

| RD                  |            |            |                   | I      | TTL       | Read control for Parallel Slave Port                              |

| AN5                 |            |            |                   | 1      | Analog    | (see also WR and CS pins).<br>Analog input 5.                     |

| RE1/WR/AN6          | 9          | 26         | 26                | •      | , maiog   |                                                                   |

| RE1                 | 9          | 20         | 20                | I/O    | ST        | Digital I/O.                                                      |

| WR                  |            |            |                   | I      | TTL       | Write control for Parallel Slave Port                             |

|                     |            |            |                   |        |           | (see $\overline{CS}$ and $\overline{RD}$ pins).                   |

| AN6                 |            |            |                   | I      | Analog    | Analog input 6.                                                   |

| RE2/CS/AN7          | 10         | 27         | 27                |        | <b>0T</b> |                                                                   |

| RE2<br>CS           |            |            |                   | I/O    | ST<br>TTL | Digital I/O.<br>Chip Select control for Parallel Slave Port       |

| 00                  |            |            |                   | 1      |           | (see related $\overline{\text{RD}}$ and $\overline{\text{WR}}$ ). |

| AN7                 |            |            |                   | I.     | Analog    |                                                                   |

| RE3                 |            |            | _                 | _      | _         | See MCLR/VPP/RE3 pin.                                             |

| Vss                 | 12, 31     | 6, 30,     | 6, 29             | Р      | _         | Ground reference for logic and I/O pins.                          |

|                     |            | 31         |                   |        |           |                                                                   |

| Vdd                 | 11, 32     |            | 7, 28             | Р      | —         | Positive supply for logic and I/O pins.                           |

|                     |            | 28, 29     | 40.40             |        |           |                                                                   |

| NC                  | _          | 13         | 12, 13,<br>33, 34 | _      | _         | No Connect.                                                       |

| Legend: TTL = TTL c | •          | •          |                   |        |           | CMOS = CMOS compatible input or output                            |

|                     | itt Trigge | er input v | with CM           | OS lev |           | = Input                                                           |

| O = Outpu           | ıt         |            |                   |        | F         | P = Power                                                         |

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

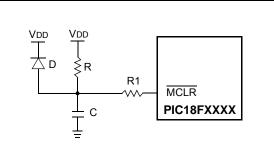

## 4.2 Master Clear (MCLR)

The MCLR pin provides a method for triggering an external Reset of the device. A Reset is generated by holding the pin low. These devices have a noise filter in the MCLR Reset path which detects and ignores small pulses.

The MCLR pin is not driven low by any internal Resets, including the WDT.

In PIC18F2420/2520/4420/4520 devices, the  $\overline{\text{MCLR}}$  input can be disabled with the MCLRE Configuration bit. When  $\overline{\text{MCLR}}$  is disabled, the pin becomes a digital input. See **Section 10.5** "**PORTE, TRISE and LATE Registers**" for more information.

## 4.3 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip whenever VDD rises above a certain threshold. This allows the device to start in the initialized state when VDD is adequate for operation.

To take advantage of the POR circuitry, tie the  $\overline{\text{MCLR}}$  pin through a resistor (1 k $\Omega$  to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 4-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

POR events are captured by the  $\overrightarrow{POR}$  bit (RCON<1>). The state of the bit is set to '0' whenever a POR occurs; it does not change for any other Reset event.  $\overrightarrow{POR}$  is not reset to '1' by any hardware event. To capture multiple events, the user manually resets the bit to '1' in software following any POR.

### FIGURE 4-2:

### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \ k\Omega$  is recommended to make sure that the voltage drop across R does not violate the device's electrical specification.

### 4.6 Reset State of Registers

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state" depending on the type of Reset that occurred.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register,  $\overline{RI}$ ,  $\overline{TO}$ ,  $\overline{PD}$ ,  $\overline{POR}$  and  $\overline{BOR}$ , are set or cleared differently in different Reset situations, as indicated in Table 4-3. These bits are used in software to determine the nature of the Reset. Table 4-4 describes the Reset states for all of the Special Function Registers. These are categorized by Power-on and Brown-out Resets, Master Clear and WDT Resets and WDT wake-ups.

| TABLE 4-3: | STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION |

|------------|------------------------------------------------------------------|

|            | FOR RCON REGISTER                                                |

| Condition                                                   | Program               | Program RCON Register |    |    |     |     | STKPTR Register |        |

|-------------------------------------------------------------|-----------------------|-----------------------|----|----|-----|-----|-----------------|--------|

| Condition                                                   | Counter               | RI                    | то | PD | POR | BOR | STKFUL          | STKUNF |

| Power-on Reset                                              | 0000h                 | 1                     | 1  | 1  | 0   | 0   | 0               | 0      |

| RESET Instruction                                           | 0000h                 | 0                     | u  | u  | u   | u   | u               | u      |

| Brown-out Reset                                             | 0000h                 | 1                     | 1  | 1  | u   | 0   | u               | u      |

| MCLR Reset during Power-Managed Run Modes                   | 0000h                 | u                     | 1  | u  | u   | u   | u               | u      |

| MCLR Reset during Power-Managed Idle Modes and Sleep Mode   | 0000h                 | u                     | 1  | 0  | u   | u   | u               | u      |

| WDT Time-out during Full Power or<br>Power-Managed Run Mode | 0000h                 | u                     | 0  | u  | u   | u   | u               | u      |

| MCLR Reset during Full-Power Execution                      | 0000h                 | u                     | u  | u  | u   | u   | u               | u      |

| Stack Full Reset (STVREN = 1)                               | 0000h                 | u                     | u  | u  | u   | u   | 1               | u      |

| Stack Underflow Reset (STVREN = 1)                          | 0000h                 | u                     | u  | u  | u   | u   | u               | 1      |

| Stack Underflow Error (not an actual<br>Reset, STVREN = 0)  | 0000h                 | u                     | u  | u  | u   | u   | u               | 1      |

| WDT Time-out during<br>Power-Managed Idle or Sleep Modes    | PC + 2                | u                     | 0  | 0  | u   | u   | u               | u      |

| Interrupt Exit from Power-Managed<br>Modes                  | PC + 2 <sup>(1)</sup> | u                     | u  | 0  | u   | u   | u               | u      |

**Legend:** u = unchanged

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the interrupt vector (008h or 0018h).

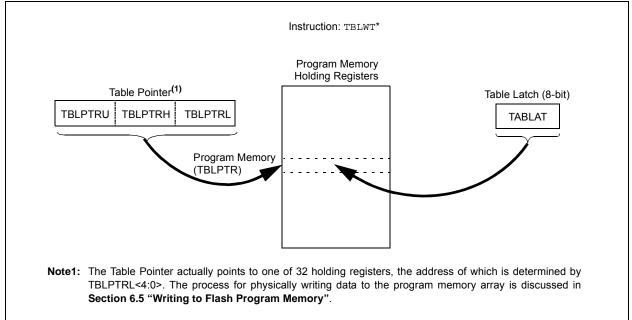

### FIGURE 6-2: TABLE WRITE OPERATION

## 6.2 Control Registers

Several control registers are used in conjunction with the  $\tt TBLRD$  and  $\tt TBLWT$  instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

### 6.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 6-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The EEPGD control bit determines if the access will be a program or data EEPROM memory access. When clear, any subsequent operations will operate on the data EEPROM memory. When set, any subsequent operations will operate on the program memory.

The CFGS control bit determines if the access will be to the Configuration/Calibration registers or to program memory/data EEPROM memory. When set, subsequent operations will operate on Configuration registers regardless of EEPGD (see **Section 23.0 "Special Features of the CPU"**). When clear, memory selection access is determined by EEPGD. The FREE bit, when set, will allow a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR is       |  |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | read as '1'. This can indicate that a write |  |  |  |  |  |  |  |  |  |

|       | operation was prematurely terminated by     |  |  |  |  |  |  |  |  |  |

|       | a Reset, or a write operation was           |  |  |  |  |  |  |  |  |  |

|       | attempted improperly.                       |  |  |  |  |  |  |  |  |  |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation.

**Note:** The EEIF interrupt flag bit (PIR2<4>) is set when the write is complete. It must be cleared in software.

### 9.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Enable registers (PIE1 and PIE2). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

### REGISTER 9-6: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|-------|-------|-------|--------|--------|--------|

| PSPIE <sup>(1)</sup> | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE |

| bit 7                |       |       |       |       |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | <b>PSPIE:</b> Parallel Slave Port Read/Write Interrupt Enable bit <sup>(1)</sup>                                   |

|-------|--------------------------------------------------------------------------------------------------------------------|

|       | <ol> <li>Enables the PSP read/write interrupt</li> <li>Disables the PSP read/write interrupt</li> </ol>            |

| bit 6 | ADIE: A/D Converter Interrupt Enable bit                                                                           |

|       | <ul><li>1 = Enables the A/D interrupt</li><li>0 = Disables the A/D interrupt</li></ul>                             |

| bit 5 | RCIE: EUSART Receive Interrupt Enable bit                                                                          |

|       | <ul> <li>1 = Enables the EUSART receive interrupt</li> <li>0 = Disables the EUSART receive interrupt</li> </ul>    |

| bit 4 | TXIE: EUSART Transmit Interrupt Enable bit                                                                         |

|       | <ul> <li>1 = Enables the EUSART transmit interrupt</li> <li>0 = Disables the EUSART transmit interrupt</li> </ul>  |

| bit 3 | SSPIE: Master Synchronous Serial Port Interrupt Enable bit                                                         |

|       | <ul><li>1 = Enables the MSSP interrupt</li><li>0 = Disables the MSSP interrupt</li></ul>                           |

| bit 2 | CCP1IE: CCP1 Interrupt Enable bit                                                                                  |

|       | <ul><li>1 = Enables the CCP1 interrupt</li><li>0 = Disables the CCP1 interrupt</li></ul>                           |

| bit 1 | TMR2IE: TMR2 to PR2 Match Interrupt Enable bit                                                                     |

|       | <ul><li>1 = Enables the TMR2 to PR2 match interrupt</li><li>0 = Disables the TMR2 to PR2 match interrupt</li></ul> |

| bit 0 | TMR1IE: TMR1 Overflow Interrupt Enable bit                                                                         |

|       | 1 = Enables the TMR1 overflow interrupt                                                                            |

|       | 0 = Disables the TMR1 overflow interrupt                                                                           |

Note 1: This bit is unimplemented on 28-pin devices and will read as '0'.

| Name   | Bit 7                 | Bit 6                 | Bit 5    | Bit 4        | Bit 3       | Bit 2       | Bit 1       | Bit 0 | Reset<br>Values<br>on page |

|--------|-----------------------|-----------------------|----------|--------------|-------------|-------------|-------------|-------|----------------------------|

| PORTA  | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5      | RA4          | RA3         | RA2         | RA1         | RA0   | 52                         |

| LATA   | LATA7 <sup>(1)</sup>  | LATA6 <sup>(1)</sup>  | PORTA Da | ta Latch Re  | gister (Rea | d and Write | to Data Lat | ch)   | 52                         |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | PORTA Da | ta Direction | Register    |             |             |       | 52                         |

| ADCON1 | —                     | —                     | VCFG1    | VCFG0        | PCFG3       | PCFG2       | PCFG1       | PCFG0 | 51                         |

| CMCON  | C2OUT                 | C10UT                 | C2INV    | C1INV        | CIS         | CM2         | CM1         | CM0   | 51                         |

| CVRCON | CVREN                 | CVROE                 | CVRR     | CVRSS        | CVR3        | CVR2        | CVR1        | CVR0  | 51                         |

TABLE 10-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTA.

**Note 1:** RA<7:6> and their associated latch and data direction bits are enabled as I/O pins based on oscillator configuration; otherwise, they are read as '0'.

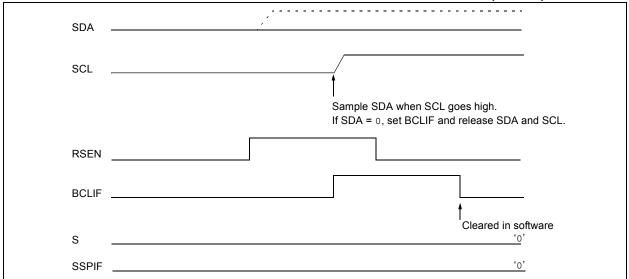

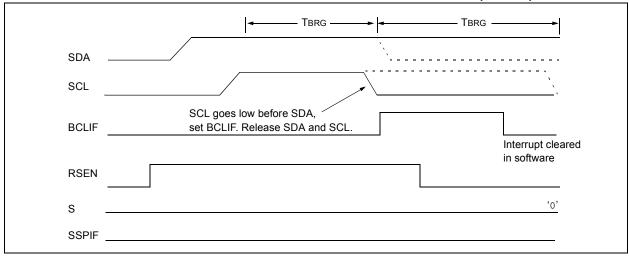

## 17.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 17-29). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 17-30.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

### FIGURE 17-29: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

### FIGURE 17-30: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

### 18.1 Baud Rate Generator (BRG)

The BRG is a dedicated, 8-bit or 16-bit generator that supports both the Asynchronous and Synchronous modes of the EUSART. By default, the BRG operates in 8-bit mode; setting the BRG16 bit (BAUDCON<3>) selects 16-bit mode.

The SPBRGH:SPBRG register pair controls the period of a free-running timer. In Asynchronous mode, bits, BRGH (TXSTA<2>) and BRG16 (BAUDCON<3>), also control the baud rate. In Synchronous mode, BRGH is ignored. Table 18-1 shows the formula for computation of the baud rate for different EUSART modes which only apply in Master mode (internally generated clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRGH:SPBRG registers can be calculated using the formulas in Table 18-1. From this, the error in baud rate can be determined. An example calculation is shown in Example 18-1. Typical baud rates and error values for the various Asynchronous modes are shown in Table 18-2. It may be advantageous to use the high baud rate (BRGH = 1) or the 16-bit BRG to reduce the baud rate error, or achieve a slow baud rate for a fast oscillator frequency.

Writing a new value to the SPBRGH:SPBRG registers causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

## 18.1.1 OPERATION IN POWER-MANAGED MODES

The device clock is used to generate the desired baud rate. When one of the power-managed modes is entered, the new clock source may be operating at a different frequency. This may require an adjustment to the value in the SPBRG register pair.

### 18.1.2 SAMPLING

The data on the RX pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

TABLE 18-1:BAUD RATE FORMULAS

| C    | Configuration Bits |      | BRG/EUSART Mode     | Baud Rate Formula    |  |  |

|------|--------------------|------|---------------------|----------------------|--|--|

| SYNC | BRG16              | BRGH | BRG/EUSART Mode     | Baud Rate Formula    |  |  |

| 0    | 0                  | 0    | 8-Bit/Asynchronous  | Fosc/[64 (n + 1)]    |  |  |

| 0    | 0                  | 1    | 8-Bit/Asynchronous  | $E_{0000}/[16(p+1)]$ |  |  |

| 0    | 1                  | 0    | 16-Bit/Asynchronous | Fosc/[16 (n + 1)]    |  |  |

| 0    | 1                  | 1    | 16-Bit/Asynchronous |                      |  |  |

| 1    | 0                  | x    | 8-Bit/Synchronous   | Fosc/[4 (n + 1)]     |  |  |

| 1    | 1 x                |      | 16-Bit/Synchronous  |                      |  |  |

**Legend:** x = Don't care, n = value of SPBRGH:SPBRG register pair

## 20.0 COMPARATOR MODULE

The analog comparator module contains two comparators that can be configured in a variety of ways. The inputs can be selected from the analog inputs multiplexed with pins, RA0 through RA5, as well as the on-chip voltage reference (see Section 21.0 "Comparator Voltage Reference Module"). The digital outputs (normal or inverted) are available at the pin level and can also be read through the control register.

The CMCON register (Register 20-1) selects the comparator input and output configuration. Block diagrams of the various comparator configurations are shown in Figure 20-1.

### **REGISTER 20-1: CMCON: COMPARATOR CONTROL REGISTER**

| R-0                                                                    | R-0   | R/W-0        | R/W-0 | R/W-0                              | R/W-1 | R/W-1 | R/W-1 |  |  |

|------------------------------------------------------------------------|-------|--------------|-------|------------------------------------|-------|-------|-------|--|--|

| C2OUT                                                                  | C10UT | C2INV        | C1INV | CIS                                | CM2   | CM1   | CM0   |  |  |

| bit 7                                                                  | •     |              |       |                                    |       | •     | bit 0 |  |  |

|                                                                        |       |              |       |                                    |       |       |       |  |  |

| Legend:                                                                |       |              |       |                                    |       |       |       |  |  |

| R = Readable                                                           | bit   | W = Writable | bit   | U = Unimplemented bit, read as '0' |       |       |       |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unk |       |              |       |                                    | nown  |       |       |  |  |

| bit 7 C2OUT: Comparator 2 Output bit<br>$ \frac{When C2INV = 0:}{1 = C2 VIN + C2 VIN-} \\ 0 = C2 VIN + C2 VIN- When C2INV = 1: 1 = C2 VIN + C2 VIN- 0 = C1 VIN + C1 VIN- 0 = C2 Output Inversion bit 1 = C2 output inverted 0 = C2 output not inverted$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6<br>$ \frac{1}{1} = C2 VIN+ > C2 VIN- 0 = C2 VIN+ < C2 VIN-  \frac{When C2INV = 1:}{1 = C2 VIN+ < C2 VIN-} \\ 0 = C2 VIN+ > C2 VIN- 0 = C2 VIN+ > C2 VIN- 0 = C1 VIN+ > C1 VIN- 0 = C1 VIN+ > C1 VIN- 0 = C1 VIN+ < C1 VIN-  \frac{When C1INV = 1:}{1 = C1 VIN+ > C1 VIN-} \\ 0 = C1 VIN+ > C1 VIN- 0 = C1 VIN+ > C1 VIN- 0 = C1 VIN+ > C1 VIN- 0 = C2 VIN+ > C1 VIN- VIN+ > C1 VIN+ > C1 VIN+ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 6<br>$\frac{When C2INV = 1:}{1 = C2 VIN+ < C2 VIN-}$ $0 = C2 VIN+ > C2 VIN-$ bit 6<br>$C1OUT: Comparator 1 Output bit$ $\frac{When C1INV = 0:}{1 = C1 VIN+ > C1 VIN-}$ $0 = C1 VIN+ < C1 VIN-$ $\frac{When C1INV = 1:}{1 = C1 VIN+ < C1 VIN-}$ $0 = C1 VIN+ < C1 VIN-$ $0 = C1 VIN+ < C1 VIN-$ $1 = C1 VIN+ > C1 VIN-$ bit 5<br>C2INV: Comparator 2 Output Inversion bit $1 = C2 output inverted$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 6<br>$1 = C2 VIN + C2 VIN - 0 = C2 VIN + C2 VIN - 0 = C2 VIN + C2 VIN - 0 = C1 OUT: Comparator 1 Output bit \frac{When C1INV = 0:}{1 = C1 VIN + C1 VIN - 0} = C1 VIN + C1 VIN - 0 = C1 VIN + C1 VIN + C1 VIN - 0 = C1 VIN + C1 $ |

| bit 6<br>$0 = C2 V_{IN} + > C2 V_{IN}$ bit 6<br>$C1OUT: Comparator 1 Output bit$ $\frac{When C1INV = 0:}{1 = C1 V_{IN} + > C1 V_{IN}}$ $0 = C1 V_{IN} + < C1 V_{IN}$ $\frac{When C1INV = 1:}{1 = C1 V_{IN} + < C1 V_{IN}}$ $0 = C1 V_{IN} + < C1 V_{IN}$ bit 5<br>C2INV: Comparator 2 Output Inversion bit $1 = C2 output inverted$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| bit 6 C1OUT: Comparator 1 Output bit<br>$\frac{When C1INV = 0:}{1 = C1 VIN+ > C1 VIN-}$ $0 = C1 VIN+ < C1 VIN-$ $\frac{When C1INV = 1:}{1 = C1 VIN+ < C1 VIN-}$ $0 = C1 VIN+ < C1 VIN-$ $0 = C1 VIN+ > C1 VIN-$ bit 5 C2INV: Comparator 2 Output Inversion bit<br>1 = C2  output inverted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $\frac{When C1INV = 0:}{1 = C1 VIN+ > C1 VIN-}$ $0 = C1 VIN+ < C1 VIN-$ $\frac{When C1INV = 1:}{1 = C1 VIN+ < C1 VIN-}$ $0 = C1 VIN+ < C1 VIN-$ $0 = C1 VIN+ > C1 VIN-$ bit 5 $C2INV: Comparator 2 Output Inversion bit$ $1 = C2 output inverted$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $1 = C1 VIN+ > C1 VIN-$ $0 = C1 VIN+ < C1 VIN-$ $\frac{When C1INV = 1:}{1 = C1 VIN+ < C1 VIN-}$ $0 = C1 VIN+ < C1 VIN-$ $0 = C1 VIN+ > C1 VIN-$ bit 5 $C2INV: Comparator 2 Output Inversion bit$ $1 = C2 output inverted$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0 = C1 VIN+ < C1 VIN-         When C1INV = 1:         1 = C1 VIN+ < C1 VIN-         0 = C1 VIN+ > C1 VIN-         0 = C1 VIN+ > C1 VIN-         bit 5         C2INV: Comparator 2 Output Inversion bit         1 = C2 output inverted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| When $C1INV = 1$ : $1 = C1 VIN+ < C1 VIN 0 = C1 VIN+ > C1 VIN-$ bit 5 <b>C2INV</b> : Comparator 2 Output Inversion bit $1 = C2$ output inverted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 5<br>$ \begin{array}{r} 1 = C1 \ VIN+ < C1 \ VIN-\\ 0 = C1 \ VIN+ > C1 \ VIN-\\ \hline C2INV: Comparator 2 \ Output Inversion \ bit\\ 1 = C2 \ output inverted \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 5 $C2INV$ : Comparator 2 Output Inversion bit<br>1 = C2 output inverted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bit 5 <b>C2INV</b> : Comparator 2 Output Inversion bit<br>1 = C2 output inverted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1 = C2 output inverted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 4 <b>C1INV</b> : Comparator 1 Output Inversion bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1 = C1 output inverted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0 = C1 output not inverted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| bit 3 CIS: Comparator Input Switch bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| When CM<2:0> = 110:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1 = C1 VIN- connects to RA3/AN3/VREF+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| C2 VIN- connects to RA2/AN2/VREF-/CVREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0 = C1 VIN- connects to RA0/AN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| C2 VIN- connects to RA1/AN1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |