Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1.5K x 8                                                                    |

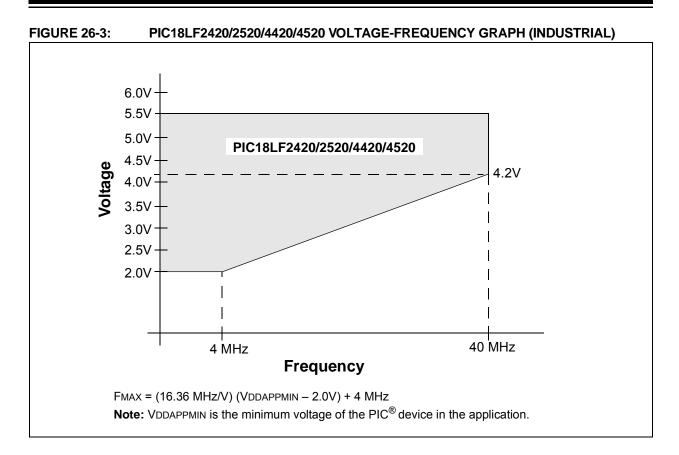

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2520t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

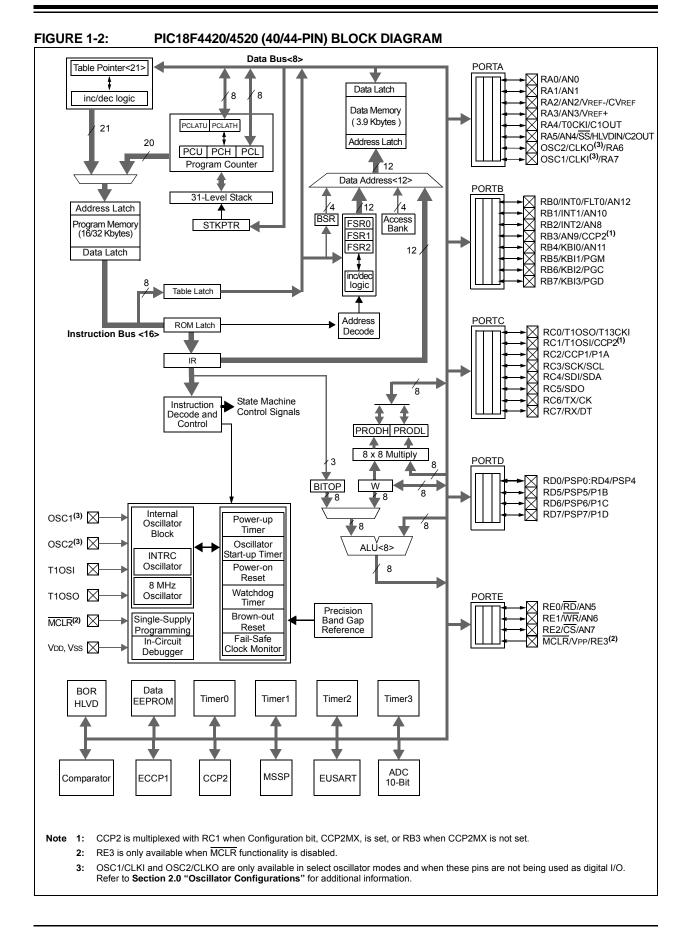

| Features                                | PIC18F2420                                                                                             | PIC18F2520                                                                                                     | PIC18F4420                                                                                             | PIC18F4520                                                                                             |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Operating Frequency                     | DC – 40 MHz                                                                                            | DC – 40 MHz                                                                                                    | DC – 40 MHz                                                                                            | DC – 40 MHz                                                                                            |

| Program Memory (Bytes)                  | 16384                                                                                                  | 32768                                                                                                          | 16384                                                                                                  | 32768                                                                                                  |

| Program Memory<br>(Instructions)        | 8192                                                                                                   | 16384                                                                                                          | 8192                                                                                                   | 16384                                                                                                  |

| Data Memory (Bytes)                     | 768                                                                                                    | 1536                                                                                                           | 768                                                                                                    | 1536                                                                                                   |

| Data EEPROM Memory (Bytes)              | 256                                                                                                    | 256                                                                                                            | 256                                                                                                    | 256                                                                                                    |

| Interrupt Sources                       | 19                                                                                                     | 19                                                                                                             | 20                                                                                                     | 20                                                                                                     |

| I/O Ports                               | Ports A, B, C, (E)                                                                                     | Ports A, B, C, (E)                                                                                             | Ports A, B, C, D, E                                                                                    | Ports A, B, C, D, E                                                                                    |

| Timers                                  | 4                                                                                                      | 4                                                                                                              | 4                                                                                                      | 4                                                                                                      |

| Capture/Compare/PWM Modules             | 2                                                                                                      | 2                                                                                                              | 1                                                                                                      | 1                                                                                                      |

| Enhanced<br>Capture/Compare/PWM Modules | 0                                                                                                      | 0                                                                                                              | 1                                                                                                      | 1                                                                                                      |

| Serial Communications                   | MSSP,<br>Enhanced USART                                                                                | MSSP,<br>Enhanced USART                                                                                        | MSSP,<br>Enhanced USART                                                                                | MSSP,<br>Enhanced USART                                                                                |

| Parallel Communications (PSP)           | No                                                                                                     | No                                                                                                             | Yes                                                                                                    | Yes                                                                                                    |

| 10-Bit Analog-to-Digital Module         | 10 Input Channels                                                                                      | 10 Input Channels                                                                                              | 13 Input Channels                                                                                      | 13 Input Channels                                                                                      |

| Resets (and Delays)                     | POR, BOR,<br>RESET Instruction,<br>Stack Full, Stack<br>Underflow (PWRT, OST),<br>MCLR (optional), WDT | POR, BOR,<br>RESET Instruction,<br>Stack Full, Stack<br><u>Underfl</u> ow (PWRT, OST),<br>MCLR (optional), WDT | POR, BOR,<br>RESET Instruction,<br>Stack Full, Stack<br>Underflow (PWRT, OST),<br>MCLR (optional), WDT | POR, BOR,<br>RESET Instruction,<br>Stack Full, Stack<br>Underflow (PWRT, OST),<br>MCLR (optional), WDT |

| Programmable<br>High/Low-Voltage Detect | Yes                                                                                                    | Yes                                                                                                            | Yes                                                                                                    | Yes                                                                                                    |

| Programmable Brown-out Reset            | Yes                                                                                                    | Yes                                                                                                            | Yes                                                                                                    | Yes                                                                                                    |

| Instruction Set                         | 75 Instructions;<br>83 with Extended<br>Instruction Set Enabled                                        | 75 Instructions;<br>83 with Extended<br>Instruction Set Enabled                                                | 75 Instructions;<br>83 with Extended<br>Instruction Set Enabled                                        | 75 Instructions;<br>83 with Extended<br>Instruction Set Enabled                                        |

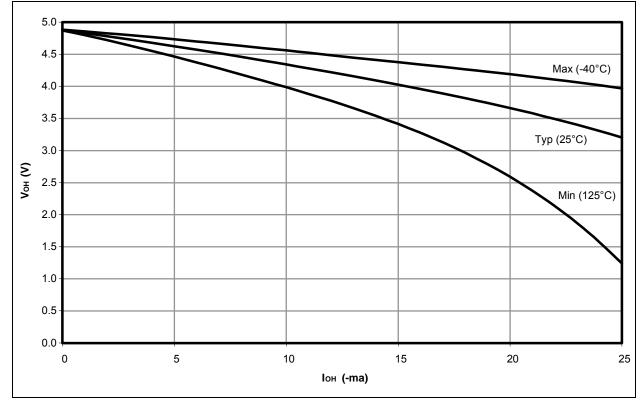

| Packages                                | 28-Pin SPDIP<br>28-Pin SOIC<br>28-Pin QFN                                                              | 28-Pin SPDIP<br>28-Pin SOIC<br>28-Pin QFN                                                                      | 40-Pin PDIP<br>44-Pin QFN<br>44-Pin TQFP                                                               | 40-Pin PDIP<br>44-Pin QFN<br>44-Pin TQFP                                                               |

### TABLE 1-1: DEVICE FEATURES

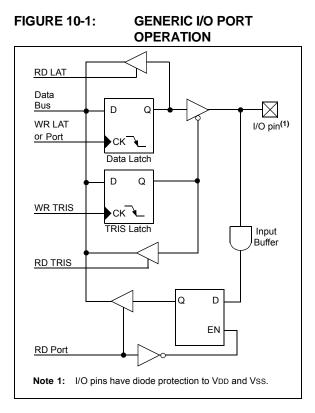

## 10.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (Data Direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (Data Latch register)

The Data Latch (LAT register) is useful for read-modifywrite operations on the value that the I/O pins are driving.

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 10-1.

### 10.1 PORTA, TRISA and LATA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin). Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the port latch.

The Data Latch (LATA) register is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input and one of the comparator outputs to become the RA4/T0CKI/C1OUT pin. Pins RA6 and RA7 are multiplexed with the main oscillator pins; they are enabled as oscillator or I/O pins by the selection of the main oscillator in the Configuration register (see **Section 23.1 "Configuration Bits**" for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as 'o'.

The other PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs and the comparator voltage reference output. The operation of pins RA<3:0> and RA5 as A/D Converter inputs is selected by clearing or setting the control bits in the ADCON1 register (A/D Control Register 1).

Pins RA0 through RA5 may also be used as comparator inputs or outputs by setting the appropriate bits in the CMCON register. To use RA<3:0> as digital inputs, it is also necessary to turn off the comparators.

| Note: | On a Power-on Reset, RA5 and RA<3:0>          |

|-------|-----------------------------------------------|

|       | are configured as analog inputs and read      |

|       | as '0'. RA4 is configured as a digital input. |

The RA4/T0CKI/C1OUT pin is a Schmitt Trigger input. All other PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

### EXAMPLE 10-1: INITIALIZING PORTA

| CLRF  | PORTA  | ; | Initialize PORTA by   |

|-------|--------|---|-----------------------|

|       |        | ; | clearing output       |

|       |        | ; | data latches          |

| CLRF  | LATA   | ; | Alternate method      |

|       |        | ; | to clear output       |

|       |        | ; | data latches          |

| MOVLW | 07h    | ; | Configure A/D         |

| MOVWF | ADCON1 | ; | for digital inputs    |

| MOVWF | 07h    | ; | Configure comparators |

| MOVWF | CMCON  | ; | for digital input     |

| MOVLW | 0CFh   | ; | Value used to         |

|       |        | ; | initialize data       |

|       |        | ; | direction             |

| MOVWF | TRISA  | ; | Set RA<3:0> as inputs |

|       |        | ; | RA<5:4> as outputs    |

|       |        |   | -                     |

| Name    | Bit 7                                    | Bit 6                                   | Bit 5        | Bit 4       | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|------------------------------------------|-----------------------------------------|--------------|-------------|---------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH                                 | PEIE/GIEL                               | TMR0IE       | INT0IE      | RBIE    | TMR0IF | INT0IF | RBIF   | 49                         |

| RCON    | IPEN                                     | SBOREN                                  | _            | RI          | TO      | PD     | POR    | BOR    | 48                         |

| PIR1    | PSPIF <sup>(1)</sup>                     | ADIF                                    | RCIF         | TXIF        | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 52                         |

| PIE1    | PSPIE <sup>(1)</sup>                     | ADIE                                    | RCIE         | TXIE        | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 52                         |

| IPR1    | PSPIP <sup>(1)</sup>                     | ADIP                                    | RCIP         | TXIP        | SSPIP   | CCP1IP | TMR2IP | TMR1IP | 52                         |

| PIR2    | OSCFIF                                   | CMIF                                    | _            | EEIF        | BCLIF   | HLVDIF | TMR3IF | CCP2IF | 52                         |

| PIE2    | OSCFIE                                   | CMIE                                    | _            | EEIE        | BCLIE   | HLVDIE | TMR3IE | CCP2IE | 52                         |

| IPR2    | OSCFIP                                   | CMIP                                    | _            | EEIP        | BCLIP   | HLVDIP | TMR3IP | CCP2IP | 52                         |

| TRISB   | PORTB Da                                 | PORTB Data Direction Register           |              |             |         |        |        |        |                            |

| TRISC   | PORTC Da                                 | ata Direction                           | Register     |             |         |        |        |        | 52                         |

| TMR1L   | Timer1 Re                                | gister Low B                            | yte          |             |         |        |        |        | 50                         |

| TMR1H   | Timer1 Reg                               | gister High E                           | Byte         |             |         |        |        |        | 50                         |

| T1CON   | RD16                                     | T1RUN                                   | T1CKPS1      | T1CKPS0     | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 50                         |

| TMR3H   | Timer3 Re                                | gister High E                           | Byte         |             |         |        |        |        | 51                         |

| TMR3L   | Timer3 Re                                | gister Low B                            | yte          |             |         |        |        |        | 51                         |

| T3CON   | RD16                                     | T3CCP2                                  | T3CKPS1      | T3CKPS0     | T3CCP1  | T3SYNC | TMR3CS | TMR3ON | 51                         |

| CCPR1L  | Capture/Co                               | ompare/PWI                              | M Register   | 1 Low Byte  |         |        |        |        | 51                         |

| CCPR1H  | Capture/Compare/PWM Register 1 High Byte |                                         |              |             |         |        |        | 51     |                            |

| CCP1CON | P1M1 <sup>(1)</sup>                      | P1M0 <sup>(1)</sup>                     | DC1B1        | DC1B0       | CCP1M3  | CCP1M2 | CCP1M1 | CCP1M0 | 51                         |

| CCPR2L  | Capture/Co                               | Capture/Compare/PWM Register 2 Low Byte |              |             |         |        |        |        | 51                         |

| CCPR2H  | Capture/Co                               | ompare/PWI                              | M Register 2 | 2 High Byte |         |        |        |        | 51                         |

| CCP2CON |                                          | _                                       | DC2B1        | DC2B0       | CCP2M3  | CCP2M2 | CCP2M1 | CCP2M0 | 51                         |

| TARI E 15-3- | <b>REGISTERS ASSOCIATED WITH CAPTURE</b> | COMPARE TIMER1 AND TIMER3      |

|--------------|------------------------------------------|--------------------------------|

| IADLL IJ-J.  | REGISTERS ASSOCIATED WITH CAPTORE        | , COMPARE, HIMLERI AND HIMLERS |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by Capture/Compare, Timer1 or Timer3.

Note 1: These bits are unimplemented on 28-pin devices; always maintain these bits clear.

| R/W-0         | R-1                                                                               | R/W-0                                                           | R/W-0                                                   | R/W-0            | U-0             | R/W-0            | R/W-0           |

|---------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------|------------------|-----------------|------------------|-----------------|

| ABDOVF        | RCIDL                                                                             | RXDTP                                                           | TXCKP                                                   | BRG16            | _               | WUE              | ABDEN           |

| bit 7         |                                                                                   |                                                                 |                                                         |                  |                 |                  | bit             |

| Legend:       |                                                                                   |                                                                 |                                                         |                  |                 |                  |                 |

| R = Readable  | e bit                                                                             | W = Writable                                                    | bit                                                     | U = Unimple      | mented bit, rea | d as '0'         |                 |

| -n = Value at | POR                                                                               | '1' = Bit is set                                                |                                                         | '0' = Bit is cle | ared            | x = Bit is unki  | nown            |

| bit 7         | 1 = A BRG ro                                                                      | to-Baud Acqui<br>blover has occ<br>rollover has oc              | urred during A                                          |                  | Detect mode (   | must be cleared  | d in software)  |

| bit 6         | 1 = Receive o                                                                     | ive Operation l<br>peration is Idle                             | ;                                                       |                  |                 |                  |                 |

|               |                                                                                   | peration is act                                                 |                                                         |                  |                 |                  |                 |

| bit 5         | Asynchronous<br>1 = Receive d<br>0 = Receive d                                    | lata (RX) is inv<br>lata (RX) is no                             | erted (active-lo                                        | ,                |                 |                  |                 |

|               |                                                                                   | mode:<br>is inverted (ad<br>is not inverted                     |                                                         |                  |                 |                  |                 |

| bit 4         | Asynchronous<br>1 = Idle state<br>0 = Idle state<br>Synchronous<br>1 = Idle state | for transmit (T<br>for transmit (T                              | X) is a low leve<br>X) is a high lev<br>is a high level | el               |                 |                  |                 |

| bit 3         |                                                                                   | it Baud Rate R                                                  |                                                         | e bit            |                 |                  |                 |

|               | 1 = 16-bit Bau                                                                    | ud Rate Gener                                                   | ator – SPBRG                                            | H and SPBRG      | le mode), SPB   | RGH value igno   | red             |

| bit 2         | Unimplemen                                                                        | ted: Read as '                                                  | 0'                                                      |                  |                 |                  |                 |

| bit 1         | WUE: Wake-u                                                                       | up Enable bit                                                   |                                                         |                  |                 |                  |                 |

|               | hardware                                                                          |                                                                 | ising edge                                              |                  | upt generated   | on falling edge  | ; bit cleared i |

|               | Synchronous                                                                       |                                                                 |                                                         |                  |                 |                  |                 |

|               | Unused in this                                                                    |                                                                 |                                                         |                  |                 |                  |                 |

| bit 0         | Asynchronous<br>1 = Enable b<br>cleared ir                                        | aud rate meas<br>n hardware upo<br>e measuremen<br><u>mode:</u> | urement on th<br>on completion.                         |                  | er. Requires re | eception of a Sy | vnc field (55h  |

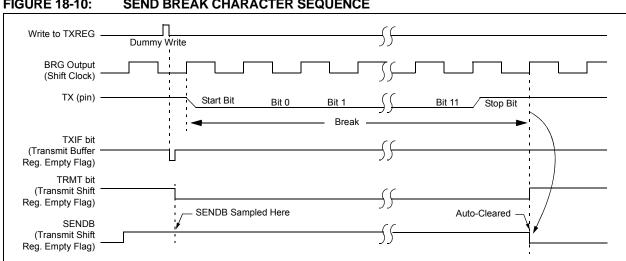

#### 18.2.5 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift register is loaded with data. Note that the value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

Note that the data value written to the TXREG for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 18-10 for the timing of the Break character sequence.

#### 18.2.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN bus master.

- Configure the EUSART for the desired mode. 1.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- Write '55h' to TXREG to load the Sync character 4. into the transmit FIFO buffer.

- After the Break has been sent, the SENDB bit is 5. reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### 18.2.6 **RECEIVING A BREAK CHARACTER**

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in Section 18.2.4 "Auto-Wake-up on Sync Break Character". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABD bit once the TXIF interrupt is observed.

#### **FIGURE 18-10:** SEND BREAK CHARACTER SEQUENCE

| REGISTER 23-4: CON | NFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h) |

|--------------------|--------------------------------------------------------------|

|--------------------|--------------------------------------------------------------|

| R/P-1          | U-0                                                                                                                | U-0                   | U-0            | U-0          | R/P-0            | R/P-1      | R/P-1  |

|----------------|--------------------------------------------------------------------------------------------------------------------|-----------------------|----------------|--------------|------------------|------------|--------|

| MCLRE          | —                                                                                                                  | —                     | _              | _            | LPT1OSC          | PBADEN     | CCP2MX |

| bit 7          | •                                                                                                                  |                       |                |              |                  |            | bit 0  |

|                |                                                                                                                    |                       |                |              |                  |            |        |

| Legend:        |                                                                                                                    |                       |                |              |                  |            |        |

| R = Readable b | bit                                                                                                                | P = Programm          | nable bit      | U = Unimpler | mented bit, read | as '0'     |        |

| -n = Value whe | n device is unp                                                                                                    | programmed            |                | u = Unchang  | ed from progran  | nmed state |        |

|                |                                                                                                                    |                       |                |              |                  |            |        |

| bit 7          | MCLRE: MCL                                                                                                         | R Pin Enable          | bit            |              |                  |            |        |

|                | $1 = \overline{MCLR}$ pin                                                                                          | enabled; RE3          | input pin disa | bled         |                  |            |        |

|                | 0 = RE3 input                                                                                                      | pin enabled; <b>N</b> | ICLR disable   | d            |                  |            |        |

| bit 6-3        | Unimplement                                                                                                        | ted: Read as '        | o'             |              |                  |            |        |

| bit 2          | LPT1OSC: Low-Power Timer1 Oscillator Enable bit                                                                    |                       |                |              |                  |            |        |

|                |                                                                                                                    | onfigured for lov     |                |              |                  |            |        |

|                | 0 = Timer1 co                                                                                                      | onfigured for hig     | gher power op  | eration      |                  |            |        |

| bit 1          | <b>PBADEN:</b> PORTB A/D Enable bit<br>(Affects ADCON1 Reset state. ADCON1 controls PORTB<4:0> pin configuration.) |                       |                |              |                  |            |        |

|                | •                                                                                                                  |                       |                |              | •                | •          |        |

|                |                                                                                                                    | •                     | •              | • •          | annels on Rese   | t          |        |

| <b>h</b> # 0   |                                                                                                                    | 1:0> pins are co      | Singuleu as u  |              | eset             |            |        |

| bit 0          | CCP2MX: CC                                                                                                         |                       |                | 504          |                  |            |        |

|                |                                                                                                                    | ut/output is mu       |                |              |                  |            |        |

|                | $0 = CCP2 \ln p$                                                                                                   | ut/output is mu       | inplexed with  | RDJ          |                  |            |        |

## REGISTER 23-5: CONFIG4L: CONFIGURATION REGISTER 4 LOW (BYTE ADDRESS 300006h)

| R/P-1 | R/P-0 | U-0 | U-0 | U-0 | R/P-1 | U-0 | R/P-1  |

|-------|-------|-----|-----|-----|-------|-----|--------|

| DEBUG | XINST | —   | _   | _   | LVP   | _   | STVREN |

| bit 7 |       |     |     |     |       |     | bit 0  |

| Legend:                                |                      |                                     |

|----------------------------------------|----------------------|-------------------------------------|

| R = Readable bit                       | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device is unprogrammed |                      | u = Unchanged from programmed state |

|                                        |                      |                                     |

| DEBUG: Background Debugger Enable bit                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1 = Background debugger disabled, RB6 and RB7 configured as general purpose I/O pins</li> <li>0 = Background debugger enabled, RB6 and RB7 are dedicated to In-Circuit Debug</li> </ul> |

| XINST: Extended Instruction Set Enable bit                                                                                                                                                       |

| <ul> <li>1 = Instruction set extension and Indexed Addressing mode enabled</li> <li>0 = Instruction set extension and Indexed Addressing mode disabled (Legacy mode)</li> </ul>                  |

| Unimplemented: Read as '0'                                                                                                                                                                       |

| LVP: Single-Supply ICSP™ Enable bit                                                                                                                                                              |

| <ul><li>1 = Single-Supply ICSP enabled</li><li>0 = Single-Supply ICSP disabled</li></ul>                                                                                                         |

| Unimplemented: Read as '0'                                                                                                                                                                       |

| STVREN: Stack Full/Underflow Reset Enable bit                                                                                                                                                    |

| 1 = Stack full/underflow will cause Reset                                                                                                                                                        |

| 0 = Stack full/underflow will not cause Reset                                                                                                                                                    |

|                                                                                                                                                                                                  |

| DAW                                     | Decimal Adjust W Register                                                                                                |                           |                                       | DECF                   | Decrement                                   | Decrement f                                                                                                                                                            |                |  |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------------------|------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|

| Syntax:                                 | DAW                                                                                                                      |                           |                                       | Syntax:                | DECF f{,d                                   | {,a}}                                                                                                                                                                  |                |  |

| Operands:                               | None                                                                                                                     |                           |                                       | Operands:              | $0 \leq f \leq 255$                         |                                                                                                                                                                        |                |  |

| Operation:                              | If [W<3:0> > 9] or [DC = 1] then,<br>(W<3:0>) + 6 $\rightarrow$ W<3:0>;                                                  |                           |                                       | d ∈ [0,1]<br>a ∈ [0,1] |                                             |                                                                                                                                                                        |                |  |

| else,<br>(W<3:0>) $\rightarrow$ W<3:0>; |                                                                                                                          | Operation:                | Operation: $(f) - 1 \rightarrow dest$ |                        |                                             |                                                                                                                                                                        |                |  |

|                                         |                                                                                                                          | Status Affected:          | C, DC, N, O                           | C, DC, N, OV, Z        |                                             |                                                                                                                                                                        |                |  |

|                                         | If [W<7:4> + DC > 9] or [C = 1] then,                                                                                    |                           | Encoding:                             | 0000                   | 0000 01da ffff ffff                         |                                                                                                                                                                        |                |  |

|                                         | · · ·                                                                                                                    | $-6 + DC \rightarrow W$   | <7:4>;                                | Description:           | Decrement r                                 | egister 'f'. If '                                                                                                                                                      | d' is '0', the |  |

|                                         | else,<br>(\//<7:4>) +                                                                                                    | $DC \rightarrow W < 7:43$ | >                                     |                        |                                             | ed in W. If 'd'                                                                                                                                                        | ,              |  |

| Status Affected:                        | (W (7.42))<br>C                                                                                                          |                           | -                                     |                        | (default).                                  | ed back in re                                                                                                                                                          | gister t       |  |

| Encoding:                               | 0000                                                                                                                     | 0000 000                  | 0 0111                                |                        | If 'a' is '0', the Access Bank is selected. |                                                                                                                                                                        |                |  |

| Description:                            |                                                                                                                          |                           |                                       |                        |                                             | If 'a' is '1', the BSR is used to select the GPR bank (default).                                                                                                       |                |  |

| Boconpuoli                              | DAW adjusts the 8-bit value in W,<br>resulting from the earlier addition of two<br>variables (each in packed BCD format) |                           |                                       |                        | •                                           | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See |                |  |

|                                         |                                                                                                                          |                           |                                       |                        |                                             |                                                                                                                                                                        |                |  |

|                                         | and produces a correct packed BCD<br>result.                                                                             |                           |                                       |                        |                                             |                                                                                                                                                                        |                |  |

| Words:                                  | 1                                                                                                                        |                           |                                       |                        | Section 24.2.3 "Byte-Oriented and           |                                                                                                                                                                        |                |  |

| Cycles:                                 | 1                                                                                                                        |                           |                                       |                        |                                             | d Instruction<br>et Mode" for                                                                                                                                          | s in Indexed   |  |

| Q Cycle Activity:                       |                                                                                                                          |                           |                                       | Words:                 | 1                                           |                                                                                                                                                                        | detailo.       |  |

| Q1                                      | Q2                                                                                                                       | Q3                        | Q4                                    | Cycles:                | 1                                           |                                                                                                                                                                        |                |  |

| Decode                                  | Read                                                                                                                     | Process                   | Write                                 | Q Cycle Activity:      | I                                           |                                                                                                                                                                        |                |  |

|                                         | register W                                                                                                               | Data                      | W                                     | Q Cycle Activity.      | Q2                                          | Q3                                                                                                                                                                     | Q4             |  |

| Example 1:                              | 5344                                                                                                                     |                           |                                       | Decode                 | Read                                        | Process                                                                                                                                                                | Write to       |  |

| Defens lasta                            | DAW                                                                                                                      |                           |                                       |                        | register 'f'                                | Data                                                                                                                                                                   | destination    |  |

| Before Instru<br>W                      | = A5h                                                                                                                    |                           |                                       |                        |                                             |                                                                                                                                                                        |                |  |

| С                                       | = 0                                                                                                                      |                           |                                       | Example:               | DECF CI                                     | NT, 1, 0                                                                                                                                                               |                |  |

| DC<br>After Instruct                    | = 0                                                                                                                      |                           |                                       | Before Instru          | ction<br>= 01h                              |                                                                                                                                                                        |                |  |

| W                                       | = 05h                                                                                                                    |                           |                                       | CNT<br>Z               | = 0111                                      |                                                                                                                                                                        |                |  |

| C                                       | = 1                                                                                                                      |                           |                                       | After Instruct         |                                             |                                                                                                                                                                        |                |  |

| DC<br>Example 2:                        | = 0                                                                                                                      |                           |                                       | CNT<br>Z               | = 00h<br>= 1                                |                                                                                                                                                                        |                |  |

| Before Instru                           | ction                                                                                                                    |                           |                                       |                        |                                             |                                                                                                                                                                        |                |  |

| W                                       | = CEh                                                                                                                    |                           |                                       |                        |                                             |                                                                                                                                                                        |                |  |

| C<br>DC                                 | = 0<br>= 0                                                                                                               |                           |                                       |                        |                                             |                                                                                                                                                                        |                |  |

| After Instruct                          | 0                                                                                                                        |                           |                                       |                        |                                             |                                                                                                                                                                        |                |  |

| W                                       | = 34h                                                                                                                    |                           |                                       |                        |                                             |                                                                                                                                                                        |                |  |

| C<br>DC                                 | = 1<br>= 0                                                                                                               |                           |                                       |                        |                                             |                                                                                                                                                                        |                |  |

| 00                                      | - 0                                                                                                                      |                           |                                       |                        |                                             |                                                                                                                                                                        |                |  |

| RRNCF                                                                                                                                                            | Rotate Right f (No Carry)                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                                                                                                                          | RRNCF                                                                                                                                                                                                                                                                                                                                                                                                                | RRNCF f {,d {,a}}                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Operands:                                                                                                                                                        | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Operation:                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                      | $(f < n >) \rightarrow dest < n - 1 >,$<br>$(f < 0 >) \rightarrow dest < 7 >$                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Status Affected:                                                                                                                                                 | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                 | N, Z                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |