Welcome to E-XFL.COM

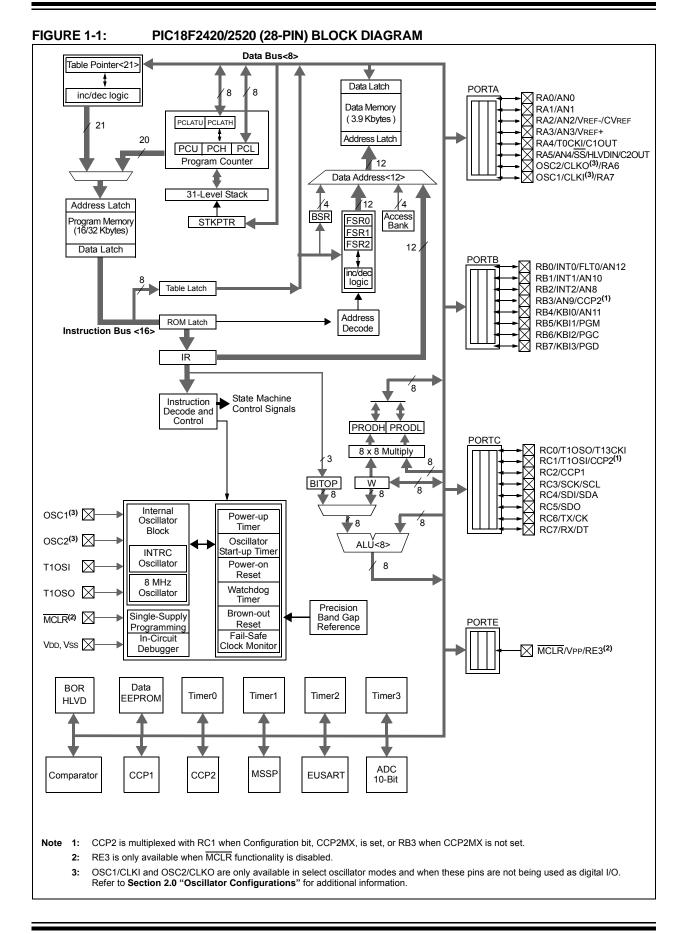

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

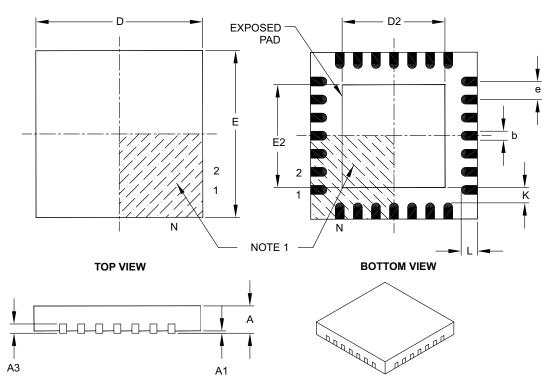

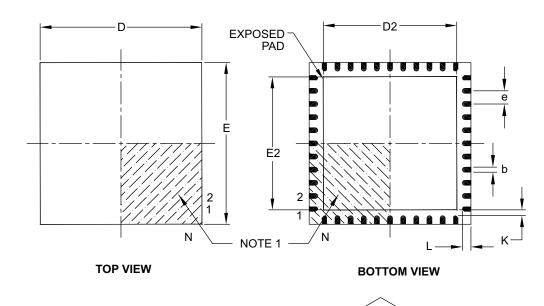

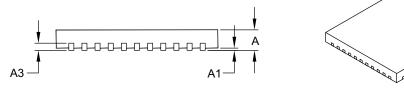

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4420-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name            | Pi         | Pin Number |                   |        | Buffer    | Description                                                       |

|---------------------|------------|------------|-------------------|--------|-----------|-------------------------------------------------------------------|

| Fill Name           | PDIP       | QFN        | TQFP              | Туре   | Туре      | Description                                                       |

|                     |            |            |                   |        |           | PORTE is a bidirectional I/O port.                                |

| RE0/RD/AN5          | 8          | 25         | 25                |        |           |                                                                   |

| RE0                 |            |            |                   | I/O    | ST        | Digital I/O.                                                      |

| RD                  |            |            |                   | I      | TTL       | Read control for Parallel Slave Port                              |

| AN5                 |            |            |                   | 1      | Analog    | (see also WR and CS pins).<br>Analog input 5.                     |

| RE1/WR/AN6          | 9          | 26         | 26                | •      | , analog  |                                                                   |

| RE1                 | 9          | 20         | 20                | I/O    | ST        | Digital I/O.                                                      |

| WR                  |            |            |                   | I      | TTL       | Write control for Parallel Slave Port                             |

|                     |            |            |                   |        |           | (see $\overline{CS}$ and $\overline{RD}$ pins).                   |

| AN6                 |            |            |                   | I      | Analog    | Analog input 6.                                                   |

| RE2/CS/AN7          | 10         | 27         | 27                |        | <b>0T</b> |                                                                   |

| RE2<br>CS           |            |            |                   | I/O    | ST<br>TTL | Digital I/O.<br>Chip Select control for Parallel Slave Port       |

| 00                  |            |            |                   | 1      |           | (see related $\overline{\text{RD}}$ and $\overline{\text{WR}}$ ). |

| AN7                 |            |            |                   | I.     | Analog    |                                                                   |

| RE3                 |            |            | _                 | _      | _         | See MCLR/VPP/RE3 pin.                                             |

| Vss                 | 12, 31     | 6, 30,     | 6, 29             | Р      | _         | Ground reference for logic and I/O pins.                          |

|                     |            | 31         |                   |        |           |                                                                   |

| Vdd                 | 11, 32     |            | 7, 28             | Р      | —         | Positive supply for logic and I/O pins.                           |

|                     |            | 28, 29     | 40.40             |        |           |                                                                   |

| NC                  | _          | 13         | 12, 13,<br>33, 34 | _      | _         | No Connect.                                                       |

| Legend: TTL = TTL c | •          | •          |                   |        |           | CMOS = CMOS compatible input or output                            |

|                     | itt Trigge | er input v | with CM           | OS lev |           | = Input                                                           |

| O = Outpu           | ıt         |            |                   |        | F         | P = Power                                                         |

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

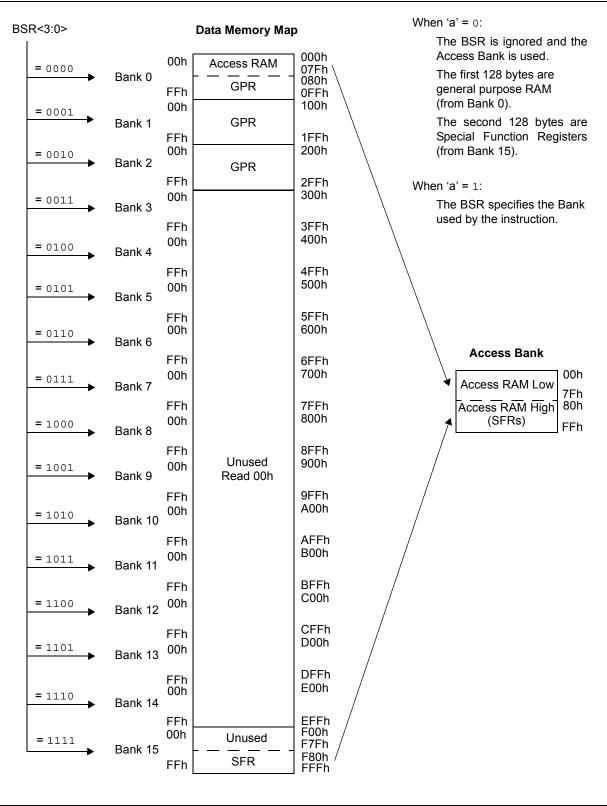

#### FIGURE 5-5: DATA MEMORY MAP FOR PIC18F2420/4420 DEVICES

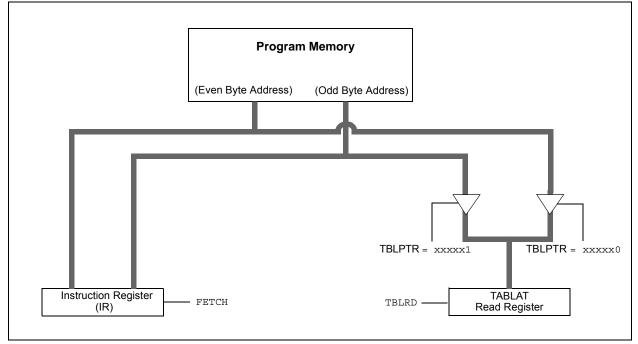

### 6.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

### FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

| MOVLW<br>MOVWF<br>MOVLW<br>MOVLW<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW       |                                                                                                                                                                              | Load TBLPTR with the base<br>address of the word                                                                                                                                       |

|-------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 110 V W1                                  |                                                                                |                                                                                                                                                                              |                                                                                                                                                                                        |

| TBLRD*+                                   | -                                                                              | ;                                                                                                                                                                            | read into TABLAT and increment                                                                                                                                                         |

| MOVF                                      | TABLAT, W                                                                      | ;                                                                                                                                                                            | get data                                                                                                                                                                               |

| MOVWF                                     | WORD EVEN                                                                      |                                                                                                                                                                              |                                                                                                                                                                                        |

| TBLRD*+                                   |                                                                                | ;                                                                                                                                                                            | read into TABLAT and increment                                                                                                                                                         |

| MOVFW                                     | TABLAT, W                                                                      | ;                                                                                                                                                                            | get data                                                                                                                                                                               |

| MOVF                                      | WORD_ODD                                                                       |                                                                                                                                                                              |                                                                                                                                                                                        |

|                                           | MOVWF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVF<br>MOVVF<br>TBLRD*4<br>MOVFW | MOVWF TBLPTRU<br>MOVLW CODE_ADDR_HIGH<br>MOVWF TBLPTRH<br>MOVLW CODE_ADDR_LOW<br>MOVWF TBLPTRL<br>TBLRD*+<br>MOVF TABLAT, W<br>MOVWF WORD_EVEN<br>TBLRD*+<br>MOVFW TABLAT, W | MOVWF TBLPTRU ;<br>MOVUW CODE_ADDR_HIGH<br>MOVWF TBLPTRH<br>MOVLW CODE_ADDR_LOW<br>MOVWF TBLPTRL<br>TBLRD*+ ;<br>MOVF TABLAT, W ;<br>MOVWF WORD_EVEN<br>TBLRD*+ ;<br>MOVFW TABLAT, W ; |

| R/W-1      | R/W-1                                   | U-0                                  | R/W-0            | R/W-0             | U-0            | R/W-0              | R/W-0  |

|------------|-----------------------------------------|--------------------------------------|------------------|-------------------|----------------|--------------------|--------|

| INT2IP     | P INT1IP                                | _                                    | INT2IE           | INT1IE            | _              | INT2IF             | INT1IF |

| bit 7      |                                         |                                      |                  |                   |                |                    | bit C  |

| Legend:    |                                         |                                      |                  |                   |                |                    |        |

| R = Read   | able bit                                | W = Writable                         | bit              | U = Unimplem      | ented bit, rea | d as '0'           |        |

| -n = Value |                                         | '1' = Bit is set                     |                  | '0' = Bit is clea |                | x = Bit is unkn    | iown   |

|            |                                         |                                      | •                | 0 2010 000        |                |                    |        |

| bit 7      | INT2IP: INT                             | 2 External Interi                    | upt Priority bit |                   |                |                    |        |

|            | 1 = High pri                            |                                      |                  |                   |                |                    |        |

|            | 0 = Low price                           | ority                                |                  |                   |                |                    |        |

| bit 6      | INT1IP: INT                             | 1 External Inter                     | upt Priority bit |                   |                |                    |        |

|            | 1 = High pri                            | ,                                    |                  |                   |                |                    |        |

|            | 0 = Low pric                            | •                                    |                  |                   |                |                    |        |

| bit 5      | •                                       | nted: Read as '                      |                  |                   |                |                    |        |

| bit 4      |                                         | 2 External Inter                     | -                |                   |                |                    |        |

|            |                                         | s the INT2 exter<br>s the INT2 exter |                  |                   |                |                    |        |

| bit 3      |                                         | 1 External Interi                    | •                |                   |                |                    |        |

| Sit 0      |                                         | the INT1 exter                       | •                |                   |                |                    |        |

|            |                                         | s the INT1 exter                     |                  |                   |                |                    |        |

| bit 2      | Unimpleme                               | nted: Read as '                      | 0'               |                   |                |                    |        |

| bit 1      | INT2IF: INT                             | 2 External Interr                    | upt Flag bit     |                   |                |                    |        |

|            |                                         |                                      |                  | must be cleared   | in software)   |                    |        |

|            | 0 = The INT                             | 2 external inter                     | rupt did not oco | cur               |                |                    |        |

| bit 0      |                                         | 1 External Interr                    |                  |                   |                |                    |        |

|            |                                         |                                      | •                | must be cleared   | in software)   |                    |        |

|            | 0 = 1  ne IN I                          | 1 external inter                     | מיטר מומ חטל סכנ | JUI               |                |                    |        |

| Note:      | Interrupt flag bit<br>enable bit or the |                                      |                  |                   |                |                    |        |

|            | prior to enabling                       |                                      |                  |                   |                | ate interrupt liag |        |

#### REGISTER 9-3: INTCON3: INTERRUPT CONTROL REGISTER 3

### REGISTER 16-3: ECCP1AS: ECCP AUTO-SHUTDOWN CONTROL REGISTER

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0                 | R/W-0                 |

|---------|---------|---------|---------|--------|--------|-----------------------|-----------------------|

| ECCPASE | ECCPAS2 | ECCPAS1 | ECCPAS0 | PSSAC1 | PSSAC0 | PSSBD1 <sup>(1)</sup> | PSSBD0 <sup>(1)</sup> |

| bit 7   |         |         |         |        |        |                       | bit 0                 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | ECCPASE: ECCP Auto-Shutdown Event Status bit                                                                                                                                                      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = A shutdown event has occurred; ECCP outputs are in shutdown state</li> <li>0 = ECCP outputs are operating</li> </ul>                                                                 |

| bit 6-4 | ECCPAS<2:0>: ECCP Auto-Shutdown Source Select bits                                                                                                                                                |

|         | <ul> <li>111 = FLT0 or Comparator 1 or Comparator 2</li> <li>110 = FLT0 or Comparator 2</li> <li>101 = FLT0 or Comparator 1</li> </ul>                                                            |

|         | 100 = FLTO                                                                                                                                                                                        |

|         | 011 = Either Comparator 1 or 2<br>010 = Comparator 2 output<br>001 = Comparator 1 output<br>000 = Auto-shutdown is disabled                                                                       |

| bit 3-2 | PSSAC<1:0>: Pins A and C Shutdown State Control bits                                                                                                                                              |

|         | <ul> <li>1x = Pins A and C are tri-state (40/44-pin devices); PWM output is tri-state (28-pin devices)</li> <li>01 = Drive Pins A and C to '1'</li> <li>00 = Drive Pins A and C to '0'</li> </ul> |

| bit 1-0 | PSSBD<1:0>: Pins B and D Shutdown State Control bits <sup>(1)</sup>                                                                                                                               |

|         | 1x = Pins B and D tri-state<br>01 = Drive Pins B and D to '1'<br>00 = Drive Pins B and D to '0'                                                                                                   |

| Note 1: | Reserved on 28-pin devices; maintain these bits clear.                                                                                                                                            |

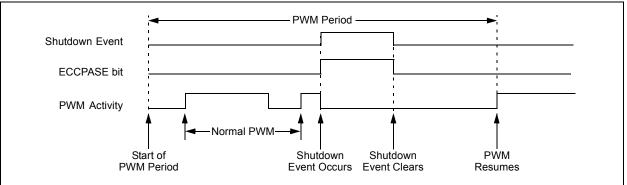

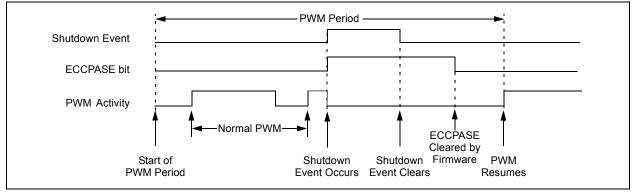

#### 16.4.7.1 Auto-Shutdown and Automatic Restart

The auto-shutdown feature can be configured to allow automatic restarts of the module following a shutdown event. This is enabled by setting the PRSEN bit of the PWM1CON register (PWM1CON<7>).

In Shutdown mode with PRSEN = 1 (Figure 16-10), the ECCPASE bit will remain set for as long as the cause of the shutdown continues. When the shutdown condition clears, the ECCPASE bit is cleared. If PRSEN = 0 (Figure 16-11), once a shutdown condition occurs, the ECCPASE bit will remain set until it is cleared by firmware. Once ECCPASE is cleared, the Enhanced PWM will resume at the beginning of the next PWM period.

| Note: | Writing to the ECCPASE bit is disabled |

|-------|----------------------------------------|

|       | while a shutdown condition is active.  |

Independent of the PRSEN bit setting, if the autoshutdown source is one of the comparators, the shutdown condition is a level. The ECCPASE bit cannot be cleared as long as the cause of the shutdown persists.

The Auto-Shutdown mode can be forced by writing a '1' to the ECCPASE bit.

### 16.4.8 START-UP CONSIDERATIONS

When the ECCP module is used in the PWM mode, the application hardware must use the proper external pullup and/or pull-down resistors on the PWM output pins. When the microcontroller is released from Reset, all of the I/O pins are in the high-impedance state. The external circuits must keep the power switch devices in the OFF state until the microcontroller drives the I/O pins with the proper signal levels or activates the PWM output(s).

The CCP1M<1:0> bits (CCP1CON<1:0>) allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (P1A/P1C and P1B/P1D). The PWM output polarities must be selected before the PWM pins are configured as outputs. Changing the polarity configuration while the PWM pins are configured as outputs is not recommended, since it may result in damage to the application circuits.

The P1A, P1B, P1C and P1D output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pins for output at the same time as the ECCP module may cause damage to the application circuit. The ECCP module must be enabled in the proper output mode and complete a full PWM cycle before configuring the PWM pins as outputs. The completion of a full PWM cycle is indicated by the TMR2IF bit being set as the second PWM period begins.

### FIGURE 16-10: PWM AUTO-SHUTDOWN (PRSEN = 1, AUTO-RESTART ENABLED)

### FIGURE 16-11: PWM AUTO-SHUTDOWN (PRSEN = 0, AUTO-RESTART DISABLED)

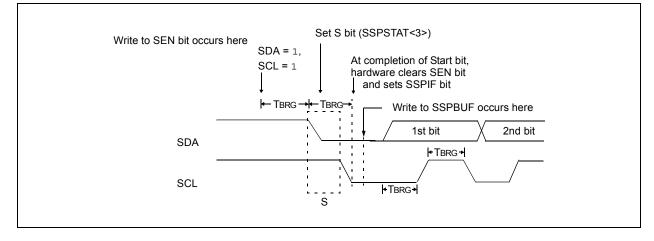

### 17.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware; the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

**Note:** If, at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

#### 17.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

#### FIGURE 17-19: FIRST START BIT TIMING

NOTES:

### 23.0 SPECIAL FEATURES OF THE CPU

PIC18F2420/2520/4420/4520 devices include several features intended to maximize reliability and minimize cost through elimination of external components. These are:

- Oscillator Selection

- Resets:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- · Fail-Safe Clock Monitor

- Two-Speed Start-up

- Code Protection

- · ID Locations

- In-Circuit Serial Programming

The oscillator can be configured for the application depending on frequency, power, accuracy and cost. All of the options are discussed in detail in **Section 2.0 "Oscillator Configurations"**.

A complete discussion of device Resets and interrupts is available in previous sections of this data sheet.

In addition to their Power-up and Oscillator Start-up Timers provided for Resets, PIC18F2420/2520/4420/ 4520 devices have a Watchdog Timer, which is either permanently enabled via the Configuration bits or software controlled (if configured as disabled). The inclusion of an internal RC oscillator also provides the additional benefits of a Fail-Safe Clock Monitor (FSCM) and Two-Speed Start-up. FSCM provides for background monitoring of the peripheral clock and automatic switchover in the event of its failure. Two-Speed Start-up enables code to be executed almost immediately on start-up, while the primary clock source completes its start-up delays.

All of these features are enabled and configured by setting the appropriate Configuration register bits.

## 23.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped starting at program memory location, 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h-3FFFFh), which can only be accessed using table reads and table writes.

Programming the Configuration registers is done in a manner similar to programming the Flash memory. The WR bit in the EECON1 register starts a self-timed write to the Configuration register. In normal operation mode, a TBLWT instruction with the TBLPTR pointing to the Configuration register sets up the address and the data for the Configuration register write. Setting the WR bit starts a long write to the Configuration registers are written a byte at a time. To write or erase a configuration cell, a TBLWT instruction can write a '1' or a '0' into the cell. For additional details on Flash programming, refer to Section 6.5 "Writing to Flash Program Memory".

| File    | Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3                | Bit 2                | Bit 1  | Bit 0  | Default/<br>Unprogrammed<br>Value |

|---------|----------|-------|-------|-------|--------|----------------------|----------------------|--------|--------|-----------------------------------|

| 300001h | CONFIG1H | IESO  | FCMEN |       |        | FOSC3                | FOSC2                | FOSC1  | FOSC0  | 00 0111                           |

| 300002h | CONFIG2L | -     | _     | _     | BORV1  | BORV0                | BOREN1               | BOREN0 | PWRTEN | 1 1111                            |

| 300003h | CONFIG2H |       |       |       | WDTPS3 | WDTPS2               | WDTPS1               | WDTPS0 | WDTEN  | 1 1111                            |

| 300005h | CONFIG3H | MCLRE |       |       | _      |                      | LPT10SC              | PBADEN | CCP2MX | 1011                              |

| 300006h | CONFIG4L | DEBUG | XINST |       | _      |                      | LVP                  |        | STVREN | 101-1                             |

| 300008h | CONFIG5L | _     | _     | _     | _      | CP3 <sup>(1)</sup>   | CP2 <sup>(1)</sup>   | CP1    | CP0    | 1111                              |

| 300009h | CONFIG5H | CPD   | CPB   | _     |        |                      | —                    |        | —      | 11                                |

| 30000Ah | CONFIG6L |       |       |       |        | WRT3 <sup>(1)</sup>  | WRT2 <sup>(1)</sup>  | WRT1   | WRT0   | 1111                              |

| 30000Bh | CONFIG6H | WRTD  | WRTB  | WRTC  | _      | _                    | —                    | _      | —      | 111                               |

| 30000Ch | CONFIG7L |       | _     |       |        | EBTR3 <sup>(1)</sup> | EBTR2 <sup>(1)</sup> | EBTR1  | EBTR0  | 1111                              |

| 30000Dh | CONFIG7H |       | EBTRB |       | _      | _                    | _                    | _      | _      | -1                                |

| 3FFFFEh | DEVID1   | DEV2  | DEV1  | DEV0  | REV4   | REV3                 | REV2                 | REV1   | REV0   | xxxx xxxx <sup>(2)</sup>          |

| 3FFFFFh | DEVID2   | DEV10 | DEV9  | DEV8  | DEV7   | DEV6                 | DEV5                 | DEV4   | DEV3   | xxxx xxxx <sup>(2)</sup>          |

TABLE 23-1: CONFIGURATION BITS AND DEVICE IDs

**Legend:** x = unknown, u = unchanged, — = unimplemented, q = value depends on condition.

Shaded cells are unimplemented, read as '0'.

**Note 1:** Unimplemented in PIC18F2420/4420 devices; maintain this bit set.

2: See Register 23-12 for DEVID1 values. DEVID registers are read-only and cannot be programmed by the user.

| ADDWFC                        | ADD W a                                                                                                                                                                  | ADD W and Carry bit to f                                                                                                   |                                                                                                                                                                      |  |  |  |  |  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                       | ADDWFC                                                                                                                                                                   | f {,d {,a}}                                                                                                                |                                                                                                                                                                      |  |  |  |  |  |

| Operands:                     | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                      |                                                                                                                            |                                                                                                                                                                      |  |  |  |  |  |

| Operation:                    | (W) + (f) +                                                                                                                                                              | $(C) \rightarrow dest$                                                                                                     |                                                                                                                                                                      |  |  |  |  |  |

| Status Affected:              | N,OV, C, D                                                                                                                                                               | C, Z                                                                                                                       |                                                                                                                                                                      |  |  |  |  |  |

| Encoding:                     | 0010                                                                                                                                                                     | 00da ff                                                                                                                    | ff ffff                                                                                                                                                              |  |  |  |  |  |

|                               | placed in V<br>placed in d<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank<br>If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode when<br>Section 24<br>Bit-Oriente | he BSR is use<br>(default).<br>Ind the extend<br>led, this instru<br>Literal Offset<br>never $f \le 95$ (5<br>.2.3 "Byte-O | he result is<br>bocation 'f'.<br>nk is selected.<br>ed to select the<br>led instruction<br>ction operates<br>Addressing<br>6Fh). See<br>riented and<br>ns in Indexed |  |  |  |  |  |

| Words:                        | 1                                                                                                                                                                        |                                                                                                                            |                                                                                                                                                                      |  |  |  |  |  |

| Cycles:                       | 1                                                                                                                                                                        |                                                                                                                            |                                                                                                                                                                      |  |  |  |  |  |

| Q Cycle Activity:             |                                                                                                                                                                          |                                                                                                                            |                                                                                                                                                                      |  |  |  |  |  |

| Q1                            | Q2                                                                                                                                                                       | Q3                                                                                                                         | Q4                                                                                                                                                                   |  |  |  |  |  |

| Decode                        | Read<br>register 'f'                                                                                                                                                     | Process<br>Data                                                                                                            | Write to destination                                                                                                                                                 |  |  |  |  |  |

| Example:                      | ADDWFC                                                                                                                                                                   | REG, 0,                                                                                                                    | 1                                                                                                                                                                    |  |  |  |  |  |

| Before Instruc                |                                                                                                                                                                          |                                                                                                                            |                                                                                                                                                                      |  |  |  |  |  |

| Carry bit<br>REG<br>W         | = 1<br>= 02h<br>= 4Dh                                                                                                                                                    |                                                                                                                            |                                                                                                                                                                      |  |  |  |  |  |

| After Instructio<br>Carry bit | on<br>= 0                                                                                                                                                                |                                                                                                                            |                                                                                                                                                                      |  |  |  |  |  |

| REG<br>W                      | = 0<br>= 02h<br>= 50h                                                                                                                                                    |                                                                                                                            |                                                                                                                                                                      |  |  |  |  |  |

| ANC               | DLW            | AN    | AND Literal with W |                         |     |    |          |  |  |  |

|-------------------|----------------|-------|--------------------|-------------------------|-----|----|----------|--|--|--|

| Syntax:           |                | AND   | DLW                | k                       |     |    |          |  |  |  |

| Oper              | ands:          | 0 ≤ I | k ≤ 255            |                         |     |    |          |  |  |  |

| Oper              | ation:         | (W)   | AND.               | $k \to W$               |     |    |          |  |  |  |

| Statu             | is Affected:   | N, Z  |                    |                         |     |    |          |  |  |  |

| Enco              | oding:         | 0     | 000                | 1011                    | kkk | k  | kkkk     |  |  |  |

| Desc              | cription:      |       |                    | ts of W a<br>'k'. The r |     |    |          |  |  |  |

| Word              | ls:            | 1     |                    |                         |     |    |          |  |  |  |

| Cycles:           |                | 1     |                    |                         |     |    |          |  |  |  |

| QC                | ycle Activity: |       |                    |                         |     |    |          |  |  |  |

|                   | Q1             | C     | Q2                 |                         |     |    | Q4       |  |  |  |

|                   | Decode         |       | literal<br>k'      | Proce<br>Dat            |     | Wr | ite to W |  |  |  |

| <u>Exan</u>       | nple:          | AND   | LW                 | 05Fh                    |     |    |          |  |  |  |

|                   | Before Instruc | ction |                    |                         |     |    |          |  |  |  |

| W =               |                | = /   | A3h                |                         |     |    |          |  |  |  |

| After Instruction |                | on    |                    |                         |     |    |          |  |  |  |

|                   |                |       |                    |                         |     |    |          |  |  |  |

| BCF                       | Bit Clear f                                                                                                                                                                                                                                                                                                                                                                                                                                           | BN                                                                              | Branch if Negative                                                                                                                                                                                                                                              |  |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                   | BCF f, b {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                         | Syntax:                                                                         | BN n                                                                                                                                                                                                                                                            |  |  |  |

| Operands:                 | $0 \le f \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                     | Operands:                                                                       | -128 ≤ n ≤ 127<br>if Negative bit is '1',<br>(PC) + 2 + 2n → PC                                                                                                                                                                                                 |  |  |  |

|                           | $0 \le b \le 7$ $a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                         | Operation:                                                                      |                                                                                                                                                                                                                                                                 |  |  |  |

| Operation:                | $0 \rightarrow f \le b >$                                                                                                                                                                                                                                                                                                                                                                                                                             | Status Affected:                                                                | None                                                                                                                                                                                                                                                            |  |  |  |

| Status Affected:          | None                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Encoding:                                                                       | 1110 0110 nnnn nnnn                                                                                                                                                                                                                                             |  |  |  |

| Encoding:                 | 1001 bbba ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                   | Description:                                                                    | If the Negative bit is '1', then the                                                                                                                                                                                                                            |  |  |  |

| Description:              | Bit 'b' in register 'f' is cleared.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. | Words:<br>Cycles:                                                               | program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction.<br>1<br>1(2) |  |  |  |

| Words:                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Q Cycle Activity:<br>If Jump:                                                   |                                                                                                                                                                                                                                                                 |  |  |  |

| Cycles:                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Q1                                                                              | Q2 Q3 Q4                                                                                                                                                                                                                                                        |  |  |  |

| Q Cycle Activity:         |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Decode                                                                          | Read literalProcessWrite to PC'n'Data                                                                                                                                                                                                                           |  |  |  |

| Q1<br>Decode              | Q2 Q3 Q4<br>Read Process Write<br>register 'f' Data register 'f'                                                                                                                                                                                                                                                                                                                                                                                      | No<br>operation                                                                 | No No No<br>operation operation                                                                                                                                                                                                                                 |  |  |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | If No Jump:<br>Q1                                                               | Q2 Q3 Q4                                                                                                                                                                                                                                                        |  |  |  |

| Example:                  | BCF FLAG REG, 7, 0                                                                                                                                                                                                                                                                                                                                                                                                                                    | Decode                                                                          | Q2 Q3 Q4<br>Read literal Process No                                                                                                                                                                                                                             |  |  |  |

| Before Instruc<br>FLAG_RI | tion<br>EG = C7h                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                 | 'n' Data operation                                                                                                                                                                                                                                              |  |  |  |

| After Instructio          |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Example:                                                                        | HERE BN Jump                                                                                                                                                                                                                                                    |  |  |  |

| FLAG_RI                   | EG = 47h                                                                                                                                                                                                                                                                                                                                                                                                                                              | Before Instruct<br>PC<br>After Instructio<br>If Negati<br>PC<br>If Negati<br>PC | = address (HERE)<br>on<br>ve = 1;<br>= address (Jump)                                                                                                                                                                                                           |  |  |  |

| NEGF             | Negate f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |      |      |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|--|--|--|

| Syntax:          | NEGF f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | {,a}  |      |      |  |  |  |

| Operands:        | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |      |      |  |  |  |

| Operation:       | $(\overline{f}) + 1 \rightarrow f$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |      |      |  |  |  |

| Status Affected: | N, OV, C, I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DC, Z |      |      |  |  |  |

| Encoding:        | 0110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 110a  | ffff | ffff |  |  |  |

| Description:     | Location 'f' is negated using two's<br>complement. The result is placed in the<br>data memory location 'f'.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |       |      |      |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |      |      |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |      |      |  |  |  |

| NOF                   | NOP No Operation |            |       |           |    |         |  |  |

|-----------------------|------------------|------------|-------|-----------|----|---------|--|--|

| Synta                 | ax:              | NOP        | NOP   |           |    |         |  |  |

| Oper                  | ands:            | None       |       |           |    |         |  |  |

| Oper                  | ation:           | No operati | on    |           |    |         |  |  |

| Status Affected: None |                  |            |       |           |    |         |  |  |

| Encoding:             |                  | 0000       | 0000  | 0000      |    | 0000    |  |  |

|                       |                  | 1111       | xxxx  | XXXX XXXX |    | xxxx    |  |  |

| Desc                  | ription:         | No operati | on.   |           |    |         |  |  |

| Word                  | ls:              | 1          |       |           |    |         |  |  |

| Cycle                 | es:              | 1          |       |           |    |         |  |  |

| QC                    | ycle Activity:   |            |       |           |    |         |  |  |

|                       | Q1               | Q2         | Q3 Q4 |           |    | Q4      |  |  |

|                       | Decode           | No         | No    | )         |    | No      |  |  |

|                       |                  | operation  | opera | tion      | ор | eration |  |  |

Example:

None.

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: NEGF REG, 1

| Before Instruction |      |      |       |

|--------------------|------|------|-------|

| REG =              | 0011 | 1010 | [3Ah] |

| After Instruction  |      |      |       |

| REG =              | 1100 | 0110 | [C6h] |

|       | .LW                  | Subroutir                                                                                                                            | ne Call Using                                                                                                                                                                                         | WREG                                                                                                                   |  |  |  |

|-------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Synta | ax:                  | CALLW                                                                                                                                | CALLW                                                                                                                                                                                                 |                                                                                                                        |  |  |  |

| Oper  | ands:                | None                                                                                                                                 |                                                                                                                                                                                                       |                                                                                                                        |  |  |  |

| Oper  | ation:               | (W) → PCL<br>(PCLATH) ·                                                                                                              | $(PC + 2) \rightarrow TOS,$<br>$(W) \rightarrow PCL,$<br>$(PCLATH) \rightarrow PCH,$<br>$(PCLATU) \rightarrow PCU$                                                                                    |                                                                                                                        |  |  |  |

| Statu | is Affected:         | None                                                                                                                                 |                                                                                                                                                                                                       |                                                                                                                        |  |  |  |

| Enco  | oding:               | 0000                                                                                                                                 | 0000 000                                                                                                                                                                                              | 01 0100                                                                                                                |  |  |  |

|       | rription             | pushed ont<br>contents of<br>existing val<br>contents of<br>latched into<br>respectively<br>executed as<br>new next in<br>Unlike CAL | turn address (I<br>o the return sta<br>W are written<br>ue is discarded<br>PCLATH and I<br>PCH and PCI<br>W. The second<br>s a NOP instruction<br>struction is feto<br>L, there is no<br>STATUS or BS | ack. Next, the<br>to PCL; the<br>d. Then, the<br>PCLATU are<br>J,<br>cycle is<br>ction while the<br>ched.<br>option to |  |  |  |

| Word  | ds:                  | 1                                                                                                                                    |                                                                                                                                                                                                       |                                                                                                                        |  |  |  |

| Cycle | es:                  | 2                                                                                                                                    |                                                                                                                                                                                                       |                                                                                                                        |  |  |  |

|       |                      |                                                                                                                                      |                                                                                                                                                                                                       |                                                                                                                        |  |  |  |

| QC    | ycle Activity:       |                                                                                                                                      |                                                                                                                                                                                                       |                                                                                                                        |  |  |  |

| QC    | ycle Activity:<br>Q1 | Q2                                                                                                                                   | Q3                                                                                                                                                                                                    | Q4                                                                                                                     |  |  |  |

| QC    |                      | Read                                                                                                                                 | PUSH PC to                                                                                                                                                                                            | No                                                                                                                     |  |  |  |

| QC    | Q1<br>Decode         | Read<br>WREG                                                                                                                         | PUSH PC to<br>stack                                                                                                                                                                                   | No<br>operation                                                                                                        |  |  |  |

| QC    | Q1                   | Read                                                                                                                                 | PUSH PC to                                                                                                                                                                                            | No                                                                                                                     |  |  |  |

| мον         | SF                                                                         | Move Ind                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | exed to                                  | f            |                                 |  |  |  |

|-------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------|---------------------------------|--|--|--|

| Synta       | x:                                                                         | MOVSF [                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | z <sub>s</sub> ], f <sub>d</sub>         |              |                                 |  |  |  |

| Operands:   |                                                                            | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $0 \le z_s \le 127$ $0 \le f_d \le 4095$ |              |                                 |  |  |  |

| Operation:  |                                                                            | ((FSR2) + :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $z_s) \rightarrow f_d$                   |              |                                 |  |  |  |

| Status      | Affected:                                                                  | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                          |              |                                 |  |  |  |