Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4520-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

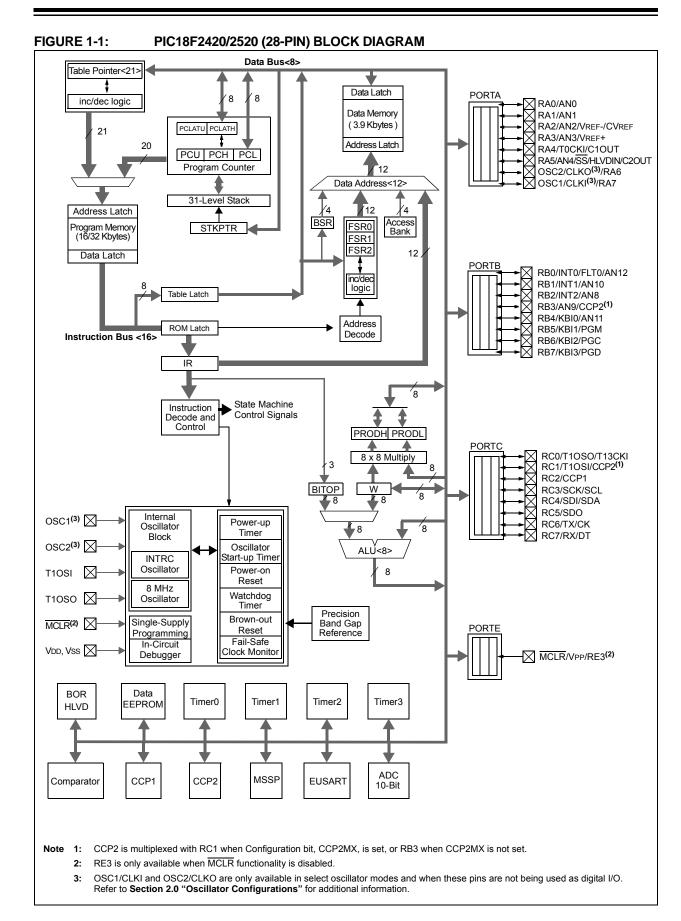

**TABLE 1-2:** PIC18F2420/2520 PINOUT I/O DESCRIPTIONS

|                       | Pin Nu         | ımber | Pin  | Buffer |                                                                                                                                  |

|-----------------------|----------------|-------|------|--------|----------------------------------------------------------------------------------------------------------------------------------|

| Pin Name              | SPDIP,<br>SOIC | QFN   | Туре |        | Description                                                                                                                      |

| MCLR/VPP/RE3<br>MCLR  | 1              | 26    | ı    | ST     | Master Clear (input) or programming voltage (input).  Master Clear (Reset) input. This pin is an active-low Reset to the device. |

| VPP                   |                |       | Р    |        | Programming voltage input.                                                                                                       |

| RE3                   |                |       | I    | ST     | Digital input.                                                                                                                   |

| OSC1/CLKI/RA7         | 9              | 6     |      |        | Oscillator crystal or external clock input.                                                                                      |

| OSC1                  |                |       | ı    | ST     | Oscillator crystal input or external clock source input.                                                                         |

| CLKI                  |                |       | ı    | CMOS   | function, OSC1. (See related OSC1/CLKI, OSC2/CLKO                                                                                |

| RA7                   |                |       | I/O  | TTL    | pins.)<br>General purpose I/O pin.                                                                                               |

| OSC2/CLKO/RA6<br>OSC2 | 10             | 7     | 0    | _      | Oscillator crystal or clock output. Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode.      |

| CLKO                  |                |       | 0    | _      | In RC mode, OSC2 pin outputs CLKO which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate.                    |

| RA6                   |                |       | I/O  | TTL    | General purpose I/O pin.                                                                                                         |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

= Output

CMOS = CMOS compatible input or output

= Input

= Power Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

TABLE 1-2: PIC18F2420/2520 PINOUT I/O DESCRIPTIONS (CONTINUED)

|                                                   | Pin Nu         |     | Pin             | Buffer                    | LOCKIF HONG (CONTINUED)                                                                                       |

|---------------------------------------------------|----------------|-----|-----------------|---------------------------|---------------------------------------------------------------------------------------------------------------|

| Pin Name                                          | SPDIP,<br>SOIC | QFN | Туре            |                           | Description                                                                                                   |

|                                                   |                |     |                 |                           | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |

| RB0/INT0/FLT0/AN12<br>RB0<br>INT0<br>FLT0<br>AN12 | 21             | 18  | I/O<br>I<br>I   | TTL<br>ST<br>ST<br>Analog | Digital I/O. External interrupt 0. PWM Fault input for CCP1. Analog input 12.                                 |

| RB1/INT1/AN10<br>RB1<br>INT1<br>AN10              | 22             | 19  | I/O<br>I<br>I   | TTL<br>ST<br>Analog       | Digital I/O.<br>External interrupt 1.<br>Analog input 10.                                                     |

| RB2/INT2/AN8<br>RB2<br>INT2<br>AN8                | 23             | 20  | I/O<br>I<br>I   | TTL<br>ST<br>Analog       | Digital I/O.<br>External interrupt 2.<br>Analog input 8.                                                      |

| RB3/AN9/CCP2<br>RB3<br>AN9<br>CCP2 <sup>(1)</sup> | 24             | 21  | I/O<br>I<br>I/O | TTL<br>Analog<br>ST       | Digital I/O.<br>Analog input 9.<br>Capture 2 input/Compare 2 output/PWM2 output.                              |

| RB4/KBI0/AN11<br>RB4<br>KBI0<br>AN11              | 25             | 22  | I/O<br>I<br>I   | TTL<br>TTL<br>Analog      | Digital I/O.<br>Interrupt-on-change pin.<br>Analog input 11.                                                  |

| RB5/KBI1/PGM<br>RB5<br>KBI1<br>PGM                | 26             | 23  | I/O<br>I<br>I/O | TTL<br>TTL<br>ST          | Digital I/O.<br>Interrupt-on-change pin.<br>Low-Voltage ICSP™ Programming enable pin.                         |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC                | 27             | 24  | I/O<br>I<br>I/O | TTL<br>TTL<br>ST          | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming clock pin.               |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD                | 28             | 25  | I/O<br>I<br>I/O | TTL<br>TTL<br>ST          | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data pin.                |

Legend: TTL = TTL compatible input

CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

I = Input

O = Output

P = Power

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

NOTES:

#### REGISTER 9-7: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| R/W-0       | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|-------------|-------|-----|-------|-------|--------|--------|--------|

| OSCFIE      | CMIE  | _   | EEIE  | BCLIE | HLVDIE | TMR3IE | CCP2IE |

| bit 7 bit C |       |     |       |       |        |        |        |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 OSCFIE: Oscillator Fail Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 6 **CMIE:** Comparator Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 5 Unimplemented: Read as '0'

bit 4 **EEIE:** Data EEPROM/Flash Write Operation Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 3 BCLIE: Bus Collision Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 2 **HLVDIE**: High/Low-Voltage Detect Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 1 TMR3IE: TMR3 Overflow Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 0 CCP2IE: CCP2 Interrupt Enable bit

1 = Enabled0 = Disabled

#### 12.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Reset on CCP Special Event Trigger

- · Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 12-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 12-2.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 12-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

#### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0 | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| RD16  | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

|  |    | <br> | - |

|--|----|------|---|

|  | зе |      |   |

|  |    |      |   |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 RD16: 16-Bit Read/Write Mode Enable bit

1 = Enables register read/write of Tlmer1 in one 16-bit operation

0 = Enables register read/write of Timer1 in two 8-bit operations

bit 6 T1RUN: Timer1 System Clock Status bit

1 = Device clock is derived from Timer1 oscillator0 = Device clock is derived from another source

bit 5-4 T1CKPS<1:0>: Timer1 Input Clock Prescale Select bits

11 = 1:8 Prescale value 10 = 1:4 Prescale value 01 = 1:2 Prescale value 00 = 1:1 Prescale value

bit 3 T10SCEN: Timer1 Oscillator Enable bit

1 = Timer1 oscillator is enabled0 = Timer1 oscillator is shut off

The oscillator inverter and feedback resistor are turned off to eliminate power drain.

bit 2 T1SYNC: Timer1 External Clock Input Synchronization Select bit

When TMR1CS = 1:

1 = Do not synchronize external clock input

0 = Synchronize external clock input

When TMR1CS = 0:

This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0.

bit 1 TMR1CS: Timer1 Clock Source Select bit

1 = External clock from pin RC0/T10SO/T13CKI (on the rising edge)

0 = Internal clock (Fosc/4)

bit 0 TMR1ON: Timer1 On bit

1 = Enables Timer1

0 = Stops Timer1

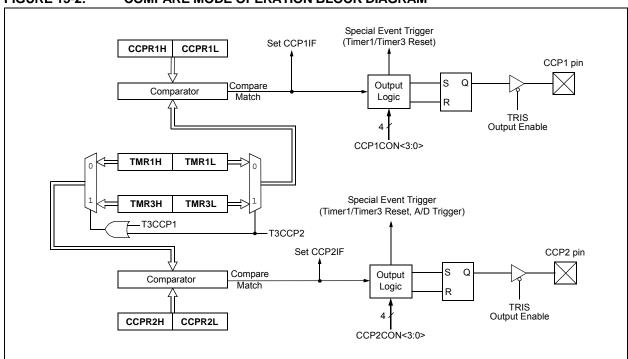

#### 15.3 Compare Mode

In Compare mode, the 16-bit CCPRx register value is constantly compared against either the TMR1 or TMR3 register pair value. When a match occurs, the CCPx pin can be:

- · driven high

- · driven low

- · toggled (high-to-low or low-to-high)

- remain unchanged (that is, reflects the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCPxM<3:0>). At the same time, the interrupt flag bit, CCPxIF, is set.

#### 15.3.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the appropriate TRIS bit.

Note:

Clearing the CCP2CON register will force the RB3 or RC1 compare output latch (depending on device configuration) to the default low level. This is not the PORTB or PORTC I/O data latch.

#### 15.3.2 TIMER1/TIMER3 MODE SELECTION

Timer1 and/or Timer3 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

### 15.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the corresponding CCPx pin is not affected. A CCP interrupt is generated when the CCPxIF interrupt flag is set while the CCPxIE bit is set.

#### 15.3.4 SPECIAL EVENT TRIGGER

Both CCP modules are equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode (CCPxM<3:0> = 1011).

For either CCP module, the Special Event Trigger resets the Timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPRx registers to serve as a programmable Period register for either timer.

The Special Event Trigger for CCP2 can also start an A/D conversion. In order to do this, the A/D Converter must already be enabled.

FIGURE 15-2: COMPARE MODE OPERATION BLOCK DIAGRAM

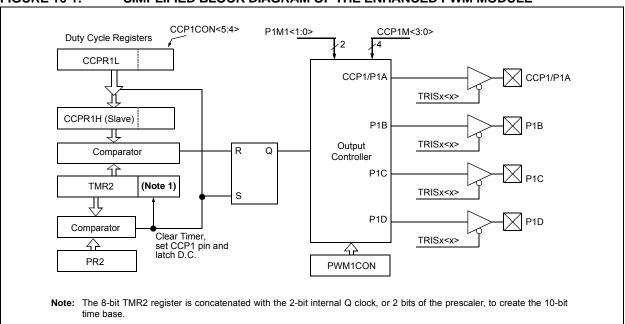

#### 16.4 Enhanced PWM Mode

The Enhanced PWM mode provides additional PWM output options for a broader range of control applications. The module is a backward compatible version of the standard CCP module and offers up to four outputs, designated P1A through P1D. Users are also able to select the polarity of the signal (either active-high or active-low). The module's output mode and polarity are configured by setting the P1M<1:0> and CCP1M<3:0> bits of the CCP1CON register.

Figure 16-1 shows a simplified block diagram of PWM operation. All control registers are double-buffered and are loaded at the beginning of a new PWM cycle (the period boundary when Timer2 resets) in order to prevent glitches on any of the outputs. The exception is the PWM Dead-Band Delay register, PWM1CON, which is loaded at either the duty cycle boundary or the period boundary (whichever comes first). Because of the buffering, the module waits until the assigned timer resets instead of starting immediately. This means that Enhanced PWM waveforms do not exactly match the standard PWM waveforms, but are instead offset by one full instruction cycle (4 Tosc).

As before, the user must manually configure the appropriate TRIS bits for output.

#### 16.4.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following equation.

#### **EQUATION 16-1:**

PWM Period =

$$[(PR2) + 1] \cdot 4 \cdot TOSC \cdot$$

(TMR2 Prescale Value)

PWM frequency is defined as 1/[PWM period]. When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- · TMR2 is cleared

- The CCP1 pin is set (if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is copied from CCPR1L into CCPR1H

Note: The Timer2 postscaler (see Section 13.0 "Timer2 Module") is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

FIGURE 16-1: SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODULE

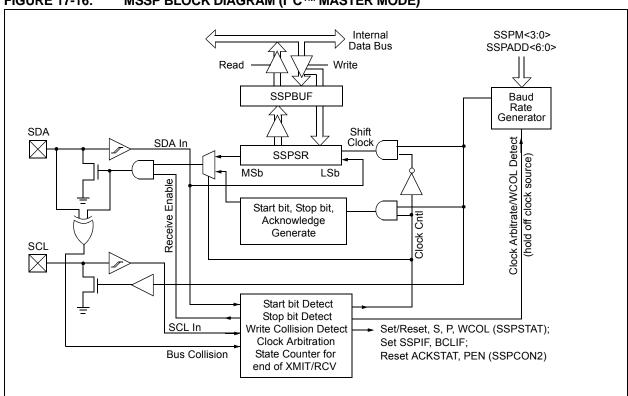

#### 17.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $\rm I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause the MSSP Interrupt Flag bit, SSPIF, to be set (MSSP interrupt, if enabled):

· Start condition

Note:

- Stop condition

- · Data transfer byte transmitted/received

- · Acknowledge transmit

- · Repeated Start

FIGURE 17-16: MSSP BLOCK DIAGRAM (I<sup>2</sup>C™ MASTER MODE)

### **EXAMPLE 18-1: CALCULATING BAUD RATE ERROR**

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG:

Desired Baud Rate = Fosc/(64 ([SPBRGH:SPBRG] + 1))

Solving for SPBRGH:SPBRG:

X = ((Fosc/Desired Baud Rate)/64) - 1

= ((16000000/9600)/64) - 1

= [25.042] = 25

Calculated Baud Rate = 16000000/(64(25+1))

= 9615

Error = (Calculated Baud Rate – Desired Baud Rate)/Desired Baud Rate

= (9615 - 9600)/9600 = 0.16%

### TABLE 18-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name    | Bit 7    | Bit 6                                         | Bit 5       | Bit 4       | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset Values on page |

|---------|----------|-----------------------------------------------|-------------|-------------|-------|-------|-------|-------|----------------------|

| TXSTA   | CSRC     | TX9                                           | TXEN        | SYNC        | SENDB | BRGH  | TRMT  | TX9D  | 51                   |

| RCSTA   | SPEN     | RX9                                           | SREN        | CREN        | ADDEN | FERR  | OERR  | RX9D  | 51                   |

| BAUDCON | ABDOVF   | RCIDL                                         | RXDTP       | TXCKP       | BRG16 | _     | WUE   | ABDEN | 51                   |

| SPBRGH  | EUSART B | EUSART Baud Rate Generator Register High Byte |             |             |       |       |       |       | 51                   |

| SPBRG   | EUSART B | aud Rate G                                    | Senerator R | egister Low | Byte  |       |       |       | 51                   |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the BRG.

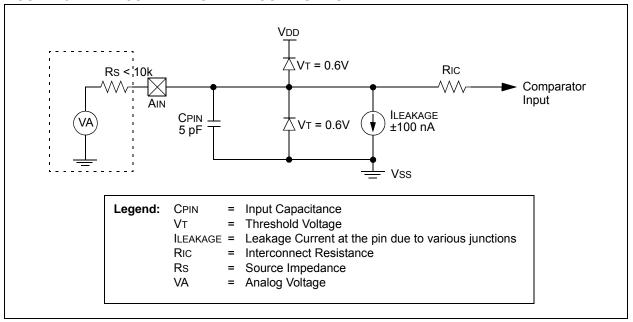

# 20.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 20-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this

range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of 10  $k\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

#### FIGURE 20-4: COMPARATOR ANALOG INPUT MODEL

TABLE 20-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Name   | Bit 7                 | Bit 6                 | Bit 5    | Bit 4                                                    | Bit 3    | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|-----------------------|-----------------------|----------|----------------------------------------------------------|----------|--------|--------|--------|----------------------------|

| CMCON  | C2OUT                 | C10UT                 | C2INV    | C1INV                                                    | CIS      | CM2    | CM1    | CM0    | 51                         |

| CVRCON | CVREN                 | CVROE                 | CVRR     | CVRSS                                                    | CVR3     | CVR2   | CVR1   | CVR0   | 51                         |

| INTCON | GIE/GIEH              | PEIE/GIEL             | TMR0IE   | INT0IE                                                   | RBIE     | TMR0IF | INT0IF | RBIF   | 52                         |

| PIR2   | OSCFIF                | CMIF                  | _        | EEIF                                                     | BCLIF    | HLVDIF | TMR3IF | CCP2IF | 52                         |

| PIE2   | OSCFIE                | CMIE                  | _        | EEIE                                                     | BCLIE    | HLVDIE | TMR3IE | CCP2IE | 52                         |

| IPR2   | OSCFIP                | CMIP                  | _        | EEIP                                                     | BCLIP    | HLVDIP | TMR3IP | CCP2IP | 52                         |

| PORTA  | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5      | RA4                                                      | RA3      | RA2    | RA1    | RA0    | 52                         |

| LATA   | LATA7 <sup>(1)</sup>  | LATA6 <sup>(1)</sup>  | PORTA Da | PORTA Data Latch Register (Read and Write to Data Latch) |          |        |        |        |                            |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | PORTA Da | ata Direction                                            | Register |        |        |        | 52                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

**Note 1:** PORTA<7:6> and their direction and latch bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits are read as '0'.

#### REGISTER 23-8: CONFIG6L: CONFIGURATION REGISTER 6 LOW (BYTE ADDRESS 30000Ah)

| U-0         | U-0 | U-0 | U-0 | R/C-1               | R/C-1               | R/C-1 | R/C-1 |

|-------------|-----|-----|-----|---------------------|---------------------|-------|-------|

| _           | _   | _   | _   | WRT3 <sup>(1)</sup> | WRT2 <sup>(1)</sup> | WRT1  | WRT0  |

| bit 7 bit 0 |     |     |     |                     |                     |       |       |

Legend:

R = Readable bit C = Clearable bit U = Unimplemented bit, read as '0'

-n = Value when device is unprogrammed u = Unchanged from programmed state

bit 7-4 **Unimplemented:** Read as '0' bit 3 **WRT3:** Write Protection bit<sup>(1)</sup>

1 = Block 3 (006000-007FFFh) not write-protected 0 = Block 3 (006000-007FFFh) write-protected

bit 2 WRT2: Write Protection bit<sup>(1)</sup>

1 = Block 2 (004000-005FFFh) not write-protected 0 = Block 2 (004000-005FFFh) write-protected

bit 1 WRT1: Write Protection bit

1 = Block 1 (002000-003FFFh) not write-protected 0 = Block 1 (002000-003FFFh) write-protected

bit 0 WRT0: Write Protection bit

1 = Block 0 (000800-001FFFh) not write-protected 0 = Block 0 (000800-001FFFh) write-protected

Note 1: Unimplemented in PIC18F2420/4420 devices; maintain this bit set.

#### REGISTER 23-9: CONFIG6H: CONFIGURATION REGISTER 6 HIGH (BYTE ADDRESS 30000Bh)

| R/C-1 | R/C-1 | R/C-1               | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|---------------------|-----|-----|-----|-----|-------|

| WRTD  | WRTB  | WRTC <sup>(1)</sup> | _   | _   | _   | _   | _     |

| bit 7 | •     | •                   | •   | •   |     |     | bit 0 |

Legend:

R = Readable bit C = Clearable bit U = Unimplemented bit, read as '0'

-n = Value when device is unprogrammed u = Unchanged from programmed state

bit 7 WRTD: Data EEPROM Write Protection bit

1 = Data EEPROM not write-protected 0 = Data EEPROM write-protected

bit 6 WRTB: Boot Block Write Protection bit

1 = Boot block (000000-0007FFh) not write-protected 0 = Boot block (000000-0007FFh) write-protected

bit 5 WRTC: Configuration Register Write Protection bit<sup>(1)</sup>

1 = Configuration registers (300000-3000FFh) not write-protected 0 = Configuration registers (300000-3000FFh) write-protected

bit 4-0 **Unimplemented:** Read as '0'

Note 1: This bit is read-only in normal execution mode; it can be written only in Program mode.

TABLE 24-2: PIC18FXXXX INSTRUCTION SET (CONTINUED)

|           |        | 1 10 101 70 70 70 110 110 110 0 |        | •    | ,        | ,        |      |                 |       |

|-----------|--------|---------------------------------|--------|------|----------|----------|------|-----------------|-------|

| Mnem      | onic,  | Description                     | 0      | 16   | -Bit Ins | truction | Word | Status          | Nata  |

| Operands  |        | Description                     | Cycles | MSb  |          |          | LSb  | Affected        | Notes |

| LITERAL ( | OPERAT | TIONS                           |        |      |          |          |      |                 |       |

| ADDLW     | k      | Add Literal and WREG            | 1      | 0000 | 1111     | kkkk     | kkkk | C, DC, Z, OV, N |       |

| ANDLW     | k      | AND Literal with WREG           | 1      | 0000 | 1011     | kkkk     | kkkk | Z, N            |       |

| IORLW     | k      | Inclusive OR Literal with WREG  | 1      | 0000 | 1001     | kkkk     | kkkk | Z, N            |       |

| LFSR      | f, k   | Move Literal (12-bit)2nd word   | 2      | 1110 | 1110     | OOff     | kkkk | None            |       |

|           |        | to FSR(f) 1st word              |        | 1111 | 0000     | kkkk     | kkkk |                 |       |

| MOVLB     | k      | Move Literal to BSR<3:0>        | 1      | 0000 | 0001     | 0000     | kkkk | None            |       |

| MOVLW     | k      | Move Literal to WREG            | 1      | 0000 | 1110     | kkkk     | kkkk | None            |       |

| MULLW     | k      | Multiply Literal with WREG      | 1      | 0000 | 1101     | kkkk     | kkkk | None            |       |

| RETLW     | k      | Return with Literal in WREG     | 2      | 0000 | 1100     | kkkk     | kkkk | None            |       |

| SUBLW     | k      | Subtract WREG from Literal      | 1      | 0000 | 1000     | kkkk     | kkkk | C, DC, Z, OV, N |       |

| XORLW     | k      | Exclusive OR Literal with WREG  | 1      | 0000 | 1010     | kkkk     | kkkk | Z, N            |       |

| DATA MEN  | MORY ← | PROGRAM MEMORY OPERATION        | NS     |      |          |          |      |                 |       |

| TBLRD*    |        | Table Read                      | 2      | 0000 | 0000     | 0000     | 1000 | None            |       |

| TBLRD*+   |        | Table Read with Post-Increment  |        | 0000 | 0000     | 0000     | 1001 | None            |       |

| TBLRD*-   |        | Table Read with Post-Decrement  |        | 0000 | 0000     | 0000     | 1010 | None            |       |

| TBLRD+*   |        | Table Read with Pre-Increment   |        | 0000 | 0000     | 0000     | 1011 | None            |       |

| TBLWT*    |        | Table Write                     | 2      | 0000 | 0000     | 0000     | 1100 | None            |       |

| TBLWT*+   |        | Table Write with Post-Increment |        | 0000 | 0000     | 0000     | 1101 | None            |       |

| TBLWT*-   |        | Table Write with Post-Decrement |        | 0000 | 0000     | 0000     | 1110 | None            |       |

| TBLWT+*   |        | Table Write with Pre-Increment  |        | 0000 | 0000     | 0000     | 1111 | None            |       |

Note 1: When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

- 2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

- 3: If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

- 4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| ANDWF            | AND W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | ANDWF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ dest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Status Affected: | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Encoding:        | 0001 01da ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Description:     | The contents of W are ANDed with register 'f'. If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in register 'f' (default). If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the GPR bank (default). If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 24.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Q1     | Q2           | Q3      | Q4          |  |

|--------|--------------|---------|-------------|--|

| Decode | Read         | Process | Write to    |  |

|        | register 'f' | Data    | destination |  |

Example: ANDWF REG, 0, 0

1

Before Instruction

Cycles:

Q Cycle Activity:

W 17h REG C2h

After Instruction W

02h REG C2h BC **Branch if Carry**

Syntax: BC n

$-128 \le n \le 127$ Operands:

Operation: if Carry bit is '1',  $(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1110 0010 nnnn nnnn Description: If the Carry bit is '1', then the program

will branch.

The 2's complement number '2n' is added to the PC. Since the PC will have

incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a

two-cycle instruction.

Words: 1

Cycles: 1(2)

Q Cycle Activity:

If Jump:

| Q1        | Q2           | Q3        | Q4          |

|-----------|--------------|-----------|-------------|

| Decode    | Read literal | Process   | Write to PC |

|           | 'n'          | Data      |             |

| No        | No           | No        | No          |

| operation | operation    | operation | operation   |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | ʻn'          | Data    | operation |

Example: HERE BC5

Before Instruction

PC address (HERE)

After Instruction

If Carry PC

address (HERE + 12)

If Carry PC =

address (HERE + 2)

| BTG               | Bit Toggle f                                                                                                                                                                                                                                                                                                                                                                                                                         |         |      |      |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|------|--|

| Syntax:           | BTG f, b {                                                                                                                                                                                                                                                                                                                                                                                                                           | ,a}     |      |      |  |

| Operands:         | $0 \le f \le 255$<br>$0 \le b < 7$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                  |         |      |      |  |

| Operation:        | $(\overline{f < b >}) \rightarrow f$                                                                                                                                                                                                                                                                                                                                                                                                 | <b></b> |      |      |  |

| Status Affected:  | None                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |      |      |  |

| Encoding:         | 0111                                                                                                                                                                                                                                                                                                                                                                                                                                 | bbba    | ffff | ffff |  |

|                   | Bit 'b' in data memory location 'f' is inverted.  If 'a' is '0', the Access Bank is selected.  If 'a' is '1', the BSR is used to select the GPR bank (default).  If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See  Section 24.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. |         |      |      |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |      |      |  |

| Cycles:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |      |      |  |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |      |      |  |

|          | register | register 'f' Da |       | ata |   |  |

|----------|----------|-----------------|-------|-----|---|--|

|          |          |                 |       |     |   |  |

| Example: | BTG      | PC              | ORTC, | 4,  | 0 |  |

Q2

Read

Q3

**Process**

Q4 Write

register 'f'

Before Instruction:

Q1

Decode

PORTC = 0111 0101 **[75h]**

After Instruction:

PORTC = 0110 0101 [65h]

#### BOV **Branch if Overflow**

Syntax: BOV n Operands:  $-128 \le n \le 127$ Operation: if Overflow bit is '1', (PC) + 2 +  $2n \rightarrow PC$

Status Affected: None

Encoding: 1110 0100 nnnn nnnn Description: If the Overflow bit is '1', then the

program will branch.

The 2's complement number, '2n', is added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a

two-cycle instruction.

Words: 1 Cycles: 1(2)

Q Cycle Activity:

If Jump:

| Q1        | Q2           | Q3        | Q4          |

|-----------|--------------|-----------|-------------|

| Decode    | Read literal | Process   | Write to PC |

|           | ʻn'          | Data      |             |

| No        | No           | No        | No          |

| operation | operation    | operation | operation   |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | ʻn'          | Data    | operation |

Example: HERE BOV Jump

Before Instruction

PC address (HERE)

After Instruction

If Overflow PC

1; address (Jump)

If Overflow PC address (HERE + 2)

| COMF              | Complem                                                                                                                                                                                | Complement f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|

| Syntax:           | COMF f                                                                                                                                                                                 | {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |  |  |  |  |

| Operands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |  |  |  |  |

| Operation:        | $(\overline{f}) \to dest$                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |  |  |  |  |

| Status Affected:  | N, Z                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |  |  |  |  |

| Encoding:         | 0001                                                                                                                                                                                   | 11da ff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ff ffff              |  |  |  |  |

| Description:      | complemer<br>stored in W<br>stored back<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank<br>If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode when<br>Section 24<br>Bit-Oriente | The contents of register 'f' are complemented. If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in register 'f' (default). If 'a' is '0', the Access Bank is selected If 'a' is '1', the BSR is used to select the GPR bank (default). If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 24.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. |                      |  |  |  |  |

| Words:            | 1                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |  |  |  |  |

| Q Cycle Activity: |                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |  |  |  |  |

| Q1                | Q2                                                                                                                                                                                     | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Q4                   |  |  |  |  |

| Decode            | Read register 'f'                                                                                                                                                                      | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Write to destination |  |  |  |  |

| Example:          | CC         | OMF | REG, | Ο, | 0 |

|-------------------|------------|-----|------|----|---|

| Before Instruc    | ction<br>= | 13h |      |    |   |

| After Instruction |            |     |      |    |   |

| REG               | =          | 13h |      |    |   |

| W                 | =          | ECh |      |    |   |

| CPF    | SEQ                     | Compare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | f with W, Sk                                             | ip if f = W       |  |  |  |  |  |  |

|--------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------|--|--|--|--|--|--|

| Synta  | ax:                     | CPFSEQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | f {,a}                                                   |                   |  |  |  |  |  |  |

| Oper   | ands:                   | $0 \le f \le 255$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |                   |  |  |  |  |  |  |

| Oper   | ation:                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (f) – (W),<br>skip if (f) = (W)<br>(unsigned comparison) |                   |  |  |  |  |  |  |

| Statu  | s Affected:             | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          |                   |  |  |  |  |  |  |

| Enco   | ding:                   | 0110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 001a fff                                                 | f ffff            |  |  |  |  |  |  |

| Desc   | ription:                | Compares the contents of data memory location 'f' to the contents of W by performing an unsigned subtraction. If 'f' = W, then the fetched instruction is discarded and a NOP is executed instead, making this a two-cycle instruction. If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the GPR bank (default). If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 24.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed |                                                          |                   |  |  |  |  |  |  |

|        |                         | Literal Offs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | set Mode" for                                            | details.          |  |  |  |  |  |  |

| Word   | ls:                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |                   |  |  |  |  |  |  |

| Cycle  | es:                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ycles if skip an<br>a 2-word instru                      |                   |  |  |  |  |  |  |

| QC     | ycle Activity:          | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |                   |  |  |  |  |  |  |

|        | Q1                      | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Q3                                                       | Q4                |  |  |  |  |  |  |

|        | Decode                  | Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Process                                                  | No                |  |  |  |  |  |  |

| 16 -1. | ·                       | register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Data                                                     | operation         |  |  |  |  |  |  |

| lf sk  | ιρ.<br>Q1               | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Q3                                                       | 04                |  |  |  |  |  |  |

|        | No                      | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | No No                                                    | Q4<br>No          |  |  |  |  |  |  |

|        | operation               | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | operation                                                | operation         |  |  |  |  |  |  |

| If sk  | ip and followed         | d by 2-word in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | struction:                                               |                   |  |  |  |  |  |  |

|        | Q1                      | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Q3                                                       | Q4                |  |  |  |  |  |  |

|        | No                      | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | No                                                       | No                |  |  |  |  |  |  |

|        | operation<br>No         | operation<br>No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | operation<br>No                                          | operation<br>No   |  |  |  |  |  |  |

|        | operation               | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | operation                                                | operation         |  |  |  |  |  |  |

| Exan   | nple:<br>Before Instruc | HERE NEQUAL EQUAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CPFSEQ REG                                               |                   |  |  |  |  |  |  |

|        | PC Addre                | ess = HE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RE                                                       | PC Address = HERE |  |  |  |  |  |  |

W REG After Instruction If REG

> If REG PC

W;

Address (EQUAL)

Address (NEQUAL)

| DECFSZ                                                | Decreme                                                                                                                                                                                                | nt f, Skip if (                                                                   | D                                                                                                                                                                                                   | DCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SNZ                                                 | Decreme                                                                                                                                                                                              | nt f, Skip if N                      | Not 0          |