Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4520-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

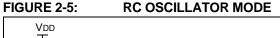

## 2.4 RC Oscillator

For timing insensitive applications, the "RC" and "RCIO" device options offer additional cost savings. The actual oscillator frequency is a function of several factors:

- supply voltage

- values of the external resistor (REXT) and capacitor (CEXT)

- operating temperature

Given the same device, operating voltage and temperature and component values, there will also be unit-to-unit frequency variations. These are due to factors such as:

- normal manufacturing variation

- difference in lead frame capacitance between package types (especially for low CEXT values)

- variations within the tolerance of limits of  $\ensuremath{\mathsf{REXT}}$  and  $\ensuremath{\mathsf{CEXT}}$

In the RC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 2-5 shows how the R/C combination is connected.

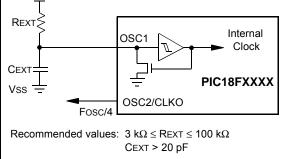

The RCIO Oscillator mode (Figure 2-6) functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

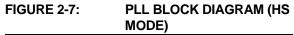

## 2.5 PLL Frequency Multiplier

A Phase Locked Loop (PLL) circuit is provided as an option for users who wish to use a lower frequency oscillator circuit or to clock the device up to its highest rated frequency from a crystal oscillator. This may be useful for customers who are concerned with EMI due to high-frequency crystals or users who require higher clock speeds from an internal oscillator.

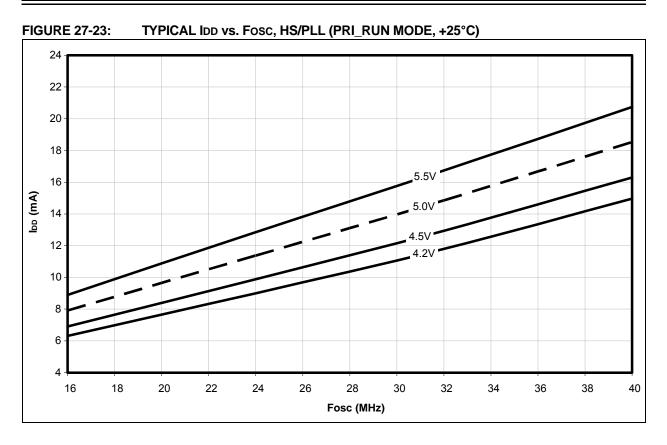

### 2.5.1 HSPLL OSCILLATOR MODE

The HSPLL mode makes use of the HS Oscillator mode for frequencies up to 10 MHz. A PLL then multiplies the oscillator output frequency by 4 to produce an internal clock frequency up to 40 MHz. The PLLEN bit is not available in this oscillator mode.

The PLL is only available to the crystal oscillator when the FOSC<3:0> Configuration bits are programmed for HSPLL mode (= 0110).

## 2.5.2 PLL AND INTOSC

The PLL is also available to the internal oscillator block in selected oscillator modes. In this configuration, the PLL is enabled in software and generates a clock output of up to 32 MHz. The operation of INTOSC with the PLL is described in **Section 2.6.4** "**PLL in INTOSC Modes**".

### 2.8 Effects of Power-Managed Modes on the Various Clock Sources

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin, if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_IDLE), the Timer1 oscillator is operating and providing the device clock. The Timer1 oscillator may also run in all power-managed modes if required to clock Timer1 or Timer3.

In internal oscillator modes (RC\_RUN and RC\_IDLE), the internal oscillator block provides the device clock source. The 31 kHz INTRC output can be used directly to provide the clock and may be enabled to support various special features, regardless of the powermanaged mode (see Section 23.2 "Watchdog Timer (WDT)", Section 23.3 "Two-Speed Start-up" and Section 23.4 "Fail-Safe Clock Monitor" for more information on WDT, Fail-Safe Clock Monitor and Two-Speed Start-up). The INTOSC output at 8 MHz may be used directly to clock the device or may be divided down by the postscaler. The INTOSC output is disabled if the clock is provided directly from the INTRC output.

If Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support a Real-Time Clock. Other features may be operating that do not require a device clock source (i.e., MSSP slave, PSP, INTx pins and others). Peripherals that may add significant current consumption are listed in **Section 26.2 "DC Characteristics".**

# 2.9 Power-up Delays

Power-up delays are controlled by two timers so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 4.5 "Device Reset Timers"**.

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on power-up (parameter 33, Table 26-10). It is enabled by clearing (= 0) the PWRTEN Configuration bit.

The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (LP, XT and HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

When the HSPLL Oscillator mode is selected, the device is kept in Reset for an additional 2 ms, following the HS mode OST delay, so the PLL can lock to the incoming clock frequency.

There is a delay of interval, TCSD (parameter 38, Table 26-10), following POR, while the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the EC, RC or INTIO modes are used as the primary clock source.

| OSC Mode      | OSC1 Pin                                              | OSC2 Pin                                              |  |  |

|---------------|-------------------------------------------------------|-------------------------------------------------------|--|--|

| RC, INTIO1    | Floating, external resistor should pull high          | At logic low (clock/4 output)                         |  |  |

| RCIO          | Floating, external resistor should pull high          | Configured as PORTA, bit 6                            |  |  |

| INTIO2        | Configured as PORTA, bit 7                            | Configured as PORTA, bit 6                            |  |  |

| ECIO          | Floating, pulled by external clock                    | Configured as PORTA, bit 6                            |  |  |

| EC            | Floating, pulled by external clock                    | At logic low (clock/4 output)                         |  |  |

| LP, XT and HS | Feedback inverter disabled at quiescent voltage level | Feedback inverter disabled at quiescent voltage level |  |  |

TABLE 2-3:OSC1 AND OSC2 PIN STATES IN SLEEP MODE

Note: See Table 4-2 in Section 4.0 "Reset" for time-outs due to Sleep and MCLR Reset.

| REGISTER 6-1: | EECON1: EEPROM CONTROL REGISTER 1 |

|---------------|-----------------------------------|

|---------------|-----------------------------------|

| R/W-x | R/W-x | U-0 | R/W-0 | R/W-x                | R/W-0 | R/S-0 | R/S-0 |

|-------|-------|-----|-------|----------------------|-------|-------|-------|

| EEPGD | CFGS  | —   | FREE  | WRERR <sup>(1)</sup> | WREN  | WR    | RD    |

| bit 7 |       |     |       |                      |       |       | bit 0 |

| Legend:           | S = Settable bit (cannot be cleared in software) |                                    |                    |  |  |

|-------------------|--------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                 | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                 | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 7   | EEPGD: Flash Program or Data EEPROM Memory Select bit                                                                                                                                                                                                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Access Flash program memory                                                                                                                                                                                                                                         |

|         | 0 = Access data EEPROM memory                                                                                                                                                                                                                                           |

| bit 6   | CFGS: Flash Program/Data EEPROM or Configuration Select bit                                                                                                                                                                                                             |

|         | 1 = Access Configuration registers                                                                                                                                                                                                                                      |

|         | 0 = Access Flash program or data EEPROM memory                                                                                                                                                                                                                          |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                                                              |

| bit 4   | FREE: Flash Row Erase Enable bit                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Erase the program memory row addressed by TBLPTR on the next WR command (cleared by<br/>completion of erase operation)</li> </ul>                                                                                                                          |

|         | 0 = Perform write only                                                                                                                                                                                                                                                  |

| bit 3   | WRERR: Flash Program/Data EEPROM Error Flag bit <sup>(1)</sup>                                                                                                                                                                                                          |

|         | <ul> <li>1 = A write operation is prematurely terminated (any Reset during self-timed programming in normal<br/>operation, or an improper write attempt)</li> </ul>                                                                                                     |

|         | 0 = The write operation completed                                                                                                                                                                                                                                       |

| bit 2   | WREN: Flash Program/Data EEPROM Write Enable bit                                                                                                                                                                                                                        |

|         | 1 = Allows write cycles to Flash program/data EEPROM                                                                                                                                                                                                                    |

|         | 0 = Inhibits write cycles to Flash program/data EEPROM                                                                                                                                                                                                                  |

| bit 1   | WR: Write Control bit                                                                                                                                                                                                                                                   |

|         | <ul> <li>1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle<br/>(The operation is self-timed and the bit is cleared by hardware once write is complete. The WR bit<br/>can only be set (not cleared) in software.)</li> </ul> |

|         | 0 = Write cycle to the EEPROM is complete                                                                                                                                                                                                                               |

| bit 0   | RD: Read Control bit                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit can only<br/>be set (not cleared) in software. RD bit cannot be set when EEPGD = 1 or CFGS = 1.)</li> </ul>                                                          |

|         | 0 = Does not initiate an EEPROM read                                                                                                                                                                                                                                    |

| Note 1: | When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error                                                                                                                                                                          |

**Note 1:** When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error condition.

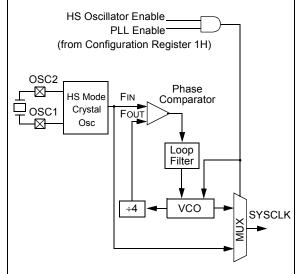

# 6.5 Writing to Flash Program Memory

The minimum programming block is 16 words or 32 bytes. Word or byte programming is not supported. Table writes are used internally to load the holding registers needed to program the Flash memory. There are 32 holding registers used by the table writes for programming.

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction may need to be executed 32 times for each programming operation. All of the table write operations will essentially be short writes because only the holding registers are written. At the end of updating the 32 holding registers, the EECON1 register must be written to in order to start the programming operation with a long write. The long write is necessary for programming the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

The EEPROM on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

Note: The default value of the holding registers on device Resets and after write operations is FFh. A write of FFh to a holding register does not modify that byte. This means individual bytes of program memory may be modified, provided that the change does not attempt to change any bit from a '0' to a '1'. When modifying individual bytes, it is not necessary to load all 32 holding registers before executing a write operation.

### FIGURE 6-5: TABLE WRITES TO FLASH PROGRAM MEMORY

#### 6.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read 64 bytes into RAM.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer register with address being erased.

- 4. Execute the row erase procedure.

- 5. Load Table Pointer register with address of first byte being written.

- 6. Write the 32 bytes into the holding registers with auto-increment.

- 7. Set the EECON1 register for the write operation:

- set EEPGD bit to point to program memory;

- · clear the CFGS bit to access program memory;

- · set WREN to enable byte writes.

- 8. Disable interrupts.

- 9. Write 55h to EECON2.

- 10. Write 0AAh to EECON2.

- 11. Set the WR bit. This will begin the write cycle.

- 12. The CPU will stall for duration of the write (about 2 ms using internal timer).

- 13. Re-enable interrupts.

- 14. Verify the memory (table read).

This procedure will require about 6 ms to update one row of 64 bytes of memory. An example of the required code is given in Example 6-3.

**Note:** Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the 32 bytes in the holding register.

### 9.4 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Priority registers (IPR1 and IPR2). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

#### REGISTER 9-8: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

|       | TMR1IP |

|-------|--------|

| bit 7 | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

|                   |                  |                       |                    |

| bit 7          | <b>PSPIP:</b> Parallel Slave Port Read/Write Interrupt Priority bit <sup>(1)</sup>                                                                                                                                                                                                                                                     |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | 1 = High priority<br>0 = Low priority                                                                                                                                                                                                                                                                                                  |

| bit 6          | ADIP: A/D Converter Interrupt Priority bit                                                                                                                                                                                                                                                                                             |

|                | <ul><li>1 = High priority</li><li>0 = Low priority</li></ul>                                                                                                                                                                                                                                                                           |

| bit 5          | RCIP: EUSART Receive Interrupt Priority bit                                                                                                                                                                                                                                                                                            |

|                | 1 = High priority                                                                                                                                                                                                                                                                                                                      |

|                | 0 = Low priority                                                                                                                                                                                                                                                                                                                       |

| bit 4          | <b>TXIP:</b> EUSART Transmit Interrupt Priority bit                                                                                                                                                                                                                                                                                    |

|                | 1 = High priority                                                                                                                                                                                                                                                                                                                      |

|                | 0 = Low priority                                                                                                                                                                                                                                                                                                                       |

|                |                                                                                                                                                                                                                                                                                                                                        |

| bit 3          | SSPIP: Master Synchronous Serial Port Interrupt Priority bit                                                                                                                                                                                                                                                                           |

| bit 3          | 1 = High priority                                                                                                                                                                                                                                                                                                                      |

| bit 3          | , , ,                                                                                                                                                                                                                                                                                                                                  |

| bit 3<br>bit 2 | 1 = High priority                                                                                                                                                                                                                                                                                                                      |

|                | <ul> <li>1 = High priority</li> <li>0 = Low priority</li> </ul>                                                                                                                                                                                                                                                                        |

|                | <ul> <li>1 = High priority</li> <li>0 = Low priority</li> <li>CCP1IP: CCP1 Interrupt Priority bit</li> </ul>                                                                                                                                                                                                                           |

|                | <ul> <li>1 = High priority</li> <li>0 = Low priority</li> <li>CCP1IP: CCP1 Interrupt Priority bit</li> <li>1 = High priority</li> </ul>                                                                                                                                                                                                |

| bit 2          | <ul> <li>1 = High priority</li> <li>0 = Low priority</li> <li>CCP1IP: CCP1 Interrupt Priority bit</li> <li>1 = High priority</li> <li>0 = Low priority</li> </ul>                                                                                                                                                                      |

| bit 2          | <ul> <li>1 = High priority</li> <li>0 = Low priority</li> <li>CCP1IP: CCP1 Interrupt Priority bit</li> <li>1 = High priority</li> <li>0 = Low priority</li> <li>TMR2IP: TMR2 to PR2 Match Interrupt Priority bit</li> </ul>                                                                                                            |

| bit 2          | <ul> <li>1 = High priority</li> <li>0 = Low priority</li> <li>CCP1IP: CCP1 Interrupt Priority bit</li> <li>1 = High priority</li> <li>0 = Low priority</li> <li>TMR2IP: TMR2 to PR2 Match Interrupt Priority bit</li> <li>1 = High priority</li> </ul>                                                                                 |

| bit 2<br>bit 1 | <ul> <li>1 = High priority</li> <li>0 = Low priority</li> <li>CCP1IP: CCP1 Interrupt Priority bit</li> <li>1 = High priority</li> <li>0 = Low priority</li> <li>TMR2IP: TMR2 to PR2 Match Interrupt Priority bit</li> <li>1 = High priority</li> <li>0 = Low priority</li> </ul>                                                       |

| bit 2<br>bit 1 | <ul> <li>1 = High priority</li> <li>0 = Low priority</li> <li>CCP1IP: CCP1 Interrupt Priority bit</li> <li>1 = High priority</li> <li>0 = Low priority</li> <li>TMR2IP: TMR2 to PR2 Match Interrupt Priority bit</li> <li>1 = High priority</li> <li>0 = Low priority</li> <li>TMR1IP: TMR1 Overflow Interrupt Priority bit</li> </ul> |

### 10.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 10-5). The pins have Schmitt Trigger input buffers. RC1 is normally configured by Configuration bit, CCP2MX, as the default peripheral pin of the CCP2 module (default/erased state, CCP2MX = 1).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for additional information. Note: On a Power-on Reset, these pins are configured as digital inputs.

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

| EXAMPLE 10-3:   | INITIALIZING PORTC |

|-----------------|--------------------|

| LARMII LL IV-J. |                    |

| CLRF  | PORTC | ; Initialize PORTC by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATC  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0CFh  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISC | ; Set RC<3:0> as inputs |

|       |       | ; RC<5:4> as outputs    |

|       |       | ; RC<7:6> as inputs     |

|       |       |                         |

### TABLE 10-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Name                 | Bit 7                                                       | Bit 6               | Bit 5 | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|----------------------|-------------------------------------------------------------|---------------------|-------|---------|--------|--------|--------|--------|----------------------------|

| PORTD                | RD7                                                         | RD6                 | RD5   | RD4     | RD3    | RD2    | RD1    | RD0    | 52                         |

| LATD                 | TD PORTD Data Latch Register (Read and Write to Data Latch) |                     |       |         |        |        |        | 52     |                            |

| TRISD                | RISD         PORTD Data Direction Register                  |                     |       |         |        |        | 52     |        |                            |

| TRISE <sup>(1)</sup> | IBF                                                         | OBF                 | IBOV  | PSPMODE | _      | TRISE2 | TRISE1 | TRISE0 | 52                         |

| CCP1CON              | P1M1 <sup>(1)</sup>                                         | P1M0 <sup>(1)</sup> | DC1B1 | DC1B0   | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 | 51                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTD.

Note 1: These registers and/or bits are unimplemented on 28-oin devices.

NOTES:

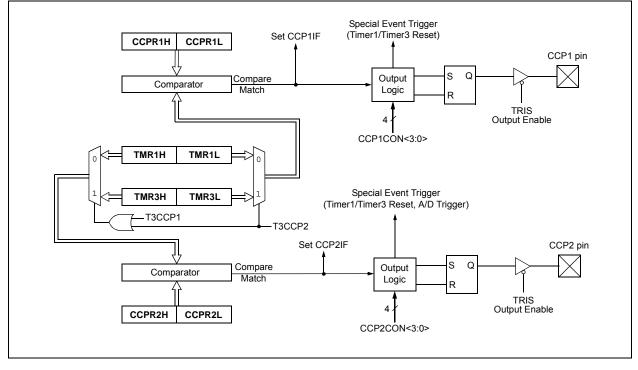

# 15.3 Compare Mode

In Compare mode, the 16-bit CCPRx register value is constantly compared against either the TMR1 or TMR3 register pair value. When a match occurs, the CCPx pin can be:

- · driven high

- · driven low

- toggled (high-to-low or low-to-high)

- remain unchanged (that is, reflects the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCPxM<3:0>). At the same time, the interrupt flag bit, CCPxIF, is set.

#### 15.3.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the appropriate TRIS bit.

| Note: | Clearing the CCP2CON register will force    |

|-------|---------------------------------------------|

|       | the RB3 or RC1 compare output latch         |

|       | (depending on device configuration) to the  |

|       | default low level. This is not the PORTB or |

|       | PORTC I/O data latch.                       |

### 15.3.2 TIMER1/TIMER3 MODE SELECTION

Timer1 and/or Timer3 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 15.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the corresponding CCPx pin is not affected. A CCP interrupt is generated when the CCPxIF interrupt flag is set while the CCPxIE bit is set.

### 15.3.4 SPECIAL EVENT TRIGGER

Both CCP modules are equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode (CCPxM<3:0> = 1011).

For either CCP module, the Special Event Trigger resets the Timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPRx registers to serve as a programmable Period register for either timer.

The Special Event Trigger for CCP2 can also start an A/D conversion. In order to do this, the A/D Converter must already be enabled.

# FIGURE 15-2: COMPARE MODE OPERATION BLOCK DIAGRAM

# REGISTER 17-2: SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE)

| R/W-0      | R/W-0                                   | R/W-0                                  | R/W-0                          | R/W-0                                  | R/W-0                  | R/W-0                | R/W-0                |

|------------|-----------------------------------------|----------------------------------------|--------------------------------|----------------------------------------|------------------------|----------------------|----------------------|

| WCOL       | SSPOV <sup>(1)</sup>                    | SSPEN <sup>(2)</sup>                   | CKP                            | SSPM3 <sup>(3)</sup>                   | SSPM2 <sup>(3)</sup>   | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| oit 7      | ·                                       |                                        |                                | ·                                      |                        |                      | bit                  |

| <u> </u>   |                                         |                                        |                                |                                        |                        |                      |                      |

| Legend:    |                                         |                                        | .,                             |                                        |                        |                      |                      |

| R = Reada  |                                         | W = Writable k                         | Dit                            |                                        | nented bit, read       |                      |                      |

| -n = Value | at POR                                  | '1' = Bit is set                       |                                | '0' = Bit is clea                      | ared                   | x = Bit is unkr      | IOWN                 |

| bit 7      | WCOL: Write                             | Collision Detec                        | t bit                          |                                        |                        |                      |                      |

|            | 1 = The SSP<br>software                 | -                                      | s written while                | e it is still transm                   | nitting the previ      | ious word (mus       | t be cleared ir      |

|            | 0 = No collisi                          | on                                     |                                |                                        |                        |                      |                      |

| bit 6      | SSPOV: Rece                             | eive Overflow Ir                       | dicator bit <sup>(1)</sup>     |                                        |                        |                      |                      |

|            | SPI Slave mo                            |                                        |                                |                                        |                        |                      |                      |

|            | -                                       |                                        |                                | BUF register is s                      |                        |                      |                      |

|            |                                         |                                        |                                | flow can only oc<br>a, to avoid settir |                        |                      |                      |

|            | 0 = No overfl                           | •                                      | anonnung uat                   |                                        | ng overnow (m          |                      | in soltware).        |

| bit 5      | SSPEN: Mas                              | ter Synchronou                         | s Serial Port I                | Enable bit <sup>(2)</sup>              |                        |                      |                      |

|            | 1 = Enables s                           | erial port and c                       | onfigures SC                   | K, SDO, SDI an<br>ese pins as I/O p    |                        | port pins            |                      |

| bit 4      | CKP: Clock F                            | olarity Select b                       | it                             |                                        |                        |                      |                      |

|            | 1 = Idle state                          | for clock is a hi<br>for clock is a lo | gh level                       |                                        |                        |                      |                      |

| bit 3-0    |                                         |                                        |                                | Port Mode Selec                        | ct bits <sup>(3)</sup> |                      |                      |

|            | 0101 = SPI S<br>0100 = SPI S            | lave mode, clo                         | ck = SCK pin;<br>ck = SCK pin; | SS pin control SS pin control          | disabled; SS c         | an be used as I      | /O pin               |

|            |                                         | laster mode, clo                       |                                |                                        |                        |                      |                      |

|            |                                         | laster mode, clo                       |                                | 6                                      |                        |                      |                      |

|            | 0000 = SPI N                            | laster mode, clo                       | ock = Fosc/4                   |                                        |                        |                      |                      |

| Note 1:    | In Master mode, t<br>writing to the SSF |                                        | is not set sind                | ce each new rec                        | eption (and tra        | insmission) is ir    | nitiated by          |

| 2:         | When enabled, th                        | •                                      | be properly co                 | onfigured as inp                       | ut or output.          |                      |                      |

|            |                                         |                                        |                                |                                        |                        |                      |                      |

**3:** Bit combinations not specifically listed here are either reserved or implemented in  $I^2C^{TM}$  mode only.

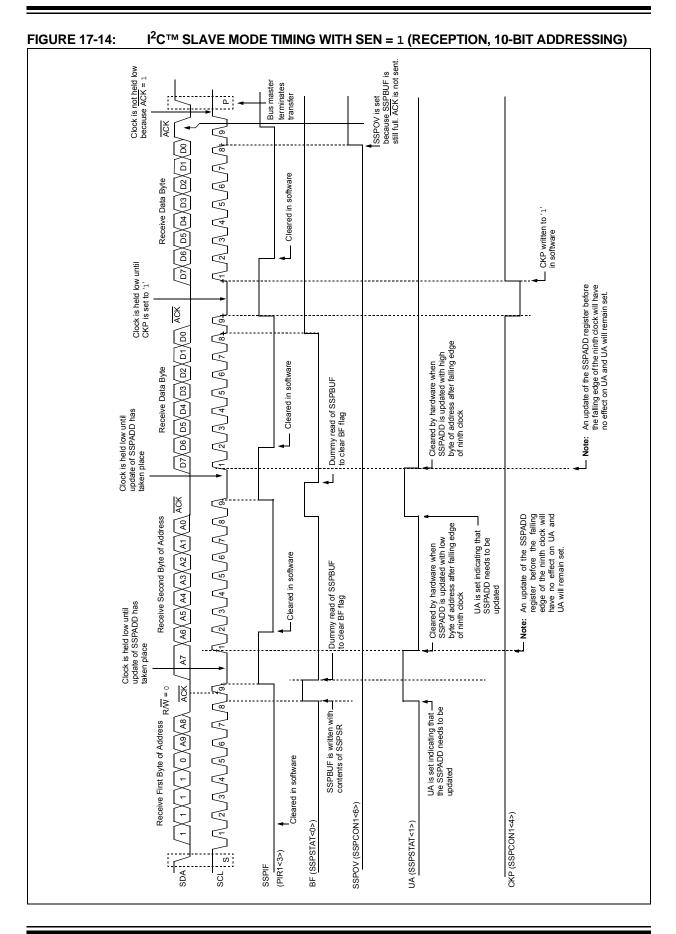

# 17.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the  $R/\overline{W}$  bit. In this case, the  $R/\overline{W}$  bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

The Baud Rate Generator used for the SPI mode operation is used to set the SCL clock frequency for either 100 kHz, 400 kHz or 1 MHz I<sup>2</sup>C operation. See **Section 17.4.7 "Baud Rate"** for more detail.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start Enable bit, SEN (SSPCON2<0>).

- 2. SSPIF is set. The MSSP module will wait the required start time before any other operation takes place.

- 3. The user loads the SSPBUF with the slave address to transmit.

- 4. Address is shifted out the SDA pin until all 8 bits are transmitted.

- 5. The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 6. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 7. The user loads the SSPBUF with eight bits of data.

- 8. Data is shifted out the SDA pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 11. The user generates a Stop condition by setting the Stop Enable bit, PEN (SSPCON2<2>).

- 12. Interrupt is generated once the Stop condition is complete.

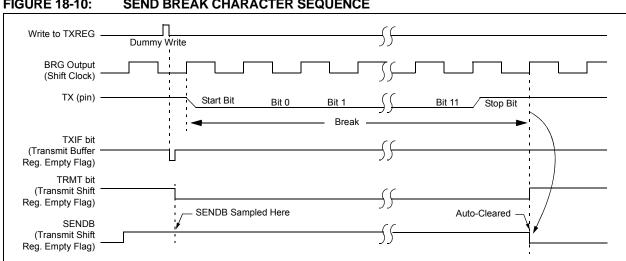

#### 18.2.5 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift register is loaded with data. Note that the value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

Note that the data value written to the TXREG for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 18-10 for the timing of the Break character sequence.

#### 18.2.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN bus master.

- Configure the EUSART for the desired mode. 1.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- Write '55h' to TXREG to load the Sync character 4. into the transmit FIFO buffer.

- After the Break has been sent, the SENDB bit is 5. reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### 18.2.6 **RECEIVING A BREAK CHARACTER**

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in Section 18.2.4 "Auto-Wake-up on Sync Break Character". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABD bit once the TXIF interrupt is observed.

#### **FIGURE 18-10:** SEND BREAK CHARACTER SEQUENCE

| U-0                   | U-0                          |                   | R/W-      | 0       | R/V     | V-0     | R                  | /W-0               | F                  | 2/W-q <b>(</b> 1 | )     | R/W-    | q <sup>(1)</sup> | R/   | W-q <sup>(1)</sup> |

|-----------------------|------------------------------|-------------------|-----------|---------|---------|---------|--------------------|--------------------|--------------------|------------------|-------|---------|------------------|------|--------------------|

| _                     | _                            |                   | VCFG      | 61      | VCF     | G0      | PC                 | FG3                | F                  | PCFG2            | 2     | PCF     | G1               | P    | CFG0               |

| bit 7                 |                              |                   |           |         |         |         |                    |                    |                    |                  |       |         |                  | •    | bi                 |

| Legend:               |                              |                   |           |         |         |         |                    |                    |                    |                  |       |         |                  |      |                    |

| R = Reada             | able bit                     | N                 | / = Writ  | table b | it      |         | U = L              | Jnimple            | emente             | ed bit. i        | ead a | s '0'   |                  |      |                    |

| -n = Value            |                              |                   | ' = Bit i |         | -       |         |                    | -                  | leared             | ,                |       | = Bit i | s unki           | nown |                    |

| <b>h</b> # <b>7</b> 0 | Unimalan                     |                   |           |         |         |         |                    |                    |                    |                  |       |         |                  |      |                    |

| bit 7-6               |                              |                   |           |         |         | ation k |                    |                    |                    |                  |       |         |                  |      |                    |

| bit 5                 | <b>VCFG1:</b> V<br>1 = VREF- | -                 |           | ence C  | oniigui | ation   | лt (VRE            | : SOU              | ice)               |                  |       |         |                  |      |                    |

|                       | 1 = VREF-<br>0 = VSS         | (ANZ)             |           |         |         |         |                    |                    |                    |                  |       |         |                  |      |                    |

| bit 4                 | VCFG0: V                     | /oltage           | Refere    | ence C  | onfigur | ation b | dit (Vre           | F+ SOI             | urce)              |                  |       |         |                  |      |                    |

|                       | 1 = VREF+                    | -                 |           | -       | 0       |         | `                  |                    | ,                  |                  |       |         |                  |      |                    |

|                       | 0 = VDD                      |                   |           |         |         |         |                    |                    |                    |                  |       |         |                  |      |                    |

| bit 3-0               | PCFG<3:0                     | <b>0&gt;:</b> A/[ | ) Port (  | Configu | uration | Contro  | ol bits:           |                    |                    |                  |       |         |                  |      |                    |

|                       | PCFG3:                       | 12                | 11        | 10      | 6       | ŝ       | 7(2)               | 5(2)               | 5(2)               | 4                | ~     | 2       | -                | 6    |                    |

|                       | PCFG0                        | AN12              | AN11      | AN10    | AN9     | AN8     | AN7 <sup>(2)</sup> | AN6 <sup>(2)</sup> | AN5 <sup>(2)</sup> | AN4              | AN3   | AN2     | AN1              | ANO  |                    |

|                       | 0000 <b>(1)</b>              | А                 | Α         | Α       | Α       | Α       | Α                  | Α                  | Α                  | Α                | Α     | Α       | Α                | Α    |                    |

|                       | 0001                         | Α                 | Α         | Α       | Α       | Α       | Α                  | Α                  | Α                  | Α                | Α     | Α       | Α                | Α    |                    |

|                       | 0010                         | Α                 | Α         | Α       | Α       | Α       | Α                  | Α                  | Α                  | Α                | Α     | Α       | Α                | Α    |                    |

|                       | 0011                         | D                 | Α         | Α       | Α       | Α       | Α                  | Α                  | Α                  | Α                | Α     | Α       | Α                | А    |                    |

|                       | 0100                         | D                 | D         | Α       | Α       | Α       | Α                  | Α                  | Α                  | Α                | Α     | Α       | Α                | Α    |                    |

|                       | 0101                         | D                 | D         | D       | Α       | Α       | Α                  | Α                  | Α                  | Α                | Α     | Α       | Α                | Α    |                    |

|                       | 0110                         | D                 | D         | D       | D       | Α       | Α                  | Α                  | Α                  | Α                | Α     | Α       | Α                | Α    |                    |

|                       | 0111 <b>(1)</b>              | D                 | D         | D       | D       | D       | A                  | A                  | A                  | A                | A     | A       | A                | A    |                    |

|                       | 1000                         | D                 | D         | D       | D       | D       | D                  | Α                  | Α                  | Α                | Α     | А       | А                | Α    |                    |

|                       | 1001                         | D                 | D         | D       | D       | D       | D                  | D                  | Α                  | Α                | Α     | Α       | Α                | Α    |                    |

|                       | 1010                         | D                 | D         | D       | D       | D       | D                  | D                  | D                  | Α                | Α     | А       | А                | А    |                    |

|                       | 1011                         | D                 | D         | D       | D       | D       | D                  | D                  | D                  | D                | Α     | Α       | Α                | Α    |                    |

|                       | 1100                         | D                 | D         | D       | D       | D       | D                  | D                  | D                  | D                | D     | Α       | Α                | Α    |                    |

|                       | 1101                         | D                 | D         | D       | D       | D       | D                  | D                  | D                  | D                | D     | D       | Α                | Α    |                    |

|                       | 1110                         | D                 | D         | D       | D       | D       | D                  | D                  | D                  | D                | D     | D       | D                | Α    |                    |

|                       | 1111                         | D                 | D         | D       | D       | D       | D                  | D                  | D                  | D                | D     | D       | D                | D    |                    |

### REGISTER 19-2: ADCON1: A/D CONTROL REGISTER 1

**Note 1:** The POR value of the PCFG bits depends on the value of the PBADEN Configuration bit. When PBADEN = 1, PCFG<2:0> = 000; when PBADEN = 0, PCFG<2:0> = 111.

D = Digital I/O

2: AN5 through AN7 are available only on 40/44-pin devices.

A = Analog input

| BNC                    | Branch if Not Carry                                                      |                                                                                      | BNN                                                  | l            | Branch if Not Negative       |                                                                                                                                                                                                                                                                                           |                 |                 |  |

|------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------|--------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|--|

| Syntax:                | BNC n                                                                    |                                                                                      |                                                      | Synta        | ax:                          | BNN n                                                                                                                                                                                                                                                                                     |                 |                 |  |

| Operands:              | -128 ≤ n ≤ ′                                                             | 127                                                                                  |                                                      | Oper         | ands:                        | -128 ≤ n ≤                                                                                                                                                                                                                                                                                | 127             |                 |  |

| Operation:             | if Carry bit i<br>(PC) + 2 + 2                                           |                                                                                      |                                                      | Oper         | ation:                       | if Negative<br>(PC) + 2 +                                                                                                                                                                                                                                                                 |                 |                 |  |

| Status Affected:       | None                                                                     |                                                                                      |                                                      | Statu        | s Affected:                  | None                                                                                                                                                                                                                                                                                      |                 |                 |  |

| Encoding:              | 1110                                                                     | 0011 nn:                                                                             | nn nnnn                                              | Enco         | ding:                        | 1110                                                                                                                                                                                                                                                                                      | 0111 nn:        | nn nnnn         |  |

| Description:           | will branch.<br>The 2's cor<br>added to th<br>incremente<br>instruction, | nplement num<br>e PC. Since th<br>d to fetch the<br>the new addre<br>n. This instruc | ber '2n' is<br>e PC will have<br>next<br>ess will be | Description: |                              | If the Negative bit is '0', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will hav<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |                 |                 |  |

| Words:                 | 1                                                                        |                                                                                      |                                                      | Word         | s:                           | 1                                                                                                                                                                                                                                                                                         |                 |                 |  |

| Cycles:                | 1(2)                                                                     |                                                                                      |                                                      | Cycle        | es:                          | 1(2)                                                                                                                                                                                                                                                                                      |                 |                 |  |

| Q Cycle Activity       | /:                                                                       |                                                                                      |                                                      | Q C<br>If Ju | ycle Activity:<br>mp:        |                                                                                                                                                                                                                                                                                           |                 |                 |  |

| Q1                     | Q2                                                                       | Q3                                                                                   | Q4                                                   |              | Q1                           | Q2                                                                                                                                                                                                                                                                                        | Q3              | Q4              |  |

| Decode                 | Read literal<br>'n'                                                      | Process<br>Data                                                                      | Write to PC                                          |              | Decode                       | Read literal<br>'n'                                                                                                                                                                                                                                                                       | Process<br>Data | Write to PC     |  |

| No<br>operation        | No<br>n operation                                                        | No<br>operation                                                                      | No<br>operation                                      |              | No<br>operation              | No<br>operation                                                                                                                                                                                                                                                                           | No<br>operation | No<br>operation |  |

| If No Jump:            |                                                                          |                                                                                      |                                                      | lf No        | o Jump:                      |                                                                                                                                                                                                                                                                                           |                 |                 |  |

| Q1                     | Q2                                                                       | Q3                                                                                   | Q4                                                   |              | Q1                           | Q2                                                                                                                                                                                                                                                                                        | Q3              | Q4              |  |

| Decode                 | Read literal<br>'n'                                                      | Process<br>Data                                                                      | No<br>operation                                      |              | Decode                       | Read literal<br>'n'                                                                                                                                                                                                                                                                       | Process<br>Data | No<br>operation |  |

| Example:               | HERE                                                                     | BNC Jump                                                                             |                                                      | Exan         | <u>nple:</u>                 | HERE                                                                                                                                                                                                                                                                                      | BNN Jump        |                 |  |

| Before Inst            | ruction                                                                  |                                                                                      |                                                      |              | Before Instruc               | ction                                                                                                                                                                                                                                                                                     |                 |                 |  |

| PC                     |                                                                          | dress (HERE                                                                          | )                                                    |              | PC                           |                                                                                                                                                                                                                                                                                           | dress (HERE     | )               |  |

| After Instru<br>If Car |                                                                          |                                                                                      |                                                      |              | After Instructi<br>If Negati |                                                                                                                                                                                                                                                                                           |                 |                 |  |

|                        |                                                                          | dress (Jump                                                                          | )                                                    |              | PC                           |                                                                                                                                                                                                                                                                                           | dress (Jump     | )               |  |

| If Car                 |                                                                          | - <u>-</u>                                                                           |                                                      |              | If Negati                    |                                                                                                                                                                                                                                                                                           | · <u>-</u>      |                 |  |

| Syntax:CLRF f {.a}Operands: $0 \le f \le 255$ $a \in [0,1]$ Operation:Operation: $000h \rightarrow f$ , $1 \rightarrow Z$ $1 \rightarrow Z$ Status Affected:ZEncoding: $0110$ $0110$ $101a$ f 'a' is 'o', the Access Bank is selected.If 'a' is 'o', and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f $\le 95$ (5Fh). SeeSection 24.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.Words:1Cycles:1Q Cycle Activity:Q 1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q1Q2Q2Q3Q4                                                                 | ,<br>,    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| $a \in [0,1]$ Operation: $000h \rightarrow f$ ,<br>$1 \rightarrow Z$ Operation: $000h \rightarrow WDT$ ,<br>$000h \rightarrow WDT postscalerStatus Affected:ZI \rightarrow \overline{TO},1 \rightarrow \overline{PD}I \rightarrow \overline{TO},1 \rightarrow \overline{PD}Status Affected:TO, \overline{PD}Description:Clears the contents of the specifiedregister.Status Affected:TO, \overline{PD}Encoding:0000  0000  000If 'a' is 'o', the Access Bank is selected.If 'a' is 'o', the Access Bank is selected.If 'a' is 'o' and the extended instructionset is enabled, this instruction operatesin Indexed Literal Offset Addressingmode whenever f \leq 95 (5Fh). SeeSection 24.2.3 "Byte-Oriented andBit-Oriented Instructions in IndexedLiteral Offset Mode" for details.Words:1Words:1Q1Q2Q3Q Cycle Activity:Q1Q2Q3DecodeNoProcessDataVords:1Example:CLRWDTQ Cycle Activity:Effere InstructionExample:$ | ,         |

| Operation: $000h \rightarrow f,$<br>$1 \rightarrow Z$ $000h \rightarrow WDT$ postscalerStatus Affected:Z $1 \rightarrow \overline{D},$<br>$1 \rightarrow \overline{PD}$ Encoding: $0110$ $101a$ ffffDescription:Clears the contents of the specified<br>register.Status Affected: $\overline{TO}, \overline{PD}$ If 'a' is 'o', the Access Bank is selected.<br>If 'a' is 'o', the Access Bank is selected.<br>If 'a' is 'o' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f $\leq 95$ (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details.Words:1Words:1Q1Q2Q3Q Cycle Activity:Q1Q2Q3DecodeNoProcessoperationDataData                                                                                                                                | 3         |

| $1 \rightarrow Z$ $1 \rightarrow \overline{TO}$ Status Affected:Z $1 \rightarrow \overline{TO}$ Encoding: $0110$ $101a$ ffffDescription:Clears the contents of the specified<br>register.<br>If 'a' is 'o', the Access Bank is selected.<br>If 'a' is 'o', the Access Bank is selected.<br>If 'a' is 'o' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details.Status Affected: $\overline{TO}, \overline{PD}$ Words:1CLRWDT instruction result<br>Words:Words:1Q Cycle Activity:Q1Q2Q3Q Cycle Activity:Q1Q2Q3DecodeNoProcessoperationDataData                                                                                                                                                 | ,         |

| Status Affected:Z $1 \rightarrow \overline{PD}$ Encoding:0110101affffffffDescription:Clears the contents of the specified<br>register.<br>If 'a' is 'o', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is 'o' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f $\leq$ 95 (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details.Uoto1Words:1Q2Q3Q Cycles:1Q2Q3DecodeNoProcess<br>OperationQ Cycle Activity:Example:CLRWDTQ Cycle Activity:Example:CLRWDT                                                                                                                                                                                                                                  |           |

| Status Affected:ZEncoding: $0110$ $101a$ ffffffffDescription:Clears the contents of the specified<br>register.<br>If 'a' is 'o', the Access Bank is selected.<br>If 'a' is 'o' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f $\leq$ 95 (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details.Status Affected:TO, PDWords:1Cycles:1Cycles:1Q Cycle Activity:Q1Q2Q3DecodeNoProcess<br>operationQ Cycle Activity:Example:CLRWDTQ Cycle Activity:Example:CLRWDT                                                                                                                                                                                                                                                                                           |           |