Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1.5K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 13x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4520t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

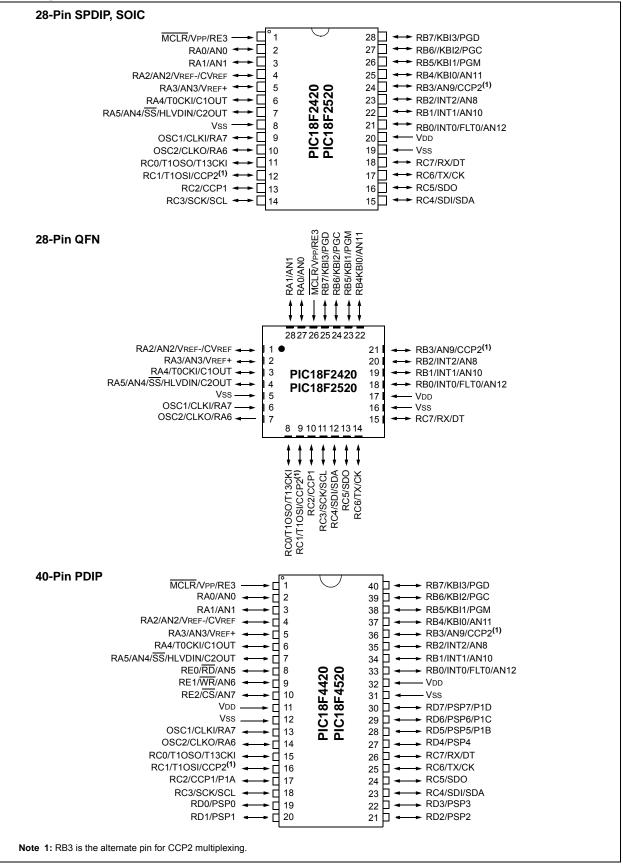

## **Pin Diagrams**

| Pin Name             | Pi        | Pin Number |         | Pin      | Buffer     | Description                                                                    |  |  |

|----------------------|-----------|------------|---------|----------|------------|--------------------------------------------------------------------------------|--|--|

| Pin Name             | PDIP      | QFN        | TQFP    | Туре     | Туре       | Description                                                                    |  |  |

|                      |           |            |         |          |            | PORTC is a bidirectional I/O port.                                             |  |  |

| RC0/T10SO/T13CKI     | 15        | 34         | 32      |          |            |                                                                                |  |  |

| RC0                  |           |            |         | I/O      | ST         | Digital I/O.                                                                   |  |  |

| T10SO                |           |            |         | 0        |            | Timer1 oscillator output.                                                      |  |  |

| T13CKI               |           |            |         | Ι        | ST         | Timer1/Timer3 external clock input.                                            |  |  |

| RC1/T1OSI/CCP2       | 16        | 35         | 35      | 1/0      | <b>0T</b>  |                                                                                |  |  |

| RC1<br>T1OSI         |           |            |         | 1/O<br>1 | ST<br>CMOS | Digital I/O.<br>Timer1 oscillator input.                                       |  |  |

| CCP2 <sup>(2)</sup>  |           |            |         | ı<br>I/O | ST         | Capture 2 input/Compare 2 output/PWM2 output.                                  |  |  |

|                      |           |            |         | 1/0      | 51         |                                                                                |  |  |

| RC2/CCP1/P1A<br>RC2  | 17        | 36         | 36      | I/O      | ST         | Digital I/O.                                                                   |  |  |

| CCP1                 |           |            |         | 1/O      | ST         | Capture 1 input/Compare 1 output/PWM1 output.                                  |  |  |

| P1A                  |           |            |         | 0        | _          | Enhanced CCP1 output.                                                          |  |  |

| RC3/SCK/SCL          | 18        | 37         | 37      |          |            |                                                                                |  |  |

| RC3                  | 10        | 57         | 57      | I/O      | ST         | Digital I/O.                                                                   |  |  |

| SCK                  |           |            |         | I/O      | ST         | Synchronous serial clock input/output for                                      |  |  |

|                      |           |            |         | -        | -          | SPI mode.                                                                      |  |  |

| SCL                  |           |            |         | I/O      | ST         | Synchronous serial clock input/output for I <sup>2</sup> C™ mode               |  |  |

| RC4/SDI/SDA          | 23        | 42         | 42      |          |            |                                                                                |  |  |

| RC4                  |           |            |         | I/O      | ST         | Digital I/O.                                                                   |  |  |

| SDI                  |           |            |         | Ι        | ST         | SPI data in.                                                                   |  |  |

| SDA                  |           |            |         | I/O      | ST         | l <sup>2</sup> C data I/O.                                                     |  |  |

| RC5/SDO              | 24        | 43         | 43      |          |            |                                                                                |  |  |

| RC5                  |           |            |         | I/O      | ST         | Digital I/O.                                                                   |  |  |

| SDO                  |           |            |         | 0        | —          | SPI data out.                                                                  |  |  |

| RC6/TX/CK            | 25        | 44         | 44      |          |            |                                                                                |  |  |

| RC6                  |           |            |         | I/O      | ST         | Digital I/O.                                                                   |  |  |

| TX<br>CK             |           |            |         | 0<br>I/O | ST         | EUSART asynchronous transmit.<br>EUSART synchronous clock (see related RX/DT). |  |  |

|                      |           |            |         | 1/0      | 01         |                                                                                |  |  |

| RC7/RX/DT<br>RC7     | 26        | 1          | 1       | I/O      | ST         | Digital I/O.                                                                   |  |  |

| RX                   |           |            |         | 1        | ST         | EUSART asynchronous receive.                                                   |  |  |

| DT                   |           |            |         | I/O      | ST         | EUSART synchronous data (see related TX/CK).                                   |  |  |

| Legend: TTL = TTL co | ompatibl  | e input    |         |          | (          | CMOS = CMOS compatible input or output                                         |  |  |

| ST = Schmi           | tt Trigge |            | with CM | OS lev   |            | = Input                                                                        |  |  |

| O = Outpu            | t         |            |         |          | F          | P = Power                                                                      |  |  |

## TABLE 1-3: PIC18F4420/4520 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

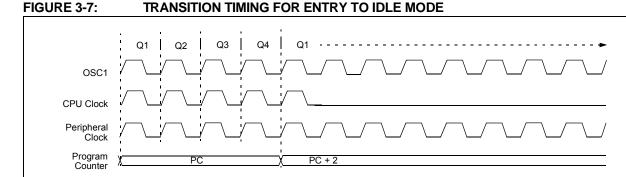

## 3.4.1 PRI\_IDLE MODE

This mode is unique among the three low-power Idle modes in that it does not disable the primary device clock. For timing-sensitive applications, this allows for the fastest resumption of device operation with its more accurate primary clock source, since the clock source does not have to "warm-up" or transition from another oscillator.

PRI\_IDLE mode is entered from PRI\_RUN mode by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, set IDLEN first, then clear the SCS bits and execute SLEEP. Although the CPU is disabled, the peripherals continue to be clocked from the primary clock source specified by the FOSC<3:0> Configuration bits. The OSTS bit remains set (see Figure 3-7).

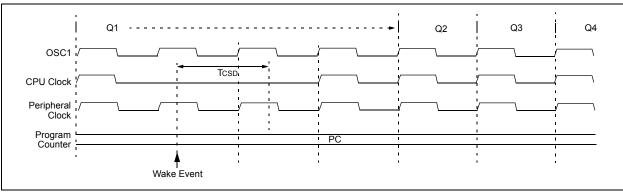

When a wake event occurs, the CPU is clocked from the primary clock source. A delay of interval TCSD is required between the wake event and when code execution starts. This is required to allow the CPU to become ready to execute instructions. After the wake-up, the OSTS bit remains set. The IDLEN and SCS bits are not affected by the wake-up (see Figure 3-8).

## 3.4.2 SEC\_IDLE MODE

In SEC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the Timer1 oscillator. This mode is entered from SEC\_RUN by

setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, set the IDLEN bit first, then set the SCS<1:0> bits to '01' and execute SLEEP. When the clock source is switched to the Timer1 oscillator, the primary oscillator is shut down, the OSTS bit is cleared and the T1RUN bit is set.

When a wake event occurs, the peripherals continue to be clocked from the Timer1 oscillator. After an interval of TCSD, following the wake event, the CPU begins executing code being clocked by the Timer1 oscillator. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run (see Figure 3-8).

Note: The Timer1 oscillator should already be running prior to entering SEC\_IDLE mode. If the T1OSCEN bit is not set when the SLEEP instruction is executed, the SLEEP instruction will be ignored and entry to SEC\_IDLE mode will not occur. If the Timer1 oscillator is enabled but not yet running, peripheral clocks will be delayed until the oscillator has started. In such situations, initial oscillator operation is far from stable and unpredictable operation may result.

#### FIGURE 3-8: TRANSITION TIMING FOR WAKE FROM IDLE TO RUN MODE

## 4.6 Reset State of Registers

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state" depending on the type of Reset that occurred.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register,  $\overline{RI}$ ,  $\overline{TO}$ ,  $\overline{PD}$ ,  $\overline{POR}$  and  $\overline{BOR}$ , are set or cleared differently in different Reset situations, as indicated in Table 4-3. These bits are used in software to determine the nature of the Reset. Table 4-4 describes the Reset states for all of the Special Function Registers. These are categorized by Power-on and Brown-out Resets, Master Clear and WDT Resets and WDT wake-ups.

| TABLE 4-3: | STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION |

|------------|------------------------------------------------------------------|

|            | FOR RCON REGISTER                                                |

| Condition                                                   | Program               |    | RCC | ON Reg | ister |     | STKPTR Register |        |

|-------------------------------------------------------------|-----------------------|----|-----|--------|-------|-----|-----------------|--------|

| Condition                                                   | Counter               | RI | то  | PD     | POR   | BOR | STKFUL          | STKUNF |

| Power-on Reset                                              | 0000h                 | 1  | 1   | 1      | 0     | 0   | 0               | 0      |

| RESET Instruction                                           | 0000h                 | 0  | u   | u      | u     | u   | u               | u      |

| Brown-out Reset                                             | 0000h                 | 1  | 1   | 1      | u     | 0   | u               | u      |

| MCLR Reset during Power-Managed Run Modes                   | 0000h                 | u  | 1   | u      | u     | u   | u               | u      |

| MCLR Reset during Power-Managed Idle Modes and Sleep Mode   | 0000h                 | u  | 1   | 0      | u     | u   | u               | u      |

| WDT Time-out during Full Power or<br>Power-Managed Run Mode | 0000h                 | u  | 0   | u      | u     | u   | u               | u      |

| MCLR Reset during Full-Power Execution                      | 0000h                 | u  | u   | u      | u     | u   | u               | u      |

| Stack Full Reset (STVREN = 1)                               | 0000h                 | u  | u   | u      | u     | u   | 1               | u      |

| Stack Underflow Reset (STVREN = 1)                          | 0000h                 | u  | u   | u      | u     | u   | u               | 1      |

| Stack Underflow Error (not an actual<br>Reset, STVREN = 0)  | 0000h                 | u  | u   | u      | u     | u   | u               | 1      |

| WDT Time-out during<br>Power-Managed Idle or Sleep Modes    | PC + 2                | u  | 0   | 0      | u     | u   | u               | u      |

| Interrupt Exit from Power-Managed<br>Modes                  | PC + 2 <sup>(1)</sup> | u  | u   | 0      | u     | u   | u               | u      |

**Legend:** u = unchanged

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the interrupt vector (008h or 0018h).

## 5.3.4 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (FFFh) and extend downward to occupy the top half of Bank 15 (F80h to FFFh). A list of these registers is given in Table 5-1 and Table 5-2. The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the peripheral functions. The Reset and Interrupt registers are described in their respective chapters, while the ALU's STATUS register is described later in this section. Registers related to the operation of a peripheral feature are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's.

## TABLE 5-1: SPECIAL FUNCTION REGISTER MAP FOR PIC18F2420/2520/4420/4520 DEVICES

| Address | Name                    | Address | Name                    | Address | Name                   | Address | Name                 |

|---------|-------------------------|---------|-------------------------|---------|------------------------|---------|----------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(1)</sup>    | FBFh    | CCPR1H                 | F9Fh    | IPR1                 |

| FFEh    | TOSH                    | FDEh    | POSTINC2 <sup>(1)</sup> | FBEh    | CCPR1L                 | F9Eh    | PIR1                 |

| FFDh    | TOSL                    | FDDh    | POSTDEC2(1)             | FBDh    | CCP1CON                | F9Dh    | PIE1                 |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(1)</sup>  | FBCh    | CCPR2H                 | F9Ch    | (2)                  |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(1)</sup>   | FBBh    | CCPR2L                 | F9Bh    | OSCTUNE              |

| FFAh    | PCLATH                  | FDAh    | FSR2H                   | FBAh    | CCP2CON                | F9Ah    | (2)                  |

| FF9h    | PCL                     | FD9h    | FSR2L                   | FB9h    | (2)                    | F99h    | (2)                  |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                  | FB8h    | BAUDCON                | F98h    | (2)                  |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                   | FB7h    | PWM1CON <sup>(3)</sup> | F97h    | (2)                  |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                   | FB6h    | ECCP1AS <sup>(3)</sup> | F96h    | TRISE <sup>(3)</sup> |

| FF5h    | TABLAT                  | FD5h    | TOCON                   | FB5h    | CVRCON                 | F95h    | TRISD <sup>(3)</sup> |

| FF4h    | PRODH                   | FD4h    | (2)                     | FB4h    | CMCON                  | F94h    | TRISC                |

| FF3h    | PRODL                   | FD3h    | OSCCON                  | FB3h    | TMR3H                  | F93h    | TRISB                |

| FF2h    | INTCON                  | FD2h    | HLVDCON                 | FB2h    | TMR3L                  | F92h    | TRISA                |

| FF1h    | INTCON2                 | FD1h    | WDTCON                  | FB1h    | T3CON                  | F91h    | (2)                  |

| FF0h    | INTCON3                 | FD0h    | RCON                    | FB0h    | SPBRGH                 | F90h    | (2)                  |

| FEFh    | INDF0 <sup>(1)</sup>    | FCFh    | TMR1H                   | FAFh    | SPBRG                  | F8Fh    | (2)                  |

| FEEh    | POSTINC0 <sup>(1)</sup> | FCEh    | TMR1L                   | FAEh    | RCREG                  | F8Eh    | (2)                  |

| FEDh    | POSTDEC0 <sup>(1)</sup> | FCDh    | T1CON                   | FADh    | TXREG                  | F8Dh    | LATE <sup>(3)</sup>  |

| FECh    | PREINC0 <sup>(1)</sup>  | FCCh    | TMR2                    | FACh    | TXSTA                  | F8Ch    | LATD <sup>(3)</sup>  |

| FEBh    | PLUSW0 <sup>(1)</sup>   | FCBh    | PR2                     | FABh    | RCSTA                  | F8Bh    | LATC                 |

| FEAh    | FSR0H                   | FCAh    | T2CON                   | FAAh    | (2)                    | F8Ah    | LATB                 |

| FE9h    | FSR0L                   | FC9h    | SSPBUF                  | FA9h    | EEADR                  | F89h    | LATA                 |

| FE8h    | WREG                    | FC8h    | SSPADD                  | FA8h    | EEDATA                 | F88h    | (2)                  |

| FE7h    | INDF1 <sup>(1)</sup>    | FC7h    | SSPSTAT                 | FA7h    | EECON2 <sup>(1)</sup>  | F87h    | (2)                  |

| FE6h    | POSTINC1 <sup>(1)</sup> | FC6h    | SSPCON1                 | FA6h    | EECON1                 | F86h    | (2)                  |

| FE5h    | POSTDEC1 <sup>(1)</sup> | FC5h    | SSPCON2                 | FA5h    | (2)                    | F85h    | (2)                  |

| FE4h    | PREINC1 <sup>(1)</sup>  | FC4h    | ADRESH                  | FA4h    | (2)                    | F84h    | PORTE <sup>(3)</sup> |

| FE3h    | PLUSW1 <sup>(1)</sup>   | FC3h    | ADRESL                  | FA3h    | (2)                    | F83h    | PORTD <sup>(3)</sup> |

| FE2h    | FSR1H                   | FC2h    | ADCON0                  | FA2h    | IPR2                   | F82h    | PORTC                |

| FE1h    | FSR1L                   | FC1h    | ADCON1                  | FA1h    | PIR2                   | F81h    | PORTB                |

| FE0h    | BSR                     | FC0h    | ADCON2                  | FA0h    | PIE2                   | F80h    | PORTA                |

Note 1: This is not a physical register.

2: Unimplemented registers are read as '0'.

3: This register is not available on 28-pin devices.

## 6.3 Reading the Flash Program Memory

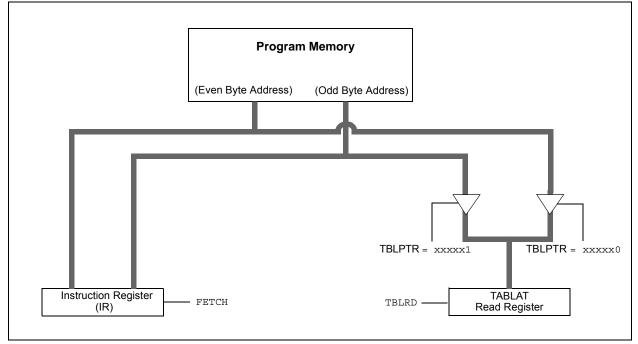

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

## FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

## EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

| MOVLW<br>MOVWF<br>MOVLW<br>MOVLW<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW       |                                                                                                                                                                              | Load TBLPTR with the base<br>address of the word                                                                                                                                       |

|-------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 110 V W1                                  |                                                                                |                                                                                                                                                                              |                                                                                                                                                                                        |

| TBLRD*+                                   | -                                                                              | ;                                                                                                                                                                            | read into TABLAT and increment                                                                                                                                                         |

| MOVF                                      | TABLAT, W                                                                      | ;                                                                                                                                                                            | get data                                                                                                                                                                               |

| MOVWF                                     | WORD EVEN                                                                      |                                                                                                                                                                              |                                                                                                                                                                                        |

| TBLRD*+                                   |                                                                                | ;                                                                                                                                                                            | read into TABLAT and increment                                                                                                                                                         |

| MOVFW                                     | TABLAT, W                                                                      | ;                                                                                                                                                                            | get data                                                                                                                                                                               |

| MOVF                                      | WORD_ODD                                                                       |                                                                                                                                                                              |                                                                                                                                                                                        |

|                                           | MOVWF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVF<br>MOVVF<br>TBLRD*4<br>MOVFW | MOVWF TBLPTRU<br>MOVLW CODE_ADDR_HIGH<br>MOVWF TBLPTRH<br>MOVLW CODE_ADDR_LOW<br>MOVWF TBLPTRL<br>TBLRD*+<br>MOVF TABLAT, W<br>MOVWF WORD_EVEN<br>TBLRD*+<br>MOVFW TABLAT, W | MOVWF TBLPTRU ;<br>MOVUW CODE_ADDR_HIGH<br>MOVWF TBLPTRH<br>MOVLW CODE_ADDR_LOW<br>MOVWF TBLPTRL<br>TBLRD*+ ;<br>MOVF TABLAT, W ;<br>MOVWF WORD_EVEN<br>TBLRD*+ ;<br>MOVFW TABLAT, W ; |

## 7.6 Operation During Code-Protect

Data EEPROM memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if code protection is enabled.

The microcontroller itself can both read and write to the internal data EEPROM, regardless of the state of the code-protect Configuration bit. Refer to **Section 23.0 "Special Features of the CPU"** for additional information.

## 7.7 Protection Against Spurious Write

There are conditions when the user may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been implemented. On power-up, the WREN bit is cleared. In addition, writes to the EEPROM are blocked during the Power-up Timer period (TPWRT, parameter 33).

The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch or software malfunction.

## 7.8 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). Frequently changing values will typically be updated more often than specification D124. If this is not the case, an array refresh must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

A simple data EEPROM refresh routine is shown in Example 7-3.

Note: If data EEPROM is only used to store constants and/or data that changes rarely, an array refresh is likely not required. See specification D124.

|  | EXAMPLE 7-3: | DATA EEPROM REFRESH ROUTINE |

|--|--------------|-----------------------------|

|--|--------------|-----------------------------|

|      | CLRF   | EEADR         | ; | Start at address 0         |

|------|--------|---------------|---|----------------------------|

|      | BCF    | EECON1, CFGS  | ; | Set for memory             |

|      | BCF    | EECON1, EEPGD | ; | Set for Data EEPROM        |

|      | BCF    | INTCON, GIE   | ; | Disable interrupts         |

|      | BSF    | EECON1, WREN  | ; | Enable writes              |

| Loop |        |               | ; | Loop to refresh array      |

|      | BSF    | EECON1, RD    | ; | Read current address       |

|      | MOVLW  | 55h           | ; |                            |

|      | MOVWF  | EECON2        | ; | Write 55h                  |

|      | MOVLW  | 0AAh          | ; |                            |

|      | MOVWF  | EECON2        | ; | Write OAAh                 |

|      | BSF    | EECON1, WR    | ; | Set WR bit to begin write  |

|      | BTFSC  | EECON1, WR    | ; | Wait for write to complete |

|      | BRA    | \$-2          |   |                            |

|      | INCFSZ | EEADR, F      | ; | Increment address          |

|      | BRA    | LOOP          | ; | Not zero, do it again      |

|      |        |               |   |                            |

|      | BCF    | EECON1, WREN  | ; | Disable writes             |

|      | BSF    | INTCON, GIE   | ; | Enable interrupts          |

|      |        |               |   | -                          |

| R/W-1        | R/W-1                                       | U-0                | R/W-1             | R/W-1             | R/W-1            | R/W-1           | R/W-1  |  |  |  |

|--------------|---------------------------------------------|--------------------|-------------------|-------------------|------------------|-----------------|--------|--|--|--|

| OSCFIP       | CMIP                                        | _                  | EEIP              | BCLIP             | HLVDIP           | TMR3IP          | CCP2IP |  |  |  |

| oit 7        |                                             |                    |                   |                   |                  |                 | bit (  |  |  |  |

|              |                                             |                    |                   |                   |                  |                 |        |  |  |  |

| Legend:      |                                             |                    |                   |                   |                  |                 |        |  |  |  |

| R = Readable | e bit                                       | W = Writable       | bit               | U = Unimplem      | nented bit, read | l as '0'        |        |  |  |  |

| n = Value at | POR                                         | '1' = Bit is set   |                   | '0' = Bit is clea | ared             | x = Bit is unkr | iown   |  |  |  |

| pit 7        | OSCFIP: Os                                  | cillator Fail Inte | rrupt Prioritv bi | t                 |                  |                 |        |  |  |  |

|              | 1 = High pric<br>0 = Low prio               | ority              |                   | -                 |                  |                 |        |  |  |  |

| oit 6        | •                                           | arator Interrupt   | Priority bit      |                   |                  |                 |        |  |  |  |

|              | 1 = High pricond0 = Low prio                | •                  |                   |                   |                  |                 |        |  |  |  |

| oit 5        | Unimplemen                                  | ted: Read as '     | 0'                |                   |                  |                 |        |  |  |  |

| oit 4        | EEIP: Data E                                | EPROM/Flash        | Write Operatio    | on Interrupt Prio | rity bit         |                 |        |  |  |  |

|              | 1 = High pric<br>0 = Low prio               | •                  |                   |                   |                  |                 |        |  |  |  |

| oit 3        | BCLIP: Bus Collision Interrupt Priority bit |                    |                   |                   |                  |                 |        |  |  |  |

|              | 1 = High pricts 0 = Low pricts 1            |                    |                   |                   |                  |                 |        |  |  |  |

| oit 2        | HLVDIP: Hig                                 | h/Low-Voltage      | Detect Interrup   | t Priority bit    |                  |                 |        |  |  |  |

|              | 1 = High pric0 = Low prio                   |                    |                   |                   |                  |                 |        |  |  |  |

| oit 1        | TMR3IP: TM                                  | R3 Overflow In     | terrupt Priority  | bit               |                  |                 |        |  |  |  |

|              | 1 = High pric<br>0 = Low prio               | •                  |                   |                   |                  |                 |        |  |  |  |

| oit 0        | CCP2IP: CC                                  | P2 Interrupt Pri   | ority bit         |                   |                  |                 |        |  |  |  |

|              | 1 = High pric                               | nrity              |                   |                   |                  |                 |        |  |  |  |

## REGISTER 9-9: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

## 15.1 CCP Module Configuration

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

#### 15.1.1 CCP MODULES AND TIMER RESOURCES

The CCP modules utilize Timers 1, 2 or 3, depending on the mode selected. Timer1 and Timer3 are available to modules in Capture or Compare modes, while Timer2 is available for modules in PWM mode.

## TABLE 15-1:CCP MODE – TIMER<br/>RESOURCE

| CCP/ECCP Mode | Timer Resource   |

|---------------|------------------|

| Capture       | Timer1 or Timer3 |

| Compare       | Timer1 or Timer3 |

| PWM           | Timer2           |

The assignment of a particular timer to a module is determined by the Timer to CCP enable bits in the T3CON register (Register 14-1). Both modules may be active at any given time and may share the same timer resource if they are configured to operate in the same mode (Capture/Compare or PWM) at the same time. The interactions between the two modules are summarized in Figure 15-1 and Figure 15-2. In Timer1 in Asynchronous Counter mode, the capture operation will not work.

## 15.1.2 CCP2 PIN ASSIGNMENT

The pin assignment for CCP2 (Capture input, Compare and PWM output) can change, based on device configuration. The CCP2MX Configuration bit determines which pin CCP2 is multiplexed to. By default, it is assigned to RC1 (CCP2MX = 1). If the Configuration bit is cleared, CCP2 is multiplexed with RB3.

Changing the pin assignment of CCP2 does not automatically change any requirements for configuring the port pin. Users must always verify that the appropriate TRIS register is configured correctly for CCP2 operation, regardless of where it is located.

## TABLE 15-2: INTERACTIONS BETWEEN CCP1 AND CCP2 FOR TIMER RESOURCES

| CCP1 Mode          | CCP2 Mode          | Interaction                                                                                                                                                                                                                                                         |

|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capture            | Capture            | Each module can use TMR1 or TMR3 as the time base. The time base can be different for each CCP.                                                                                                                                                                     |

| Capture            | Compare            | CCP2 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Automatic A/D conversions on trigger event can also be done. Operation of CCP1 could be affected if it is using the same timer as a time base. |

| Compare            | Capture            | CCP1 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Operation of CCP2 could be affected if it is using the same timer as a time base.                                                              |

| Compare            | Compare            | Either module can be configured for the Special Event Trigger to reset the time base.<br>Automatic A/D conversions on CCP2 trigger event can be done. Conflicts may occur if<br>both modules are using the same time base.                                          |

| Capture            | PWM <sup>(1)</sup> | None                                                                                                                                                                                                                                                                |

| Compare            | PWM <sup>(1)</sup> | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | Capture            | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | Compare            | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | PWM <sup>(1)</sup> | Both PWMs will have the same frequency and update rate (TMR2 interrupt).                                                                                                                                                                                            |

Note 1: Includes standard and Enhanced PWM operation.

| R/W-0        | R/W-0                                             | R/W-0                              | R/W-0                | R/W-0                | R/W-0                  | R/W-0               | R/W-0              |

|--------------|---------------------------------------------------|------------------------------------|----------------------|----------------------|------------------------|---------------------|--------------------|

| GCEN         | ACKSTAT                                           | ACKDT <sup>(2)</sup>               | ACKEN <sup>(1)</sup> | RCEN <sup>(1)</sup>  | PEN <sup>(1)</sup>     | RSEN <sup>(1)</sup> | SEN <sup>(1)</sup> |

| oit 7        | ·                                                 |                                    |                      |                      |                        |                     | bit                |

|              |                                                   |                                    |                      |                      |                        |                     |                    |

| Legend:      |                                                   |                                    |                      |                      |                        |                     |                    |

| R = Readab   |                                                   | W = Writable                       |                      | -                    | nented bit, read       |                     |                    |

| -n = Value a | t POR                                             | '1' = Bit is set                   |                      | '0' = Bit is cle     | ared                   | x = Bit is unkn     | own                |

| bit 7        | GCEN: Gene                                        | ral Call Enable                    | bit (Slave mod       | le only)             |                        |                     |                    |

|              |                                                   | nterrupt when a call address dis   | •                    | address (0000h       | ) is received in       | the SSPSR           |                    |

| bit 6        | ACKSTAT: A                                        | cknowledge Sta                     | atus bit (Maste      | r Transmit mod       | e only)                |                     |                    |

|              |                                                   | edge was not re<br>edge was receiv |                      | ave                  |                        |                     |                    |

| bit 5        |                                                   | 0                                  |                      | ceive mode on        | y) <sup>(2)</sup>      |                     |                    |

|              | 1 = Not Ackn<br>0 = Acknowle                      | •                                  |                      |                      |                        |                     |                    |

| oit 4        |                                                   | 0                                  | ience Enable b       | oit (Master Rec      | eive mode onlv         | <sub>)</sub> (1)    |                    |

|              | 1 = Initiates /<br>cleared b                      | Acknowledge so<br>by hardware.     | equence on SD        |                      | -                      | ACKDT data bit.     | Automatical        |

| bit 3        |                                                   | edge sequence<br>ive Enable bit (  |                      | volv)(1)             |                        |                     |                    |

|              |                                                   | Receive mode f                     | -                    | , ing je z           |                        |                     |                    |

| bit 2        |                                                   | ondition Enable                    | bit (Master mo       | ode only)(1)         |                        |                     |                    |

| 511 2        | -                                                 | Stop condition o                   |                      | CL pins. Automa      | atically cleared       | by hardware.        |                    |

| bit 1        | •                                                 |                                    | lition Enable bi     | it (Master mode      | e only) <sup>(1)</sup> |                     |                    |

|              | 1 = Initiates                                     |                                    | condition on S       |                      |                        | ally cleared by h   | ardware.           |

| bit 0        | SEN: Start Co                                     | ondition Enable                    | Stretch Enabl        | e bit <sup>(1)</sup> |                        |                     |                    |

|              | In Master mo<br>1 = Initiates S<br>0 = Start cond | Start condition o                  | n SDA and SC         | CL pins. Automa      | atically cleared       | by hardware.        |                    |

|              |                                                   |                                    |                      | ve transmit and      | l slave receive        | (stretch enable     | d)                 |

|              | or bits ACKEN,<br>et (no spooling)                |                                    |                      |                      |                        |                     |                    |

|              |                                                   |                                    | -                    |                      |                        | nce at the end c    | -                  |

2: Value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.

## 18.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is one of the two serial I/O modules. (Generically, the USART is also known as a Serial Communications Interface or SCI.) The EUSART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a halfduplex, synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The Enhanced USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These make it ideally suited for use in Local Interconnect Network bus (LIN bus) systems.

The EUSART can be configured in the following modes:

- Asynchronous (full duplex) with:

- Auto-wake-up on character reception

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half duplex) with selectable clock polarity

- Synchronous Slave (half duplex) with selectable clock polarity

The pins of the Enhanced USART are multiplexed with PORTC. In order to configure RC6/TX/CK and RC7/RX/DT as an EUSART:

- bit SPEN (RCSTA<7>) must be set (= 1)

- bit TRISC<7> must be set (= 1)

- bit TRISC<6> must be set (= 1)

| Note: | The EUSART control will automatically       |

|-------|---------------------------------------------|

|       | reconfigure the pin from input to output as |

|       | needed.                                     |

The operation of the Enhanced USART module is controlled through three registers:

- · Transmit Status and Control (TXSTA)

- · Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These are detailed on the following pages in Register 18-1, Register 18-2 and Register 18-3, respectively.

## 19.6 A/D Conversions

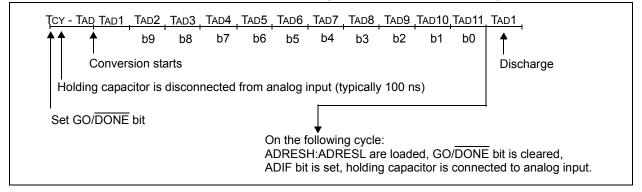

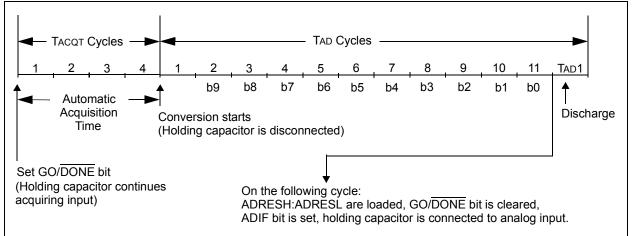

Figure 19-4 shows the operation of the A/D Converter after the GO/DONE bit has been set and the ACQT<2:0> bits are cleared. A conversion is started after the following instruction to allow entry into Sleep mode before the conversion begins.

Figure 19-5 shows the operation of the A/D Converter after the GO/DONE bit has been set and the ACQT<2:0> bits are set to '010', and selecting a 4 TAD acquisition time before the conversion starts.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. This means the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is completed or aborted, a 2 TAD wait is required before the next acquisition can be started. After this wait, acquisition on the selected channel is automatically started.

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

## 19.7 Discharge

The discharge phase is used to initialize the value of the capacitor array. The array is discharged before every sample. This feature helps to optimize the unitygain amplifier, as the circuit always needs to charge the capacitor array, rather than charge/discharge based on previous measure values.

## FIGURE 19-4: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

## FIGURE 19-5: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

## 23.2 Watchdog Timer (WDT)

For PIC18F2420/2520/4420/4520 devices, the WDT is driven by the INTRC source. When the WDT is enabled, the clock source is also enabled. The nominal WDT period is 4 ms and has the same stability as the INTRC oscillator.

The 4 ms period of the WDT is multiplied by a 16-bit postscaler. Any output of the WDT postscaler is selected by a multiplexer, controlled by bits in Configuration Register 2H. Available periods range from 4 ms to 131.072 seconds (2.18 minutes). The WDT and postscaler are cleared when any of the following events occur: a SLEEP or CLRWDT instruction is executed, the IRCF bits (OSCCON<6:4>) are changed or a clock failure has occurred.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and postscaler counts when executed.

- 2: Changing the setting of the IRCF bits (OSCCON<6:4>) clears the WDT and postscaler counts.

- **3:** When a CLRWDT instruction is executed, the postscaler count will be cleared.

## 23.2.1 CONTROL REGISTER

Register 23-14 shows the WDTCON register. This is a readable and writable register which contains a control bit that allows software to override the WDT enable Configuration bit, but only if the Configuration bit has disabled the WDT.

## FIGURE 23-1: WDT BLOCK DIAGRAM

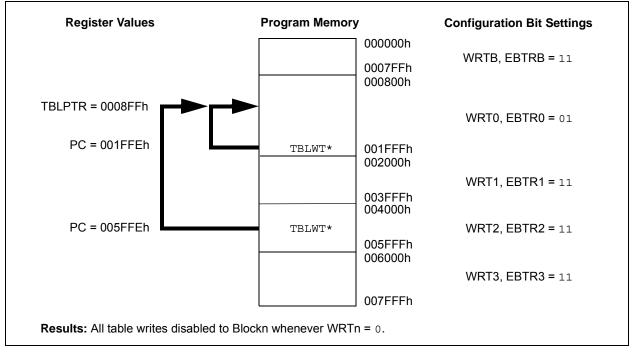

### 23.5.1 PROGRAM MEMORY CODE PROTECTION

The program memory may be read to, or written from, any location using the table read and table write instructions. The Device ID may be read with table reads. The Configuration registers may be read and written with the table read and table write instructions.

In normal execution mode, the CPn bits have no direct effect. CPn bits inhibit external reads and writes. A block of user memory may be protected from table writes if the WRTn Configuration bit is '0'. The EBTRn bits control table reads. For a block of user memory with the EBTRn bit set to '0', a table read instruction that executes from within that block is allowed to read. A table read instruction that executes from a location outside of that block is not allowed to read and will result in reading '0's. Figures 23-6 through 23-8 illustrate table write and table read protection.

Note: Code protection bits may only be written to a '0' from a '1' state. It is not possible to write a '1' to a bit in the '0' state. Code protection bits are only set to '1' by a full chip erase or block erase function. The full chip erase and block erase functions can only be initiated via ICSP or an external programmer.

## FIGURE 23-6: TABLE WRITE (WRTn) DISALLOWED

## 24.1.1 STANDARD INSTRUCTION SET

| ADDLW                                           |               | ADD Lite                          | al to W       | 1    |                          |  |  |  |

|-------------------------------------------------|---------------|-----------------------------------|---------------|------|--------------------------|--|--|--|

| Syntax:                                         |               | ADDLW                             | k             |      |                          |  |  |  |

| Operands:                                       |               | $0 \le k \le 255$                 |               |      |                          |  |  |  |

| Operation:                                      |               | (W) + k $\rightarrow$ V           | Ν             |      |                          |  |  |  |

| Status Affect                                   | ted:          | N, OV, C, D                       | 0C, Z         |      |                          |  |  |  |

| Encoding:                                       |               | 0000                              | 1111          | kkkk | kkkk                     |  |  |  |

| Description:                                    |               | The conten<br>8-bit literal<br>W. |               |      | d to the<br>is placed in |  |  |  |

| Words:                                          |               | 1                                 | 1             |      |                          |  |  |  |

| Cycles:                                         |               | 1                                 |               |      |                          |  |  |  |

| Q Cycle Ac                                      | tivity:       |                                   |               |      |                          |  |  |  |

| Q                                               | 1             | Q2                                | Q3            | 3    | Q4                       |  |  |  |

| Deco                                            | ode           | Read<br>literal 'k'               | Proce<br>Data |      | Write to W               |  |  |  |

| <u>Example:</u><br>Before<br>W<br>After In<br>W | =<br>structio | tion<br>10h                       | .5h           |      |                          |  |  |  |

| ADDWF            | ADD W t                                                                                                                                                                                                    | o f                                                                                                                           |                                                                                                                                                          |                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Syntax:          | ADDWF                                                                                                                                                                                                      | f {,d {,a}                                                                                                                    | •}                                                                                                                                                       |                                                                                                |

| Operands:        | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                        | i                                                                                                                             |                                                                                                                                                          |                                                                                                |

| Operation:       | (W) + (f) –                                                                                                                                                                                                | → dest                                                                                                                        |                                                                                                                                                          |                                                                                                |

| Status Affected: | N, OV, C,                                                                                                                                                                                                  | DC, Z                                                                                                                         |                                                                                                                                                          |                                                                                                |

| Encoding:        | 0010                                                                                                                                                                                                       | 01da                                                                                                                          | ffff                                                                                                                                                     | ffff                                                                                           |

| Description:     | Add W to result is st<br>result is st<br>(default).<br>If 'a' is 'o',<br>If 'a' is '1',<br>GPR bank<br>If 'a' is '0' a<br>set is enat<br>in Indexed<br>mode whe<br>Section 2:<br>Bit-Orient<br>Literal Off | the Access<br>the BSR (default).<br>(default).<br>and the expled, this is<br>Literal O<br>never f ≤<br>4.2.3 "By<br>ed Instru | . If 'd' is '1<br>s in registe<br>ss Bank is<br>is used to<br>xtended in<br>instruction<br>ffset Addre<br>95 (5Fh). S<br><b>te-Oriente</b><br>ictions in | r ff<br>selected.<br>select the<br>struction<br>operates<br>essing<br>See<br>ed and<br>Indexed |

| Words:           | 1                                                                                                                                                                                                          |                                                                                                                               |                                                                                                                                                          |                                                                                                |

| Cycles:          | 1                                                                                                                                                                                                          |                                                                                                                               |                                                                                                                                                          |                                                                                                |

| QC          | ycle Activity:               |                      |              |                 |      |                      |

|-------------|------------------------------|----------------------|--------------|-----------------|------|----------------------|

|             | Q1                           |                      | Q2           | Q3              |      | Q4                   |

|             | Decode                       | Read<br>register 'f' |              | Process<br>Data |      | Write to destination |

| <u>Exan</u> | Example:                     |                      | DDWF         | REG,            | 0, 0 |                      |

|             | Before Instruc               |                      |              |                 |      |                      |

|             | W<br>REG<br>After Instructio | =<br>=<br>on         | 17h<br>0C2h  |                 |      |                      |

|             | W<br>REG                     | =<br>=               | 0D9h<br>0C2h |                 |      |                      |

| Note: | All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in       |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s). |

| IORLW                 | Inclusive           | OR Lite                                                                           | eral with | W          |  |  |  |

|-----------------------|---------------------|-----------------------------------------------------------------------------------|-----------|------------|--|--|--|

| Syntax:               | IORLW k             |                                                                                   |           |            |  |  |  |

| Operands:             | $0 \le k \le 255$   | 5                                                                                 |           |            |  |  |  |

| Operation:            | (W) .OR. k          | ightarrow W                                                                       |           |            |  |  |  |

| Status Affected:      | N, Z                |                                                                                   |           |            |  |  |  |

| Encoding:             | 0000                | 1001                                                                              | kkkk      | kkkk       |  |  |  |

| Description:          |                     | The contents of W are ORed with the 8-bit literal 'k'. The result is placed in W. |           |            |  |  |  |

| Words:                | 1                   |                                                                                   |           |            |  |  |  |

| Cycles:               | 1                   |                                                                                   |           |            |  |  |  |

| Q Cycle Activity:     |                     |                                                                                   |           |            |  |  |  |

| Q1                    | Q2                  | Q3                                                                                | 1         | Q4         |  |  |  |

| Decode                | Read<br>literal 'k' | Proce<br>Dat                                                                      |           | /rite to W |  |  |  |

| Example:              | IORLW               | 35h                                                                               |           |            |  |  |  |

| Before Instruc        | tion                |                                                                                   |           |            |  |  |  |

| W<br>After Instructio | = 9Ah<br>on         |                                                                                   |           |            |  |  |  |

| IORWF Inclusive OR W with f          |                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                          |      |                        |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------|--|--|--|

| Syntax:                              | IORWF 1                                                                                                                                                                                                                                                | f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                              |      |                        |  |  |  |

| Operands:                            | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                  | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                |      |                        |  |  |  |

| Operation:                           | (W) .OR. (f                                                                                                                                                                                                                                            | $) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                     |      |                        |  |  |  |

| Status Affected:                     | N, Z                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                          |      |                        |  |  |  |

| Encoding:                            | 0001                                                                                                                                                                                                                                                   | 00da                                                                                                                                                                                                                                                                                                                                                                     | ffff | ffff                   |  |  |  |

|                                      | <ul> <li>'0', the result is<br/>the result is<br/>(default).</li> <li>If 'a' is '0', t</li> <li>If 'a' is '1', t</li> <li>GPR bank</li> <li>If 'a' is '0' a</li> <li>set is enab</li> <li>in Indexed</li> <li>mode wher</li> <li>Section 24</li> </ul> | If 'a' is '0', the Access Bank is selected<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed |      |                        |  |  |  |

| Words:                               | 1                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                          |      |                        |  |  |  |

| Cycles:                              | 1                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                          |      |                        |  |  |  |

| Q Cycle Activity:                    |                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                          |      |                        |  |  |  |

| Q1                                   | Q2                                                                                                                                                                                                                                                     | Q3                                                                                                                                                                                                                                                                                                                                                                       | 5    | Q4                     |  |  |  |

| Decode                               | Read<br>register 'f'                                                                                                                                                                                                                                   | Proce<br>Dat                                                                                                                                                                                                                                                                                                                                                             |      | Write to<br>estination |  |  |  |

| Example:<br>Before Instruc<br>RESULT | tion                                                                                                                                                                                                                                                   | ESULT,                                                                                                                                                                                                                                                                                                                                                                   | 0, 1 |                        |  |  |  |

| Before Instruction |     |

|--------------------|-----|

| RESULT =           | 13h |

| W =                | 91h |

| After Instruction  |     |

| RESULT =           | 13h |

| \// =              | 93h |

W

= BFh

26.2

## DC Characteristics: Power-Down and Supply Current PIC18F2420/2520/4420/4520 (Industrial) PIC18LF2420/2520/4420/4520 (Industrial) (Continued)

| PIC18LF2420/2520/4420/4520<br>(Industrial)<br>PIC18F2420/2520/4420/4520<br>(Industrial, Extended) |                                     |                                                                                                                                                                                         | -   | rating ( | •      | ess otherwise states $4 \le +85^{\circ}$ C for indust |                                                          |

|---------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|--------|-------------------------------------------------------|----------------------------------------------------------|

|                                                                                                   |                                     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |     |          |        |                                                       |                                                          |

| Param<br>No.                                                                                      | Device                              | Тур                                                                                                                                                                                     | Max | Units    |        | Conditio                                              | ns                                                       |

|                                                                                                   | Supply Current (IDD) <sup>(2)</sup> |                                                                                                                                                                                         |     |          |        |                                                       |                                                          |

|                                                                                                   | PIC18LF2X2X/4X20                    | 165                                                                                                                                                                                     | 250 | μΑ       | -40°C  |                                                       |                                                          |