Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                        |

|----------------------------|--------------------------------------------------------|

| Product Status             | Obsolete                                               |

| Core Processor             | Z8                                                     |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 12MHz                                                  |

| Connectivity               | EBI/EMI                                                |

| Peripherals                | POR, WDT                                               |

| Number of I/O              | 24                                                     |

| Program Memory Size        | 8KB (8K x 8)                                           |

| Program Memory Type        | OTP                                                    |

| EEPROM Size                | -                                                      |

| RAM Size                   | 237 x 8                                                |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                            |

| Data Converters            | -                                                      |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                        |

| Mounting Type              | Through Hole                                           |

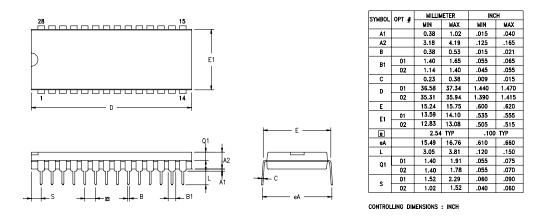

| Package / Case             | 28-DIP (0.600", 15.24mm)                               |

| Supplier Device Package    | -                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8673312psc |

|                            |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **z**ilog<sup>°</sup>

# Warning: DO NOT USE IN LIFE SUPPORT

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, Z8 Encore! XP, Z8 Encore! MC, Crimzon, eZ80, and ZNEO are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

ISO 9001:2000 FS 507510 Zilog products are designed and manufactured under an ISO registered 9001:2000 Quality Management System. For more details, please visit www.zilog.com/quality.

zilog | III

# **Revision History**

Each instance in Revision History reflects a change to this document from its previous revision. For more details, refer to the corresponding pages and appropriate links in the table below.

| Date     | <b>Revision Level</b> | Description     | Page No |

|----------|-----------------------|-----------------|---------|

| May 2008 | 01                    | Original issue. | All     |

# zilog<sup>°</sup> <sub>iv</sub>

# **Table of Contents**

| Architectural Overview 1   Features 1 |

|---------------------------------------|

| Functional Block Diagram 3            |

| Pin Description                       |

| Electrical Characteristics            |

| Absolute Maximum Ratings              |

| Standard Test Conditions              |

| Capacitance                           |

| DC Electrical Characteristics         |

| Handshake Timing Diagrams             |

| Pin Functions                         |

| EPROM Programming Mode 37             |

| Application Precaution                |

| Standard Mode                         |

| Functional Description 46             |

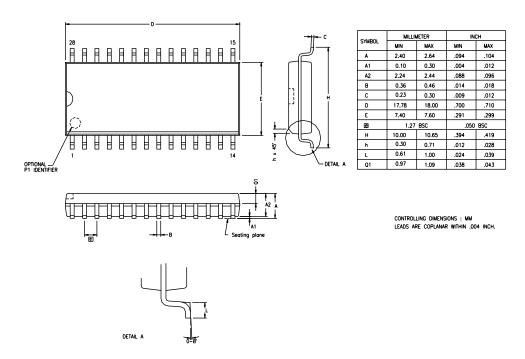

| Package Information                   |

| Ordering Information                  |

| Customer Support                      |

# zilog 4

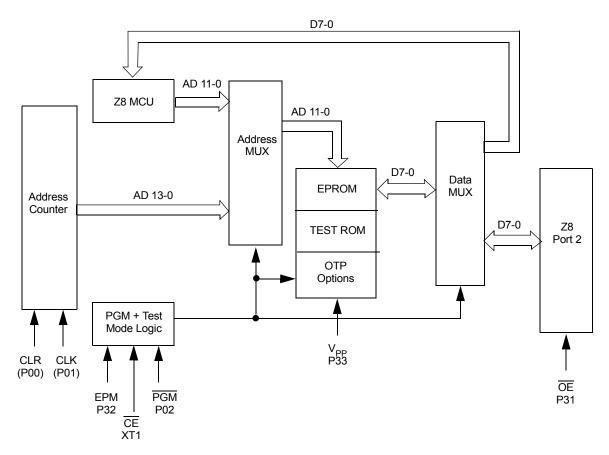

Figure 2. EPROM Programming Block Diagram

zilog | 17

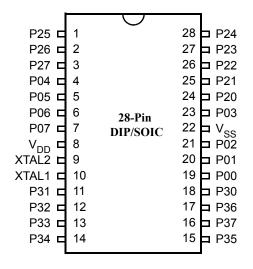

Figure 9. Standard Mode 28-Pin DIP/SOIC Pin Configuration

| Pin No | Symbol          | Function                     | Direction    |

|--------|-----------------|------------------------------|--------------|

| 1-3    | P25-P27         | Port 2, Pins 5,6,            | Input/Output |

| 4-7    | P04-P07         | Port 0, Pins 4,5,6,7 In/Outp | out          |

| 8      | V <sub>CC</sub> | Power Supply                 |              |

| 9      | XTAL2           | Crystal Oscillator           | Output       |

| 10     | XTAL1           | Crystal Oscillator           | Input        |

| 11-13  | P31-P33         | Port 3, Pins 1,2,3           | Input        |

| 14-15  | P34-P35         | Port 3, Pins 4,5             | Output       |

| 16     | P37             | Port 3, Pin 7 Output         |              |

| 17     | P36             | Port 3, Pin 6 Output         |              |

| 18     | P30             | Port 3, Pin 0                | Input        |

| 19-21  | P00-P02         | Port 0, Pins 0,1,2 Input     |              |

| 22     | V <sub>SS</sub> | Ground                       |              |

| 23     | P03             | Port 0, Pin 3 Input/         |              |

| 24-28  | P20-P24         | Port 2, Pins 0,1,2,3,4       | Input/Output |

Table 8. 28-Pin DIP/SOIC/PLCC Pin Identification Standard Mode

Zilog<sup>28</sup>

# Table 13. DC Electrical Characteristics $T_A = 0$ °C to +70 °C, 12 MHz (Continued)

| No. | Symbol    | Parameter                                                        | V <sub>cc</sub> <sup>1</sup> | Min | Мах | Units | Notes |

|-----|-----------|------------------------------------------------------------------|------------------------------|-----|-----|-------|-------|

| 4   | TwAS      | AS Low Width                                                     | 3.5V                         | 55  |     | ns    | 2     |

|     |           |                                                                  | 5.5V                         | 55  |     | ns    | 2     |

| 5   | TdAS(DS)  | Address Float to DS Fall                                         | 3.5V                         | 0   |     | ns    |       |

|     |           |                                                                  | 5.5V                         | 0   |     | ns    |       |

| 6   | TwDSR     | DS (Read) Low Width                                              | 3.5V                         | 200 |     | ns    | 2,3   |

|     |           |                                                                  | 5.5V                         | 200 |     | ns    | 2,3   |

| 7   | TwDSW     | DS (Write) Low Width                                             | 3.5V                         | 110 |     | ns    | 2,3   |

|     |           |                                                                  | 5.5V                         | 110 |     | ns    | 2,3   |

| 8   | TdDSR(DR) | DS Fail to Read Data Req'd Valid                                 | 3.5V                         |     | 150 | ns    | 2,3   |

|     |           |                                                                  | 5.5V                         |     | 150 | ns    | 2,3   |

| 9   | ThDR(DS)  | hDR(DS) Read Data to DS Rise Hold Time                           |                              | 0   |     | ns    | 2     |

|     |           |                                                                  | 5.5V                         | 0   |     | ns    | 2     |

| 10  | TdDS(A)   | Delay                                                            | 3.5V                         | 45  |     | ns    | 2     |

|     |           |                                                                  | 5.5V                         | 55  |     | ns    | 2     |

| 11  | TdDS(AS)  | $\overline{\text{DS}}$ Rise to $\overline{\text{AS}}$ Fall Delay | 3.5V                         | 30  |     | ns    | 2     |

|     |           |                                                                  | 5.5V                         | 45  |     | ns    | 2     |

| 12  | TdR/W(AS) | R/W Valid to AS Rise Delay                                       | 3.5V                         | 45  |     | ns    | 2     |

|     |           |                                                                  | 5.5V                         | 45  |     | ns    | 2     |

| 13  | TdDS(R/W) | DS Rise to R/W Not Valid                                         | 3.5V                         | 45  |     | ns    | 2     |

|     |           |                                                                  | 5.5V                         | 45  |     | ns    | 2     |

| 14  | TdDW(DSW) | Write Data Valid to DS Fall (Write)                              | 3.5V                         | 55  |     | ns    | 2     |

|     |           | Delay                                                            |                              | 55  |     | ns    | 2     |

| 15  | TdDS(DW)  | DS Rise to Write Data Not Valid                                  | 3.5V                         | 45  |     | ns    | 2     |

|     |           | Delay                                                            | 5.5V                         | 55  |     | ns    | 2     |

| 16  | TdA(DR)   | Address Valid to Read Data Req'd                                 | 3.5V                         |     | 310 | ns    | 2,3   |

|     |           | Valid                                                            | 5.5V                         |     | 310 | ns    | 2,3   |

| 17  | TdAS(DS)  | $\overline{\text{AS}}$ Rise to $\overline{\text{DS}}$ Fall Delay | 3.5V                         | 65  |     | ns    | 2     |

|     |           |                                                                  | 5.5V                         | 65  |     | ns    | 2     |

# Zilog <sub>32</sub>

| No | Symbol | Parameter               | V <sub>cc</sub> <sup>1</sup> | Min  | Max  | Min  | Max  | Units | Notes   |

|----|--------|-------------------------|------------------------------|------|------|------|------|-------|---------|

| 5  | TwTinH | Timer Input High Width  | 3.5V                         | 5TpC |      | 5TpC |      |       | 2,3,4   |

|    |        |                         | 5.5V                         | 5TpC |      | 5TpC |      |       | 2,3,4   |

| 6  | TpTin  | Timer Input Period      | 3.5V                         | 8TpC |      | 8TpC |      |       | 2,3,4   |

|    |        |                         | 5.5V                         | 8TpC |      | 8TpC |      |       | 2,3,4   |

| 7  | TrTin, | Timer Input Rise & Fall | 3.5V                         |      | 100  |      | 100  | ns    | 2,3,4   |

|    | TfTin  | Timer                   | 5.5V                         |      | 100  |      | 100  | ns    | 2,3,4   |

| 8A | TwIL   | Int. Request Low Time   | 3.5V                         | 100  |      | 100  |      | ns    | 2,3,4,5 |

|    |        |                         | 5.5V                         | 70   |      | 70   |      | ns    | 2,3,4,5 |

| 8B | TwIL   | Int. Request Low Time   | 3.5V                         | 5TpC |      | 5TpC |      |       | 2,3,4,6 |

|    |        |                         | 5.5V                         | 5TpC |      | 5TpC |      |       | 2,3,4,6 |

| 9  | TwIH   | Int. Request Input High | 3.5V                         | 5TpC |      | 5TpC |      |       | 2,3,4,5 |

|    |        | Time                    | 5.5V                         | 5TpC |      | 5TpC |      |       | 2,3,4,5 |

| 10 | Twsm   | Stop Mode Recovery      | 3.5V                         | 12   |      | 12   |      | ns    | 4,7     |

|    |        | Width Spec              | 5.5V                         | 12   |      | 12   |      | ns    | 4,7     |

| 11 | Tost   | Oscillator Startup Time | 3.5V                         |      | 5TpC |      | 5TpC |       | 4,7,8   |

|    |        |                         | 5.5V                         |      | 5TpC |      | 5TpC |       | 4,7,8   |

### Table 15. Additional Timing Table (Divide-By-One Mode) $T_A = 0$ °C to +70 °C (Continued)

Notes

1. The V<sub>CC</sub> voltage specification of 5.5 V guarantees 5.0 V  $\pm$  0.5 V and the V<sub>CC</sub> voltage specification of 3.5 V guarantees only 3.5 V.

2. Timing Reference uses 0.7  $V_{CC}$  for a logic 1 and 0.2  $V_{CC};$  for a logic 0.

3. SMR D1 = 0.

4. Maximum frequency for internal system clock is 4 MHz when using Low EMI OSC PCON Bit D7 = 0.

5. Interrupt request via Port 3 (P31-P33).

6. Interrupt request via Port 3 (P30).

7. SMR-D5 = 1, POR STOP Mode Delay is on.

8. For RC and LC oscillator, and for oscillator driven by clock driver.

#### Table 16. Additional Timing Table (Divide-By-One Mode) $T_A = -40$ °C to +105 °C

| No | Symbol | Parameter          | V <sub>cc</sub> <sup>1</sup> | Min | Max | Min | Max | Units | Notes |

|----|--------|--------------------|------------------------------|-----|-----|-----|-----|-------|-------|

| 1  | ТрС    | Input Clock Period | 4.5V                         | 250 | DC  | 166 | DC  | ns    | 2,3,4 |

|    |        |                    | 5.5V                         | 250 | DC  | 166 | DC  | ns    | 2,3,4 |

# zilog 4

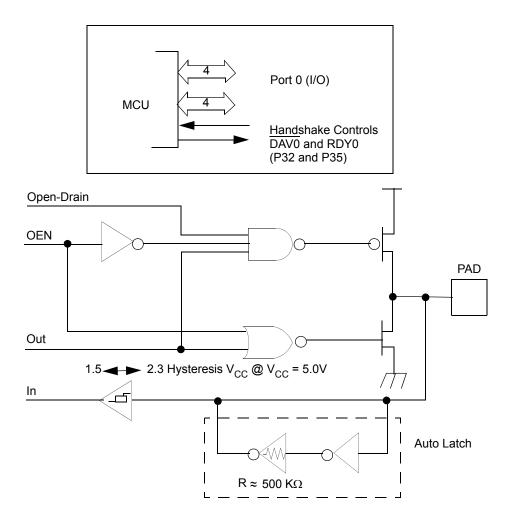

Figure 18. Port 0 Configuration

**Port 1 (P17-P10)**. Port 1 is an 8-bit, bidirectional, CMOS-compatible port with multiplexed Address (A7-A0) and Data (D7-D0) ports. These eight I/O lines can be programmed as inputs or outputs or can be configured under software control as an Address/ Data port for interfacing external memory. The input buffers are Schmitt-triggered and the output buffers can be globally programmed as either push-pull or open-drain. Low EMI output buffers can be globally programmed by the software. Port 1 can be placed under handshake control. In this configuration, Port 3, lines P33 and P34 are used as the handshake controls RDY1 and DAV1 (Ready and Data Available). To interface external memory, Port 1 must be programmed for the multiplexed Address/Data mode. If more than 256 external locations are required, Port 0 outputs the additional lines (see Figure 19).

Zilog 42

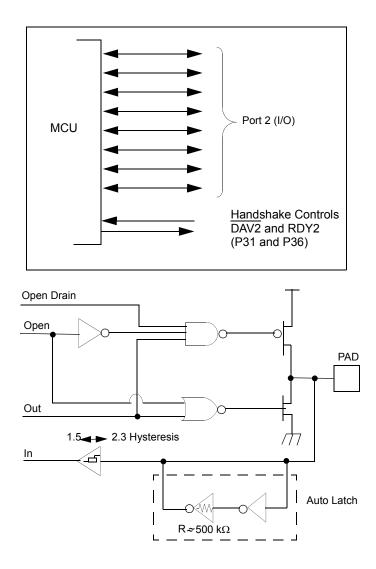

In Handshake Mode, Port 3 lines P31 and P36 are used as handshake control lines. The handshake direction is determined by the configuration (input or output) assigned to bit 7 of Port 2 (see Figure 20).

Figure 20. Port 2 Configuration

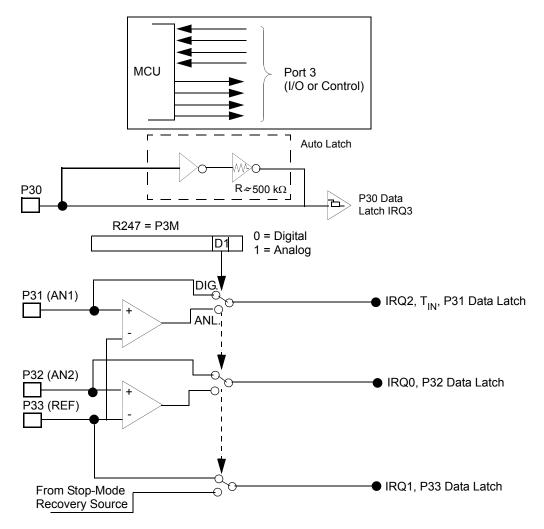

**Port 3 (P37-P30)**. Port 3 is an 8-bit, CMOS-compatible port with four fixed inputs (P33-P30) and four fixed outputs (P37-P34). These eight lines can be configured by software for interrupt and handshake control functions. Port 3, Pin 0 is Schmitt- triggered. P31, P32, and P33 are standard CMOS inputs with single trip point (no Auto Latches) and P34, P35, P36, and P37 are push-pull output lines. Low EMI output buffers can be globally programmed by the software. Two on-board comparators can process analog signals on P31

zilog .

and P32 with reference to the voltage on P33. The analog function is enabled by setting the D1 of Port 3 Mode Register (P3M). The comparator output can be outputted from P34 and P37, respectively, by setting PCON register Bit D0 to 1 state. For the interrupt function, P30 and P33 are falling edge triggered interrupt inputs. P31 and P32 can be programmed as falling, rising or both edges triggered interrupt inputs (see Figure 21). Access to Counter/Timer 1 is made through P31 ( $T_{IN}$ ) and P36 ( $T_{OUT}$ ). Handshake tines for Port 0, Port 1, and Port 2 are also available on Port 3 (see Table 19).

**Note:** When enabling or disabling analog mode, the following is recommended:

- 1. Allow two NOP decays before reading this comparator output.

- 2. Disable global interrupts, switch to analog mode, clear interrupts, and then re-enable interrupts.

- 3. IRQ register bits 3 to 0 must be cleared after enabling analog mode.

- **Note:** P33-P30 differs from the Z86C33/C43/233/243 in that there is no clamping diode to  $V_{CC}$  due to the EPROM high-voltage circuits. Exceeding the  $V_{IH}$  maximum specification during standard operating mode may cause the device to enter EPROM mode.

>

>

Figure 21. Port 3 Configuration

zilog

| Pin | I/O | CTC1             | Analog  | Interrup | t P0 HS | P1 HS | P2 HS | Ext |

|-----|-----|------------------|---------|----------|---------|-------|-------|-----|

| P30 | IN  |                  |         | IRQ3     |         |       |       |     |

| P31 | IN  | T <sub>IN</sub>  | AN1     | IRQ2     |         | D/R   |       |     |

| P32 | IN  |                  | AN2     | IRQ0     | D/R     |       |       |     |

| P33 | IN  |                  | REF     | IRQ1     |         | D/R   |       |     |

| P34 | OUT |                  | AN1-Out |          |         | R/D   |       | DM  |

| P35 | OUT |                  |         |          | R/D     |       |       |     |

| P36 | OUT | T <sub>OUT</sub> |         |          |         | R/D   |       |     |

| P37 | OUT |                  | An2-Out |          |         |       |       |     |

|     |     |                  |         |          |         |       |       |     |

#### Table 19. Port 3 Pin Assignments

**Comparator Inputs**. Port 3, P31, and P32, each have a comparator front end. The comparator reference voltage P33 is common to both comparators. In analog mode, P31 and P32 are the positive input of the comparators and P33 is the reference voltage of the comparators.

**Auto Latch**. The Auto Latch puts valid CMOS levels on all CMOS inputs (except P33-P31) that are not externally driven. Whether this level is 0 or 1, cannot be determined. A valid CMOS level, rather than a floating node, reduces excessive supply current flow in the input buffer. Auto Latches are available on Port 0, Port 1, Port 2, and P30. There are no Auto Latches on P31, P32, and P33.

**Low EMI Emission**. The Z86E43/743/E44 can be programmed to operate in a low EMI Emission Mode in the PCON register. The oscillator and all I/O ports can be programmed as low EMI emission mode independently. Use of this feature results in:

- The pre-drivers slew rate reduced to 10 ns typical.

- Low EMI output drivers have resistance of 200 Ohms (typical).

- Low EMI Oscillator.

- Internal SCLK/TCLK= XTAL operation limited to a maximum of 4 MHz 250 ns cycle time, when Low EMI Oscillator is selected.

Note: For emulation only: Do not set the emulator to emulate Port 1 in low EMI mode. Port 1 must always be configured in Standard Mode.

Zilog 46

# **Functional Description**

>

>

The MCU incorporates the following special functions to enhance the standard Z8 architecture to provide the user with increased design flexibility.

**RESET**. The device is reset in one of three ways:

- 1. Power-On Reset

- 2. Watchdog Timer

- 3. Stop Mode Recovery Source

- **Note:** Having the Auto Power-On Reset circuitry built-in, the MCU does not need to be connected to an external power-on reset circuit. The reset time is  $T_{POR}$ . The MCU does not re-initialize WDTMR, SMR, P2M, and P3M registers to their reset values on a Stop Mode Recovery operation.

- **Note:** The device  $V_{CC}$  must rise up to the operating  $V_{CC}$  specification before the  $T_{POR}$  expires.

**Program Memory**. The MCU can address up to 4/8/16 KB of Internal Program Memory (see Figure 22). The first 12 bytes of program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors that correspond to the six available interrupts. For EPROM mode, byte 12 (000Ch) to address 4095 (0FFFh)/8191 (1FFFh)/16384 (3FFFh), consists of programmable EPROM. After reset, the program counter points at the address 000Ch, which is the starting address of the user program.

In ROMless mode, the Z86E43/743/E44 can address up to 64 KB of External Program Memory. The ROM/ROMless option is only available on the 44-pin devices.

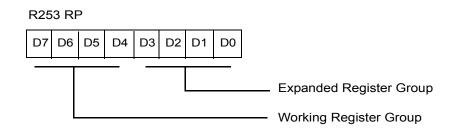

Default after RESET = 00h

#### Figure 24. Register Pointer Register

**Expanded Register File** (ERF). The register file has been expanded to allow for additional system control registers, mapping of additional peripheral devices and input/output ports into the register address area. The Z8 register address space RO through R15 is implemented as 16 groups of 16 registers per group (see Figure 26). These register banks are known as the Expanded Register File (ERF).

The low nibble (D3-D0) of the Register Pointer (RP) select the active ERF Bank, and the high nibble (D7-D4) of register RP select the working register group. Three system configuration registers reside in the Expanded Register File at bank FH: PCON, SMR, and WDTMR. The rest of the Expanded Register is not physically implemented and is reserved for future expansion.

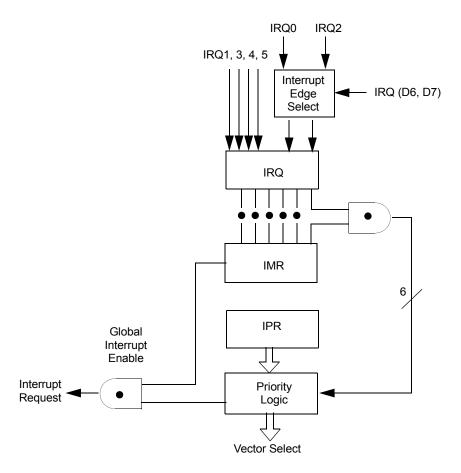

| Name | Source                      | Vector Location | Comments                                      |

|------|-----------------------------|-----------------|-----------------------------------------------|

| IRQ0 | DAV0, IRQ0                  | 0,1             | External (P32), Rising/Falling Edge Triggered |

| IRQ1 | IRQ1                        | 2,3             | External (P33), Falling Edge Triggered        |

| IRQ2 | DAV2, IRQ2, T <sub>IN</sub> | 4,5             | External (P31), Rising/Falling Edge Triggered |

| IRQ3 | IRQ3                        | 6,7             | External (P30), Falling Edge Triggered        |

| 1RQ4 | Т0                          | 8,9             | Internal                                      |

| IRQ5 | T1                          | 10,11           | Internal                                      |

PS022901-0508

\* Default setting after RESET

\*\* Default setting after RESET and STOP-Mode Recovery

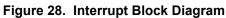

#### Figure 31. Stop Mode Recovery Register (Write-Only Except Bit D7, Which Is Read-Only)

**SCLK/TCLK Divide-by-16 Select (D0)**. This bit of the SMR controls a divide-by-16 prescaler of SCLK/TCLK. The purpose of this control is to selectively reduce device power consumption during normal processor execution (SCLK control) and/or HALT mode (where TCLK sources counter/timers and interrupt logic).

**External Clock Divide-by-Two (D1)**. This bit can eliminate the oscillator divide-by-two circuitry. When this bit is 0, the System Clock (SCLK) and Timer Clock (TCLK) are equal to the external clock frequency divided by two. The SCLK/TCLK is equal to the external clock frequency when this bit is set (D1=1). Using this bit together with D7 of PCON further helps lower EMI (that is, D7 (PCON) = 0, D1 (SMR) = 1). The default setting is zero.

**Stop Mode Recovery Source (D2, D3, and D4)**. These three bits of the SMR register specify the wake up source of the Stop Mode Recovery (Figure 32). Table 22 shows the SMR source selected with the setting of D2 to D4. P33-P31 cannot be used to wake up

Zilog

Reset and initially enabled by executing the WDT instruction and refreshed on subsequent executions of the WDT instruction. The WDT is driven either by an on-board RC oscillator or an external oscillator from XTAL1 pin. The POR clock source is selected with bit 4 of the WDT register.

**Note:** *Execution of the WDT instruction affects the Z (Zero), S (Sign), and V (Overflow) flags.*

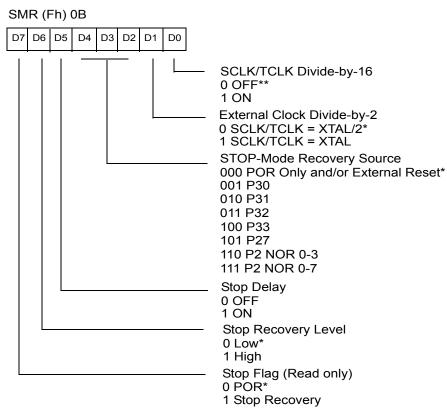

**WDT Time-Out Period (D0 and D1)**. Bits 0 and 1 control a tap circuit that determines the time-out periods that can be obtained (Table 23). The default value of DO and Dl are 1 and 0, respectively.

| D1 | DO | Internal RC<br>OSC | Time-out of the<br>System Clock |

|----|----|--------------------|---------------------------------|

| 0  | 0  | 5 ms               | 128 SCLK                        |

| 0  | 1  | 10 ms <sup>1</sup> | 256 SCLK <sup>1</sup>           |

| 1  | 0  | 20 ms              | 512 SCLK                        |

| 1  | 1  | 80 ms              | 2048 SCLK                       |

#### Table 23. Time-out Period of WDT

>

**WDT During HALT Mode (D2)**. This bit determines whether or not the WDT is active during HALT Mode. A "1" indicates that the WDT is active during HALT. A "0" disables the WDT in HALT Mode. The default value is "1 ". WDT During STOP Mode (D3). This bit determines whether or not the WDT is active during STOP mode. A "1" indicates active during STOP. A "0" disables the WDT during STOP Mode. This is applicable only when the WDT clock source is the internal RC oscillator.

**Clock Source For WDT (D4)**. This bit determines which oscillator source is used to clock the internal POR and WDT counter chain. If the bit is a 1, the internal RC oscillator is bypassed and the POR and WDT clock source is driven from the external pin, XTAL1, and the WDT is stopped in STOP Mode. The default configuration of this bit is 0, which selects the RC oscillator.

**Permanent WDT**. When this feature is enabled, the WDT is enabled after reset and will operate in Run and HALT Mode. The control bits in the WDTMR do not affect the WDT operation. If the clock source of the WDT is the internal RC oscillator, then the WDT will run in STOP mode. If the clock source of the WDT is the XTAL1 pin, then the WDT will not run in STOP mode.

\* Default setting after RESET

#### Figure 38. Watchdog Timer Mode Register (Write Only)

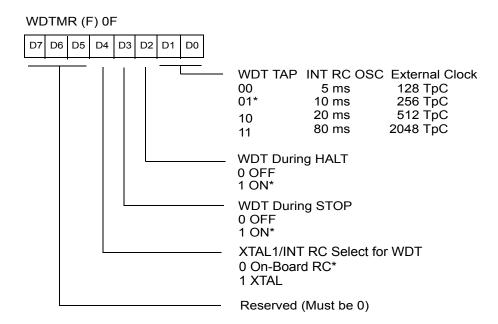

Note: Not used in conjunction with SMR Source

#### Figure 39. Stop Mode Recovery Register2 (Write Only)

Figure 59. 28-Pin SOIC Package Diagram

Zilog <sub>80</sub>

# **Customer Support**

For answers to technical questions about the product, documentation, or any other issues with Zilog's offerings, please visit Zilog's Knowledge Base at <a href="http://www.zilog.com/kb">http://www.zilog.com/kb</a>.

For any comments, detail technical questions, or reporting problems, please visit Zilog's Technical Support at <u>http://support.zilog.com</u>.