#### Zilog - Z8673312VSG Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                        |

|----------------------------|--------------------------------------------------------|

| Product Status             | Obsolete                                               |

| Core Processor             | Z8                                                     |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 12MHz                                                  |

| Connectivity               | EBI/EMI                                                |

| Peripherals                | POR, WDT                                               |

| Number of I/O              | 24                                                     |

| Program Memory Size        | 8KB (8K x 8)                                           |

| Program Memory Type        | OTP                                                    |

| EEPROM Size                | ·                                                      |

| RAM Size                   | 237 x 8                                                |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                            |

| Data Converters            | ·                                                      |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                        |

| Mounting Type              | Surface Mount                                          |

| Package / Case             | 28-LCC (J-Lead)                                        |

| Supplier Device Package    | -                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8673312vsg |

|                            |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# zilog<sup>°</sup> <sub>iv</sub>

# **Table of Contents**

| Architectural Overview 1   Features 1 |

|---------------------------------------|

| Functional Block Diagram 3            |

| Pin Description                       |

| Electrical Characteristics            |

| Absolute Maximum Ratings              |

| Standard Test Conditions              |

| Capacitance                           |

| DC Electrical Characteristics         |

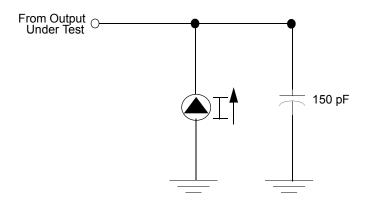

| Handshake Timing Diagrams             |

| Pin Functions                         |

| EPROM Programming Mode 37             |

| Application Precaution                |

| Standard Mode                         |

| Functional Description 46             |

| Package Information                   |

| Ordering Information                  |

| Customer Support                      |

zilog

# **Architectural Overview**

Zilog's Z86E33/733/E34, E43/743/E44 8-Bit One-Time Programmable (OTP) Microcontrollers are members of Zilog's single-chip Z8<sup>®</sup> MCU family featuring enhanced wake-up circuitry, programmable Watchdog Timers, Low Noise EMI options, and easy hardware/ software system expansion capability.

Four basic address spaces support a wide range of memory configurations. The designer has access to three additional control registers that allow easy access to register mapped peripheral and I/O circuits.

For applications demanding powerful I/O capabilities, the Z86E33/733/E34 have 24 pins, and the Z86E43/743/E44 have 32 pins of dedicated input and output. These lines are grouped into four ports, eight lines per port, and are configurable under software control to provide timing, status signals, and parallel I/O with or without handshake, and address/ data bus for interfacing external memory.

**Note:** All signals with an overline are active Low. For example,  $B/\overline{W}$ , for which WORD is active Low, and  $\overline{B}/W$ , for which BYTE is active Low.

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>CC</sub> | V <sub>DD</sub> |

| Ground     | GND             | V <sub>SS</sub> |

Power connections follow these conventional descriptions:

### **Features**

Table 1 lists the features of Z86E33/733/E34, E43/743/E44.

| Device | ROM<br>(KB) | RAM <sup>1</sup><br>(Bytes) | I/O<br>Lines | Speed<br>(MHz) |

|--------|-------------|-----------------------------|--------------|----------------|

| Z86E33 | 4           | 237                         | 24           | 12             |

| Z86733 | 8           | 237                         | 24           | 12             |

| Z86E34 | 16          | 237                         | 24           | 12             |

| Z86E43 | 4           | 236                         | 32           | 12             |

| Z86743 | 8           | 236                         | 32           | 12             |

## CMOS Z8<sup>®</sup> OTP Microcontrollers Product Specification Zilog <sub>3</sub>

On-Chip Oscillator that Accepts a Crystal, Ceramic Resonator, LC, RC, or External Clock Drive

## **Functional Block Diagram**

•

(E43/743/E44 Only) Output Input XTAL AS DS R/W RESET  $V_{CC}$ GND Machine Port 3 Timing & Inst. ĴĹ Control RESET Counter/ WDT, POR ALU TimerS (2) OTP FLAGS Interrupt Control Register Pointer Two Analog Program Comparators Counter **Register File** 7 Port 1 Port 2 Port 0 I/O Address or I/O Address/Data or I/O (Bit Programmable) (Nibble Programmable) (Byte Programmable) ((E43/743/E44 Only)

Figure 1 displays the functional block diagram.

Figure 1. Functional Block Diagram

## **Pin Description**

Din No Symbol Eunction Direction

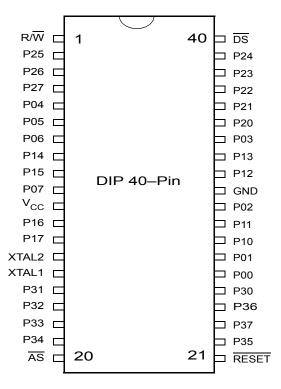

Table 2. 40-Pin DIP Pin Identification Standard Mode

| 1 $R/\overline{W}$ Read/WriteOutput2-4P25-P27Port 2, Pins 5,6,7Input/Output5-7P04-P06Port 0, Pins 4,5,6Input/Output8-9P14-P15Port 1, Pins 4,5Input/Output10P07Port 0, Pin 7Input/Output11 $V_{CC}$ Power Supply12-13P16-P17Port 1, Pins 6,7Input/Output14XTAL2Crystal OscillatorOutput | PIN NO | Symbol          | Function           | Direction    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------|--------------------|--------------|

| 5-7   P04-P06   Port 0, Pins 4,5,6   Input/Output     8-9   P14-P15   Port 1, Pins 4,5   Input/Output     10   P07   Port 0, Pin 7   Input/Output     11   V <sub>CC</sub> Power Supply   Port 1, Pins 6,7   Input/Output                                                              | 1      | R/W             | Read/Write         | Output       |

| 8-9   P14-P15   Port 1, Pins 4,5   Input/Output     10   P07   Port 0, Pin 7   Input/Output     11   V <sub>CC</sub> Power Supply   12-13     P16-P17   Port 1, Pins 6,7   Input/Output                                                                                                | 2-4    | P25-P27         | Port 2, Pins 5,6,7 | Input/Output |

| 10   P07   Port 0, Pin 7   Input/Output     11   V <sub>CC</sub> Power Supply   12-13   P16-P17   Port 1, Pins 6,7   Input/Output                                                                                                                                                      | 5-7    | P04-P06         | Port 0, Pins 4,5,6 | Input/Output |

| 11V <sub>CC</sub> Power Supply12-13P16-P17Port 1, Pins 6,7Input/Output                                                                                                                                                                                                                 | 8-9    | P14-P15         | Port 1, Pins 4,5   | Input/Output |

| 12-13   P16-P17   Port 1, Pins 6,7   Input/Output                                                                                                                                                                                                                                      | 10     | P07             | Port 0, Pin 7      | Input/Output |

|                                                                                                                                                                                                                                                                                        | 11     | V <sub>CC</sub> | Power Supply       |              |

| 14   XTAL2   Crystal Oscillator   Output                                                                                                                                                                                                                                               | 12-13  | P16-P17         | Port 1, Pins 6,7   | Input/Output |

|                                                                                                                                                                                                                                                                                        | 14     | XTAL2           | Crystal Oscillator | Output       |

# zilog <sub>6</sub>

| Pin No | Symbol  | Function                | Direction    |

|--------|---------|-------------------------|--------------|

| 15     | XTAL1   | Crystal Oscillator      | Input        |

| 16-18  | P31-P33 | Port 3, Pins 1,2,3      | Input        |

| 19     | P34     | Port 3, Pin 4           | Output       |

| 20     | AS      | Address Strobe          | Output       |

| 21     | RESET   | Reset                   | Input        |

| 22     | P35     | Port 3, Pin 5           | Output       |

| 23     | P37     | Port 3, Pin 7           | Output       |

| 24     | P36     | Port 3, Pin 6           | Output       |

| 25     | P30     | Port 3, Pin 0           | Input        |

| 26-27  | P00-P01 | Port 0, Pins 0,1        | Input/Output |

| 28-29  | P10-P11 | Port 1, Pins 0,1        | Input/Output |

| 30     | P02     | Port 0, Pin 2           | Input/Output |

| 31     | GND     | Ground                  |              |

| 32-33  | P12-P13 | Port 1, Pins 2,3        | Input/Output |

| 34     | P03     | Port 0, Pin 3           | Input/Output |

| 35-39  | P20-P24 | Port 2, Pins 0, 1,2,3,4 | Input/Output |

| 40     | DS      | Data Strobe             | Output       |

#### Table 2. 40-Pin DIP Pin Identification Standard Mode (Continued)

21

Total power dissipation should not exceed 1.21 W for the package. Power dissipation is calculated as follows:

$\begin{array}{ll} \mbox{Total Power Dissipation} = & V_{DD} \; x \; [I_{DD} - (\mbox{sum of } I_{OH}), \\ & + \; \mbox{sum of } [(V_{DD} - V_{OH}) \; x \; I_{OH}] \\ & + \; \mbox{sum of } (V_{OL} \; x \; I_{OL}) \end{array}$

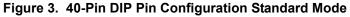

## **Standard Test Conditions**

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to GND. Positive current flows into the referenced pin (Test Load).

Figure 13. Test Load Diagram

### Capacitance

$T_A = 25$  °C,  $V_{CC} = GND = 0$  V, f = 1.0 MHz, unmeasured pins returned to GND.

| Parameter          | Min | Max   |

|--------------------|-----|-------|

| Input capacitance  | 0   | 12 pF |

| Output capacitance | 0   | 12 pF |

| I/O capacitance    | 0   | 12 pF |

Zilog<sup>®</sup> <sub>30</sub>

| TdDS(A)<br>TdDS(AS) | DSRise to Address ActiveDelayDSRise to ASFall Delay                   | 4.5V<br>5.5V<br>4.5V                                                                                                                                                                                                                                                                                                 | 45<br>55                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TdDS(AS)            |                                                                       |                                                                                                                                                                                                                                                                                                                      | 55                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TdDS(AS)            | $\overline{\text{DS}}$ Rise to $\overline{\text{AS}}$ Fall Delay      | 4 E\/                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                     |                                                                       | 4.5V                                                                                                                                                                                                                                                                                                                 | 45                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                     |                                                                       | 5.5V                                                                                                                                                                                                                                                                                                                 | 45                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TdR/W(AS)           | $R/\overline{W}$ Valid to $\overline{AS}$ Rise Delay                  | 4.5V                                                                                                                                                                                                                                                                                                                 | 45                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                     |                                                                       | 5.5V                                                                                                                                                                                                                                                                                                                 | 45                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TdDS(R/W)           | DS Rise to R/W Not Valid                                              | 4.5V                                                                                                                                                                                                                                                                                                                 | 45                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                     |                                                                       | 5.5V                                                                                                                                                                                                                                                                                                                 | 45                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TdDW(DSW)           |                                                                       |                                                                                                                                                                                                                                                                                                                      | 55                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                     | Delay                                                                 | 5.5V                                                                                                                                                                                                                                                                                                                 | 55                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TdDS(DW)            | DS Rise to Write Data Not Valid                                       | 4.5V                                                                                                                                                                                                                                                                                                                 | 55                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                     | Delay                                                                 | 5.5V                                                                                                                                                                                                                                                                                                                 | 55                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TdA(DR)             | Address Valid to Read Data Req'd                                      | 4.5V                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                        | 310                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2,3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     | Valid                                                                 |                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                     | 2,3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TdAS(DS)            | AS Rise to DS Fall Delay                                              | 4.5V                                                                                                                                                                                                                                                                                                                 | 65                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                     |                                                                       | 5.5V                                                                                                                                                                                                                                                                                                                 | 65                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TdDM(AS)            | DM Valid to AS Rise Delay                                             | 4.5V                                                                                                                                                                                                                                                                                                                 | 35                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                     |                                                                       | 5.5V                                                                                                                                                                                                                                                                                                                 | 35                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ThDS(AS)            | DS Valid to Address Valid Hold Time                                   | 4.5V                                                                                                                                                                                                                                                                                                                 | 35                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                     |                                                                       | 5.5V                                                                                                                                                                                                                                                                                                                 | 35                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| -                   | TdDS(R/W)<br>TdDW(DSW)<br>TdDS(DW)<br>TdA(DR)<br>TdAS(DS)<br>TdDM(AS) | TdDS(R/W) DS Rise to R/W Not Valid   TdDW(DSW) Write Data Valid to DS Fall (Write) Delay   TdDS(DW) DS Rise to Write Data Not Valid Delay   TdDS(DW) DS Rise to Write Data Not Valid Delay   TdA(DR) Address Valid to Read Data Req'd Valid   TdAS(DS) AS Rise to DS Fall Delay   TdDM(AS) DM Valid to AS Rise Delay | 5.5VTdDS(R/W)DS Rise to R/W Not Valid4.5VTdDW(DSW)Write Data Valid to DS Fall (Write)<br>Delay4.5VTdDS(DW)DS Rise to Write Data Not Valid<br>Delay4.5VTdDS(DW)DS Rise to Write Data Not Valid<br>Delay4.5VTdA(DR)Address Valid to Read Data Req'd<br>Valid4.5VTdAS(DS)AS Rise to DS Fall Delay4.5VTdDM(AS)DM Valid to AS Rise Delay4.5VThDS(AS)DS Valid to Address Valid Hold Time4.5V | $\overline{IdDS(R/W)}$ $\overline{DS}$ Rise to R/W Not Valid $\overline{4.5V}$ $45$ $\overline{IdDS(R/W)}$ $\overline{DS}$ Rise to R/W Not Valid $4.5V$ $45$ $\overline{IdDW(DSW)}$ Write Data Valid to $\overline{DS}$ Fall (Write)<br>Delay $4.5V$ $55$ $\overline{IdDS(DW)}$ $\overline{DS}$ Rise to Write Data Not Valid<br>Delay $4.5V$ $55$ $\overline{IdDS(DW)}$ $\overline{DS}$ Rise to Write Data Not Valid<br>Delay $4.5V$ $55$ $\overline{IdA(DR)}$ $\overline{Address}$ Valid to Read Data Req'd<br>Valid $4.5V$ $55$ $\overline{IdAS(DS)}$ $\overline{AS}$ Rise to $\overline{DS}$ Fall Delay $4.5V$ $65$ $\overline{IdDM(AS)}$ $\overline{DM}$ Valid to $\overline{AS}$ Rise Delay $4.5V$ $35$ $\overline{InDS(AS)}$ $\overline{DS}$ Valid to Address Valid Hold Time $4.5V$ $35$ | $\overline{\text{TdDS}(\text{R/W})}$ $\overline{\text{DS}}$ Rise to R/W Not Valid $\overline{4.5V}$ $45$ $\overline{\text{TdDW}(\text{DSW})}$ Write Data Valid to $\overline{\text{DS}}$ Fall (Write)<br>Delay $4.5V$ $55$ $\overline{\text{TdDS}(\text{DW})}$ $\overline{\text{DS}}$ Rise to Write Data Not Valid<br>Delay $4.5V$ $55$ $\overline{\text{TdDS}(\text{DW})}$ $\overline{\text{DS}}$ Rise to Write Data Not Valid<br>Delay $4.5V$ $55$ $\overline{\text{TdDS}(\text{DW})}$ $\overline{\text{DS}}$ Rise to Write Data Not Valid<br> | TdDS(R/W)DS Rise to R/W Not Valid $5.5V$ $45$ nsTdDS(R/W)DS Rise to R/W Not Valid $4.5V$ $45$ ns $5.5V$ $45$ nsTdDW(DSW)Write Data Valid to DS Fall (Write)<br>Delay $4.5V$ $55$ nsTdDS(DW)DS Rise to Write Data Not Valid<br>Delay $4.5V$ $55$ nsTdDS(DW)DS Rise to Write Data Not Valid<br>Delay $4.5V$ $55$ nsTdA(DR)Address Valid to Read Data Req'd<br>Valid $4.5V$ $310$ nsTdAS(DS)AS Rise to DS Fall Delay $4.5V$ $65$ nsTdDM(AS)DM Valid to AS Rise Delay $4.5V$ $35$ nsThDS(AS)DS Valid to Address Valid Hold Time<br>4.5V $4.5V$ $35$ ns |

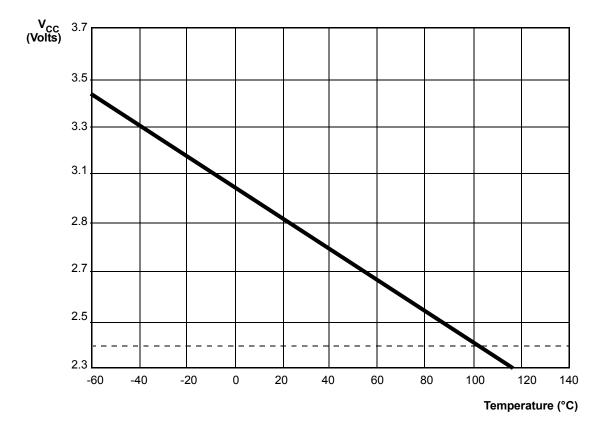

### Table 14. DC Electrical Characteristics $T_A = -40$ °C to +105 °C, 12 MHz (Continued)

#### Notes

1. The V<sub>CC</sub> voltage specification of 5.5 V guarantees 5.0 V  $\pm$  0.5 V and the V<sub>CC</sub> voltage specification of 3.5 V guarantees only 3.5 V.

2. Timing numbers given are for minimum TpC.

3. When using extended memory timing, add 2 TpC.

Standard Test Load

All timing references use 0.7  $\rm V_{CC}$  for a logic 1 and 0.2  $\rm V_{CC}$  for a logic 0.

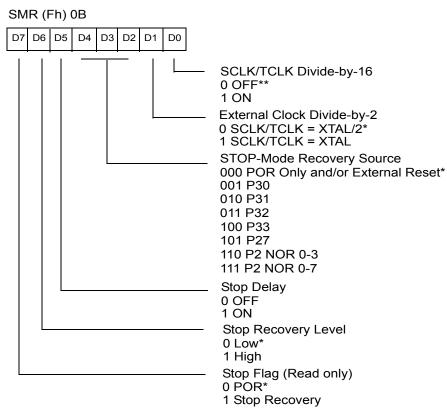

For Standard Mode (not Low-EMI Mode for outputs) with SMR, D1 = 0, D0 = 0.

# Zilog <sub>33</sub>

| No | Symbol  | Parameter                          | V <sub>cc</sub> <sup>1</sup> | Min  | Мах  | Min  | Max  | Units | Notes   |       |

|----|---------|------------------------------------|------------------------------|------|------|------|------|-------|---------|-------|

| 2  | TrC,TfC | Clock Input Rise & Fall            | 4.5V                         |      | 25   |      | 25   | ns    | 2,3,4   |       |

|    |         | Times                              | 5.5V                         |      | 25   |      | 25   | ns    | 2,3,4   |       |

| 3  | TwC     | Input Clock Width                  | 4.5V                         | 100  |      | 100  |      | ns    | 2,3,4   |       |

|    |         |                                    | 5.5V                         | 100  |      | 100  |      | ns    | 2,3,4   |       |

| 4  | TwTinL  | Timer Input Low Width              | 4.5V                         | 100  |      | 100  |      | ns    | 2,3,4   |       |

|    |         |                                    | 5.5V                         | 70   |      | 70   |      | ns    | 2,3,4   |       |

| 5  | TwTinH  | Timer Input High Width             | 4.5V                         | 5TpC |      | 5TpC |      |       | 2,3,4   |       |

|    |         |                                    |                              | 5.5V | 5TpC |      | 5TpC |       |         | 2,3,4 |

| 6  | TpTin   | Timer Input Period                 | 4.5V                         | 8TpC |      | 8TpC |      |       | 2,3,4   |       |

|    |         |                                    | 5.5V                         | 8TpC |      | 8TpC |      |       | 2,3,4   |       |

| 7  | TrTin,  | , Timer Input Rise & Fall<br>Timer | 4.5V                         |      | 100  |      | 100  | ns    | 2,3,4   |       |

|    | TfTin   |                                    | 5.5V                         |      | 100  |      | 100  | ns    | 2,3,4   |       |

| 8A | TwIL    | Int. Request Low Time              | 4.5V                         | 100  |      | 100  |      | ns    | 2,3,4,5 |       |

|    |         |                                    | 5.5V                         | 70   |      | 70   |      | ns    | 2,3,4,5 |       |

| 8B | TwIL    | Int. Request Low Time              | 4.5V                         | 5TpC |      | 5TpC |      |       | 2,3,4,6 |       |

|    |         |                                    | 5.5V                         | 5TpC |      | 5TpC |      |       | 2,3,4,6 |       |

| 9  | TwlH    | Int. Request Input High            | 4.5V                         | 5TpC |      | 5TpC |      |       | 2,3,4,5 |       |

|    |         | Time                               | 5.5V                         | 5TpC |      | 5TpC |      |       | 2,3,4,5 |       |

| 10 | Twsm    | Stop Mode Recovery                 | 4.5V                         | 12   |      | 12   |      | ns    | 4,7     |       |

|    |         | Width Spec                         | 5.5V                         | 12   |      | 12   |      | ns    | 4,7     |       |

| 11 | Tost    | Oscillator Startup Time            | 4.5V                         |      | 5TpC |      | 5TpC |       | 4,7,8   |       |

|    |         |                                    | 5.5V                         |      | 5TpC |      | 5TpC |       | 4,7,8   |       |

#### Table 16. Additional Timing Table (Divide-By-One Mode) T<sub>A</sub> = -40 °C to +105 °C (Continued)

#### Notes

1. The V<sub>CC</sub> voltage specification of 5.5 V guarantees 5.0 V  $\pm$  0.5 V and the V<sub>CC</sub> voltage specification of 3.5 V guarantees only 3.5 V.

2. Timing Reference uses 0.7  $V_{CC}$  for a logic 1 and 0.2  $V_{CC};$  for a logic 0.

3. SMR D1 = 0.

4. Maximum frequency for internal system clock is 4 MHz when using Low EMI OSC PCON Bit D7=0.

- 5. Interrupt request via Port 3 (P31-P33).

- 6. Interrupt request via Port 3 (P30).

- 7. SMR-D5 = 1, POR STOP Mode Delay is on.

8. For RC and LC oscillator, and for oscillator driven by clock driver.

# Zilog <sub>35</sub>

| No | Symbol | Parameter                           | V <sub>CC</sub> <sup>1</sup> | Min  | Max  | Min  | Max  | Units | Conditions | Notes   |

|----|--------|-------------------------------------|------------------------------|------|------|------|------|-------|------------|---------|

| 4  | TwTinL | Timer input Low                     | 3.5V                         | 70   |      | 70   |      | ns    |            | 2,6,4   |

|    |        | Width                               | 5.5V                         | 70   |      | 70   |      | ns    |            | 2,6,4   |

| 5  | TwTinH | Timer Input High                    | 3.5V                         | 5TpC |      | 5TpC |      |       |            | 2,6,4   |

|    |        | Width                               | 5.5V                         | 5TpC |      | 5TpC |      |       |            | 2,6,4   |

| 6  | TpTin  | Timer Input Period                  | 3.5V                         | 8TpC |      | 8TpC |      |       |            | 2,6,4   |

|    |        |                                     | 5.5V                         | 8TpC |      | 8TpC |      |       |            | 2,6,4   |

| 7  | TrTin, | Timer Input Rise &                  | 3.5V                         |      | 100  |      | 100  | ns    |            | 2,6,4   |

|    | TfTin  | Fall Timer                          | 5.5V                         |      | 100  |      | 100  | ns    |            | 2,6,4   |

| 8A | TwIL   | Int. Request Low                    | 3.5V                         | 70   |      | 70   |      | ns    |            | 2,6,4,5 |

|    |        | Time                                | 5.5V                         | 70   |      | 70   |      | ns    |            | 2,6,4,5 |

| 8B | TwIL   | Int. Request Low<br>Time            | 3.5V                         | 5TpC |      | 5TpC |      |       |            | 2,6,4,5 |