Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                        |

|----------------------------|--------------------------------------------------------|

| Product Status             | Obsolete                                               |

| Core Processor             | Z8                                                     |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 12MHz                                                  |

| Connectivity               | EBI/EMI                                                |

| Peripherals                | POR, WDT                                               |

| Number of I/O              | 24                                                     |

| Program Memory Size        | 16KB (16K x 8)                                         |

| Program Memory Type        | OTP                                                    |

| EEPROM Size                | -                                                      |

| RAM Size                   | 237 x 8                                                |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                            |

| Data Converters            | -                                                      |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                        |

| Mounting Type              | Surface Mount                                          |

| Package / Case             | 28-LCC (J-Lead)                                        |

| Supplier Device Package    | -                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86e3412vsc |

|                            |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

zilog

## **Architectural Overview**

Zilog's Z86E33/733/E34, E43/743/E44 8-Bit One-Time Programmable (OTP) Microcontrollers are members of Zilog's single-chip Z8<sup>®</sup> MCU family featuring enhanced wake-up circuitry, programmable Watchdog Timers, Low Noise EMI options, and easy hardware/ software system expansion capability.

Four basic address spaces support a wide range of memory configurations. The designer has access to three additional control registers that allow easy access to register mapped peripheral and I/O circuits.

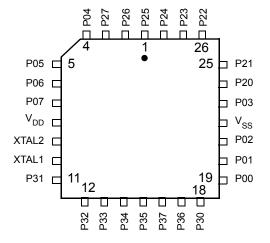

For applications demanding powerful I/O capabilities, the Z86E33/733/E34 have 24 pins, and the Z86E43/743/E44 have 32 pins of dedicated input and output. These lines are grouped into four ports, eight lines per port, and are configurable under software control to provide timing, status signals, and parallel I/O with or without handshake, and address/ data bus for interfacing external memory.

**Note:** All signals with an overline are active Low. For example,  $B/\overline{W}$ , for which WORD is active Low, and  $\overline{B}/W$ , for which BYTE is active Low.

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>CC</sub> | V <sub>DD</sub> |

| Ground     | GND             | V <sub>SS</sub> |

Power connections follow these conventional descriptions:

## **Features**

Table 1 lists the features of Z86E33/733/E34, E43/743/E44.

| Device | ROM<br>(KB) | RAM <sup>1</sup><br>(Bytes) | I/O<br>Lines | Speed<br>(MHz) |

|--------|-------------|-----------------------------|--------------|----------------|

| Z86E33 | 4           | 237                         | 24           | 12             |

| Z86733 | 8           | 237                         | 24           | 12             |

| Z86E34 | 16          | 237                         | 24           | 12             |

| Z86E43 | 4           | 236                         | 32           | 12             |

| Z86743 | 8           | 236                         | 32           | 12             |

# zilog 4

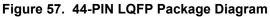

Figure 2. EPROM Programming Block Diagram

## Zilog<sup>®</sup>,

| Pin No | in No Symbol Function |                        | Direction    |

|--------|-----------------------|------------------------|--------------|

| 1-2    | GND                   | Ground                 |              |

| 3-4    | P12-P13               | Port 1, Pins 2,3       | Input/Output |

| 5      | P03                   | Port 0, Pin 3          | Input/Output |

| 6-10   | P20-P24               | Port 2, Pins 0,1,2,3,4 | Input/Output |

| 11     | DS                    | Data Strobe            | Output       |

| 12     | NC                    | No Connection          |              |

| 13     | R/W                   | Read/Write             | Output       |

| 14-16  | P25-P27               | Port 2, Pins 5,6,7     | Input/Output |

| 17-19  | P04-P06               | Port 0, Pins 4,5,6     | Input/Output |

| 20-21  | P14-P15               | Port 1, Pins 4,5       | Input/Output |

| 22     | P07                   | Port 0, Pin 7          | Input/Output |

| 23-24  | V <sub>CC</sub>       | Power Supply           |              |

| 25-26  | P16-P17               | Port 1, Pins 6,7       | Input/Output |

|        |                       |                        |              |

zilog |<sub>9</sub>

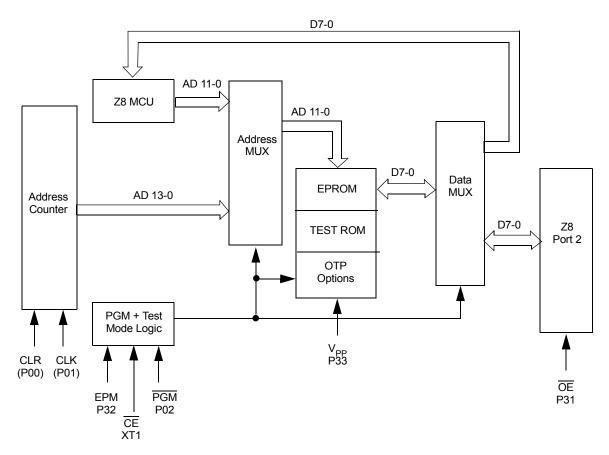

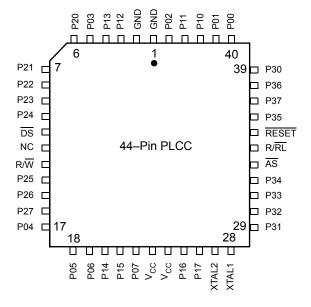

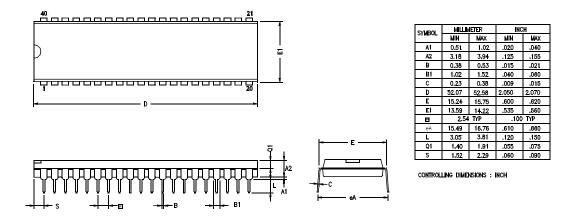

Figure 5. 44-Pin LQFP Pin Configuration Standard Mode

Table 4. 44-Pin LQFP Pin Identification

| Pin No | Symbol          | Function           | Direction    |

|--------|-----------------|--------------------|--------------|

| 1-2    | P05-P06         | Port 0, Pins 5,6   | Input/Output |

| 3-4    | P14-P15         | Port 1, Pins 4,5   | Input/Output |

| 5      | P07             | Port 0, Pin 7      | Input/Output |

| 6-7    | V <sub>CC</sub> | Power Supply       |              |

| 8-9    | P16-P17         | Port 1, Pins 6,7   | Input/Output |

| 10     | XTAL2           | Crystal Oscillator | Output       |

| 11     | XTAL1           | Crystal Oscillator | Input        |

| 12-14  | P31-P33         | Port 3, Pins 1,2,3 | Input        |

| 15     | P34             | Port 3, Pin 4      | Output       |

| 16     | AS              | Address Strobe     | Output       |

| 17     | R//RL           | ROM/ROMless select | Input        |

|        |                 |                    |              |

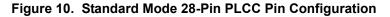

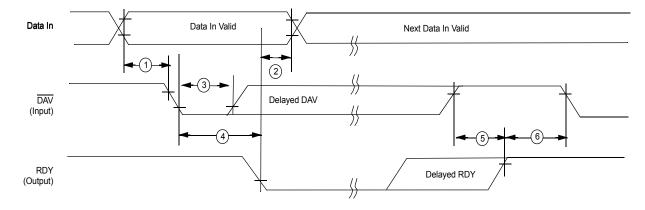

Figure 11. EPROM Programming Mode 28-Pin DIP/SOIC Pin Configuration

## Zilog<sup>1</sup><sub>26</sub>

| Symbo<br>I       | Parameter                    | V <sub>cc</sub> <sup>1</sup> | Min  | Мах | Typical<br>@ 25°C | Units | Conditions             | Notes |

|------------------|------------------------------|------------------------------|------|-----|-------------------|-------|------------------------|-------|

| I <sub>CC2</sub> | Standby Current<br>STOP Mode | 4.5V                         |      | 10  | 2                 | μA    | $V_{IN} = 0V, V_{CC}$  | 7,8,9 |

|                  |                              | 5.5V                         |      | 10  | 3                 | μA    | $V_{IN} = 0V, V_{CC}$  | 7,8,9 |

|                  |                              | 4.5V                         |      | 40  | 10                | μA    | $V_{IN} = 0V, V_{CC}$  | 7,8   |

|                  |                              | 5.5V                         |      | 40  | 10                | μA    | $V_{IN} = 0V, V_{CC}$  | 7,8   |

| I <sub>ALL</sub> | Auto Latch Low<br>Current    | 4.5V                         | 1.4  | 20  | 4.7               | μA    | $0V < V_{IN} < V_{CC}$ | 10    |

|                  |                              | 5.5V                         | 1.4  | 20  | 4.7               | μA    | $0V < V_{IN} < V_{CC}$ | 10    |

| I <sub>ALH</sub> | Auto Latch High<br>Current   | 4.5V                         | -1.0 | -10 | -3.8              | μA    | $0V < V_{IN} < V_{CC}$ | 10    |

|                  |                              | 5.5V                         | -1.0 | -10 | -3.8              | μA    | $0V < V_{IN} < V_{CC}$ | 10    |

| T <sub>POR</sub> | Power-On Reset               | 4.5V                         | 1.0  | 14  | 4                 | ms    |                        |       |

|                  |                              | 5.5V                         | 1.0  | 14  | 4                 | ms    |                        |       |

| V <sub>LV</sub>  | Auto Reset Voltage           | 9                            | 2.0  | 3.3 | 2.8               | V     |                        | 11    |

## Table 12. DC Electrical Characteristics T<sub>A</sub>= -40 °C to +105 °C (Continued)

#### Notes

1. The V<sub>CC</sub> voltage specification of 5.5 V guarantees 5.0 V  $\pm$  0.5 V and the V<sub>CC</sub> voltage specification of 3.5 V guarantees only 3.5 V.

2. STD Mode (not Low EMI Mode).

3. Z86E43/743/E44 only.

4. For analog comparator inputs when analog comparators are enabled.

5. All outputs unloaded, I/O pins floating, inputs at rail.

- 6. CL1=CL2=22 pF.

- Same as note 5 except inputs at V<sub>CC</sub>.

Clock must be forced Low, when XTAL1 is clock driven and XTAL2.

- 9. WDT is not running.

- 10. Auto Latch (mask option) selected.

- 11. Device does function down to the Auto Reset voltage.

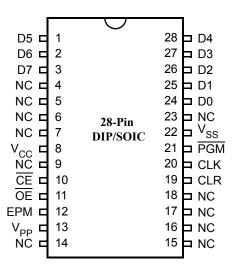

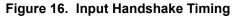

## Handshake Timing Diagrams

Figure 17. Output Handshake Timing

| Table 17. Additional Timing Table (Divide by Two Mode) $T_A$ | = 0 °C to +70 °C |

|--------------------------------------------------------------|------------------|

|--------------------------------------------------------------|------------------|

| No | Symbol  | Parameter          | V <sub>CC</sub> <sup>1</sup> | Min  | Max | Min | Max | Units Conditions | Notes |

|----|---------|--------------------|------------------------------|------|-----|-----|-----|------------------|-------|

| 1  | ТрС     | Input Clock Period | 3.5V                         | 62.5 | DC  | 250 | DC  | ns               | 2,6,4 |

|    |         |                    | 5.5V                         | 62.5 | DC  | 250 | DC  | ns               | 2,6,4 |

| 2  | TrC,TfC | Clock Input Rise & | 3.5V                         |      | 15  |     | 25  | ns               | 2,6,4 |

|    |         | Fall Times         | 5.5V                         |      | 15  |     | 25  | ns               | 2,6,4 |

| 3  | TwC     | Input Clock Width  | 3.5V                         | 31   |     | 31  |     | ns               | 2,6,4 |

|    |         |                    | 5.5V                         | 31   |     | 31  |     | ns               | 2,6,4 |

zilog

CLR Clear (active High). This pin resets the internal address counter at the High Level.

**CLK** Address Clock. This pin is a clock input. The internal address counter increases by one for each clock cycle.

## **Application Precaution**

The production test-mode environment may be enabled accidentally during normal operation if excessive noise surges above  $V_{CC}$  occur on pins P31 and RESET.

In addition, processor operation of Z8 OTP devices may be affected by excessive noise surges on the  $V_{PP}$  EPM,  $\overline{OE}$  pins while the microcontroller is in Standard Mode.

Recommendations for dampening voltage surges in both test and OTP mode include the following:

- Using a clamping diode to V<sub>CC</sub>

- Adding a capacitor to the affected pin

- Enable EPROM/Test Mode Disable OTP option bit.

### Standard Mode

**XTAL** Crystal 1 (time-based input). This pin connects a parallel-resonant crystal, ceramic resonator, LC, RC network, or external single-phase clock to the on-chip oscillator input.

**XTAL2** Crystal 2 (time-based output). This pin connects a parallel-resonant crystal, ceramic resonator, LC, or RC network to the on-chip oscillator output.

$\mathbf{R}/\overline{\mathbf{W}}$  Read/Write (output, write Low). The  $\mathbf{R}/\overline{\mathbf{W}}$  signal is Low when the CCP is writing to the external program or data memory (Z86E43/743/E44 only).

**RESET** Reset (input, active Low). Reset will initialize the MCU. Reset is accomplished either through Power-On, Watchdog Timer reset, Stop Mode Recovery, or external reset. During Power-On Reset and Watchdog Timer Reset, the internally generated reset drives the reset pin low for the POR time. Any devices driving the reset line must be open-drain in order to avoid damage from a possible conflict during reset conditions. Pull-up is provided internally. After the POR time, RESET is a Schmitt-triggered input. (RESET is available on Z86E43/743/E44 only.)

To avoid asynchronous and noisy reset problems, the Z86E43/743/E44 is equipped with a reset filter of four external clocks (4TpC). If the external reset signal is less than 4TpC in duration, no reset occurs. On the fifth clock after the reset is detected, an internal RST signal is latched and held for an internal register count of 18 external clocks, or for the duration of the external reset, whichever is longer. During the reset cycle,  $\overline{\text{DS}}$  is held active Low while  $\overline{\text{AS}}$  cycles at a rate of TpC/2. Program execution begins at location 000CH, 5-10 TpC cycles after  $\overline{\text{RESET}}$  is released. For Power-On Reset, the reset output time is 5 ms.

Zilog 46

## **Functional Description**

>

>

The MCU incorporates the following special functions to enhance the standard Z8 architecture to provide the user with increased design flexibility.

**RESET**. The device is reset in one of three ways:

- 1. Power-On Reset

- 2. Watchdog Timer

- 3. Stop Mode Recovery Source

- **Note:** Having the Auto Power-On Reset circuitry built-in, the MCU does not need to be connected to an external power-on reset circuit. The reset time is  $T_{POR}$ . The MCU does not re-initialize WDTMR, SMR, P2M, and P3M registers to their reset values on a Stop Mode Recovery operation.

- **Note:** The device  $V_{CC}$  must rise up to the operating  $V_{CC}$  specification before the  $T_{POR}$  expires.

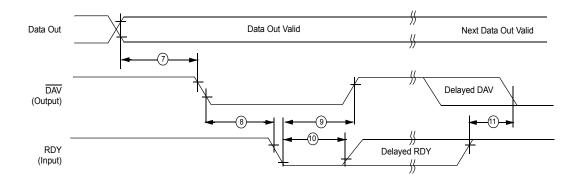

**Program Memory**. The MCU can address up to 4/8/16 KB of Internal Program Memory (see Figure 22). The first 12 bytes of program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors that correspond to the six available interrupts. For EPROM mode, byte 12 (000Ch) to address 4095 (0FFFh)/8191 (1FFFh)/16384 (3FFFh), consists of programmable EPROM. After reset, the program counter points at the address 000Ch, which is the starting address of the user program.

In ROMless mode, the Z86E43/743/E44 can address up to 64 KB of External Program Memory. The ROM/ROMless option is only available on the 44-pin devices.

Zilog 48

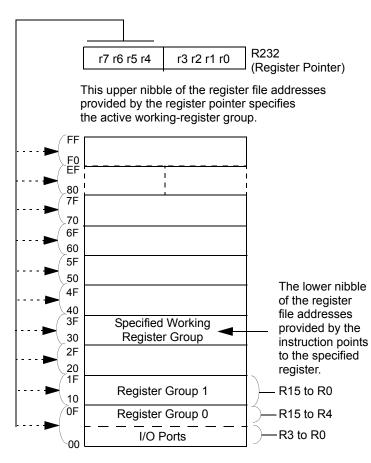

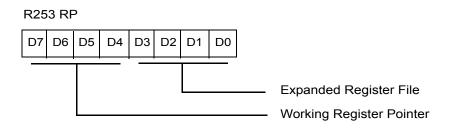

**Register File**. The register file consists of three I/O port registers, 236/125 general-purpose registers, 15 control and status registers, and three system configuration registers in the expanded register group. The instructions can access registers directly or indirectly through an 8-bit address field. This allows a short 4-bit register address using the Register Pointer (see Figure 24). In the 4-bit mode, the register file is divided into 16 working register groups, each occupying 16 continuous locations. The Register Pointer addresses the starting location of the active working-register group.

**Note:** *Register Group E0-EF can only be accessed through working register and indirect addressing modes.*

## zilog <sub>50</sub>

\* Expanded Register Group (0) is selected in this figure by handling bits D3 to D0 as "0" in Register R253 (RP).

Figure 25. Register Pointer

zilog

RAM Protect. The upper portion of the RAM's address spaces 80h to EFh (excluding the control registers) can be protected from reading and writing. This option can be selected during the EPROM Programming Mode. After this option is selected, the user can activate this feature from the internal EPROM. D6 of the IMR control register (R251) is used to turn off/on the RAM protect by loading a 0 or 1, respectively. A "1" in D6 indicates RAM Protect enabled.

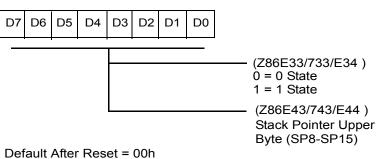

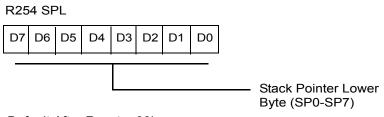

**Stack**. The Z86E43/743/E44 external data memory or the internal register file can be used for the stack. The 16-bit Stack Pointer (R254-R255) is used for the external stack, which can reside anywhere in the data memory for ROMless mode, but only from 4096/8192/16384 to 65535 in ROM mode. An 8-bit Stack Pointer (R255) is used for the internal stack on the Z8 that resides within the 236 general-purpose registers (R4-R239). SPH (R254) can be used as a general-purpose register when using internal stack only. R254 and R255 are set to 00H after any reset or Stop Mode Recovery.

**Counter/Timers**. There are two 8-bit programmable counter/timers (T0 and T1), each driven by its own 6-bit programmable prescaler. The Ti prescaler is driven by internal or external clock sources; however, the TO prescaler is driven by the internal clock only (see Figure 27).

The 6-bit prescalers can divide the input frequency of the clock source by any integer number from 1 to 64. Each prescaler drives its counter, which decrements the value (1 to 256), that has been loaded into the counter. When the counter reaches the end of count, a timer interrupt request, IRQ4 (T0) or IRQ5 (T1), is generated.

The counters can be programmed to start, stop, restart to continue, or restart from the initial value. The counters can also be programmed to stop upon reaching one (single pass mode) or to automatically reload the initial value and continue counting (modulo-n continuous mode).

The counters, but not the prescalers, can be read at any time without disturbing their value or count mode. The clock source for T1 is user-definable and can be either the internal microprocessor clock divided by four, or an external signal input through Port 3. The Timer Mode register configures the external timer input (P31) as an external clock, a trigger input that can be retriggerable or non-retriggerable, or as a gate input for the internal clock. Port 3 line P36 serves as a timer output ( $T_{OUT}$ ) through which T0, T1, or the internal clock can be output. The counter/timers can be cascaded by connecting the T0 output to the input of T1.

## zilog

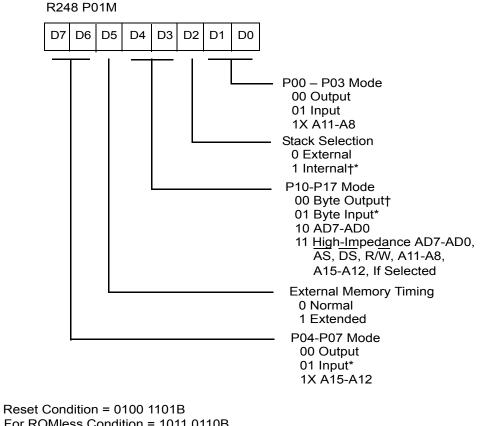

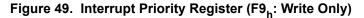

When more than one interrupt is pending, priorities are resolved by a programmable priority encoder that is controlled by the Interrupt Priority Register (IPR). An interrupt machine cycle is activated when an interrupt request is granted. Thus, disabling all subsequent interrupts, saves the Program Counter and Status Flags, and then branches to the program memory vector location reserved for that interrupt. All interrupts are vectored through locations in the program memory. This memory location and the next byte contain the 16bit starting address of the interrupt service routine for that particular interrupt request.

To accommodate polled interrupt systems, interrupt inputs are masked and the interrupt request register is polled to determine which of the interrupt requests need service.

An interrupt resulting from AN1 is mapped into IRQ2, and an interrupt from AN2 is mapped into IRQ0. Interrupts IRQ2 and IRQ0 may be rising, falling or both edge triggered, and are programmable by the user. The software may poll to identify the state of the pin.

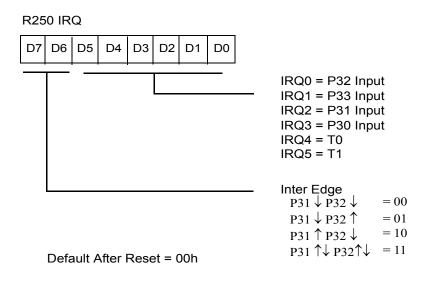

Programming bits for the Interrupt Edge Select are located in bits D7 and D6 of the IRQ Register (R250). The configuration is shown in Table 21.

|    | IRO                             | Inte | Interrupt Edge |  |  |

|----|---------------------------------|------|----------------|--|--|

| D7 | D6                              | P31  | P32            |  |  |

| 0  | 0                               | F    | F              |  |  |

| 0  | 1                               | F    | R              |  |  |

| 1  | 0                               | R    | F              |  |  |

| 1  | 1                               | R/F  | R/F            |  |  |

|    | = Falling Edge<br>= Rising Edge |      |                |  |  |

### Table 21. IRQ Register Configuration

**Clock**. The on-chip oscillator has a high-gain, parallel-resonant amplifier for connection to a crystal, RC, ceramic resonator, or any suitable external clock source (XTAL1 = Input, XTAL2 = Output). The crystal should be AT cut, 10 kHz to 16 MHz max, with a series resistance (RS) less than or equal to  $100 \Omega$ .

The crystal should be connected across XTAL1 and XTAL2 using the vendor's recommended capacitor values from each pin directly to device pin Ground. The RC oscillator option can be selected in the programming mode. The RC oscillator configuration must be an external resistor connected from XTAL1 to XTAL2, with a frequency-setting capacitor from XTAL1 to Ground (Table 29).

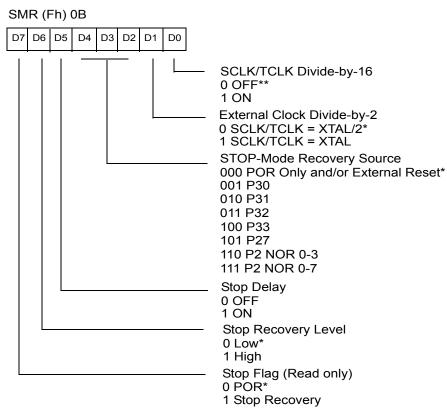

\* Default setting after RESET

\*\* Default setting after RESET and STOP-Mode Recovery

### Figure 31. Stop Mode Recovery Register (Write-Only Except Bit D7, Which Is Read-Only)

**SCLK/TCLK Divide-by-16 Select (D0)**. This bit of the SMR controls a divide-by-16 prescaler of SCLK/TCLK. The purpose of this control is to selectively reduce device power consumption during normal processor execution (SCLK control) and/or HALT mode (where TCLK sources counter/timers and interrupt logic).

**External Clock Divide-by-Two (D1)**. This bit can eliminate the oscillator divide-by-two circuitry. When this bit is 0, the System Clock (SCLK) and Timer Clock (TCLK) are equal to the external clock frequency divided by two. The SCLK/TCLK is equal to the external clock frequency when this bit is set (D1=1). Using this bit together with D7 of PCON further helps lower EMI (that is, D7 (PCON) = 0, D1 (SMR) = 1). The default setting is zero.

**Stop Mode Recovery Source (D2, D3, and D4)**. These three bits of the SMR register specify the wake up source of the Stop Mode Recovery (Figure 32). Table 22 shows the SMR source selected with the setting of D2 to D4. P33-P31 cannot be used to wake up

## Zilog <sub>67</sub>

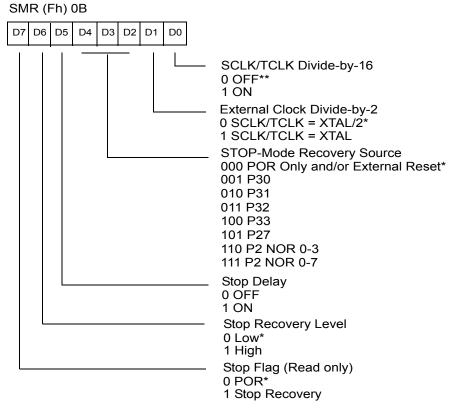

Note: Note used in conjunction with SMR2 Source

\* Default setting after RESET

\*\* Default setting after RESET and STOP-Mode Recovery

Figure 37. Stop Mode Recovery Register (Write Only Except Bit D7, Which is Read Only)

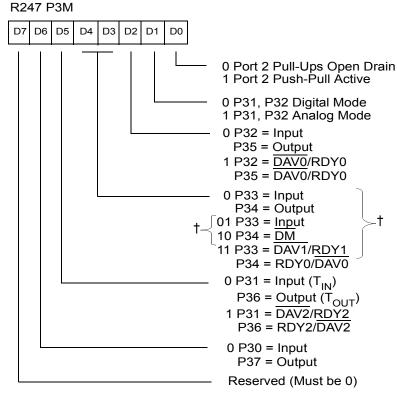

Default After Reset = 00h † Z86E33/733/E34 Must be 00

Zilog <sub>73</sub>

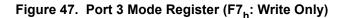

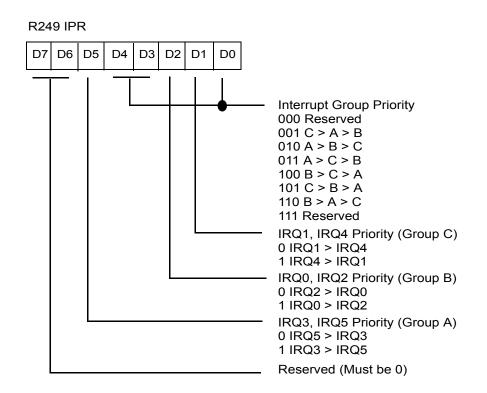

Reset Condition = 0100 1101B For ROMless Condition = 1011 0110B † Z86E33/733/E34 Must be 00 \* Default after Reset

Figure 48. Port 0 and 1 Mode Register (F8<sub>h</sub>: Write Only)

Zilog<sup>®</sup> <sub>74</sub>

Figure 50. Interrupt Request Register (FA<sub>h</sub>: Read/Write)

Default After Reset = 00h

### Figure 53. Register Pointer (FD<sub>h</sub>: Read/Write)

Default After Reset = 00h

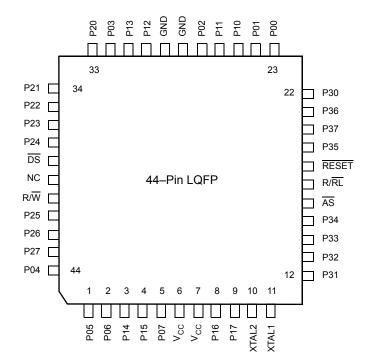

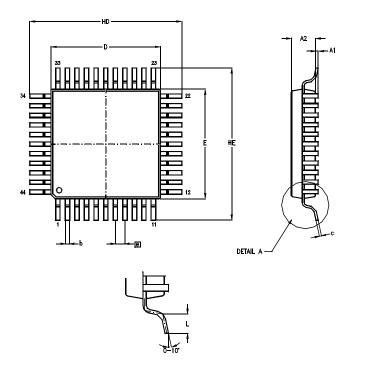

## **Package Information**

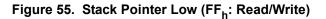

Figure 56. 40-PIN DIP Package Diagram

| SYMBOL | MILLIN   | <b>/ETER</b> | IN    | СН   |

|--------|----------|--------------|-------|------|

| STMDOL | MIN      | MAX          | MIN   | MAX  |

| A1     | 0.05     | 0,25         | ,002  | .010 |

| A2     | 2.00     | 2.25         | .078  | .089 |

| b      | 0.25     | 0.45         | .010  | .018 |

| с      | 0.13     | 0.20         | .005  | .008 |

| HD     | 13.70    | 14.15        | .539  | .557 |

| D      | 9.90     | 10.10        | .390  | .398 |

| HE     | 13.70    | 14.15        | .539  | .557 |

| E      | 9.90     | 10.10        | .390  | .398 |

| e      | 0.80 BSC |              | .0315 | BSC  |

| L      | 0.60     | 1.20         | .024  | .047 |

NOTES: 1. CONTROLLING DIMENSIONS : WILLIMETER 2. LEAD COPLANARITY : MAX <u>.10</u> .004"