Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                        |

|----------------------------|--------------------------------------------------------|

| Product Status             | Obsolete                                               |

| Core Processor             | 28                                                     |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 12MHz                                                  |

| Connectivity               | EBI/EMI                                                |

| Peripherals                | POR, WDT                                               |

| Number of I/O              | 32                                                     |

| Program Memory Size        | 4KB (4K x 8)                                           |

| Program Memory Type        | OTP                                                    |

| EEPROM Size                | ·                                                      |

| RAM Size                   | 236 x 8                                                |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                            |

| Data Converters            | -                                                      |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                        |

| Mounting Type              | Surface Mount                                          |

| Package / Case             | 44-LCC (J-Lead)                                        |

| Supplier Device Package    | -                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86e4312vsc |

|                            |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# zilog <sub>6</sub>

| Pin No | Symbol  | Function                | Direction    |

|--------|---------|-------------------------|--------------|

| 15     | XTAL1   | Crystal Oscillator      | Input        |

| 16-18  | P31-P33 | Port 3, Pins 1,2,3      | Input        |

| 19     | P34     | Port 3, Pin 4           | Output       |

| 20     | AS      | Address Strobe          | Output       |

| 21     | RESET   | Reset                   | Input        |

| 22     | P35     | Port 3, Pin 5           | Output       |

| 23     | P37     | Port 3, Pin 7           | Output       |

| 24     | P36     | Port 3, Pin 6           | Output       |

| 25     | P30     | Port 3, Pin 0           | Input        |

| 26-27  | P00-P01 | Port 0, Pins 0,1        | Input/Output |

| 28-29  | P10-P11 | Port 1, Pins 0,1        | Input/Output |

| 30     | P02     | Port 0, Pin 2           | Input/Output |

| 31     | GND     | Ground                  |              |

| 32-33  | P12-P13 | Port 1, Pins 2,3        | Input/Output |

| 34     | P03     | Port 0, Pin 3           | Input/Output |

| 35-39  | P20-P24 | Port 2, Pins 0, 1,2,3,4 | Input/Output |

| 40     | DS      | Data Strobe             | Output       |

### Table 2. 40-Pin DIP Pin Identification Standard Mode (Continued)

# Zilog<sup>®</sup>,

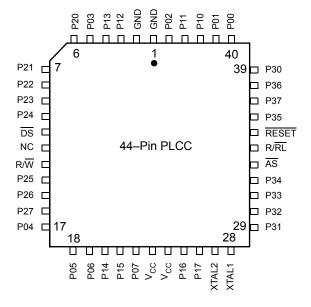

| Pin No | Symbol          | Function               | Direction    |

|--------|-----------------|------------------------|--------------|

| 1-2    | GND             | Ground                 |              |

| 3-4    | P12-P13         | Port 1, Pins 2,3       | Input/Output |

| 5      | P03             | Port 0, Pin 3          | Input/Output |

| 6-10   | P20-P24         | Port 2, Pins 0,1,2,3,4 | Input/Output |

| 11     | DS              | Data Strobe            | Output       |

| 12     | NC              | No Connection          |              |

| 13     | R/W             | Read/Write             | Output       |

| 14-16  | P25-P27         | Port 2, Pins 5,6,7     | Input/Output |

| 17-19  | P04-P06         | Port 0, Pins 4,5,6     | Input/Output |

| 20-21  | P14-P15         | Port 1, Pins 4,5       | Input/Output |

| 22     | P07             | Port 0, Pin 7          | Input/Output |

| 23-24  | V <sub>CC</sub> | Power Supply           |              |

| 25-26  | P16-P17         | Port 1, Pins 6,7       | Input/Output |

|        |                 |                        |              |

# Zilog <sub>14</sub>

#### Table 6. 44-Pin PLCC Pin Configuration EPROM Programming Mode (Continued)

| Pin No Symbol Function |      | Function      | Direction |

|------------------------|------|---------------|-----------|

| 32-39                  | NC   | No Connection |           |

| 40                     | CLR  | Clear         | Input     |

| 41                     | CLK  | Clock         | Input     |

| 42-43                  | NC   | No Connection |           |

| 44                     | /PGM | Prog. Mode    | Input     |

|                        |      |               |           |

21

Total power dissipation should not exceed 1.21 W for the package. Power dissipation is calculated as follows:

$\begin{array}{ll} \mbox{Total Power Dissipation} = & V_{DD} \; x \; [I_{DD} - (\mbox{sum of } I_{OH}), \\ & + \; \mbox{sum of } [(V_{DD} - V_{OH}) \; x \; I_{OH}] \\ & + \; \mbox{sum of } (V_{OL} \; x \; I_{OL}) \end{array}$

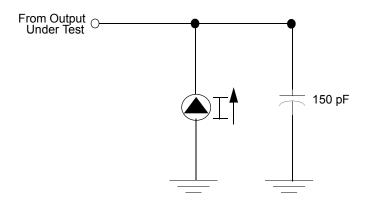

## **Standard Test Conditions**

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to GND. Positive current flows into the referenced pin (Test Load).

Figure 13. Test Load Diagram

## Capacitance

$T_A = 25$  °C,  $V_{CC} = GND = 0$  V, f = 1.0 MHz, unmeasured pins returned to GND.

| Parameter          | Min | Max   |

|--------------------|-----|-------|

| Input capacitance  | 0   | 12 pF |

| Output capacitance | 0   | 12 pF |

| I/O capacitance    | 0   | 12 pF |

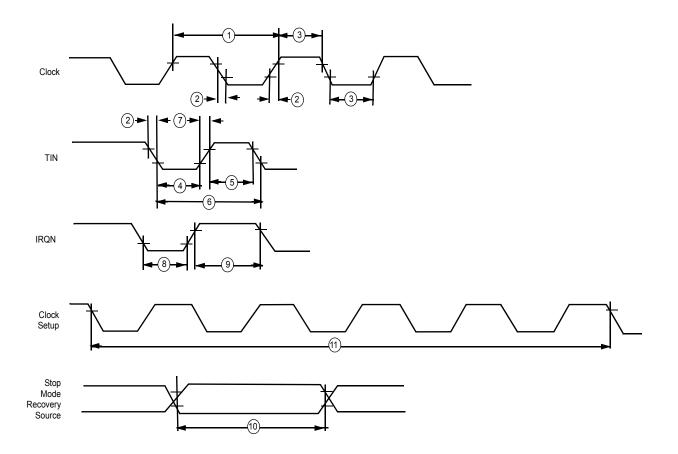

Figure 15. Additional Timing Diagram

Table 15. Additional Timing Table (Divide-By-One Mode)  $T_A = 0$  °C to +70 °C

| No        | Symbol  | Parameter                        | V <sub>cc</sub> <sup>1</sup> | Min | Мах | Min | Мах | Units | Notes |

|-----------|---------|----------------------------------|------------------------------|-----|-----|-----|-----|-------|-------|

| 1         | ТрС     | Input Clock Period               | 3.5V                         | 250 | DC  | 166 | DC  | ns    | 2,3,4 |

|           |         |                                  | 5.5V                         | 250 | DC  | 166 | DC  | ns    | 2,3,4 |

| 2 TrC,TfC | TrC,TfC | Clock Input Rise & Fall<br>Times | 3.5V                         |     | 25  |     | 25  | ns    | 2,3,4 |

|           |         |                                  | 5.5V                         |     | 25  |     | 25  | ns    | 2,3,4 |

| 3         | TwC     | Input Clock Width                | 3.5V                         | 100 |     | 100 |     | ns    | 2,3,4 |

|           |         |                                  | 5.5V                         | 100 |     | 100 |     | ns    | 2,3,4 |

| 4 TwTinL  |         | Timer Input Low Width            | 3.5V                         | 100 |     | 100 |     | ns    | 2,3,4 |

|           |         |                                  | 5.5V                         | 70  |     | 70  |     | ns    | 2,3,4 |

# Zilog <sub>33</sub>

| No | Symbol  | Parameter                        | V <sub>cc</sub> <sup>1</sup> | Min  | Мах  | Min  | Max  | Units | Notes   |

|----|---------|----------------------------------|------------------------------|------|------|------|------|-------|---------|

| 2  | TrC,TfC | Clock Input Rise & Fall          | 4.5V                         |      | 25   |      | 25   | ns    | 2,3,4   |

|    |         | Times                            | 5.5V                         |      | 25   |      | 25   | ns    | 2,3,4   |

| 3  | TwC     | Input Clock Width                | 4.5V                         | 100  |      | 100  |      | ns    | 2,3,4   |

|    |         |                                  | 5.5V                         | 100  |      | 100  |      | ns    | 2,3,4   |

| 4  | TwTinL  | Timer Input Low Width            | 4.5V                         | 100  |      | 100  |      | ns    | 2,3,4   |

|    |         |                                  | 5.5V                         | 70   |      | 70   |      | ns    | 2,3,4   |

| 5  | TwTinH  | Timer Input High Width           | 4.5V                         | 5TpC |      | 5TpC |      |       | 2,3,4   |

|    |         |                                  | 5.5V                         | 5TpC |      | 5TpC |      |       | 2,3,4   |

| 6  | TpTin   | Timer Input Period               | 4.5V                         | 8TpC |      | 8TpC |      |       | 2,3,4   |

|    |         |                                  | 5.5V                         | 8TpC |      | 8TpC |      |       | 2,3,4   |

| 7  | TrTin,  | Timer Input Rise & Fall<br>Timer | 4.5V                         |      | 100  |      | 100  | ns    | 2,3,4   |

|    | TfTin   |                                  | 5.5V                         |      | 100  |      | 100  | ns    | 2,3,4   |

| 8A | TwIL    | Int. Request Low Time            | 4.5V                         | 100  |      | 100  |      | ns    | 2,3,4,5 |

|    |         |                                  | 5.5V                         | 70   |      | 70   |      | ns    | 2,3,4,5 |

| 8B | TwIL    | Int. Request Low Time            | 4.5V                         | 5TpC |      | 5TpC |      |       | 2,3,4,6 |

|    |         |                                  | 5.5V                         | 5TpC |      | 5TpC |      |       | 2,3,4,6 |

| 9  | TwlH    | Int. Request Input High          | 4.5V                         | 5TpC |      | 5TpC |      |       | 2,3,4,5 |

|    |         | Time                             | 5.5V                         | 5TpC |      | 5TpC |      |       | 2,3,4,5 |

| 10 | Twsm    | Stop Mode Recovery               | 4.5V                         | 12   |      | 12   |      | ns    | 4,7     |

|    |         | Width Spec                       | 5.5V                         | 12   |      | 12   |      | ns    | 4,7     |

| 11 | Tost    | Oscillator Startup Time          | 4.5V                         |      | 5TpC |      | 5TpC |       | 4,7,8   |

|    |         |                                  | 5.5V                         |      | 5TpC |      | 5TpC |       | 4,7,8   |

#### Table 16. Additional Timing Table (Divide-By-One Mode) T<sub>A</sub> = -40 °C to +105 °C (Continued)

#### Notes

1. The V<sub>CC</sub> voltage specification of 5.5 V guarantees 5.0 V  $\pm$  0.5 V and the V<sub>CC</sub> voltage specification of 3.5 V guarantees only 3.5 V.

2. Timing Reference uses 0.7  $V_{CC}$  for a logic 1 and 0.2  $V_{CC};$  for a logic 0.

3. SMR D1 = 0.

4. Maximum frequency for internal system clock is 4 MHz when using Low EMI OSC PCON Bit D7=0.

- 5. Interrupt request via Port 3 (P31-P33).

- 6. Interrupt request via Port 3 (P30).

- 7. SMR-D5 = 1, POR STOP Mode Delay is on.

8. For RC and LC oscillator, and for oscillator driven by clock driver.

# Zilog <sub>35</sub>

| No | Symbol | Parameter              | V <sub>CC</sub> <sup>1</sup> | Min  | Max  | Min  | Max  | Units | Conditions | Notes   |

|----|--------|------------------------|------------------------------|------|------|------|------|-------|------------|---------|

| 4  | TwTinL | Timer input Low        | 3.5V                         | 70   |      | 70   |      | ns    |            | 2,6,4   |

|    |        | Width                  | 5.5V                         | 70   |      | 70   |      | ns    |            | 2,6,4   |

| 5  | TwTinH | Timer Input High       | 3.5V                         | 5TpC |      | 5TpC |      |       |            | 2,6,4   |

|    |        | Width                  | 5.5V                         | 5TpC |      | 5TpC |      |       |            | 2,6,4   |

| 6  | TpTin  | Timer Input Period     | 3.5V                         | 8TpC |      | 8TpC |      |       |            | 2,6,4   |

|    |        |                        | 5.5V                         | 8TpC |      | 8TpC |      |       |            | 2,6,4   |

| 7  | TrTin, | Timer Input Rise &     | 3.5V                         |      | 100  |      | 100  | ns    |            | 2,6,4   |

|    | TfTin  | Fall Timer             | 5.5V                         |      | 100  |      | 100  | ns    |            | 2,6,4   |

| 8A | TwIL   | Int. Request Low       | 3.5V                         | 70   |      | 70   |      | ns    |            | 2,6,4,5 |

|    |        | Time                   | 5.5V                         | 70   |      | 70   |      | ns    |            | 2,6,4,5 |

| 8B | TwIL   | Int. Request Low       | 3.5V                         | 5TpC |      | 5TpC |      |       |            | 2,6,4,5 |

|    |        | Time                   | 5.5V                         | 5TpC |      | 5TpC |      |       |            | 2,6,4,5 |

| 9  | TwlH   | Int. Request Input     | 3.5V                         | 5TpC |      | 5TpC |      |       |            | 2,6,4,5 |

|    |        | High Time              | 5.5V                         | 5TpC |      | 5TpC |      |       |            | 2,6,4,5 |

| 10 | Twsm   | Stop Mode              | 3.5V                         | 12   |      | 12   |      | ns    |            | 6,7     |

|    |        | Recovery Width<br>Spec | 5.5V                         | 12   |      | 12   |      | ns    |            | 6,7     |

| 11 | Tost   | Oscillator Startup     | 3.5V                         |      | 5TpC |      | 5TpC |       |            | 6,7     |

|    |        | Time                   | 5.5V                         |      | 5TpC |      | 5TpC |       |            | 6,7     |

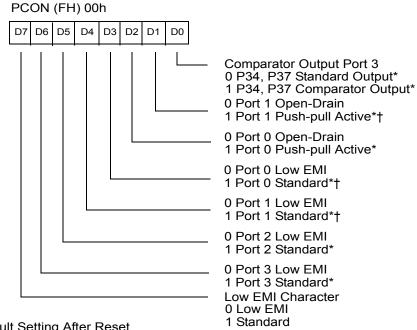

| 12 | Twdt   | Watchdog Timer         | 3.5V                         | 7    |      | 10   |      | ms    | D0 =0      | 8,9     |

|    |        | Delay Time Before      | 5.5V                         | 3.5  |      | 5    |      | ms    | D1 = 0     | 5,11    |

|    |        | Timeout                | 3.5V                         | 14   |      | 20   |      | ms    | D0 =1      | 5,11    |

|    |        |                        | 5.5V                         | 7    |      | 10   |      | ms    | D1 = 0     | 5,11    |

|    |        |                        | 3.5V                         | 28   |      | 40   |      | ms    | D1 = 0     | 5,11    |

|    |        |                        | 5.5V                         | 14   |      | 20   |      | ms    | D1 = 1     | 5,11    |

|    |        |                        | 3.5V                         | 112  |      | 160  |      | ms    | D0 = 1     | 5,11    |

|    |        |                        | 5.5V                         | 56   |      | 80   |      | ms    | D1 = 1     | 5,11    |

|    |        |                        |                              |      |      |      |      |       |            |         |

Table 17. Additional Timing Table (Divide by Two Mode)  $T_A = 0 \degree C$  to +70  $\degree C$  (Continued)

Notes

1. The V<sub>CC</sub> voltage specification of 5.5 V guarantees 5.0 V  $\pm$  0.5 V and the V<sub>CC</sub> voltage specification of 3.5 V guarantees only 3.5 V.

2. Timing Reference uses 0.7 VC0 for a logic 1 and 0.2 VGC for a logic 0.

3. SMR D1 = 0.

4. SMR-D5 = 1, POR STOP Mode Delay is on

- 5. Interrupt request via Port 3 (P31-P33)

- 6. Interrupt request via Port 3 (P30).

7. Maximum frequency for internal system clock is 2 MHz when using Low EMI OSC PCON Bit D7 = 0

8. Reg. WDTMR.

9. Using internal RC.

zilog<sup>®</sup>

Port 1 can be placed in the high-impedance state along with Port 0,  $\overline{AS}$ ,  $\overline{DS}$ , and  $R/\overline{W}$ , allowing the Z86E43/743/E44 to share common resources in multiprocessor and DMA applications. In ROM mode, Port 1 is defined as input after reset.

Figure 19. Port 1 Configuration (Z86E43/743/E44 Only)

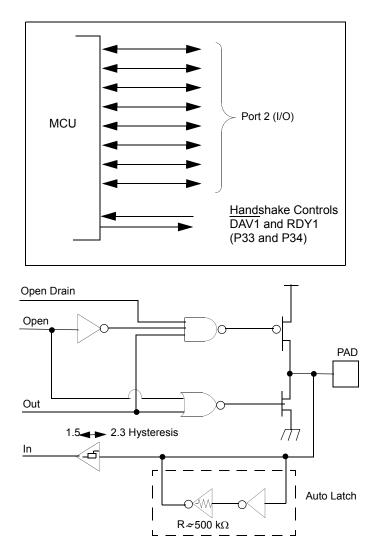

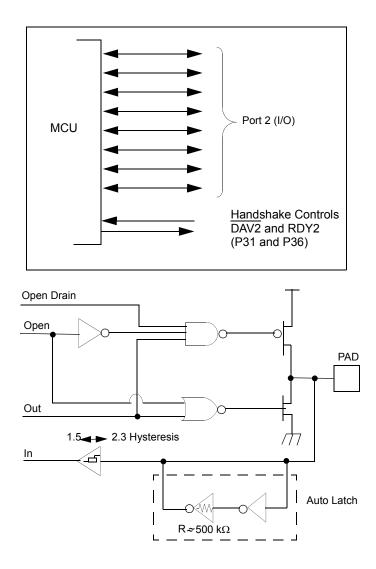

**Port 2 (P27-P20)**. Port 2 is an 8-bit, bidirectional, CMOS-compatible I/O port. These eight I/O lines can be configured under software control as an input or output, independently. All input buffers are Schmitt-triggered. Bits programmed as outputs can be globally programmed as either push-pull or open-drain. Low EMI output buffers can be globally programmed by the software. When used as an I/O port, Port 2 can be placed under handshake control. After reset, Port 2 is defined as an input.

Zilog 42

In Handshake Mode, Port 3 lines P31 and P36 are used as handshake control lines. The handshake direction is determined by the configuration (input or output) assigned to bit 7 of Port 2 (see Figure 20).

Figure 20. Port 2 Configuration

**Port 3 (P37-P30)**. Port 3 is an 8-bit, CMOS-compatible port with four fixed inputs (P33-P30) and four fixed outputs (P37-P34). These eight lines can be configured by software for interrupt and handshake control functions. Port 3, Pin 0 is Schmitt- triggered. P31, P32, and P33 are standard CMOS inputs with single trip point (no Auto Latches) and P34, P35, P36, and P37 are push-pull output lines. Low EMI output buffers can be globally programmed by the software. Two on-board comparators can process analog signals on P31

**z**ilog<sup>°</sup>

| Pin | I/O | CTC1             | Analog  | Interrup | t P0 HS | P1 HS | P2 HS | Ext |

|-----|-----|------------------|---------|----------|---------|-------|-------|-----|

| P30 | IN  |                  |         | IRQ3     |         |       |       |     |

| P31 | IN  | T <sub>IN</sub>  | AN1     | IRQ2     |         | D/R   |       |     |

| P32 | IN  |                  | AN2     | IRQ0     | D/R     |       |       |     |

| P33 | IN  |                  | REF     | IRQ1     |         | D/R   |       |     |

| P34 | OUT |                  | AN1-Out |          |         | R/D   |       | DM  |

| P35 | OUT |                  |         |          | R/D     |       |       |     |

| P36 | OUT | T <sub>OUT</sub> |         |          |         | R/D   |       |     |

| P37 | OUT |                  | An2-Out |          |         |       |       |     |

| -   |     |                  |         |          |         |       |       |     |

#### Table 19. Port 3 Pin Assignments

**Comparator Inputs**. Port 3, P31, and P32, each have a comparator front end. The comparator reference voltage P33 is common to both comparators. In analog mode, P31 and P32 are the positive input of the comparators and P33 is the reference voltage of the comparators.

**Auto Latch**. The Auto Latch puts valid CMOS levels on all CMOS inputs (except P33-P31) that are not externally driven. Whether this level is 0 or 1, cannot be determined. A valid CMOS level, rather than a floating node, reduces excessive supply current flow in the input buffer. Auto Latches are available on Port 0, Port 1, Port 2, and P30. There are no Auto Latches on P31, P32, and P33.

**Low EMI Emission**. The Z86E43/743/E44 can be programmed to operate in a low EMI Emission Mode in the PCON register. The oscillator and all I/O ports can be programmed as low EMI emission mode independently. Use of this feature results in:

- The pre-drivers slew rate reduced to 10 ns typical.

- Low EMI output drivers have resistance of 200 Ohms (typical).

- Low EMI Oscillator.

- Internal SCLK/TCLK= XTAL operation limited to a maximum of 4 MHz 250 ns cycle time, when Low EMI Oscillator is selected.

Note: For emulation only: Do not set the emulator to emulate Port 1 in low EMI mode. Port 1 must always be configured in Standard Mode.

Default after RESET = 00h

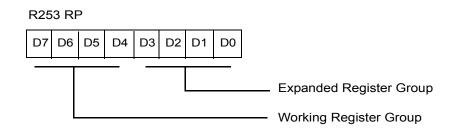

#### Figure 24. Register Pointer Register

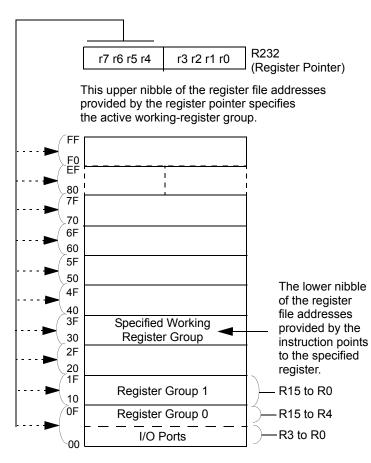

**Expanded Register File** (ERF). The register file has been expanded to allow for additional system control registers, mapping of additional peripheral devices and input/output ports into the register address area. The Z8 register address space RO through R15 is implemented as 16 groups of 16 registers per group (see Figure 26). These register banks are known as the Expanded Register File (ERF).

The low nibble (D3-D0) of the Register Pointer (RP) select the active ERF Bank, and the high nibble (D7-D4) of register RP select the working register group. Three system configuration registers reside in the Expanded Register File at bank FH: PCON, SMR, and WDTMR. The rest of the Expanded Register is not physically implemented and is reserved for future expansion.

# zilog <sub>50</sub>

\* Expanded Register Group (0) is selected in this figure by handling bits D3 to D0 as "0" in Register R253 (RP).

Figure 25. Register Pointer

## zilog

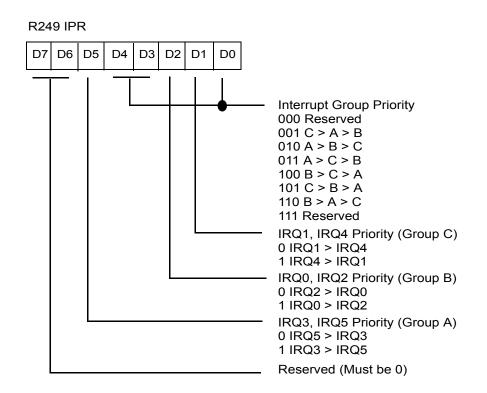

When more than one interrupt is pending, priorities are resolved by a programmable priority encoder that is controlled by the Interrupt Priority Register (IPR). An interrupt machine cycle is activated when an interrupt request is granted. Thus, disabling all subsequent interrupts, saves the Program Counter and Status Flags, and then branches to the program memory vector location reserved for that interrupt. All interrupts are vectored through locations in the program memory. This memory location and the next byte contain the 16bit starting address of the interrupt service routine for that particular interrupt request.

To accommodate polled interrupt systems, interrupt inputs are masked and the interrupt request register is polled to determine which of the interrupt requests need service.

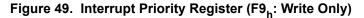

An interrupt resulting from AN1 is mapped into IRQ2, and an interrupt from AN2 is mapped into IRQ0. Interrupts IRQ2 and IRQ0 may be rising, falling or both edge triggered, and are programmable by the user. The software may poll to identify the state of the pin.

Programming bits for the Interrupt Edge Select are located in bits D7 and D6 of the IRQ Register (R250). The configuration is shown in Table 21.

|    | IRO                             | Inte | Interrupt Edge |  |  |  |

|----|---------------------------------|------|----------------|--|--|--|

| D7 | D6                              | P31  | P32            |  |  |  |

| 0  | 0                               | F    | F              |  |  |  |

| 0  | 1                               | F    | R              |  |  |  |

| 1  | 0                               | R    | F              |  |  |  |

| 1  | 1                               | R/F  | R/F            |  |  |  |

|    | = Falling Edge<br>= Rising Edge |      |                |  |  |  |

#### Table 21. IRQ Register Configuration

**Clock**. The on-chip oscillator has a high-gain, parallel-resonant amplifier for connection to a crystal, RC, ceramic resonator, or any suitable external clock source (XTAL1 = Input, XTAL2 = Output). The crystal should be AT cut, 10 kHz to 16 MHz max, with a series resistance (RS) less than or equal to  $100 \Omega$ .

The crystal should be connected across XTAL1 and XTAL2 using the vendor's recommended capacitor values from each pin directly to device pin Ground. The RC oscillator option can be selected in the programming mode. The RC oscillator configuration must be an external resistor connected from XTAL1 to XTAL2, with a frequency-setting capacitor from XTAL1 to Ground (Table 29).

zilog

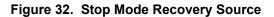

**Comparator Output Port 3** (D0). Bit 0 controls the comparator output in Port 3. A "1" in this location brings the comparator outputs to P34 and P37, and a "0" releases the Port to its standard I/O configuration. The default value is 0.

**Port 1 Open-Drain** (D1). Port 1 can be configured as an open-drain by resetting this bit (D1=0) or configured as push-pull active by setting this bit (D1=1). The default value is 1.

**Port 0 Open-Drain** (D2). Port 0 can be configured as an open-drain by resetting this bit (D2=0) or configured as push-pull active by setting this bit (D2=1). The default value is 1.

**Low EMI Port 0** (D3). Port 0 can be configured as a Low EMI Port by resetting this bit (D3=0) or configured as a Standard Port by setting this bit (D3=1). The default value is 1.

**Low EMI Port 1** (D4). Port 1 can be configured as a Low EMI Port by resetting this bit (D4=0) or configured as a Standard Port by setting this bit (D4=1). The default value is 1.

**Note:** The emulator does not support Port 1 low EMI mode and must be set D4 = 1.

**Low EMI Port 2** (D5). Port 2 can be configured as a Low EMI Port by resetting this bit (D5=0) or configured as a Standard Port by setting this bit (D5=1). The default value is 1.

**Low EMI Port 3** (D6). Port 3 can be configured as a Low EMI Port by resetting this bit (D6=0) or configured as a Standard Port by setting this bit (D6=1). The default value is 1.

**Low EMI OSC** (D7). This bit of the PCON Register controls the low EMI noise oscillator. A "1" in this location configures the oscillator with standard drive. While a "0" configures the oscillator with low noise drive, however, it does not affect the relationship of SCLK and XTAL. The low EMI mode will reduce the drive of the oscillator (OSC). The default value is 1.

**Note:** 4 *MHz* is the maximum external clock frequency when running in the low EMI oscillator mode.

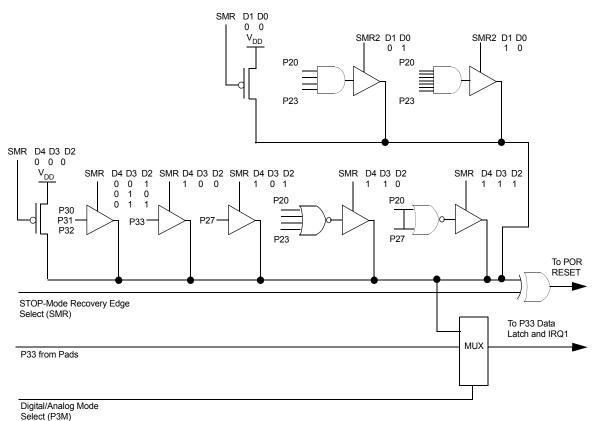

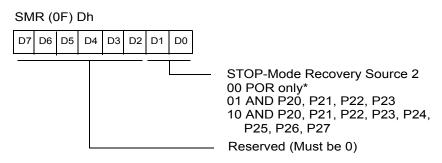

**Stop-Mode Recovery Register** (SMR). This register selects the clock divide value and determines the mode of Stop Mode Recovery (Figure 31). All bits are Write Only except bit 7 which is a Read Only. Bit 7 is a flag bit that is hardware set on the condition of STOP Recovery and reset by a power-on cycle. Bit 6 controls whether a low or high level is required from the recovery source. Bit 5 controls the reset delay after recovery. Bits 2, 3, and 4 of the SMR register specify the Stop Mode Recovery Source. The SMR is located in Bank F of the Expanded Register File at address 0BH.

>

>

zilog <sub>60</sub>

from STOP mode when programmed as analog inputs. When the Stop Mode Recovery sources are selected in this register then SMR2 register bits D0, D1 must be set to zero.

**Note:** *If the Port 2 pin is configured as an output, this output level will be read by the SMR circuitry.*

## **Z8 Control Register Diagrams**

## **Ordering Information**

\* Default Setting After Reset † Must be set to "1" for Z86E33/733/E34

Figure 36. Port Configuration Register (PCON) (Write Only)

\* Default setting after RESET

#### Figure 38. Watchdog Timer Mode Register (Write Only)

Note: Not used in conjunction with SMR Source

#### Figure 39. Stop Mode Recovery Register2 (Write Only)

Zilog<sup>®</sup> <sub>74</sub>

Figure 50. Interrupt Request Register (FA<sub>h</sub>: Read/Write)

## **Package Information**

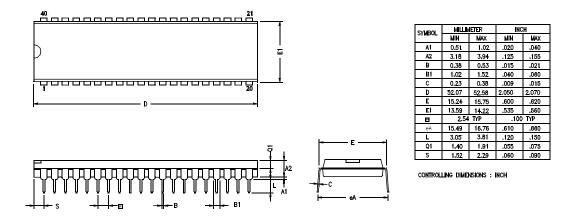

Figure 56. 40-PIN DIP Package Diagram

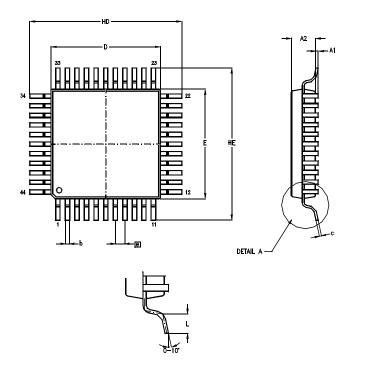

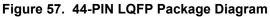

| SYMBOL | MILLIN | <b>/ETER</b> | INCH |      |  |

|--------|--------|--------------|------|------|--|

| STMDOL | MIN    | MAX          | MIN  | MAX  |  |

| A1     | 0.05   | 0,25         | ,002 | .010 |  |

| A2     | 2.00   | 2.25         | .078 | .089 |  |

| b      | 0.25   | 0.45         | .010 | .018 |  |

| с      | 0.13   | 0.20         | .005 | .008 |  |

| HD     | 13.70  | 14.15        | .539 | .557 |  |

| D      | 9.90   | 10.10        | .390 | .398 |  |

| HE     | 13.70  | 14.15        | .539 | .557 |  |

| E      | 9.90   | 10.10        | .390 | .398 |  |

| e      | 0.80   | 0.80 BSC     |      | BSC  |  |

| L      | 0.60   | 1.20         | .024 | .047 |  |

NOTES: 1. CONTROLLING DIMENSIONS : WILLIMETER 2. LEAD COPLANARITY : MAX <u>.10</u> .004"

Zilog 80

## **Customer Support**

For answers to technical questions about the product, documentation, or any other issues with Zilog's offerings, please visit Zilog's Knowledge Base at <a href="http://www.zilog.com/kb">http://www.zilog.com/kb</a>.

For any comments, detail technical questions, or reporting problems, please visit Zilog's Technical Support at <u>http://support.zilog.com</u>.