### E·XFL

### Zilog - Z86E4412FSC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                   |

|----------------------------|------------------------------------------------------------|

| Core Processor             | Z8                                                         |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 12MHz                                                      |

| Connectivity               | EBI/EMI                                                    |

| Peripherals                | POR, WDT                                                   |

| Number of I/O              | 32                                                         |

| Program Memory Size        | 16KB (16K x 8)                                             |

| Program Memory Type        | OTP                                                        |

| EEPROM Size                | -                                                          |

| RAM Size                   | 236 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                |

| Data Converters            | -                                                          |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                            |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 44-LQFP                                                    |

| Supplier Device Package    | 44-LQFP (10x10)                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86e4412fsc00tr |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **z**ilog<sup>°</sup>

### Warning: DO NOT USE IN LIFE SUPPORT

### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, Z8 Encore! XP, Z8 Encore! MC, Crimzon, eZ80, and ZNEO are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

ISO 9001:2000 FS 507510 Zilog products are designed and manufactured under an ISO registered 9001:2000 Quality Management System. For more details, please visit www.zilog.com/quality.

zilog

### Table 1. Z86E33/733/E34, E43/743/E44 Features (Continued)

| Device                      | ROM<br>(KB) | RAM <sup>1</sup><br>(Bytes) | I/O<br>Lines | Speed<br>(MHz) |

|-----------------------------|-------------|-----------------------------|--------------|----------------|

| Z86E44                      | 16          | 236                         | 32           | 12             |

| <sup>1</sup> General-Purpos | se          |                             |              |                |

- Standard Temperature ( $V_{CC} = 3.5 \text{ V to } 5.5 \text{ V}$ )

- Extended Temperature ( $V_{CC} = 3.5 \text{ V to } 5.5 \text{ V}$ )

- Available Packages:

- 28-Pin DIP/SOIC/PLCC OTP (E33/733/E34)

- 40-Pin DIP OTP (E43/743/E44)

- 44-Pin PLCC/LQFP OTP (E43/743/E44)

- Software Enabled Watchdog Timer (WDT)

- Push-Pull/Open-Drain Programmable on Port 0, Port 1, and Port 2

- 24/32 Input/Output Lines

- Clock-Free WDT Reset

- Auto Power-On Reset (POR)

- Programmable OTP Options:

- RC Oscillator

- EPROM Protect

- Auto Latch Disable

- Permanently Enabled WDT

- Crystal Oscillator Feedback Resistor Disable

- RAM Protect

- Low-Power Consumption: 60 mW

- Fast Instruction Pointer: 0.75 µs

- Two Standby Modes: STOP and HALT

- Digital Inputs CMOS Levels, Schmitt-Triggered

- Software Programmable Low EMI Mode

- Two Programmable 8-Bit Counter/Timers Each with a 6-Bit Programmable Prescaler

- Six Vectored, Priority Interrupts from Six Different Sources

- Two Comparators

zilog |<sub>9</sub>

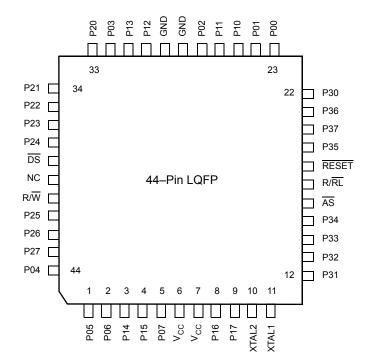

Figure 5. 44-Pin LQFP Pin Configuration Standard Mode

Table 4. 44-Pin LQFP Pin Identification

| Pin No | Symbol          | Symbol Function           |              |

|--------|-----------------|---------------------------|--------------|

| 1-2    | P05-P06         | Port 0, Pins 5,6 Input/Ou |              |

| 3-4    | P14-P15         | Port 1, Pins 4,5          | Input/Output |

| 5      | P07             | Port 0, Pin 7             | Input/Output |

| 6-7    | V <sub>CC</sub> | Power Supply              |              |

| 8-9    | P16-P17         | Port 1, Pins 6,7 Input/C  |              |

| 10     | XTAL2           | Crystal Oscillator Output |              |

| 11     | XTAL1           | Crystal Oscillator Input  |              |

| 12-14  | P31-P33         | Port 3, Pins 1,2,3        | Input        |

| 15     | P34             | Port 3, Pin 4 Output      |              |

| 16     | AS              | Address Strobe Output     |              |

| 17     | R//RL           | ROM/ROMIess select Input  |              |

|        |                 |                           |              |

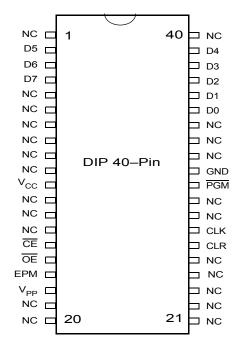

Figure 6. 40-Pin DIP Pin Configuration EPROM Mode

| Table 5. 40-Pin DIP Package Pin Identification EPROM Mode |

|-----------------------------------------------------------|

|-----------------------------------------------------------|

| Pin No | Symbol          | Function               | Direction    |

|--------|-----------------|------------------------|--------------|

| 1      | NC              | No Connection          |              |

| 2-4    | D5-D7           | Data 5,6,7             | Input/Output |

| 5-10   | NC              | No Connection          |              |

| 11     | V <sub>CC</sub> | Power Supply           |              |

| 12-14  | NC              | No Connection          |              |

| 15     | CE              | Chip Select Ing        |              |

| 16     | OE              | Output Enable Input    |              |

| 17     | EPM             | EPROM Prog. Mode Input |              |

| 18     | V <sub>PP</sub> | Prog. Voltage Input    |              |

| 19-25  | NC              | No Connection          |              |

| 26     | CLR             | Clear                  | Input        |

| 27     | CLK             | Clock                  | Input        |

| 28-29  | NC              | No Connection          |              |

|        |                 |                        |              |

## zilog <sub>12</sub>

| Pin No | Symbol | Function       | Direction    |

|--------|--------|----------------|--------------|

| 30     | /PGM   | Prog. Mode     | Input        |

| 31     | GND    | Ground         |              |

| 32-34  | NC     | No Connection  |              |

| 35-39  | D0-D4  | Data 0,1,2,3,4 | Input/Output |

| 40     | NC     | No Connection  |              |

### Table 5. 40-Pin DIP Package Pin Identification EPROM Mode (Continued)

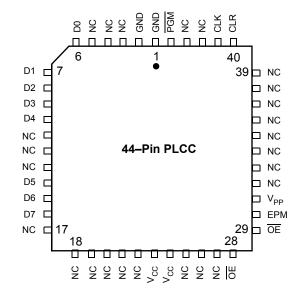

Figure 7. 44-Pin PLCC Pin Configuration EPROM Programming Mode

| D: 11  | • • •           |                  | Direction    |

|--------|-----------------|------------------|--------------|

| Pin No | Symbol          | Symbol Function  |              |

| 1-2    | GND             | Ground           |              |

| 3-5    | NC              | No Connection    |              |

| 6-10   | D0-D4           | Data 0,1,2,3,4   | Input/Output |

| 11-13  | NC              | No Connection    |              |

| 14-16  | D5-D7           | Data 5,6,7       | Input/Output |

| 17-22  | NC              | No Connection    |              |

| 23-24  | V <sub>CC</sub> | Power Supply     |              |

| 25-27  | NC              | No Connection    |              |

| 28     | CE              | Chip Select      | Input        |

| 29     | OE              | Output Enable    | Input        |

| 30     | EPM             | EPROM Prog. Mode | Input        |

| 31     | V <sub>PP</sub> | Prog. Voltage    | Input        |

zilog <sub>15</sub>

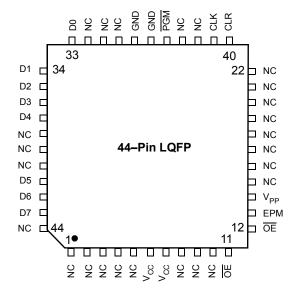

Figure 8. 44-Pin LQFP Pin Configuration EPROM Programming Mode

| Pin No | Symbol          | Function               | Direction |

|--------|-----------------|------------------------|-----------|

| 1-5    | NC              | No Connection          |           |

| 6-7    | V <sub>CC</sub> | Power Supply           |           |

| 8-10   | NC              | No Connection          |           |

| 11     | CE              | Chip Select            | Input     |

| 12     | OE              | Output Enable          | Input     |

| 13     | EPM             | EPROM Prog. Mode Input |           |

| 14     | V <sub>PP</sub> | Prog. Voltage Input    |           |

| 15-22  | NC              | No Connection          |           |

| 23     | CLR             | Clear Input            |           |

| 24     | CLK             | Clock Input            |           |

| 25-26  | NC              | No Connection          |           |

| 27     | /PGM            | Prog. Mode             | Input     |

| 28-29  | GND             | Ground                 |           |

| 30-32  | NC              | No Connection          |           |

Table 7. 44-Pin LQFP Pin Identification EPROM Programming Mode

# zilog <sub>16</sub>

### Table 7. 44-Pin LQFP Pin Identification EPROM Programming Mode (Continued)

| Pin No | Symbol | Function       | Direction    |

|--------|--------|----------------|--------------|

| 33-37  | D0-D4  | Data 0,1,2,3,4 | Input/Output |

| 38-40  | NC     | No Connection  |              |

| 41-43  | D5-D7  | Data 5,6,7     | Input/Output |

| 44     | NC     | No Connection  |              |

PS022901-0508

zilog <sub>20</sub>

### **Electrical Characteristics**

### **Absolute Maximum Ratings**

### Table 10. Absolute Maximum Ratings

| Parameter Min                                                                                      |      | Мах                | Units | Notes |

|----------------------------------------------------------------------------------------------------|------|--------------------|-------|-------|

| Ambient Temperature under Bias                                                                     | -40  | +105               | С     |       |

| Storage Temperature                                                                                | -65  | +150               | С     |       |

| Voltage on any Pin with Respect to V <sub>SS</sub>                                                 | -0.6 | +7                 | V     | 1     |

| Voltage on V <sub>DD</sub> Pin with Respect to V <sub>SS</sub> –0.3                                |      |                    | V     |       |

| Voltage on XTAL1, P32, P33 and $\overline{\text{RESET}}$ Pins with Respect to V <sub>SS</sub> –0.6 |      | V <sub>DD</sub> +1 | V     | 2     |

| Total Power Dissipation                                                                            |      | 1.21               | W     |       |

| Maximum Allowable Current out of V <sub>SS</sub>                                                   |      | 220                | mA    |       |

| Maximum Allowable Current into V <sub>DD</sub>                                                     |      | 180                | mA    |       |

| Maximum Allowable Current into an Input Pin                                                        | -600 | +600               | μA    | 3     |

| Maximum Allowable Current into an Open-Drain Pin -600                                              |      | +600               | μA    | 4     |

| Maximum Allowable Output Current Sunk by Any I/O Pin                                               |      | 25                 | mA    |       |

| Maximum Allowable Output Current Sourced by Any I/O Pin                                            |      | 25                 | mA    |       |

| Maximum Allowable Output Current Sunk by RESET Pin                                                 |      | 3                  | mA    |       |

|                                                                                                    |      |                    |       |       |

### Notes

1. This applies to all pins except XTAL pins and where otherwise noted.

2. There is no input protection diode from pin to V<sub>DD</sub>.

3. This excludes XTAL pins.

4. Device pin is not at an output Low state.

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period may affect device reliability.

## Zilog<sup>°</sup> 27

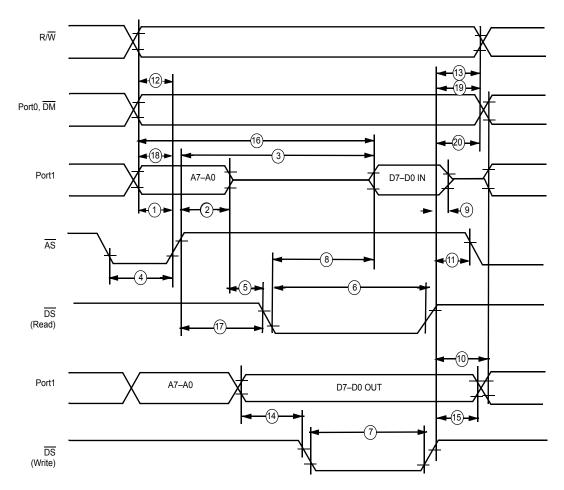

Figure 14. External I/O or Memory Read/Write Timing (Z86E43/743/E44 Only)

| Table 13. DC Electrical Characteristics $T_A = 0$ °C to +70 °C, 12 MHz |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

| No. | Symbol   | Parameter                                   | V <sub>CC</sub> <sup>1</sup> | Min | Max | Units | Notes |

|-----|----------|---------------------------------------------|------------------------------|-----|-----|-------|-------|

| 1   | TdA(AS)  | Address Valid to $\overline{AS}$ Rise Delay | 3.5V                         | 35  |     | ns    | 2     |

|     |          |                                             | 5.5V                         | 35  |     | ns    | 2     |

| 2   | TdAS(A)  | AS Rise to Address Float Delay              | 3.5V                         | 45  |     | ns    | 2     |

|     |          |                                             | 5.5V                         | 45  |     | ns    | 2     |

| 3   | TdAS(DR) | AS Rise to Read Data Req'd Valid            | 3.5V                         |     | 250 | ns    | 2,3   |

|     |          |                                             | 5.5V                         |     | 250 | ns    | 2,3   |

Zilog<sup>28</sup>

### Table 13. DC Electrical Characteristics $T_A = 0$ °C to +70 °C, 12 MHz (Continued)

| No. | Symbol    | Parameter                                                        | V <sub>cc</sub> <sup>1</sup> | Min | Мах | Units | Notes |

|-----|-----------|------------------------------------------------------------------|------------------------------|-----|-----|-------|-------|

| 4   | TwAS      | AS Low Width                                                     | 3.5V                         | 55  |     | ns    | 2     |

|     |           |                                                                  | 5.5V                         | 55  |     | ns    | 2     |

| 5   | TdAS(DS)  | Address Float to $\overline{\text{DS}}$ Fall                     | 3.5V                         | 0   |     | ns    |       |

|     |           |                                                                  | 5.5V                         | 0   |     | ns    |       |

| 6   | TwDSR     | DS (Read) Low Width                                              | 3.5V                         | 200 |     | ns    | 2,3   |

|     |           |                                                                  | 5.5V                         | 200 |     | ns    | 2,3   |

| 7   | TwDSW     | DS (Write) Low Width                                             | 3.5V                         | 110 |     | ns    | 2,3   |

|     |           |                                                                  | 5.5V                         | 110 |     | ns    | 2,3   |

| 8   | TdDSR(DR) | DS Fail to Read Data Req'd Valid                                 | 3.5V                         |     | 150 | ns    | 2,3   |

|     |           |                                                                  | 5.5V                         |     | 150 | ns    | 2,3   |

| 9   | ThDR(DS)  | Read Data to $\overline{\text{DS}}$ Rise Hold Time               | 3.5V                         | 0   |     | ns    | 2     |

|     |           |                                                                  | 5.5V                         | 0   |     | ns    | 2     |

| 10  | TdDS(A)   | DS Rise to Address Active Delay                                  | 3.5V                         | 45  |     | ns    | 2     |

|     |           |                                                                  | 5.5V                         | 55  |     | ns    | 2     |

| 11  | TdDS(AS)  | $\overline{\text{DS}}$ Rise to $\overline{\text{AS}}$ Fall Delay | 3.5V                         | 30  |     | ns    | 2     |

|     |           |                                                                  | 5.5V                         | 45  |     | ns    | 2     |

| 12  | TdR/W(AS) | S) $R/\overline{W}$ Valid to $\overline{AS}$ Rise Delay          | 3.5V                         | 45  |     | ns    | 2     |

|     |           |                                                                  | 5.5V                         | 45  |     | ns    | 2     |

| 13  | TdDS(R/W) | $PS(R/W)$ DS Rise to $R/\overline{W}$ Not Valid                  | 3.5V                         | 45  |     | ns    | 2     |

|     |           |                                                                  | 5.5V                         | 45  |     | ns    | 2     |

| 14  | TdDW(DSW) | DSW) Write Data Valid to DS Fall (Write)<br>Delay                | 3.5V                         | 55  |     | ns    | 2     |

|     |           |                                                                  | 5.5V                         | 55  |     | ns    | 2     |

| 15  | TdDS(DW)  | DS Rise to Write Data Not Valid Delay                            | 3.5V                         | 45  |     | ns    | 2     |

|     |           |                                                                  | 5.5V                         | 55  |     | ns    | 2     |

| 16  | TdA(DR)   | DR) Address Valid to Read Data Req'd<br>Valid                    | 3.5V                         |     | 310 | ns    | 2,3   |

|     |           |                                                                  | 5.5V                         |     | 310 | ns    | 2,3   |

| 17  | TdAS(DS)  | $\overline{\text{AS}}$ Rise to $\overline{\text{DS}}$ Fall Delay | 3.5V                         | 65  |     | ns    | 2     |

|     |           |                                                                  | 5.5V                         | 65  |     | ns    | 2     |

Zilog<sup>®</sup> <sub>30</sub>

| No.   | Symbol    | Parameter                                                         | V <sub>CC</sub> <sup>1</sup> | Min | Мах | Units | Notes |

|-------|-----------|-------------------------------------------------------------------|------------------------------|-----|-----|-------|-------|

| 10    | TdDS(A)   | DS Rise to Address Active<br>Delay                                | 4.5V                         | 45  |     | ns    | 2     |

|       |           |                                                                   | 5.5V                         | 55  |     | ns    | 2     |

| 11    | TdDS(AS)  | $\overline{\text{DS}}$ Rise to $\overline{\text{AS}}$ Fall Delay  | 4.5V                         | 45  |     | ns    | 2     |

|       |           |                                                                   | 5.5V                         | 45  |     | ns    | 2     |

| 12    | TdR/W(AS) | $R/\overline{W}$ Valid to $\overline{AS}$ Rise Delay              | 4.5V                         | 45  |     | ns    | 2     |

|       |           |                                                                   | 5.5V                         | 45  |     | ns    | 2     |

| 13    | TdDS(R/W) | $\overline{\text{DS}}$ Rise to R/ $\overline{\text{W}}$ Not Valid | 4.5V                         | 45  |     | ns    | 2     |

|       |           |                                                                   | 5.5V                         | 45  |     | ns    | 2     |

| 14    | TdDW(DSW) | Write Data Valid to DS Fall (Write)<br>Delay                      | 4.5V                         | 55  |     | ns    | 2     |

|       |           |                                                                   | 5.5V                         | 55  |     | ns    | 2     |

| 15    | TdDS(DW)  | DS Rise to Write Data Not Valid Delay                             | 4.5V                         | 55  |     | ns    | 2     |

|       |           |                                                                   | 5.5V                         | 55  |     | ns    | 2     |

| 16    | TdA(DR)   | Address Valid to Read Data Req'd Valid                            | 4.5V                         |     | 310 | ns    | 2,3   |

|       |           |                                                                   | 5.5V                         |     | 310 | ns    | 2,3   |

| 17    | TdAS(DS)  | $\overline{\text{AS}}$ Rise to $\overline{\text{DS}}$ Fall Delay  | 4.5V                         | 65  |     | ns    | 2     |

|       |           |                                                                   | 5.5V                         | 65  |     | ns    | 2     |

| 18    | TdDM(AS)  | DM Valid to AS Rise Delay                                         | 4.5V                         | 35  |     | ns    | 2     |

|       |           |                                                                   | 5.5V                         | 35  |     | ns    | 2     |

| 19    | ThDS(AS)  | S(AS) DS Valid to Address Valid Hold Time                         | 4.5V                         | 35  |     | ns    | 2     |

|       |           |                                                                   | 5.5V                         | 35  |     | ns    | 2     |

| Notoo |           |                                                                   |                              |     |     |       |       |

### Table 14. DC Electrical Characteristics $T_A = -40$ °C to +105 °C, 12 MHz (Continued)

#### Notes

1. The V<sub>CC</sub> voltage specification of 5.5 V guarantees 5.0 V  $\pm$  0.5 V and the V<sub>CC</sub> voltage specification of 3.5 V guarantees only 3.5 V.

2. Timing numbers given are for minimum TpC.

3. When using extended memory timing, add 2 TpC.

Standard Test Load

All timing references use 0.7  $\rm V_{CC}$  for a logic 1 and 0.2  $\rm V_{CC}$  for a logic 0.

For Standard Mode (not Low-EMI Mode for outputs) with SMR, D1 = 0, D0 = 0.

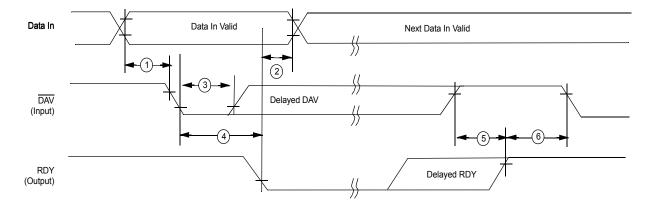

### Handshake Timing Diagrams

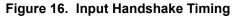

Figure 17. Output Handshake Timing

| Table 17. Additional Timing Table (Divide by | Two Mode) T <sub>A</sub> = 0 °C to +70 °C |

|----------------------------------------------|-------------------------------------------|

|----------------------------------------------|-------------------------------------------|

| No | Symbol    | Parameter                     | V <sub>CC</sub> <sup>1</sup> | Min  | Max | Min | Мах | Units Conditions | Notes |

|----|-----------|-------------------------------|------------------------------|------|-----|-----|-----|------------------|-------|

| 1  | ТрС       | Input Clock Period            | 3.5V                         | 62.5 | DC  | 250 | DC  | ns               | 2,6,4 |

|    |           |                               | 5.5V                         | 62.5 | DC  | 250 | DC  | ns               | 2,6,4 |

| 2  | 2 TrC,TfC | Clock Input Rise & Fall Times | 3.5V                         |      | 15  |     | 25  | ns               | 2,6,4 |

|    |           |                               | 5.5V                         |      | 15  |     | 25  | ns               | 2,6,4 |

| 3  | TwC       | Input Clock Width             | 3.5V                         | 31   |     | 31  |     | ns               | 2,6,4 |

|    |           |                               | 5.5V                         | 31   |     | 31  |     | ns               | 2,6,4 |

zilog

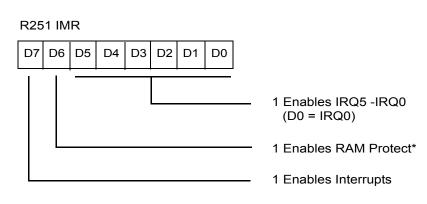

RAM Protect. The upper portion of the RAM's address spaces 80h to EFh (excluding the control registers) can be protected from reading and writing. This option can be selected during the EPROM Programming Mode. After this option is selected, the user can activate this feature from the internal EPROM. D6 of the IMR control register (R251) is used to turn off/on the RAM protect by loading a 0 or 1, respectively. A "1" in D6 indicates RAM Protect enabled.

**Stack**. The Z86E43/743/E44 external data memory or the internal register file can be used for the stack. The 16-bit Stack Pointer (R254-R255) is used for the external stack, which can reside anywhere in the data memory for ROMless mode, but only from 4096/8192/16384 to 65535 in ROM mode. An 8-bit Stack Pointer (R255) is used for the internal stack on the Z8 that resides within the 236 general-purpose registers (R4-R239). SPH (R254) can be used as a general-purpose register when using internal stack only. R254 and R255 are set to 00H after any reset or Stop Mode Recovery.

**Counter/Timers**. There are two 8-bit programmable counter/timers (T0 and T1), each driven by its own 6-bit programmable prescaler. The Ti prescaler is driven by internal or external clock sources; however, the TO prescaler is driven by the internal clock only (see Figure 27).

The 6-bit prescalers can divide the input frequency of the clock source by any integer number from 1 to 64. Each prescaler drives its counter, which decrements the value (1 to 256), that has been loaded into the counter. When the counter reaches the end of count, a timer interrupt request, IRQ4 (T0) or IRQ5 (T1), is generated.

The counters can be programmed to start, stop, restart to continue, or restart from the initial value. The counters can also be programmed to stop upon reaching one (single pass mode) or to automatically reload the initial value and continue counting (modulo-n continuous mode).

The counters, but not the prescalers, can be read at any time without disturbing their value or count mode. The clock source for T1 is user-definable and can be either the internal microprocessor clock divided by four, or an external signal input through Port 3. The Timer Mode register configures the external timer input (P31) as an external clock, a trigger input that can be retriggerable or non-retriggerable, or as a gate input for the internal clock. Port 3 line P36 serves as a timer output ( $T_{OUT}$ ) through which T0, T1, or the internal clock can be output. The counter/timers can be cascaded by connecting the T0 output to the input of T1.

### zilog

When more than one interrupt is pending, priorities are resolved by a programmable priority encoder that is controlled by the Interrupt Priority Register (IPR). An interrupt machine cycle is activated when an interrupt request is granted. Thus, disabling all subsequent interrupts, saves the Program Counter and Status Flags, and then branches to the program memory vector location reserved for that interrupt. All interrupts are vectored through locations in the program memory. This memory location and the next byte contain the 16bit starting address of the interrupt service routine for that particular interrupt request.

To accommodate polled interrupt systems, interrupt inputs are masked and the interrupt request register is polled to determine which of the interrupt requests need service.

An interrupt resulting from AN1 is mapped into IRQ2, and an interrupt from AN2 is mapped into IRQ0. Interrupts IRQ2 and IRQ0 may be rising, falling or both edge triggered, and are programmable by the user. The software may poll to identify the state of the pin.

Programming bits for the Interrupt Edge Select are located in bits D7 and D6 of the IRQ Register (R250). The configuration is shown in Table 21.

|                                                    | IRO | Inte | Interrupt Edge |  |  |  |  |

|----------------------------------------------------|-----|------|----------------|--|--|--|--|

| D7                                                 | D6  | P31  | P32            |  |  |  |  |

| 0                                                  | 0   | F    | F              |  |  |  |  |

| 0                                                  | 1   | F    | R              |  |  |  |  |

| 1                                                  | 0   | R    | F              |  |  |  |  |

| 1                                                  | 1   | R/F  | R/F            |  |  |  |  |

| Notes<br>1. F = Falling Edge<br>2. R = Rising Edge |     |      |                |  |  |  |  |

### Table 21. IRQ Register Configuration

**Clock**. The on-chip oscillator has a high-gain, parallel-resonant amplifier for connection to a crystal, RC, ceramic resonator, or any suitable external clock source (XTAL1 = Input, XTAL2 = Output). The crystal should be AT cut, 10 kHz to 16 MHz max, with a series resistance (RS) less than or equal to  $100 \Omega$ .

The crystal should be connected across XTAL1 and XTAL2 using the vendor's recommended capacitor values from each pin directly to device pin Ground. The RC oscillator option can be selected in the programming mode. The RC oscillator configuration must be an external resistor connected from XTAL1 to XTAL2, with a frequency-setting capacitor from XTAL1 to Ground (Table 29).

zilog ,

**Note:** WDT time-out in STOP Mode will not reset SMR,SMR2,PCON, WDTMR, P2M, P3M, Ports 2 & 3 Data Registers, but will activate the  $T_{POR}$  delay.

**WDTMR Register Accessibility**. The WDTMR register is accessible only during the first 60 internal system clock cycles from the execution of the first instruction after Power-On Reset, Watchdog reset or a Stop Mode Recovery (Figure 33 and Figure 34). After this point, the register cannot be modified by any means, intentional or otherwise. The WDTMR cannot be read and is located in Bank F of the Expanded Register File at address location 0Fh.

**Clock Free WDT Reset**. The WDT will enable the Z8 to reset the I/0 pins whenever the WDT times out, even without a clock source running on the XTAL1 and XTAL2 pins. WDTMR Bit D4 must be 0 for the clock Free WDT to work. The I/O pins will default to their default settings.

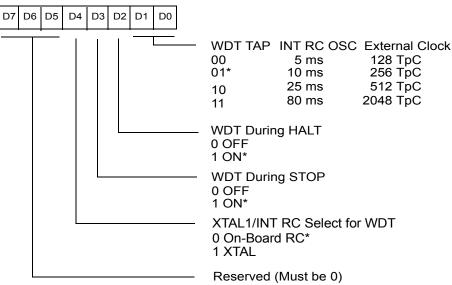

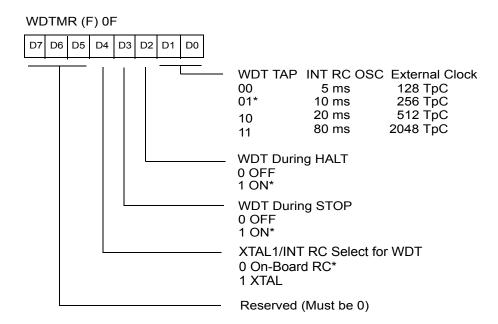

### WDTMR (F) 0F

>

\* Default setting after RESET

### Figure 33. Watchdog Timer Mode Register Write Only

\* Default setting after RESET

### Figure 38. Watchdog Timer Mode Register (Write Only)

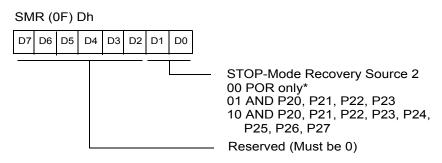

Note: Not used in conjunction with SMR Source

### Figure 39. Stop Mode Recovery Register2 (Write Only)

Zilog <sub>73</sub>

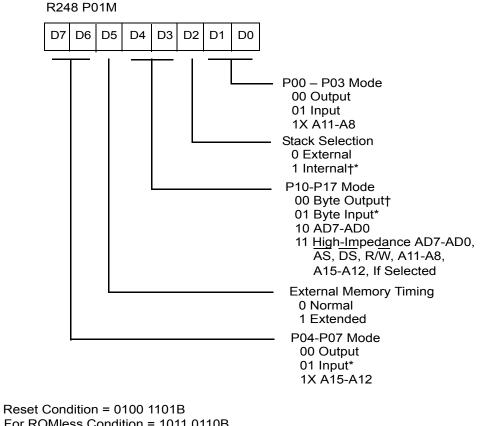

Reset Condition = 0100 1101B For ROMless Condition = 1011 0110B † Z86E33/733/E34 Must be 00 \* Default after Reset

Figure 48. Port 0 and 1 Mode Register (F8<sub>h</sub>: Write Only)

\* This option must be selected when ROM code is submitted for ROM Masking, otherwise this control bit is disabled permanently

Zilog <sub>80</sub>

### **Customer Support**

For answers to technical questions about the product, documentation, or any other issues with Zilog's offerings, please visit Zilog's Knowledge Base at <a href="http://www.zilog.com/kb">http://www.zilog.com/kb</a>.

For any comments, detail technical questions, or reporting problems, please visit Zilog's Technical Support at <u>http://support.zilog.com</u>.