Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                             |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 40MHz                                                                        |

| Connectivity               | CSIO, I <sup>2</sup> C, LINbus, SmartCard, UART/USART, USB                   |

| Peripherals                | I <sup>2</sup> S, LVD, POR, PWM, WDT                                         |

| Number of I/O              | 65                                                                           |

| Program Memory Size        | 304KB (304K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 32K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                                 |

| Data Converters            | A/D 16x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 80-LQFP                                                                      |

| Supplier Device Package    | 80-LQFP (12x12)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/s6e1b34e0agv20000 |

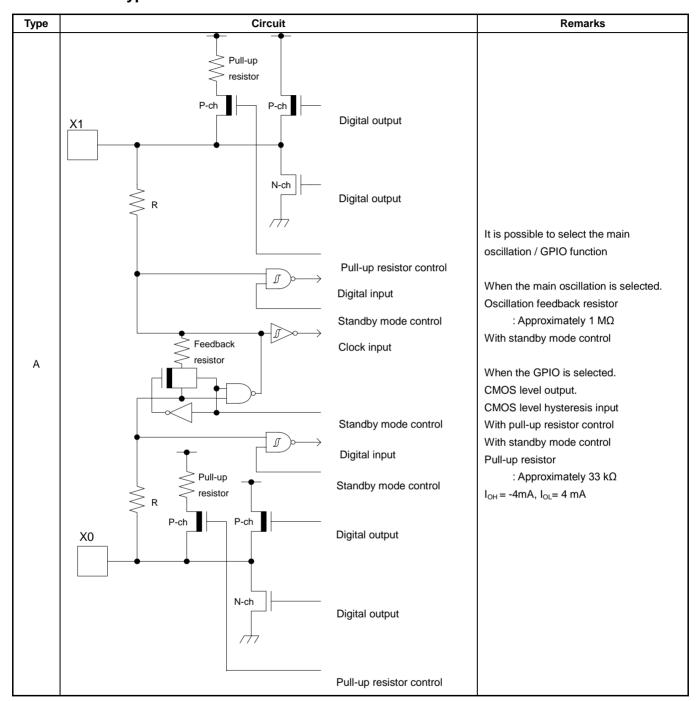

# **Descriptor System Data Transfer Controller (DSTC)** (64 Channels)

- ■The DSTC can transfer data at high-speed without going via the CPU. The DSTC adopts the Descriptor

- system and, following the specified contents of the Descriptor that has already been constructed on the

- memory, can access directly the memory / peripheral device and performs the data transfer operation.

- It supports the software activation, the hardware activation, and the chain activation functions

## A/D Converter (Max: 24 Channels)

- ■12-bit A/D Converter

- □ Successive approximation type

- □ Conversion time: 2.0 µs @ 2.7 V to 3.6 V

- □ Priority conversion available (2 levels of priority)

- □ Scan conversion mode

- ☐ Built-in FIFO for conversion data storage (for scan conversion: 16 steps, for priority conversion: 4 steps)

## **Base Timer (Max: 8 Channels)**

The operation mode of each channel can be selected from one of the following.

- ■16-bit PWM timer

- ■16-bit PPG timer

- ■16/32-bit reload timer

- ■16/32-bit PWC timer

#### **General-Purpose I/O Port**

This series can use its pin as a general-purpose I/O port when it is not used for an external bus or a peripheral function. All ports can be set to fast general-purpose I/O ports or slow general-purpose I/O ports. In addition, this series has a port relocate function that can set to which I/O port a peripheral function can be allocated.

- ■All ports are Fast GPIO which can be accessed by 1cycle

- ■Capable of controlling the pull-up of each pin

- ■Capable of reading pin level directly

- ■Port relocate function

- ■Up to 102 fast general-purpose I/O ports @120-pin package

- Certain ports are 5 V tolerant. See 4. List of Pin Functions and 5. I/O Circuit Type for the corresponding pins.

#### **Dual Timer (32-/16-bit Down Counter)**

The Dual Timer consists of two programmable 32-/16-bit down counters. The operation mode of each timer channel can be selected from one of the following.

- ■Free-running mode

- ■Periodic mode (= Reload mode)

- ■One-shot mode

#### **Multi-Function Timer**

The Multi-function Timer consists of the following blocks.

- ■16-bit free-run timer × 3 channels

- ■Input capture × 4 channels

- ■Output compare x 6 channels

- ■ADC start compare × 6 channel

- ■Waveform generator × 3 channels

- ■16-bit PPG timer x 3 channels

IGBT mode is contained.

The following function can be used to achieve the motor control.

- ■PWM signal output function

- ■DC chopper waveform output function

- ■Dead time function

- ■Input capture function

- ■ADC start function

- ■DTIF (motor emergency stop) interrupt function

## Real-Time Clock (RTC with Vbat)

The Real-time Clock counts year/month/day/hour/minute/second/day of the week from year 01 to year 99.

- ■The RTC can generate an interrupt at a specific time (year/month/day/hour/minute/second/day of the week) and can also generate an interrupt in a specific year, in a specific month, on a specific day, at a specific hour or at a specific minute.

- ■It has a timer interrupt function generating an interrupt upon a specific time or at specific intervals.

- ■It can keep counting while rewriting the time.

- It can count leap years automatically.

#### **Watch Counter**

The Watch Counter wakes up the microcontroller from the low power consumption mode. The clock source can be selected from the main clock, the sub clock, the built-in high-speed CR clock or the built-in low-speed CR clock.

Interval timer: up to 64 s (sub clock: 32.768 kHz)

## **External Interrupt Controller Unit**

- ■Up to 24 external interrupt input pins

- ■Non-maskable interrupt (NMI) input pin: 1

## **Watchdog Timer (2 Channels)**

The watchdog timer generates an interrupt or a reset when the counter reaches a time-out value.

This series consists of two different watchdogs, hardware watchdog and software watchdog.

The hardware watchdog timer is clocked by the built-in low-speed CR oscillator. Therefore, the hardware watchdog is

## **Power Supply**

■Wide voltage range:

VCC = 1.65V to 3.6 V

VCC = 3.0V to 3.6V (when USB is used)

■Power supply for VBAT: VBAT = 1.65 V to 3.6 V

| 12.  | Ordering Information                | 110 |

|------|-------------------------------------|-----|

| 13.  | Package Dimensions                  | 111 |

| Doc  | ument History                       | 114 |

| Sale | s, Solutions, and Legal Information | 115 |

|          | Pin No.  |         | Din Nama   | I/O Circuit Tyro | Din State Type |  |

|----------|----------|---------|------------|------------------|----------------|--|

| LQFP-120 | LQFP-100 | LQFP-80 | - Pin Name | I/O Circuit Type | Pin State Type |  |

|          |          |         | P64        |                  |                |  |

| 112      | -        | -       | SOT5_1     | – F              | J              |  |

| 112      |          | _       | TIOA7_0    | '                |                |  |

|          |          |         | INT10_2    |                  |                |  |

|          |          |         | P63        |                  |                |  |

|          |          |         | MI2SWS5_0  |                  |                |  |

| 113      | 93       | 73      | INT03_0    | _ I              | J              |  |

| 110      |          |         | TIOB6_1    |                  |                |  |

|          |          |         | IC0_DATA_0 |                  |                |  |

|          | -        | -       | SIN5_1     |                  |                |  |

|          |          |         | P62        |                  |                |  |

|          |          |         | SCK5_0     |                  | J              |  |

|          |          |         | MI2SCK5_0  |                  |                |  |

| 114      | 94       | 74      | ADTG_3     | I                |                |  |

|          |          |         | INT07_1    |                  |                |  |

|          |          |         | TIOA6_1    |                  |                |  |

|          |          |         | IC0_RST_0  |                  |                |  |

|          |          |         | P61        |                  |                |  |

|          |          |         | SOT5_0     |                  |                |  |

| 115      | 95       | 75      | MI2SDO5_0  | I                | I              |  |

|          |          |         | TIOB2_2    |                  |                |  |

|          |          |         | DTTI0X_2   |                  |                |  |

|          |          |         | P60        |                  |                |  |

|          |          |         | SIN5_0     |                  |                |  |

|          | 00       |         |            | MI2SDI5_0        |                |  |

| 44.0     |          | 70      | TIOA2_2    |                  |                |  |

| 116      | 96       | 76      | CEC1_0     | 1                | 0              |  |

|          |          |         | INT15_1    |                  |                |  |

|          |          |         | WKUP3      |                  |                |  |

|          |          |         | IGTRG0_1   |                  |                |  |

|          |          |         | P80        |                  |                |  |

| 447      | 07       | 77      | SIN7_2     |                  |                |  |

| 117      | 97       | 77      | INT20_1    | - I              | J              |  |

|          |          |         | C0         |                  |                |  |

|          |          |         | P81        |                  |                |  |

| 44.0     | 00       | 70      | SOT7_2     |                  |                |  |

| 118      | 98       | 78      | INT11_0    | <u> </u>         | J              |  |

|          |          |         | C1         |                  |                |  |

| 440      | 00       | 70      | P82        |                  |                |  |

| 119      | 99       | 79      | SCK7_2     | - I              | 1              |  |

| 120      | 100      | 80      | VSS        | -                | -              |  |

<sup>\*: 5</sup> V tolerant I/O

| Pin Function | Pin Name           | Function Description                    | 1.050.463 | Pin No.  | LOED OS |

|--------------|--------------------|-----------------------------------------|-----------|----------|---------|

|              |                    | T direction 2000 spiron                 | LQFP-120  | LQFP-100 | LQFP-80 |

|              | INT00_0            | <u></u>                                 | 2         | 2        | 2       |

|              | INT00_1            | External interrupt request 00 input pin | 97        | 82       | -       |

|              | INT00_2            |                                         | 102       | 87       | 67      |

|              | INT01_0            | External interrupt request 01 input pin | 3         | 3        | 3       |

|              | INT01_1            | External interrupt request of impat pin | 98        | 83       | -       |

|              | INT02_0            |                                         | 4         | 4        | 4       |

|              | INT02_1            | External interrupt request 02 input pin | 63        | 53       | 43      |

|              | INT02_2            |                                         | 82        | -        | -       |

|              | INT03_0            |                                         | 113       | 93       | 73      |

|              | INT03_1            | External interrupt request 03 input pin | 66        | 56       | 46      |

| [            | INT03_2            |                                         | 14        | 9        | 9       |

|              | INT04_0            |                                         | 17        | 12       | 12      |

|              | INT04_1            | External interrupt request 04 input pin | 69        | 59       | 49      |

|              | INT04_2            |                                         | 15        | 10       | 10      |

|              | INT05_0            |                                         | 89        | 74       | -       |

|              | INT05_1            | External interrupt request 05 input pin | 76        | 66       | 56      |

|              | INT05_2            |                                         | 16        | 11       | 11      |

|              | INT06_0            |                                         | 23        | 18       | 13      |

| External     | INT06_1            | External interrupt request 06 input pin | 88        | 73       | 60      |

| Interrupt    | INT06_2            |                                         | 96        | 81       | 65      |

|              | INT07_0            |                                         | 24        | 19       | 14      |

|              | INT07_1            | External interrupt request 07 input pin | 114       | 94       | 74      |

| _            | INT07_2            |                                         | 5         | 5        | 5       |

| _            | INT08_0<br>INT08_1 | External interrupt request 08 input pin | 34<br>19  | 29<br>14 | -       |

|              | INT08_1            | External interrupt request 00 input pin | 8         | 8        | 8       |

|              | INT09_0            |                                         | 35        | 30       | -       |

|              | INT09_1            | External interrupt request 09 input pin | 20        | 15       | _       |

|              | INT10_0            |                                         | 36        | 31       | 21      |

|              | INT10_1            | External interrupt request 10 input pin | 21        | 16       | -       |

|              | INT10_2            |                                         | 112       | -        | -       |

|              | INT11_0            |                                         | 118       | 98       | 78      |

|              | INT11_1            | External interrupt request 11 input pin | 22        | 17       | -       |

|              | INT11_2            |                                         | 110       | -        | -       |

|              | INT12_0            |                                         | 49        | 44       | 34      |

|              | INT12_1            | External interrupt request 12 input pin | 32        | 27       | ı       |

|              | INT12_2            |                                         | 108       | -        | -       |

|              | INT13_0            |                                         | 50        | 45       | 35      |

| <u> </u>     | INT13_1            | External interrupt request 13 input pin | 33        | 28       | -       |

| <u> </u>     | INT13_2            |                                         | 52        | -        | -       |

|              | INT14_0            | <del>_</del>                            | 67        | 57       | 47      |

| <u> </u>     | INT14_1            | External interrupt request 14 input pin | 92        | 77       | 61      |

|              | INT14_2            |                                         | 53        | -        | -       |

| Pin Function               | Pin Name           | Function Description                                                               |          | Pin No.  |         |

|----------------------------|--------------------|------------------------------------------------------------------------------------|----------|----------|---------|

| Fili Function              | FIII Naille        | Function Description                                                               | LQFP-120 | LQFP-100 | LQFP-80 |

|                            | SIN3_0             |                                                                                    | 110      | -        | -       |

|                            | SIN3_1             | Multi-function serial interface ch.3 input pin                                     | 2        | 2        | 2       |

|                            | SIN3_2             |                                                                                    | 94       | 79       | 63      |

|                            | SOT3_0<br>(SDA3_0) | Multi-function serial interface ch.3 output pin.                                   | 109      | -        | -       |

| Multi-function             | SOT3_1<br>(SDA3_1) | This pin operates as SOT3 when used as a UART/CSIO/LIN pin (operation mode 0 to 3) | 3        | 3        | 3       |

| Serial 3                   | SOT3_2<br>(SDA3_2) | and as SDA3 when used as an I <sup>2</sup> C pin (operation mode 4).               | 92       | 77       | 61      |

|                            | SCK3_0<br>(SCL3_0) | Multi-function serial interface ch.3 clock I/O pin.                                | 108      | -        | -       |

|                            | SCK3_1<br>(SCL3_1) | This pin operates as SCK3 when used as a CSIO (operation mode 2) and as SCL3       | 4        | 4        | 4       |

|                            | SCK3_2<br>(SCL3_2) | when used as an I <sup>2</sup> C pin (operation mode 4).                           | 96       | 81       | 65      |

|                            | SIN4_0             |                                                                                    | 102      | 87       | 67      |

|                            | SIN4_1             | Multi-function serial interface ch.4 input pin                                     | 76       | 66       | 56      |

|                            | SIN4_2             | 7                                                                                  | 97       | 82       | -       |

|                            | SOT4_0<br>(SDA4_0) | Multi-function serial interface ch.4 output pin.                                   | 99       | 84       | 66      |

|                            | SOT4_1<br>(SDA4_1) | This pin operates as SOT4 when used as a UART/CSIO/LIN pin (operation mode 0 to 3) | 77       | 67       | 57      |

|                            | SOT4_2<br>(SDA4_2) | and as SDA4 when used as an I <sup>2</sup> C pin (operation mode 4).               | 98       | 83       | -       |

| Multi-function<br>Serial 4 | SCK4_0<br>(SCL4_0) | Multi-function serial interface ch.4 clock I/O pin.                                | 107      | 92       | 72      |

| Senai 4                    | SCK4_1<br>(SCL4_1) | This pin operates as SCK4 when used as a CSIO (operation mode 2) and as SCL4       | 78       | 68       | -       |

|                            | SCK4_2<br>(SCL4_2) | when used as an I <sup>2</sup> C pin (operation mode 4).                           | 99       | 84       | 66      |

|                            | CTS4_0             | Multi formation and interference A CTO insert                                      | 106      | 91       | 71      |

|                            | CTS4_1             | Multi-function serial interface ch4 CTS input pin                                  | 79       | 69       | -       |

|                            | CTS4_2             | γιι                                                                                | 100      | 85       | -       |

|                            | RTS4_0             | Multi-function serial interface ch4 RTS input                                      | 105      | 90       | 70      |

|                            | RTS4_1             | pin                                                                                | 80       | 70       | -       |

|                            | RTS4_2             | k                                                                                  | 101      | 86       | -       |

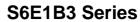

## 5. I/O Circuit Type

## **Surface Mount Type**

Surface mount packaging has longer and thinner leads than lead-insertion packaging, and therefore leads are more easily deformed or bent. The use of packages with higher pin counts and narrower pin pitch results in increased susceptibility to open connections caused by deformed pins, or shorting due to solder bridges.

You must use appropriate mounting techniques. Spansion recommends the solder reflow method, and has established a ranking of mounting conditions for each product. Users are advised to mount packages in accordance with Spansion ranking of recommended conditions.

#### **Lead-Free Packaging**

CAUTION: When ball grid array (BGA) packages with Sn-Ag-Cu balls are mounted using Sn-Pb eutectic soldering, junction strength may be reduced under some conditions of use.

### **Storage of Semiconductor Devices**

Because plastic chip packages are formed from plastic resins, exposure to natural environmental conditions will cause absorption of moisture. During mounting, the application of heat to a package that has absorbed moisture can cause surfaces to peel, reducing moisture resistance and causing packages to crack. To prevent, do the following:

- (1) Avoid exposure to rapid temperature changes, which cause moisture to condense inside the product. Store products in locations where temperature changes are slight.

- (2) Use dry boxes for product storage. Products should be stored below 70% relative humidity, and at temperatures between 5 °C and 30 °C.

When you open Dry Package that recommends humidity 40% to 70% relative humidity.

- (3) When necessary, Spansion packages semiconductor devices in highly moisture-resistant aluminum laminate bags, with a silica gel desiccant. Devices should be sealed in their aluminum laminate bags for storage.

- (4) Avoid storing packages where they are exposed to corrosive gases or high levels of dust.

#### **Baking**

Packages that have absorbed moisture may be de-moisturized by baking (heat drying). Follow the Spansion recommended conditions for baking.

Condition: 125°C/24 h

### **Static Electricity**

Because semiconductor devices are particularly susceptible to damage by static electricity, you must take the following precautions:

- (1) Maintain relative humidity in the working environment between 40% and 70%.

- Use of an apparatus for ion generation may be needed to remove electricity.

- (2) Electrically ground all conveyors, solder vessels, soldering irons and peripheral equipment.

- (3) Eliminate static body electricity by the use of rings or bracelets connected to ground through high resistance (on the level of 1  $M\Omega$ ).

Wearing of conductive clothing and shoes, use of conductive floor mats and other measures to minimize shock loads is recommended.

- (4) Ground all fixtures and instruments, or protect with anti-static measures.

- (5) Avoid the use of styrofoam or other highly static-prone materials for storage of completed board assemblies.

## 7. Handling Devices

## **Power Supply Pins**

In products with multiple VCC and VSS pins, respective pins at the same potential are interconnected within the device in order to prevent malfunctions such as latch-up. However, all of these pins should be connected externally to the power supply or ground lines in order to reduce electromagnetic emission levels, to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total output current rating.

Moreover, connect the current supply source with each Power supply pin and GND pin of this device at low impedance. It is also advisable that a ceramic capacitor of approximately 0.1  $\mu$ F be connected as a bypass capacitor between each Power supply pin and GND pin, between AVCC pin and AVSS pin near this device.

## **Stabilizing Supply Voltage**

A malfunction may occur when the power supply voltage fluctuates rapidly even though the fluctuation is within the recommended operating conditions of the VCC power supply voltage. As a rule, with voltage stabilization, suppress the voltage fluctuation so that the fluctuation in VCC ripple (peak-to-peak value) at the commercial frequency (50 Hz/60 Hz) does not exceed 10% of the VCC value in the recommended operating conditions, and the transient fluctuation rate does not exceed 0.1 V/µs when there is a momentary fluctuation on switching the power supply.

#### **Crystal Oscillator Circuit**

Noise near the X0/X1 and X0A/X1A pins may cause the device to malfunction. Design the printed circuit board so that X0/X1, X0A/X1A pins, the crystal oscillator, and the bypass capacitor to ground are located as close to the device as possible.

It is strongly recommended that the PC board artwork be designed such that the X0/X1 and X0A/X1A pins are surrounded by ground plane as this is expected to produce stable operation.

Evaluate oscillation of your using crystal oscillator by your mount board.

### **Sub Crystal Oscillator**

This series sub oscillator circuit is low gain to keep the low current consumption. The crystal oscillator to fill the following conditions is recommended for sub crystal oscillator to stabilize the oscillation.

■Surface mount type

Size: More than 3.2 mm x 1.5 mm

Load capacitance: Approximately 6 pF to 7 pF

■Lead type

Load capacitance: Approximately 6 pF to 7 pF

## 8. Block Diagram

| Pin Status Type | Functio<br>n Group                                  | roup                        |                                                         | RTC M                                                   | mer Mode,<br>ode, or<br>Mode                                              | State in De<br>RTC Mod<br>Standby S<br>Sta                                | State<br>when<br>Return<br>from Deep<br>Standby<br>Mode<br>State          |                                                                           |                                                                           |                                                                           |

|-----------------|-----------------------------------------------------|-----------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Pin             |                                                     | Power<br>Supply<br>Unstable | Power<br>Supply<br>Stable                               | Power<br>Supply<br>Stable                               | Power<br>Supply<br>Stable                                                 |                                                                           | oply Stable                                                               |                                                                           | oply Stable                                                               | Power<br>Supply<br>Stable                                                 |

|                 |                                                     | -                           | INITX=0                                                 | INITX=1                                                 | INITX=1                                                                   | INIT                                                                      |                                                                           | INIT                                                                      |                                                                           | INITX=1                                                                   |

|                 |                                                     | -                           |                                                         |                                                         | -                                                                         | SPL=0                                                                     | SPL=1                                                                     | SPL=0                                                                     | SPL=1                                                                     | -                                                                         |

|                 | Analog<br>input<br>selected                         | Hi-Z                        | Hi-Z / Internal input fixed at 0 / Analog input enabled | Hi-Z / Internal input fixed at 0 / Analog input enabled | Hi-Z /<br>Internal<br>input fixed<br>at 0 /<br>Analog<br>input<br>enabled |

| L               | External interrupt enabled selected                 |                             |                                                         |                                                         |                                                                           |                                                                           | Maintain<br>previous<br>state                                             | GPIO                                                                      |                                                                           | GPIO                                                                      |

|                 | Resourc<br>e other<br>than the<br>above<br>selected | Setting<br>disabled         | Setting<br>disabled                                     | Setting<br>disabled                                     | Maintain<br>previous<br>state                                             | Maintain<br>previous<br>state                                             | Hi-Z /<br>Internal<br>input fixed                                         | selected /<br>Internal<br>input fixed<br>at 0                             | Hi-Z /<br>Internal<br>input fixed<br>at 0                                 | selected /<br>Internal<br>input fixed<br>at 0                             |

|                 | GPIO<br>selected                                    |                             |                                                         |                                                         |                                                                           |                                                                           | at 0                                                                      |                                                                           |                                                                           |                                                                           |

| M               | Mode<br>input pin                                   | Input<br>enabled            | Input<br>enabled                                        | Input<br>enabled                                        | Input<br>enabled                                                          | Input<br>enabled                                                          | Input<br>enabled                                                          | Input<br>enabled                                                          | Input<br>enabled                                                          | Input<br>enabled                                                          |

| IVI             | GPIO<br>selected                                    | Setting<br>disabled         | Setting<br>disabled                                     | Setting<br>disabled                                     | Maintain previous state                                                   | Maintain previous state                                                   | Hi-Z / Input<br>enabled                                                   | GPIO<br>selected                                                          | Hi-Z / Input<br>enabled                                                   | GPIO<br>selected                                                          |

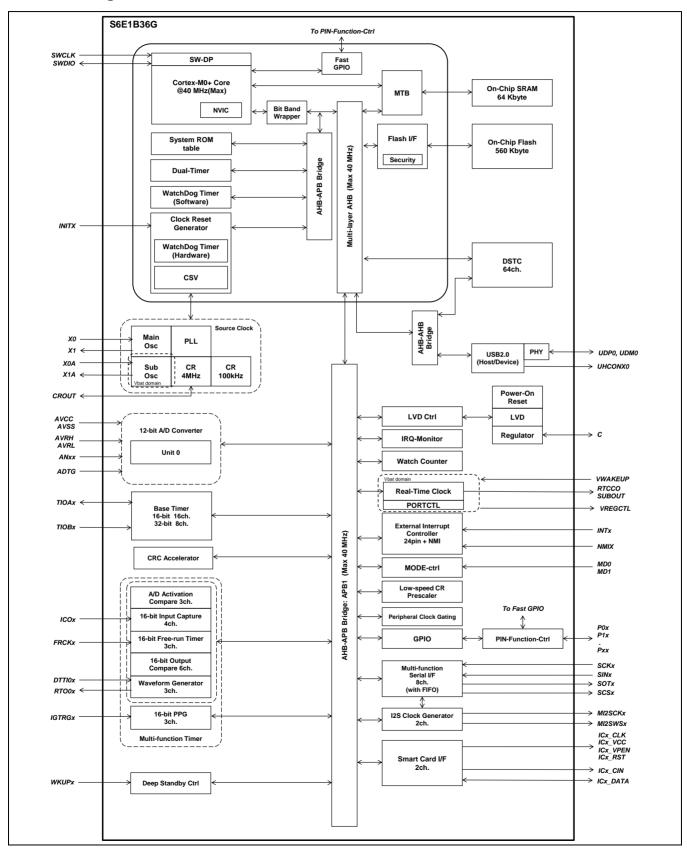

# 11.4.4 Operating Conditions of Main PLL (In the Case of Using the Main Clock as the Input Clock of the PLL)

$(V_{CC}=AV_{CC}=1.65 \text{ V to } 3.6 \text{ V}, V_{SS}=AV_{SS}=0 \text{ V}, T_{A}=-40 ^{\circ}\text{C to } +105 ^{\circ}\text{C})$

| Parameter                                                            | Symbol               | Value |     |      | Unit     | Remarks |

|----------------------------------------------------------------------|----------------------|-------|-----|------|----------|---------|

| r al allietei                                                        | Syllibol             | Min   | Тур | Max  | Oille    | Remarks |

| PLL oscillation stabilization wait time* <sup>1</sup> (LOCK UP time) | tLOCK                | 100   | -   | -    | μs       |         |

| PLL input clock frequency                                            | f <sub>PLLI</sub>    | 4     | -   | 16   | MHz      |         |

| PLL multiple rate                                                    | -                    | 5     | -   | 37   | multiple |         |

| PLL macro oscillation clock frequency                                | f <sub>PLLO</sub>    | 75    | -   | 150  | MHz      |         |

| Main PLL clock frequency*2                                           | f <sub>CLKPLL</sub>  | -     | -   | 40.8 | MHz      |         |

| USB clock frequency*3                                                | f <sub>CLKSPLL</sub> | -     | -   | 48   | MHz      |         |

<sup>\*1:</sup> The wait time is the time it takes for PLL oscillation to stabilize.

# 11.4.5 Operating Conditions of Main PLL (In the Case of Using the Built-in High-Speed CR Clock as the Input Clock of the Main PLL)

$(V_{CC}=AV_{CC}=1.65 \text{ V to } 3.6 \text{ V}, V_{SS}=AV_{SS}=0 \text{ V}, T_{A}=-40 ^{\circ}\text{C to } +105 ^{\circ}\text{C})$

| Parameter                                                            | Symbol              |     | Value |      | Unit     | Remarks |

|----------------------------------------------------------------------|---------------------|-----|-------|------|----------|---------|

| Farameter                                                            | Syllibol            | Min | Тур   | Max  | Onit     | Remarks |

| PLL oscillation stabilization wait time* <sup>1</sup> (LOCK UP time) | t <sub>LOCK</sub>   | 100 | -     | -    | μs       |         |

| PLL input clock frequency                                            | f <sub>PLLI</sub>   | 3.8 | 4     | 4.2  | MHz      |         |

| PLL multiple rate                                                    | -                   | 19  | -     | 35   | multiple |         |

| PLL macro oscillation clock frequency                                | f <sub>PLLO</sub>   | 72  | -     | 150  | MHz      |         |

| Main PLL clock frequency*2                                           | f <sub>CLKPLL</sub> | -   | -     | 40.8 | MHz      |         |

<sup>\*1:</sup> The wait time is the time it takes for PLL oscillation to stabilize.

#### Note:

For the main PLL source clock, input the high-speed CR clock (CLKHC) whose frequency has been trimmed.

When setting PLL multiple rate, please take the accuracy of the built-in High-speed CR clock into account and prevent the master clock from exceeding the maximum frequency.

<sup>\*2:</sup> For details of the main PLL clock (CLKPLL), refer to "Chapter: Clock" in "FM0+ Family Peripheral Manual".

<sup>\*3:</sup> For more information about USB clock, see "Chapter: USB Clock Generation" in "FM0+ Family Peripheral Manual Communication Macro Part".

<sup>\*2:</sup> For details of the main PLL clock (CLKPLL), refer to "Chapter: Clock" in "FM0+ Family Peripheral Manual".

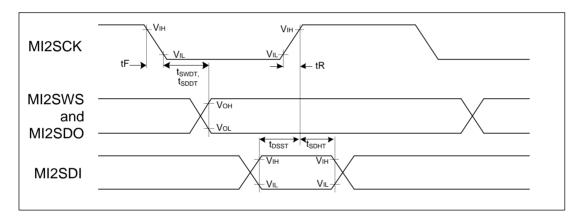

## 11.4.12 f<sup>2</sup>S Timing

$(V_{CC}=AV_{CC}=1.65 \text{ V to } 3.6 \text{ V}, V_{SS}=AV_{SS}=0 \text{ V}, T_{A}=-40 ^{\circ}\text{C to } +105 ^{\circ}\text{C})$

| Parameter                              | Symbol              | Pin Name    | Conditions            | V <sub>cc</sub> < 2 | 2.7 V | V <sub>cc</sub> ≥   | Unit  |       |

|----------------------------------------|---------------------|-------------|-----------------------|---------------------|-------|---------------------|-------|-------|

| Farameter                              | Syllibol            | FIII Naille | Conditions            | Min                 | Max   | Min                 | Max   | Ollit |

| MI2SCK max frequency (*1)              | F <sub>MI2SCK</sub> | MI2SCKx     |                       | -                   | 6.144 | ı                   | 6.144 | MHz   |

| I <sup>2</sup> S clock cycle time (*1) | t <sub>ICYC</sub>   | MI2SCKx     |                       | 4 t <sub>CYCP</sub> | -     | 4 t <sub>CYCP</sub> | ı     | ns    |

| I <sup>2</sup> S clock Duty cycle      | Δ                   | MI2SCKx     |                       | 45%                 | 55%   | 45%                 | 55%   |       |

| MI2SCK↓ → MI2SWS delay time            | 4                   | MI2SCKx,    |                       | -30                 | +30   | -20                 | +20   | no    |

| Wil25CK ↓ → Wil25W5 delay time         | tswdt               | MI2SWSx     |                       | -30                 | +30   | -20                 | +20   | ns    |

| MI2SCK↓ → MI2SDO delay time            | t                   | MI2SCKx,    |                       | -30                 | +30   | -20                 | +20   | ns    |

| Wil23CK ↓ → Wil23DO delay time         | t <sub>SDDT</sub>   | MI2SDOx     | C <sub>L</sub> =30 pF | -30                 | +30   | -20                 | +20   | 115   |

| MI2SDI → MI2SCK ↑ setup                | t <sub>DSST</sub>   | MI2SCKx,    |                       | 50                  | _     | 36                  | _     | ns    |

| time                                   | UDSST               | MI2SDIx     |                       | 50                  | -     | 30                  | •     | 115   |

| MI2SCK ↑ → MI2SDI hold time            | 4                   | MI2SCKx,    |                       | 0                   | _     | 0                   |       | no    |

| IVIIZOCK   7 IVIIZODI Hold tillle      | tsdht               | MI2SDIx     |                       | U                   | _     | U                   | •     | ns    |

| MI2SCK falling time                    | tF                  | MI2SCKx     |                       | -                   | 5     | -                   | 5     | ns    |

| MI2SCK rising time                     | tR                  | MI2SCKx     |                       | -                   | 5     |                     | 5     | ns    |

\*1:  $I^2S$  clock should meet the multiple of PCLK( $t_{ICYC}$ ) and the frequency less than  $F_{MI2SCK}$  meantime. The detail information please refer to Chapter  $I^2S$  of Communication Macro Part of Peripheral Manual.

## 11.4.13 Smart Card Interface Characteristics

(V<sub>CC</sub>=AV<sub>CC</sub>=1.65 V to 3.6 V, V<sub>SS</sub>=AV<sub>SS</sub>=0 V,  $T_A$ =- 40°C to +105°C)

| Parameter              | Symbol         | Pin Name  | Conditions            | Va  | lue | Unit | Remarks |

|------------------------|----------------|-----------|-----------------------|-----|-----|------|---------|

| Farameter              | Зуппоп         | Fili Name | Conditions            | Min | Max | Onit |         |

| Output vision stines   |                | ICx_VCC,  |                       | 4   | 00  | ns   |         |

| Output rising time     | t <sub>R</sub> | ICx_RST,  |                       | 4   | 20  |      |         |

| Output falling time    | 4              | ICx_CLK,  | C <sub>L</sub> =30 pF | 4   | 20  | 20   |         |

| Output falling time    | t <sub>F</sub> | ICx_DATA  | CL=30 pr              | 4   | 20  | ns   |         |

| Output clock frequency | $f_{CLK}$      | ICx CLK   |                       | ı   | 20  | MHz  |         |

| Duty cycle             | Δ              | ICX_CLK   |                       | 45% | 55% |      |         |

$<sup>\</sup>blacksquare$ External pull-up resistor (20 k $\Omega$  to 50 k $\Omega$ ) must be applied to ICx\_CIN pin when it's used as smart card reader function.

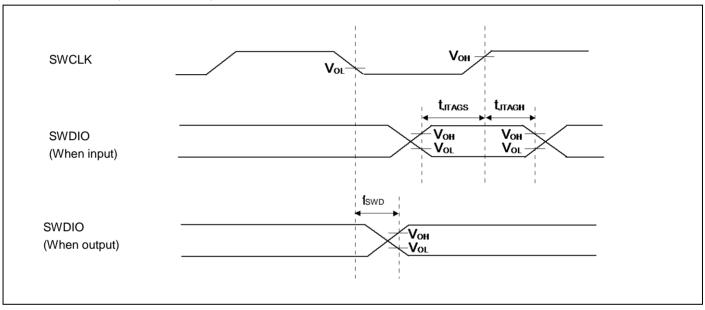

## 11.4.14 SW-DP Timing

(V<sub>CC</sub>=AV<sub>CC</sub>=1.65 V to 3.6 V, V<sub>SS</sub>=AV<sub>SS</sub>=0 V,  $T_A$ =- 40°C to +105°C)

| Barameter        | Parameter Symbol Pin Name Conditions Min |                 | Va  | lue | Unit | Remarks |  |

|------------------|------------------------------------------|-----------------|-----|-----|------|---------|--|

| Farameter        |                                          |                 | Min | Max | Oiii | Remarks |  |

| SWDIO setup time | t <sub>SWS</sub>                         | SWCLK,<br>SWDIO | -   | 15  | -    | ns      |  |

| SWDIO hold time  | t <sub>SWH</sub>                         | SWCLK,<br>SWDIO | -   | 15  |      | ns      |  |

| SWDIO delay time | t <sub>SWD</sub>                         | SWCLK,<br>SWDIO | -   | -   | 45   | ns      |  |

## Note:

## External load capacitance C<sub>L</sub>=30 pF

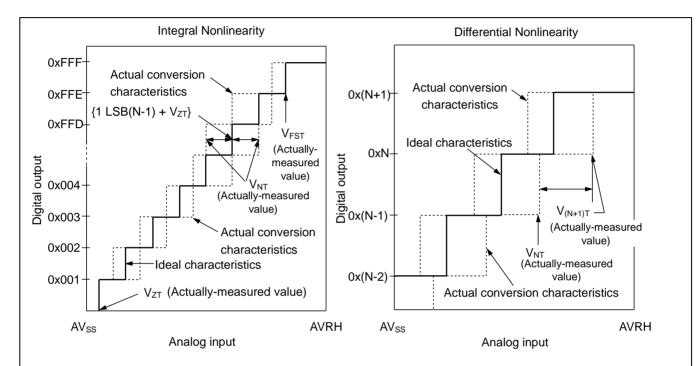

### **Definitions of 12-bit A/D Converter Terms**

■ Resolution: Analog variation that is recognized by an A/D converter.

- ■Integral Nonlinearity: Deviation of the line between the zero-transition point (0b000000000000 ←→ 0b00000000001) and the full-scale transition point (0b111111111110 ←→ 0b11111111111) from the actual conversion characteristics.

- Differential Nonlinearity: Deviation from the ideal value of the input voltage that is required to change the output code by 1 LSB.

Integral Nonlinearity of digital output N =

$$\frac{V_{NT} - \{1LSB \times (N-1) + V_{ZT}\}}{1LSB}$$

[LSB]

Differential Nonlinearity of digital output N =

$$\frac{V_{(N+1)T} - V_{NT}}{1LSB}$$

- 1 [LSB]

$$1LSB = \frac{V_{FST} - V_{ZT}}{4094}$$

N : A/D converter digital output value.

$V_{ZT}$  : Voltage at which the digital output changes from 0x000 to 0x001.  $V_{FST}$  : Voltage at which the digital output changes from 0xFFE to 0xFFF.  $V_{NT}$  : Voltage at which the digital output changes from 0x(N - 1) to 0xN.

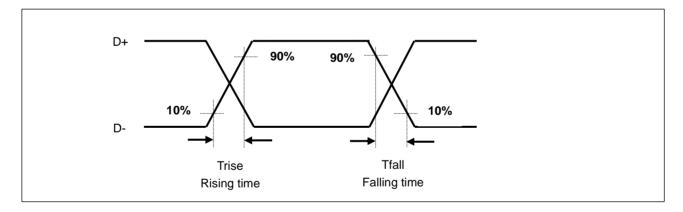

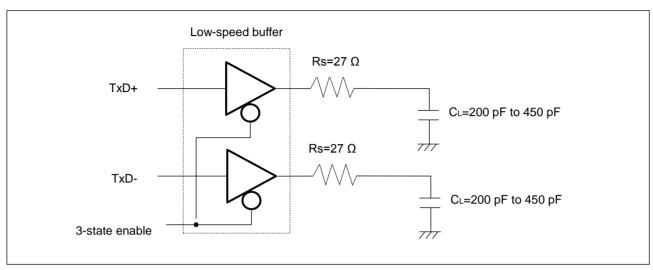

\*7: They indicate rising time (Trise) and falling time (Tfall) of the low-speed differential data signal. They are defined by the time between 10% and 90% of the output signal voltage.

See "Low-speed load (Compliance Load)" for condition of external load.

# · Low-Speed Load (Compliance Load)

# **Document History**

Document Title: S6E1B3 Series 32-bit ARM® Cortex®-M0+ FM0+ Microcontroller

Document Number: 001-99224

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change |

|----------|---------|--------------------|--------------------|-----------------------|

| **       | 4889752 | TEKA               | 08/31/2015         | New Spec.             |