Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 48 MIPS                                                         |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                          |

| Peripherals                | POR, PWM, WDT                                                   |

| Number of I/O              | 24                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | OTP                                                             |

| EEPROM Size                | -                                                               |

| RAM Size                   | 1.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                    |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 32-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 32-QFN (5x5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051t621-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

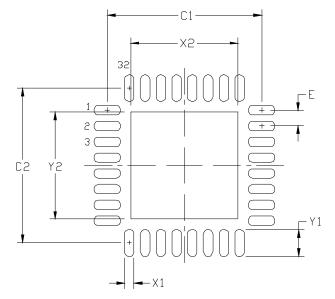

Figure 5.2. QFN-32 Recommended PCB Land Pattern

| Table 5.2. QFN-32 PCB La | and Pattern Dimensions |

|--------------------------|------------------------|

|--------------------------|------------------------|

| Dimension | Min      | Max  | ] | Dimension | Min  | Max  |

|-----------|----------|------|---|-----------|------|------|

| C1        | 4.80     | 4.90 |   | X2        | 3.20 | 3.40 |

| C2        | 4.80     | 4.90 |   | Y1        | 0.75 | 0.85 |

| E         | 0.50 BSC |      |   | Y2        | 3.20 | 3.40 |

| X1        | 0.20     | 0.30 |   |           |      |      |

| Notes:    |          | •    | • | •         |      |      |

General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

Solder Mask Design

**3.** All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

Stencil Design

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins.

- **7.** A 3x3 array of 1.0 mm openings on a 1.2 mm pitch should be used for the center pad to assure the proper paste volume.

Card Assembly

- 8. A No-Clean, Type-3 solder paste is recommended.

- **9.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

#### Table 7.13. Comparator Electrical Characteristics

$V_{DD}$  = 3.0 V, -40 to +85 °C unless otherwise noted.

| Parameters                                        | Test Condition          | Min   | Тур      | Max                    | Unit |

|---------------------------------------------------|-------------------------|-------|----------|------------------------|------|

| Response Time:                                    | CP0+ - CP0- = 100 mV    | —     | 240      | —                      | ns   |

| Mode 0, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV   | —     | 240      | —                      | ns   |

| Response Time:                                    | CP0+ - CP0- = 100 mV    | —     | 400      | —                      | ns   |

| Mode 1, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV   | _     | 400      | —                      | ns   |

| Response Time:                                    | CP0+ - CP0- = 100 mV    | _     | 650      | —                      | ns   |

| Mode 2, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV   | —     | 1100     | —                      | ns   |

| Response Time:                                    | CP0+ - CP0- = 100 mV    | —     | 2000     | —                      | ns   |

| Mode 3, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV   | —     | 5500     | —                      | ns   |

| Common-Mode Rejection Ratio                       |                         | —     | 1.0      | 4                      | mV/V |

| Positive Hysteresis 1                             | CP0HYP1-0 = 00          | —     | 0        | 1                      | mV   |

| Positive Hysteresis 2                             | CP0HYP1-0 = 01          | 2     | 5        | 8                      | mV   |

| Positive Hysteresis 3                             | CP0HYP1-0 = 10          | 6     | 10       | 14                     | mV   |

| Positive Hysteresis 4                             | CP0HYP1-0 = 11          | 12    | 20       | 28                     | mV   |

| Negative Hysteresis 1                             | CP0HYN1-0 = 00          |       | 0        | 1                      | mV   |

| Negative Hysteresis 2                             | CP0HYN1-0 = 01          | 2     | 5        | 8                      | mV   |

| Negative Hysteresis 3                             | CP0HYN1-0 = 10          | 6     | 10       | 14                     | mV   |

| Negative Hysteresis 4                             | CP0HYN1-0 = 11          | 12    | 20       | 28                     | mV   |

| Inverting or Non-Inverting Input<br>Voltage Range |                         | -0.25 | —        | V <sub>DD</sub> + 0.25 | V    |

| Input Capacitance                                 |                         | —     | 4        | —                      | pF   |

| Input Offset Voltage                              |                         | -7.5  |          | +7.5                   | mV   |

| Power Supply                                      |                         | -     | <u>+</u> |                        |      |

| Power Supply Rejection                            |                         | —     | 0.5      | —                      | mV/V |

| Power-up Time                                     |                         | _     | 10       | _                      | μs   |

| Supply Current at DC                              | Mode 0                  | —     | 26       | 50                     | μA   |

|                                                   | Mode 1                  | —     | 10       | 20                     | μA   |

|                                                   | Mode 2                  | —     | 3        | 6                      | μA   |

|                                                   | Mode 3                  | —     | 0.5      | 2                      | μA   |

| Note: Vcm is the common-mode vo                   | ltage on CP0+ and CP0–. | 1     | I        |                        |      |

## SFR Definition 11.1. REG01CN: Voltage Regulator Control

| Bit   | 7       | 6      | 5        | 4      | 3      | 2        | 1      | 0    |

|-------|---------|--------|----------|--------|--------|----------|--------|------|

| Name  | REG0DIS | VBSTAT | Reserved | REG0MD | STOPCF | Reserved | REG1MD | MPCE |

| Туре  | R/W     | R      | R/W      | R/W    | R/W    | R/W      | R/W    | R/W  |

| Reset | 0       | 0      | 0        | 0      | 0      | 0        | 0      | 0    |

#### SFR Address = 0xC9

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | REGODIS  | Voltage Regulator (REG0) Disable.<br>This bit enables or disables the REG0 Voltage Regulator.<br>0: Voltage Regulator Enabled.<br>1: Voltage Regulator Disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6   | VBSTAT   | <ul> <li>VBUS Signal Status.</li> <li>This bit indicates whether the device is connected to a USB network.</li> <li>0: VBUS signal currently absent (device not attached to USB network).</li> <li>1: VBUS signal currently present (device attached to USB network).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5   | Reserved | Must Write 0b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4   | REG0MD   | <ul> <li>Voltage Regulator (REG0) Mode Select.</li> <li>This bit selects the Voltage Regulator mode for REG0. When REG0MD is set to 1, the REG0 voltage regulator operates in lower power (suspend) mode.</li> <li>0: REG0 Voltage Regulator in normal mode.</li> <li>1: REG0 Voltage Regulator in low power mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3   | STOPCF   | <ul> <li>Stop Mode Configuration (REG1).</li> <li>This bit configures the REG1 regulator's behavior when the device enters STOP mode.</li> <li>0: REG1 Regulator is still active in STOP mode. Any enabled reset source will reset the device.</li> <li>1: REG1 Regulator is shut down in STOP mode. Only the RST pin or power cycle can reset the device.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2   | Reserved | Must Write 0b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1   | REG1MD   | <ul> <li>Voltage Regulator (REG1) Mode.</li> <li>This bit selects the Voltage Regulator mode for REG1. When REG1MD is set to 1, the REG1 voltage regulator operates in lower power mode.</li> <li>0: REG1 Voltage Regulator in normal mode.</li> <li>1: REG1 Voltage Regulator in low power mode.</li> <li>Note: This bit should not be set to '1' if the REG0 Voltage Regulator is disabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0   | MPCE     | <ul> <li>Memory Power Controller Enable.</li> <li>This bit can help the system save power at slower system clock frequencies (about 2.0 MHz or less) by automatically shutting down the EPROM memory between clocks when information is not being fetched from the EPROM memory. This bit has no effect when the prefetch engine is enabled.</li> <li>0: Normal Mode - Memory power controller disabled (EPROM memory is always on).</li> <li>1: Low Power Mode - Memory power controller enabled (EPROM turns on/off as needed).</li> <li>Note: If an external clock source is used with the Memory Power Controller enabled, and the clock frequency changes from slow (&lt; 2.0 MHz) to fast (&gt; 2.0 MHz), up to 20 clocks may be "skipped" to ensure that the EPROM power is stable before reading memory.</li> </ul> |

#### Table 16.2. Special Function Registers (Continued)

| Register | Address | Description                        | Page |

|----------|---------|------------------------------------|------|

| SBRLL1   | 0xB4    | UART1 Baud Rate Generator Low Byte | 232  |

| SBUF0    | 0x99    | UART0 Data Buffer                  | 221  |

| SBUF1    | 0xD3    | UART1 Data Buffer                  | 230  |

| SCON0    | 0x98    | UART0 Control                      | 220  |

| SCON1    | 0xD2    | UART1 Control                      | 228  |

| SMB0ADM  | 0xCF    | SMBus Slave Address Mask           | 205  |

| SMB0ADR  | 0xC7    | SMBus Slave Address                | 204  |

| SMB0CF   | 0xC1    | SMBus Configuration                | 200  |

| SMB0CN   | 0xC0    | SMBus Control                      | 202  |

| SMB0DAT  | 0xC2    | SMBus Data                         | 206  |

| SMOD1    | 0xE5    | UART1 Mode                         | 229  |

| SP       | 0x81    | Stack Pointer                      | 74   |

| SPI0CFG  | 0xA1    | SPI Configuration                  | 240  |

| SPIOCKR  | 0xA2    | SPI Clock Rate Control             | 242  |

| SPI0CN   | 0xF8    | SPI Control                        | 241  |

| SPI0DAT  | 0xA3    | SPI Data                           | 242  |

| TCON     | 0x88    | Timer/Counter Control              | 252  |

| TH0      | 0x8C    | Timer/Counter 0 High               | 255  |

| TH1      | 0x8D    | Timer/Counter 1 High               | 255  |

| TL0      | 0x8A    | Timer/Counter 0 Low                | 254  |

| TL1      | 0x8B    | Timer/Counter 1 Low                | 254  |

| TMOD     | 0x89    | Timer/Counter Mode                 | 253  |

| TMR2CN   | 0xC8    | Timer/Counter 2 Control            | 259  |

| TMR2H    | 0xCD    | Timer/Counter 2 High               | 261  |

| TMR2L    | 0xCC    | Timer/Counter 2 Low                | 260  |

| TMR2RLH  | 0xCB    | Timer/Counter 2 Reload High        | 260  |

| TMR2RLL  | 0xCA    | Timer/Counter 2 Reload Low         | 260  |

| TMR3CN   | 0x91    | Timer/Counter 3Control             | 265  |

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

## SFR Definition 17.5. EIE2: Extended Interrupt Enable 2

| Bit   | 7   | 6   | 5   | 4        | 3    | 2        | 1   | 0     |

|-------|-----|-----|-----|----------|------|----------|-----|-------|

| Name  |     |     |     | Reserved | EMAT | Reserved | ES1 | EVBUS |

| Туре  | R/W | R/W | R/W | R/W      | R/W  | R/W      | R/W | R/W   |

| Reset | 0   | 0   | 0   | 0        | 0    | 0        | 0   | 0     |

SFR Address = 0xE7

| Bit | Name     | Function                                                     |

|-----|----------|--------------------------------------------------------------|

| 7:3 | Unused   | Read = 0000b, Write = Don't Care.                            |

| 4   | Reserved | Must write 0b.                                               |

| 3   | EMAT     | Enable Port Match Interrupts.                                |

|     |          | This bit sets the masking of the Port Match Event interrupt. |

|     |          | 0: Disable all Port Match interrupts.                        |

|     |          | 1: Enable interrupt requests generated by a Port Match.      |

| 2   | Reserved | Must write 0b.                                               |

| 1   | ES1      | Enable UART1 Interrupt.                                      |

|     |          | This bit sets the masking of the UART1 interrupt.            |

|     |          | 0: Disable UART1 interrupt.                                  |

|     |          | 1: Enable UART1 interrupt.                                   |

| 0   | EVBUS    | Enable VBUS Level Interrupt.                                 |

|     |          | This bit sets the masking of the VBUS interrupt.             |

|     |          | 0: Disable all VBUS interrupts.                              |

|     |          | 1: Enable interrupt requests generated by VBUS level sense.  |

# SFR Definition 21.3. OSCICN: Internal H-F Oscillator Control

| Bit   | 7      | 6     | 5       | 4 | 3 | 2 | 1         | 0 |

|-------|--------|-------|---------|---|---|---|-----------|---|

| Name  | IOSCEN | IFRDY | SUSPEND |   |   |   | IFCN[1:0] |   |

| Туре  | R/W    | R     | R/W     | R | R | R | R/W       |   |

| Reset | 1      | 1     | 0       | 0 | 0 | 0 | 0         | 0 |

SFR Address = 0xB2

| Bit | Name      | Function                                                                                                                                                                            |

|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IOSCEN    | Internal H-F Oscillator Enable Bit.                                                                                                                                                 |

|     |           | 0: Internal H-F Oscillator Disabled.                                                                                                                                                |

|     |           | 1: Internal H-F Oscillator Enabled.                                                                                                                                                 |

| 6   | IFRDY     | Internal H-F Oscillator Frequency Ready Flag.                                                                                                                                       |

|     |           | 0: Internal H-F Oscillator is not running at programmed frequency.                                                                                                                  |

|     |           | 1: Internal H-F Oscillator is running at programmed frequency.                                                                                                                      |

| 5   | SUSPEND   | Internal Oscillator Suspend Enable Bit.                                                                                                                                             |

|     |           | Setting this bit to logic 1 places the internal oscillator in SUSPEND mode. The inter-<br>nal oscillator resumes operation when one of the SUSPEND mode awakening<br>events occurs. |

| 4:2 | Unused    | Read = 000b; Write = Don't Care                                                                                                                                                     |

| 1:0 | IFCN[1:0] | Internal H-F Oscillator Frequency Divider Control Bits.                                                                                                                             |

|     |           | The Internal H-F Oscillator is divided by the IFCN bit setting after a divide-by-4 stage.                                                                                           |

|     |           | 00: SYSCLK can be derived from Internal H-F Oscillator divided by 8 (1.5 MHz).                                                                                                      |

|     |           | 01: SYSCLK can be derived from Internal H-F Oscillator divided by 4 (3 MHz).                                                                                                        |

|     |           | 10: SYSCLK can be derived from Internal H-F Oscillator divided by 2 (6 MHz).                                                                                                        |

|     |           | 11: SYSCLK can be derived from Internal H-F Oscillator divided by 1 (12 MHz).                                                                                                       |

## SFR Definition 22.2. XBR1: Port I/O Crossbar Register 1

| Bit   | 7       | 6     | 5   | 4   | 3    | 2           | 1 | 0 |

|-------|---------|-------|-----|-----|------|-------------|---|---|

| Name  | WEAKPUD | XBARE | T1E | T0E | ECIE | PCA0ME[2:0] |   |   |

| Туре  | R/W     | R/W   | R/W | R/W | R/W  | R/W         |   |   |

| Reset | 0       | 0     | 0   | 0   | 0    | 0           | 0 | 0 |

SFR Address = 0xE2

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | WEAKPUD     | <ul> <li>Port I/O Weak Pullup Disable.</li> <li>0: Weak Pullups enabled (except for Ports whose I/O are configured for analog mode).</li> <li>1: Weak Pullups disabled.</li> </ul>                                                                                                                                                                                                                 |

| 6   | XBARE       | Crossbar Enable.<br>0: Crossbar disabled.<br>1: Crossbar enabled.                                                                                                                                                                                                                                                                                                                                  |

| 5   | T1E         | <b>T1 Enable.</b><br>0: T1 unavailable at Port pin.<br>1: T1 routed to Port pin.                                                                                                                                                                                                                                                                                                                   |

| 4   | TOE         | <b>T0 Enable.</b><br>0: T0 unavailable at Port pin.<br>1: T0 routed to Port pin.                                                                                                                                                                                                                                                                                                                   |

| 3   | ECIE        | PCA0 External Counter Input Enable.<br>0: ECI unavailable at Port pin.<br>1: ECI routed to Port pin.                                                                                                                                                                                                                                                                                               |

| 2:0 | PCA0ME[2:0] | <ul> <li>PCA Module I/O Enable Bits.</li> <li>000: All PCA I/O unavailable at Port pins.</li> <li>001: CEX0 routed to Port pin.</li> <li>010: CEX0, CEX1 routed to Port pins.</li> <li>011: CEX0, CEX1, CEX2 routed to Port pins.</li> <li>100: CEX0, CEX1, CEX2, CEX3 routed to Port pins.</li> <li>101: CEX0, CEX1, CEX2, CEX3, CEX4 routed to Port pins.</li> <li>110-111: Reserved.</li> </ul> |

## SFR Definition 22.6. P1MASK: Port 1 Mask Register

| Bit   | 7           | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|-----------------|---|---|---|---|---|---|

| Name  | P1MASK[7:0] |                 |   |   |   |   |   |   |

| Туре  |             | R/W             |   |   |   |   |   |   |

| Reset | 0           | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |

SFR Address = 0xBA

| Bit | Name        | Function                                                                                                                                                                                            |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MASK[7:0] | Port 1 Mask Value.                                                                                                                                                                                  |

|     |             | Selects P1 pins to be compared to the corresponding bits in P1MAT.<br>0: P1.n pin logic value is ignored and cannot cause a Port Mismatch event.<br>1: P1.n pin logic value is compared to P1MAT.n. |

### SFR Definition 22.7. P1MAT: Port 1 Match Register

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|------------|---|---|---|---|---|---|

| Name  |   | P1MAT[7:0] |   |   |   |   |   |   |

| Туре  |   | R/W        |   |   |   |   |   |   |

| Reset | 1 | 1          | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Address = 0xB6

| Bit | Name       | Function                                                                                                                                                                                    |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MAT[7:0] | Port 1 Match Value.                                                                                                                                                                         |

|     |            | Match comparison value used on Port 1 for bits in P1MASK which are set to 1.<br>0: P1.n pin logic value is compared with logic LOW.<br>1: P1.n pin logic value is compared with logic HIGH. |

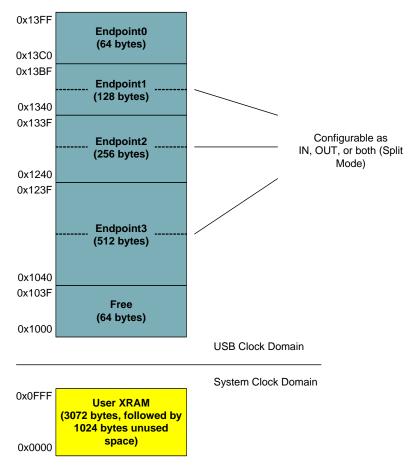

Figure 23.4. C8051T626/7 USB FIFO Allocation

#### 23.5.1. FIFO Split Mode

The FIFO space for Endpoints1-3 can be split such that the upper half of the FIFO space is used by the IN endpoint, and the lower half is used by the OUT endpoint. For example: if the Endpoint3 FIFO is configured for Split Mode, the upper 256 bytes (0x0540 to 0x063F) are used by Endpoint3 IN and the lower 256 bytes (0x0440 to 0x053F) are used by Endpoint3 OUT.

If an endpoint FIFO is not configured for split mode, that endpoint IN/OUT pair's FIFOs are combined to form a single IN *or* OUT FIFO. In this case only one direction of the endpoint IN/OUT pair may be used at a time. The endpoint direction (IN/OUT) is determined by the DIRSEL bit in the corresponding endpoint's EINCSRH register (see SFR Definition 23.13).

#### 23.5.2. FIFO Double Buffering

FIFO slots for Endpoints1-3 can be configured for double-buffered mode. In this mode, the maximum packet size is halved and the FIFO may contain two packets at a time. This mode is available for Endpoints1-3. When an endpoint is configured for split mode, double buffering may be enabled for the IN Endpoint and/or the OUT endpoint. When split mode is not enabled, double-buffering may be enabled for the entire endpoint FIFO. See Table 23.3 for a list of maximum packet sizes for each FIFO configuration.

5. Hardware sets the SUEND bit (E0CSR.4) because a control transfer ended before firmware sets the DATAEND bit (E0CSR.3).

The E0CNT register (USB Register Definition 23.11) holds the number of received data bytes in the Endpoint0 FIFO.

Hardware will automatically detect protocol errors and send a STALL condition in response. Firmware may force a STALL condition to abort the current transfer. When a STALL condition is generated, the STSTL bit will be set to 1 and an interrupt generated. The following conditions will cause hardware to generate a STALL condition:

- 1. The host sends an OUT token during a OUT data phase after the DATAEND bit has been set to 1.

- 2. The host sends an IN token during an IN data phase after the DATAEND bit has been set to 1.

- 3. The host sends a packet that exceeds the maximum packet size for Endpoint0.

- 4. The host sends a non-zero length DATA1 packet during the status phase of an IN transaction.

Firmware sets the SDSTL bit (E0CSR.5) to 1.

#### 23.10.1. Endpoint0 SETUP Transactions

All control transfers must begin with a SETUP packet. SETUP packets are similar to OUT packets, containing an 8-byte data field sent by the host. Any SETUP packet containing a command field of anything other than 8 bytes will be automatically rejected by USB0. An Endpoint0 interrupt is generated when the data from a SETUP packet is loaded into the Endpoint0 FIFO. Software should unload the command from the Endpoint0 FIFO, decode the command, perform any necessary tasks, and set the SOPRDY bit to indicate that it has serviced the OUT packet.

#### 23.10.2. Endpoint0 IN Transactions

When a SETUP request is received that requires USB0 to transmit data to the host, one or more IN requests will be sent by the host. For the first IN transaction, firmware should load an IN packet into the Endpoint0 FIFO, and set the INPRDY bit (E0CSR.1). An interrupt will be generated when an IN packet is transmitted successfully. Note that no interrupt will be generated if an IN request is received before firmware has loaded a packet into the Endpoint0 FIFO. If the requested data exceeds the maximum packet size for Endpoint0 (as reported to the host), the data should be split into multiple packets; each packet should be of the maximum packet size excluding the last (residual) packet. If the requested data is an integer multiple of the maximum packet size for Endpoint0, the last data packet should be a zero-length packet signaling the end of the transfer. Firmware should set the DATAEND bit to 1 after loading into the Endpoint0 FIFO the last data packet for a transfer.

Upon reception of the first IN token for a particular control transfer, Endpoint0 is said to be in Transmit Mode. In this mode, only IN tokens should be sent by the host to Endpoint0. The SUEND bit (E0CSR.4) is set to 1 if a SETUP or OUT token is received while Endpoint0 is in Transmit Mode.

Endpoint0 will remain in Transmit Mode until any of the following occur:

- 1. USB0 receives an Endpoint0 SETUP or OUT token.

- 2. Firmware sends a packet less than the maximum Endpoint0 packet size.

- 3. Firmware sends a zero-length packet.

Firmware should set the DATAEND bit (E0CSR.3) to 1 when performing (2) and (3) above.

The SIE will transmit a NAK in response to an IN token if there is no packet ready in the IN FIFO (INPRDY = 0).

# USB Register Definition 23.25. EOUTCNTH: USB0 OUT Endpoint Count High

| Bit                         | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0      |

|-----------------------------|---|---|---|---|---|---|------|--------|

| Name                        |   |   |   |   |   |   | EOCH | H[1:0] |

| Туре                        | R | R | R | R | R | R | R    | R      |

| Reset                       | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0      |

| USB Register Address = 0x17 |   |   |   |   |   |   |      |        |

| Bit | Name      | Function                                                                                                                                                                |

|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused    | Read = 000000b. Write = don't care.                                                                                                                                     |

| 1:0 | EOCH[1:0] | OUT Endpoint Count High Byte.                                                                                                                                           |

|     |           | EOCH holds the upper 2-bits of the 10-bit number of data bytes in the last received packet in the current OUT endpoint FIFO. This number is only valid while OPRDY = 1. |

overflow after 25 ms (and SMBTOE set), the Timer 3 interrupt service routine can be used to reset (disable and re-enable) the SMBus in the event of an SCL low timeout.

#### 24.3.5. SCL High (SMBus Free) Timeout

The SMBus specification stipulates that if the SCL and SDA lines remain high for more that 50  $\mu$ s, the bus is designated as free. When the SMBFTE bit in SMB0CF is set, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods (as defined by the timer configured for the SMBus clock source). If the SMBus is waiting to generate a Master START, the START will be generated following this timeout. A clock source is required for free timeout detection, even in a slave-only implementation.

#### 24.4. Using the SMBus

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting control for serial transfers; higher level protocol is determined by user software. The SMBus interface provides the following application-independent features:

- Byte-wise serial data transfers

- Clock signal generation on SCL (Master Mode only) and SDA data synchronization

- Timeout/bus error recognition, as defined by the SMB0CF configuration register

- START/STOP timing, detection, and generation

- Bus arbitration

- Interrupt generation

- Status information

- Optional hardware recognition of slave address and automatic acknowledgement of address/data

SMBus interrupts are generated for each data byte or slave address that is transferred. When hardware acknowledgement is disabled, the point at which the interrupt is generated depends on whether the hardware is acting as a data transmitter or receiver. When a transmitter (i.e., sending address/data, receiving an ACK), this interrupt is generated after the ACK cycle so that software may read the received ACK value; when receiving data (i.e., receiving address/data, sending an ACK), this interrupt is generated before the ACK cycle so that software may define the outgoing ACK value. If hardware acknowledgement is enabled, these interrupts are always generated after the ACK cycle. See Section 24.5 for more details on transmission sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control register) to find the cause of the SMBus interrupt. The SMB0CN register is described in Section 24.4.2; Table 24.5 provides a quick SMB0CN decoding reference.

#### 24.4.1. SMBus Configuration Register

The SMBus Configuration register (SMB0CF) is used to enable the SMBus Master and/or Slave modes, select the SMBus clock source, and select the SMBus timing and timeout options. When the ENSMB bit is set, the SMBus is enabled for all master and slave events. Slave events may be disabled by setting the INH bit. With slave events inhibited, the SMBus interface will still monitor the SCL and SDA pins; however, the interface will NACK all received addresses and will not generate any slave interrupts. When the INH bit is set, all slave events will be inhibited following the next START (interrupts will continue for the duration of the current transfer).

In this case, either a 1 or a 0 value are acceptable on the incoming slave address. Additionally, if the GC bit in register SMB0ADR is set to 1, hardware will recognize the General Call Address (0x00). Table 24.4 shows some example parameter settings and the slave addresses that will be recognized by hardware under those conditions.

| Hardware Slave Address<br>SLV[6:0] | Slave Address Mask<br>SLVM[6:0] | GC bit | Slave Addresses Recognized by Hardware |

|------------------------------------|---------------------------------|--------|----------------------------------------|

| 0x34                               | 0x7F                            | 0      | 0x34                                   |

| 0x34                               | 0x7F                            | 1      | 0x34, 0x00 (General Call)              |

| 0x34                               | 0x7E                            | 0      | 0x34, 0x35                             |

| 0x34                               | 0x7E                            | 1      | 0x34, 0x35, 0x00 (General Call)        |

| 0x70                               | 0x73                            | 0      | 0x70, 0x74, 0x78, 0x7C                 |

Table 24.4. Hardware Address Recognition Examples (EHACK = 1)

### SFR Definition 24.3. SMB0ADR: SMBus Slave Address

| Bit   | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-------|----------|---|---|---|---|---|---|-----|

| Name  | SLV[6:0] |   |   |   |   |   |   | GC  |

| Туре  | R/W      |   |   |   |   |   |   | R/W |

| Reset | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

#### SFR Address = 0xC7

| Bit | Name     | Function                                                                                                                                                                                                                                                                   |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLV[6:0] | SMBus Hardware Slave Address.                                                                                                                                                                                                                                              |

|     |          | Defines the SMBus Slave Address(es) for automatic hardware acknowledgement.<br>Only address bits which have a 1 in the corresponding bit position in SLVM[6:0]<br>are checked against the incoming address. This allows multiple addresses to be<br>recognized.            |

| 0   | GC       | General Call Address Enable.                                                                                                                                                                                                                                               |

|     |          | <ul> <li>When hardware address recognition is enabled (EHACK = 1), this bit will determine whether the General Call Address (0x00) is also recognized by hardware.</li> <li>0: General Call Address is ignored.</li> <li>1: General Call Address is recognized.</li> </ul> |

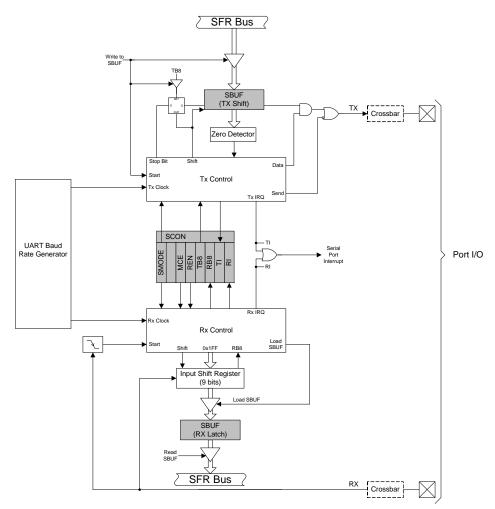

# 25. UART0

UART0 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates (details in Section "25.1. Enhanced Baud Rate Generation" on page 216). Received data buffering allows UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte.

UART0 has two associated SFRs: Serial Control Register 0 (SCON0) and Serial Data Buffer 0 (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. Writes to SBUF0 always access the Transmit register. Reads of SBUF0 always access the buffered Receive register; it is not possible to read data from the Transmit register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI0 is set in SCON0), or a data byte has been received (RI0 is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete).

Figure 25.1. UART0 Block Diagram

## 27.1. Signal Descriptions

The four signals used by SPI0 (MOSI, MISO, SCK, NSS) are described below.

#### 27.1.1. Master Out, Slave In (MOSI)

The master-out, slave-in (MOSI) signal is an output from a master device and an input to slave devices. It is used to serially transfer data from the master to the slave. This signal is an output when SPI0 is operating as a master and an input when SPI0 is operating as a slave. Data is transferred most-significant bit first. When configured as a master, MOSI is driven by the MSB of the shift register in both 3- and 4-wire mode.

#### 27.1.2. Master In, Slave Out (MISO)

The master-in, slave-out (MISO) signal is an output from a slave device and an input to the master device. It is used to serially transfer data from the slave to the master. This signal is an input when SPI0 is operating as a master and an output when SPI0 is operating as a slave. Data is transferred most-significant bit first. The MISO pin is placed in a high-impedance state when the SPI module is disabled and when the SPI operates in 4-wire mode as a slave that is not selected. When acting as a slave in 3-wire mode, MISO is always driven by the MSB of the shift register.

#### 27.1.3. Serial Clock (SCK)

The serial clock (SCK) signal is an output from the master device and an input to slave devices. It is used to synchronize the transfer of data between the master and slave on the MOSI and MISO lines. SPI0 generates this signal when operating as a master. The SCK signal is ignored by a SPI slave when the slave is not selected (NSS = 1) in 4-wire slave mode.

#### 27.1.4. Slave Select (NSS)

The function of the slave-select (NSS) signal is dependent on the setting of the NSSMD1 and NSSMD0 bits in the SPI0CN register. There are three possible modes that can be selected with these bits:

- 1. NSSMD[1:0] = 00: 3-Wire Master or 3-Wire Slave Mode: SPI0 operates in 3-wire mode, and NSS is disabled. When operating as a slave device, SPI0 is always selected in 3-wire mode. Since no select signal is present, SPI0 must be the only slave on the bus in 3-wire mode. This is intended for point-to-point communication between a master and one slave.

- NSSMD[1:0] = 01: 4-Wire Slave or Multi-Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an input. When operating as a slave, NSS selects the SPI0 device. When operating as a master, a 1-to-0 transition of the NSS signal disables the master function of SPI0 so that multiple master devices can be used on the same SPI bus.

- 3. NSSMD[1:0] = 1x: 4-Wire Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an output. The setting of NSSMD0 determines what logic level the NSS pin will output. This configuration should only be used when operating SPI0 as a master device.

See Figure 27.2, Figure 27.3, and Figure 27.4 for typical connection diagrams of the various operational modes. **Note that the setting of NSSMD bits affects the pinout of the device.** When in 3-wire master or 3-wire slave mode, the NSS pin will not be mapped by the crossbar. In all other modes, the NSS signal will be mapped to a pin on the device. See Section "22. Port Input/Output" on page 138 for general purpose port I/O and crossbar information.

# SFR Definition 28.3. TMOD: Timer Mode

| Bit   | 7     | 6    | 5        | 4 | 3     | 2    | 1        | 0 |

|-------|-------|------|----------|---|-------|------|----------|---|

| Name  | GATE1 | C/T1 | T1M[1:0] |   | GATE0 | C/T0 | T0M[1:0] |   |

| Туре  | R/W   | R/W  | R/W      |   | R/W   | R/W  | R/W      |   |

| Reset | 0     | 0    | 0        | 0 | 0     | 0    | 0        | 0 |

#### SFR Address = 0x89

| Bit | Name     | Function                                                                                                                                                                                                                     |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | GATE1    | Timer 1 Gate Control.                                                                                                                                                                                                        |

|     |          | 0: Timer 1 enabled when TR1 = 1 irrespective of $\overline{INT1}$ logic level.<br>1: Timer 1 enabled only when TR1 = 1 AND $\overline{INT1}$ is active as defined by bit IN1PL in register IT01CF (see SFR Definition 17.7). |

| 6   | C/T1     | Counter/Timer 1 Select.                                                                                                                                                                                                      |

|     |          | <ul><li>0: Timer: Timer 1 incremented by clock defined by T1M bit in register CKCON.</li><li>1: Counter: Timer 1 incremented by high-to-low transitions on external pin (T1).</li></ul>                                      |

| 5:4 | T1M[1:0] | Timer 1 Mode Select.                                                                                                                                                                                                         |

|     |          | These bits select the Timer 1 operation mode.                                                                                                                                                                                |

|     |          | 00: Mode 0, 13-bit Counter/Timer                                                                                                                                                                                             |

|     |          | 01: Mode 1, 16-bit Counter/Timer                                                                                                                                                                                             |

|     |          | 10: Mode 2, 8-bit Counter/Timer with Auto-Reload                                                                                                                                                                             |

|     |          | 11: Mode 3, Timer 1 Inactive                                                                                                                                                                                                 |

| 3   | GATE0    | Timer 0 Gate Control.                                                                                                                                                                                                        |

|     |          | 0: Timer 0 enabled when TR0 = 1 irrespective of INT0 logic level.<br>1: Timer 0 enabled only when TR0 = 1 AND $\overline{INT0}$ is active as defined by bit IN0PL in register IT01CF (see SFR Definition 17.7).              |

| 2   | C/T0     | Counter/Timer 0 Select.                                                                                                                                                                                                      |

|     |          | <ul><li>0: Timer: Timer 0 incremented by clock defined by T0M bit in register CKCON.</li><li>1: Counter: Timer 0 incremented by high-to-low transitions on external pin (T0).</li></ul>                                      |

| 1:0 | T0M[1:0] | Timer 0 Mode Select.                                                                                                                                                                                                         |

|     |          | These bits select the Timer 0 operation mode.                                                                                                                                                                                |

|     |          | 00: Mode 0, 13-bit Counter/Timer                                                                                                                                                                                             |

|     |          | 01: Mode 1, 16-bit Counter/Timer                                                                                                                                                                                             |

|     |          | 10: Mode 2, 8-bit Counter/Timer with Auto-Reload                                                                                                                                                                             |

|     |          | 11: Mode 3, Two 8-bit Counter/Timers                                                                                                                                                                                         |

#### 28.2.2. 8-bit Timers with Auto-Reload

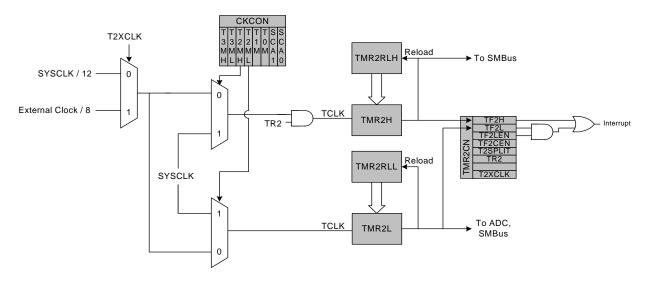

When T2SPLIT is set, Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 28.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control for TMR2H. TMR2L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bit (T2XCLK in TMR2CN), as follows:

| T2MH | T2XCLK | TMR2H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

| T2ML | T2XCLK | TMR2L Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled (IE.5), an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 28.5. Timer 2 8-Bit Mode Block Diagram

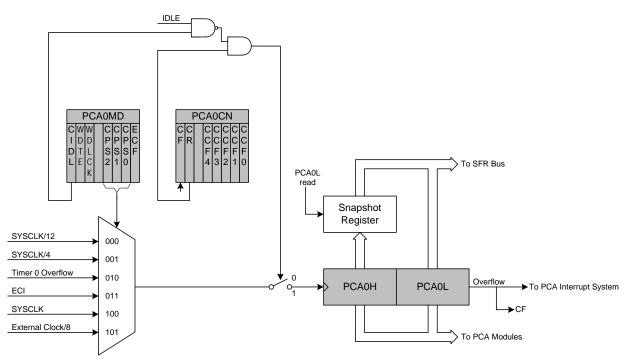

Figure 29.2. PCA Counter/Timer Block Diagram

### 29.2. PCA0 Interrupt Sources

Figure 29.3 shows a diagram of the PCA interrupt tree. There are five independent event flags that can be used to generate a PCA0 interrupt. They are: the main PCA counter overflow flag (CF), which is set upon a 16-bit overflow of the PCA0 counter, an intermediate overflow flag (COVF), which can be set on an overflow from the 8th, 9th, 10th, or 11th bit of the PCA0 counter, and the individual flags for each PCA channel (CCF0, CCF1, CCF2, CCF3, and CCF4), which are set according to the operation mode of that module. These event flags are always set when the trigger condition occurs. Each of these flags can be individually selected to generate a PCA0 interrupt, using the corresponding interrupt enable flag (ECF for CF, ECOV for COVF, and ECCFn for each CCFn). PCA0 interrupts must be globally enabled before any individual interrupt sources are recognized by the processor. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1.

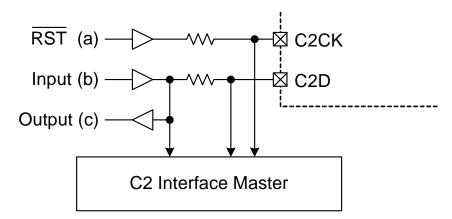

### 30.2. C2 Pin Sharing

The C2 protocol allows the C2 pins to be shared with user functions so that in-system debugging and EPROM programming functions may be performed. This is possible because C2 communication is typically performed when the device is in the halt state, where all on-chip peripherals and user software are stalled. In this halted state, the C2 interface can safely 'borrow' the C2CK (normally RST) and C2D pins. In most applications, external resistors are required to isolate C2 interface traffic from the user application when performing debug functions. These external resistors are not necessary for production boards. A typical isolation configuration is shown in Figure 30.1.

Figure 30.1. Typical C2 Pin Sharing

The configuration in Figure 30.1 assumes the following:

1. The user input (b) cannot change state while the target device is halted.

2. The  $\overline{RST}$  pin on the target device is used as an input only.

Additional resistors may be necessary depending on the specific application.

# DOCUMENT CHANGE LIST

## **Revision 0.1 to Revision 1.0**

• Updated "Electrical Characteristics" on page 34.

## **Revision 1.0 to Revision 1.1**

- Updated reset values for POWER, EMI0CF, VDM0CN, AMX0P, CPT0MX, and CPT1MX SFRs.

- Updated Figure 21.1 on page 127.

## **Revision 1.1 to Revision 1.2**

- Added C8051T626/7 part numbers and added details about these devices throughout the document.

- Updated maximum memory options on Page 1 and in Section "1. System Overview" on page 15.

- Added C8051T626/7 ordering part numbers to Table 2.1 on page 21 along with a note about the new part numbering scheme.

- Added electrical specifications for the new part numbers C8051T626/7 wherever they differed from the specifications for the rest of the part numbers.

- Table 7.2, "Global Electrical Characteristics," on page 35 Digital Supply Current (USB Suspend Mode).

- Table 7.5, "Internal Voltage Regulator Electrical Characteristics," on page 37 Bias Current (REG1).

- Table 7.7, "Internal High-Frequency Oscillator Electrical Characteristics," on page 38 Internal Oscillator Supply Current.

- Table 7.8, "Internal Low-Frequency Oscillator Electrical Characteristics," on page 39 Internal Oscillator Supply Current.

- Table 7.10, "ADC0 Electrical Characteristics," on page 40 Power Supply Current.

- Table 7.11, "Temperature Sensor Electrical Characteristics," on page 41 Slope and Offset.

- Updated Section "15. Memory Organization" on page 87 and Section "23. Universal Serial Bus Controller (USB0)" on page 160 to describe the additional memory on the new part numbers (C8051T626/7).

- Expanded PGSEL field from 3 bits to 5 bits in SFR Definition 15.1 "EMI0CN: External Memory Interface Control" on page 91 to support additional XRAM available on C8051T626/7 devices.

- Updated Table 17.1, "Interrupt Summary," on page 103 to indicate that interrupt position #19 is reserved.

- Updated SFR Definition 17.5 "EIE2: Extended Interrupt Enable 2" on page 108 and SFR Definition 17.6 "EIP2: Extended Interrupt Priority 2" on page 109 to indicate that bit 4 is reserved and requires 0b writes to this bit position.

- Updated SFR Definition 22.3 "XBR2: Port I/O Crossbar Register 2" on page 149 to indicate that bit 1 is reserved and requires 0b writes to this bit position.