Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                         |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 48 MIPS                                                          |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                           |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                       |

| Number of I/O              | 24                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                   |

| Program Memory Type        | OTP                                                              |

| EEPROM Size                | -                                                                |

| RAM Size                   | 3.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                     |

| Data Converters            | A/D 21x10b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 32-VFQFN Exposed Pad                                             |

| Supplier Device Package    | 32-QFN (5x5)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051t626-b-gm |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

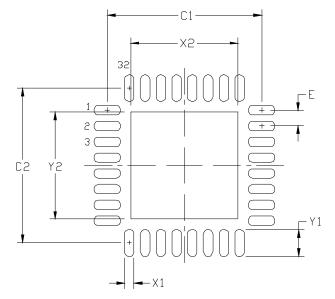

Figure 5.2. QFN-32 Recommended PCB Land Pattern

| Table 5.2. QFN-32 PCB La | and Pattern Dimensions |

|--------------------------|------------------------|

|--------------------------|------------------------|

| Dimension | Min      | Max  | ] | Dimension | Min  | Max  |

|-----------|----------|------|---|-----------|------|------|

| C1        | 4.80     | 4.90 |   | X2        | 3.20 | 3.40 |

| C2        | 4.80     | 4.90 |   | Y1        | 0.75 | 0.85 |

| E         | 0.50 BSC |      |   | Y2        | 3.20 | 3.40 |

| X1        | 0.20     | 0.30 |   |           |      |      |

| Notes:    |          | •    | • | •         |      |      |

General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

Solder Mask Design

**3.** All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

Stencil Design

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins.

- **7.** A 3x3 array of 1.0 mm openings on a 1.2 mm pitch should be used for the center pad to assure the proper paste volume.

Card Assembly

- 8. A No-Clean, Type-3 solder paste is recommended.

- **9.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

## SFR Definition 10.1. REF0CN: Reference Control

| Bit      | 7                | 6                                                                                       | 5                                    | 4              | 3             | 2             | 1               | 0            |  |

|----------|------------------|-----------------------------------------------------------------------------------------|--------------------------------------|----------------|---------------|---------------|-----------------|--------------|--|

| Nam      | e REFBG          | S                                                                                       |                                      | REGOVR         | REFSL         | TEMPE         | BIASE           | REFBE        |  |

| Тур      | e R/W            | R                                                                                       | R                                    | R/W            | R/W           | R/W           | R/W             | R/W          |  |

| Rese     | et 0             | 0                                                                                       | 0                                    | 0              | 0             | 0             | 0               | 0            |  |

| SFR A    | Address = 0      | xD1                                                                                     | I                                    |                |               | L             | I               | 11           |  |

| Bit      | Name             |                                                                                         |                                      |                | Function      |               |                 |              |  |

| 7        | REFBGS           | Reference Bu                                                                            | uffer Gain S                         | elect.         |               |               |                 |              |  |

|          |                  | This bit select                                                                         | s between 1                          | x and 2x gai   | n for the on- | chip voltage  | reference bu    | uffer.       |  |

|          |                  | 0: 2x Gain                                                                              |                                      |                |               |               |                 |              |  |

|          |                  | 1: 1x Gain                                                                              |                                      |                |               |               |                 |              |  |

| 6:5<br>4 | Unused<br>REGOVR | Read = 00b; V                                                                           |                                      |                |               |               |                 |              |  |

| 4        | REGOVR           | riogulator rio                                                                          |                                      |                |               |               |                 |              |  |

|          |                  | This bit "overr<br>erence source                                                        |                                      | FSL bit, and   | allows the l  | nternal regul | ator to be us   | ed as a ret- |  |

|          |                  | 0: The voltage                                                                          |                                      | source is sele | ected by the  | REFSL bit.    |                 |              |  |

|          |                  | 1: The interna                                                                          | l regulator is                       | s used as the  | voltage refe  | erence.       |                 |              |  |

| 3        | REFSL            | Voltage Refer                                                                           | ence Selec                           | t.             |               |               |                 |              |  |

|          |                  | This bit select                                                                         |                                      |                |               |               |                 |              |  |

|          |                  | 0: V <sub>REF</sub> pin us                                                              | -                                    |                |               |               |                 |              |  |

|          |                  | 1: V <sub>DD</sub> used a                                                               | -                                    |                |               |               |                 |              |  |

| 2        | TEMPE            | Temperature                                                                             |                                      |                |               |               |                 |              |  |

|          |                  | 0: Internal Ter                                                                         | •                                    |                |               |               |                 |              |  |

| 1        | BIASE            | 1: Internal Ter                                                                         | •                                    |                |               |               |                 |              |  |

| 1        | DIASE            | Internal Analog Bias Generator Enable Bit.                                              |                                      |                |               |               |                 |              |  |

|          |                  | 0: Internal Bias Generator off.<br>1: Internal Bias Generator on.                       |                                      |                |               |               |                 |              |  |

| 0        | REFBE            |                                                                                         | On-chip Reference Buffer Enable Bit. |                |               |               |                 |              |  |

| Ĭ        |                  | 0: On-chip Reie                                                                         |                                      |                | L.            |               |                 |              |  |

|          |                  | •                                                                                       |                                      |                | al voltage re | ference drive | en on the $V_R$ | FF pin.      |  |

|          |                  | 1: On-chip Reference Buffer on. Internal voltage reference driven on the $V_{REF}$ pin. |                                      |                |               |               |                 |              |  |

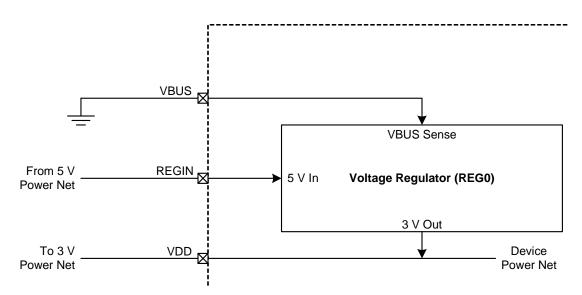

Figure 11.4. REG0 Configuration: No USB Connection

## 13. Prefetch Engine

The C8051T620/1/6/7 & C8051T320/1/2/3 family of devices incorporate a 2-byte prefetch engine. Because the access time of the EPROM memory is 40 ns, and the minimum instruction time is roughly 20 ns, the prefetch engine is necessary for full-speed code execution. Instructions are read from EPROM memory two bytes at a time by the prefetch engine and given to the CIP-51 processor core to execute. When running linear code (code without any jumps or branches), the prefetch engine allows instructions to be executed at full speed. When a code branch occurs, the processor may be stalled for up to two clock cycles while the next set of code bytes is retrieved from EPROM memory.

Note: The prefetch engine should be disabled when the device is in suspend mode to save power.

#### SFR Definition 13.1. PFE0CN: Prefetch Engine Control

| Bit   | 7 | 6 | 5    | 4 | 3 | 2 | 1 | 0 |

|-------|---|---|------|---|---|---|---|---|

| Name  |   |   | PFEN |   |   |   |   |   |

| Туре  | R | R | R/W  | R | R | R | R | R |

| Reset | 0 | 0 | 1    | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0xAF

| Bit | Name   | Function                                                                                                   |  |  |  |

|-----|--------|------------------------------------------------------------------------------------------------------------|--|--|--|

| 7:6 | Unused | Read = 00b, Write = don't care.                                                                            |  |  |  |

| 5   | PFEN   | Prefetch Enable.                                                                                           |  |  |  |

|     |        | This bit enables the prefetch engine.<br>0: Prefetch engine is disabled.<br>1: Prefetch engine is enabled. |  |  |  |

| 4:0 | Unused | Read = 00000b. Write = don't care.                                                                         |  |  |  |

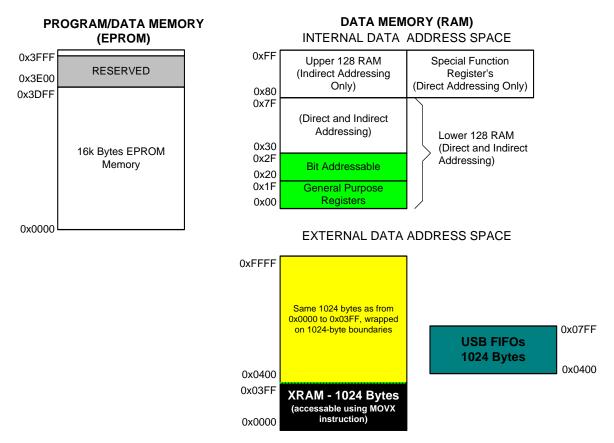

## **15. Memory Organization**

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The memory organization of the C8051T620/1/6/7 & C8051T320/1/2/3 device family is shown in Figure 15.1

Figure 15.1. C8051T620/1 and C8051T320/1/2/3 Memory Map

### SFR Definition 17.2. IP: Interrupt Priority

|       |   | -     | -   | -   | -   |     | -   |     |

|-------|---|-------|-----|-----|-----|-----|-----|-----|

| Bit   | 7 | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

| Name  |   | PSPI0 | PT2 | PS0 | PT1 | PX1 | PT0 | PX0 |

| Туре  | R | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 1 | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Address = 0xB8; Bit-Addressable

| Bit | Name   | Function                                                                                      |

|-----|--------|-----------------------------------------------------------------------------------------------|

| 7   | Unused | Read = 1b, Write = Don't Care.                                                                |

| 6   | PSPI0  | Serial Peripheral Interface (SPI0) Interrupt Priority Control.                                |

|     |        | This bit sets the priority of the SPI0 interrupt.                                             |

|     |        | 0: SPI0 interrupt set to low priority level.<br>1: SPI0 interrupt set to high priority level. |

| 5   | PT2    | Timer 2 Interrupt Priority Control.                                                           |

| -   |        | This bit sets the priority of the Timer 2 interrupt.                                          |

|     |        | 0: Timer 2 interrupt set to low priority level.                                               |

|     |        | 1: Timer 2 interrupt set to high priority level.                                              |

| 4   | PS0    | UART0 Interrupt Priority Control.                                                             |

|     |        | This bit sets the priority of the UART0 interrupt.                                            |

|     |        | 0: UART0 interrupt set to low priority level.                                                 |

|     |        | 1: UART0 interrupt set to high priority level.                                                |

| 3   | PT1    | Timer 1 Interrupt Priority Control.                                                           |

|     |        | This bit sets the priority of the Timer 1 interrupt.                                          |

|     |        | 0: Timer 1 interrupt set to low priority level.                                               |

|     |        | 1: Timer 1 interrupt set to high priority level.                                              |

| 2   | PX1    | External Interrupt 1 Priority Control.                                                        |

|     |        | This bit sets the priority of the External Interrupt 1 interrupt.                             |

|     |        | 0: External Interrupt 1 set to low priority level.                                            |

|     |        | 1: External Interrupt 1 set to high priority level.                                           |

| 1   | PT0    | Timer 0 Interrupt Priority Control.                                                           |

|     |        | This bit sets the priority of the Timer 0 interrupt.                                          |

|     |        | 0: Timer 0 interrupt set to low priority level.                                               |

|     | DV0    | 1: Timer 0 interrupt set to high priority level.                                              |

| 0   | PX0    | External Interrupt 0 Priority Control.                                                        |

|     |        | This bit sets the priority of the External Interrupt 0 interrupt.                             |

|     |        | 0: External Interrupt 0 set to low priority level.                                            |

|     |        | 1: External Interrupt 0 set to high priority level.                                           |

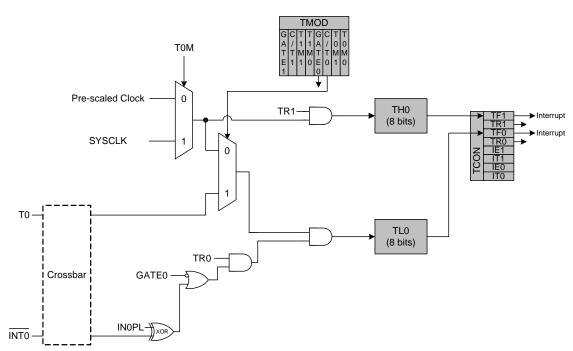

### 17.3. INTO and INT1 External Interrupt Sources

The INTO and INT1 external interrupt sources are configurable as active high or low, edge or level sensitive. The INOPL (INTO Polarity) and IN1PL (INT1 Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (Section "28.1. Timer 0 and Timer 1" on page 248) select level or edge sensitive. The table below lists the possible configurations.

| IT0 | IN0PL | INT0 Interrupt               |  |  |

|-----|-------|------------------------------|--|--|

| 1   | 0     | Active low, edge sensitive   |  |  |

| 1   | 1     | Active high, edge sensitive  |  |  |

| 0   | 0     | Active low, level sensitive  |  |  |

| 0   | 1     | Active high, level sensitive |  |  |

| IT1 | IN1PL | INT1 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

INT0 and INT1 are assigned to Port pins as defined in the IT01CF register (see SFR Definition 17.7). Note that INT0 and INT0 Port pin assignments are independent of any Crossbar assignments. INT0 and INT1 will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to INT0 and/or INT1, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register PnSKIP (see Section "22.3. Priority Crossbar Decoder" on page 142 for complete details on configuring the Crossbar).

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the INT0 and INT1 external interrupts, respectively. If an INT0 or INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

## SFR Definition 20.2. RSTSRC: Reset Source

| Bit   | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| Name  | USBRSF | MEMERR | CORSEF | SWRSF  | WDTRSF | MCDRSF | PORSF  | PINRSF |

| Туре  | R/W    | R      | R/W    | R/W    | R      | R/W    | R/W    | R      |

| Reset | Varies |

SFR Address = 0xEF

| Bit   | Name       | Description                                                                                    | Write                                                                                                                                                                | Read                                                                                                                                           |  |  |  |  |  |  |

|-------|------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7     | USBRSF     | USB Reset Flag                                                                                 | Writing a 1 enables USB as a reset source.                                                                                                                           | Set to 1 if USB caused the last reset.                                                                                                         |  |  |  |  |  |  |

| 6     |            | EPROM Error Reset Flag.                                                                        | N/A                                                                                                                                                                  | Set to 1 if EPROM<br>read/write error caused<br>the last reset.                                                                                |  |  |  |  |  |  |

| 5     | CORSEF     | Comparator0 Reset Enable and Flag.                                                             | Writing a 1 enables<br>Comparator0 as a reset<br>source (active-low).                                                                                                | Set to 1 if Comparator0 caused the last reset.                                                                                                 |  |  |  |  |  |  |

| 4     | SWRSF      | Software Reset Force and Flag.                                                                 | Writing a 1 forces a sys-<br>tem reset.                                                                                                                              | Set to 1 if last reset was<br>caused by a write to<br>SWRSF.                                                                                   |  |  |  |  |  |  |

| 3     | WDTRSF     | Watchdog Timer Reset Flag.                                                                     | N/A                                                                                                                                                                  | Set to 1 if Watchdog Timer<br>overflow caused the last<br>reset.                                                                               |  |  |  |  |  |  |

| 2     | MCDRSF     | Missing Clock Detector<br>Enable and Flag.                                                     | Writing a 1 enables the<br>Missing Clock Detector.<br>The MCD triggers a reset<br>if a missing clock condition<br>is detected.                                       | Set to 1 if Missing Clock<br>Detector timeout caused<br>the last reset.                                                                        |  |  |  |  |  |  |

| 1     | PORSF      | Power-On / V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>Reset Enable. | Writing a 1 enables the $V_{DD}$ monitor as a reset source.<br>Writing 1 to this bit before the $V_{DD}$ monitor is enabled and stabilized may cause a system reset. | Set to 1 anytime a power-<br>on or V <sub>DD</sub> monitor reset<br>occurs.<br>When set to 1 all other<br>RSTSRC flags are inde-<br>terminate. |  |  |  |  |  |  |

| 0     | PINRSF     | HW Pin Reset Flag.                                                                             | N/A                                                                                                                                                                  | Set to 1 if RST pin caused the last reset.                                                                                                     |  |  |  |  |  |  |

| Note: | Do not use | read-modify-write operations on this                                                           | Note: Do not use read-modify-write operations on this register                                                                                                       |                                                                                                                                                |  |  |  |  |  |  |

### 21.5. Programmable Internal Low-Frequency (L-F) Oscillator

All C8051T620/1/6/7 & C8051T320/1/2/3 devices include a programmable low-frequency internal oscillator, which is calibrated to a nominal frequency of 80 kHz. The low-frequency oscillator circuit includes a divider that can be changed to divide the clock by 1, 2, 4, or 8, using the OSCLD bits in the OSCLCN register (see SFR Definition 21.5). Additionally, the OSCLF[3:0] bits can be used to adjust the oscillator's output frequency.

#### 21.5.1. Calibrating the Internal L-F Oscillator

Timers 2 and 3 include capture functions that can be used to capture the oscillator frequency, when running from a known time base. When either Timer 2 or Timer 3 is configured for L-F Oscillator Capture Mode, a falling edge (Timer 2) or rising edge (Timer 3) of the low-frequency oscillator's output will cause a capture event on the corresponding timer. As a capture event occurs, the current timer value (TMRnH:TMRnL) is copied into the timer reload registers (TMRnRLH:TMRnRLL). By recording the difference between two successive timer capture values, the low-frequency oscillator's period can be calculated. The OSCLF bits can then be adjusted to produce the desired oscillator frequency.

#### SFR Definition 21.5. OSCLCN: Internal L-F Oscillator Control

| Bit   | 7      | 6       | 5      | 4                           | 3          | 2 | 1 | 0 |

|-------|--------|---------|--------|-----------------------------|------------|---|---|---|

| Name  | OSCLEN | OSCLRDY |        | OSCL                        | OSCLD[1:0] |   |   |   |

| Туре  | R/W    | R       |        | R.                          | R/         | W |   |   |

| Reset | 0      | 0       | Varies | Varies Varies Varies Varies |            |   |   | 0 |

SFR Address = 0x86

| Bit | Name       | Function                                                                                                                                                                                                        |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | OSCLEN     | Internal L-F Oscillator Enable.                                                                                                                                                                                 |

|     |            | 0: Internal L-F Oscillator Disabled.                                                                                                                                                                            |

|     |            | 1: Internal L-F Oscillator Enabled.                                                                                                                                                                             |

| 6   | OSCLRDY    | Internal L-F Oscillator Ready.                                                                                                                                                                                  |

|     |            | 0: Internal L-F Oscillator frequency not stabilized.                                                                                                                                                            |

|     |            | 1: Internal L-F Oscillator frequency stabilized.                                                                                                                                                                |

|     |            | <b>Note:</b> OSCLRDY is only set back to 0 in the event of a device reset or a change to the OSCLD[1:0] bits.                                                                                                   |

| 5:2 | OSCLF[3:0] | Internal L-F Oscillator Frequency Control Bits.                                                                                                                                                                 |

|     |            | Fine-tune control bits for the Internal L-F oscillator frequency. When set to 0000b, the L-F oscillator operates at its fastest setting. When set to 1111b, the L-F oscillator operates at its slowest setting. |

| 1:0 | OSCLD[1:0] | Internal L-F Oscillator Divider Select.                                                                                                                                                                         |

|     |            | 00: Divide by 8 selected.                                                                                                                                                                                       |

|     |            | 01: Divide by 4 selected.                                                                                                                                                                                       |

|     |            | 10: Divide by 2 selected.                                                                                                                                                                                       |

|     |            | 11: Divide by 1 selected.                                                                                                                                                                                       |

#### 21.6.2. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 21.1, "RC Mode". The capacitor should be no greater than 100 pF; however, for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation, according to Equation , where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and R = the pull-up resistor value in  $k\Omega$ .

$$f = 1.23 \times 10^3 / (R \times C)$$

#### Equation 21.1. RC Mode Oscillator Frequency

For example: If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

f = 1.23(10<sup>3</sup>) / RC = 1.23(10<sup>3</sup>) / [246 x 50] = 0.1 MHz = 100 kHz

Referring to the table in SFR Definition 21.6, the required XFCN setting is 010b.

#### 21.6.3. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 21.1, "C Mode". The capacitor should be no greater than 100 pF; however, for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation according to Equation , where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and V<sub>DD</sub> = the MCU power supply in Volts.

$$f = (KF)/(C \times V_{DD})$$

#### Equation 21.2. C Mode Oscillator Frequency

For example: Assume  $V_{DD}$  = 3.0 V and f = 150 kHz:

f = KF / (C x VDD) 0.150 MHz = KF / (C x 3.0)

Since the frequency of roughly 150 kHz is desired, select the K Factor from the table in SFR Definition 21.6 (OSCXCN) as KF = 22:

0.150 MHz = 22 / (C x 3.0) C x 3.0 = 22 / 0.150 MHz C = 146.6 / 3.0 pF = 48.8 pF

Therefore, the XFCN value to use in this example is 011b and C = 50 pF.

### SFR Definition 21.6. OSCXCN: External Oscillator Control

| Bit   | 7       | 6 | 5          | 4                      | 3 | 2     | 1 | 0 |

|-------|---------|---|------------|------------------------|---|-------|---|---|

| Name  | XCLKVLD | Х | (OSCMD[2:0 | DSCMD[2:0] - XFCN[2:0] |   |       |   |   |

| Туре  | R       |   | R/W        |                        | R | R/W   |   |   |

| Reset | 0       | 0 | 0          | 0                      | 0 | 0 0 0 |   |   |

SFR Address = 0xB1

| Bit | Name        |                                                                    |                                                                                                                                                                                                                                                                                                                                                          | Function                     |                 |  |  |  |  |  |

|-----|-------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------|--|--|--|--|--|

| 7   | XCLKVLD     | Provides<br>tion exc<br>divide by<br>0: Exter                      | Aternal Oscillator Valid Flag.<br>Tovides External Oscillator status and is valid at all times for all modes of opera-<br>on except External CMOS Clock Mode and External CMOS Clock Mode with<br>vide by 2. In these modes, XCLKVLD always returns 0.<br>External Oscillator is unused or not yet stable.<br>External Oscillator is running and stable. |                              |                 |  |  |  |  |  |

| 6:4 | XOSCMD[2:0] | 00x: Ext<br>010: Ext<br>011: Ext<br>100: RC<br>101: Ca<br>110: Cry | ternal Oscillator Mode Select.<br>x: External Oscillator circuit off.<br>D: External CMOS Clock Mode.<br>1: External CMOS Clock Mode with divide by 2 stage.<br>D: RC Oscillator Mode.<br>1: Capacitor Oscillator Mode.<br>D: Crystal Oscillator Mode.<br>1: Crystal Oscillator Mode with divide by 2 stage.                                             |                              |                 |  |  |  |  |  |

| 3   | Unused      | Read =                                                             | Read = 0; Write = Don't Care                                                                                                                                                                                                                                                                                                                             |                              |                 |  |  |  |  |  |

| 2:0 | XFCN[2:0]   | Set acco                                                           | I Oscillator Frequency<br>ording to the desired freq<br>ording to the desired K Fa                                                                                                                                                                                                                                                                       | uency for RC mode.           |                 |  |  |  |  |  |

|     |             | XFCN                                                               | Crystal Mode                                                                                                                                                                                                                                                                                                                                             | RC Mode                      | C Mode          |  |  |  |  |  |

|     |             | 000                                                                | f ≤ 20 kHz                                                                                                                                                                                                                                                                                                                                               | f ≤ 25 kHz                   | K Factor = 0.87 |  |  |  |  |  |

|     |             | 001                                                                | 20 kHz < f ≤ 58 kHz                                                                                                                                                                                                                                                                                                                                      | 25 kHz < f ≤ 50 kHz          | K Factor = 2.6  |  |  |  |  |  |

|     |             | 010                                                                | 58 kHz < f ≤ 155 kHz                                                                                                                                                                                                                                                                                                                                     | 50 kHz < f $\leq$ 100 kHz    | K Factor = 7.7  |  |  |  |  |  |

|     |             | 011                                                                | 155 kHz $<$ f $\leq$ 415 kHz                                                                                                                                                                                                                                                                                                                             | 100 kHz $<$ f $\leq$ 200 kHz | K Factor = 22   |  |  |  |  |  |

|     |             | 100                                                                | 415 kHz $<$ f $\leq$ 1.1 MHz                                                                                                                                                                                                                                                                                                                             | 200 kHz $<$ f $\leq$ 400 kHz | K Factor = 65   |  |  |  |  |  |

|     |             | 101                                                                | 1.1 MHz $<$ f $\leq$ 3.1 MHz                                                                                                                                                                                                                                                                                                                             | 400 kHz $<$ f $\le$ 800 kHz  | K Factor = 180  |  |  |  |  |  |

|     |             | 110                                                                | $3.1 \text{ MHz} < f \le 8.2 \text{ MHz}$                                                                                                                                                                                                                                                                                                                | 800 kHz $<$ f $\leq$ 1.6 MHz | K Factor = 664  |  |  |  |  |  |

|     |             | 111                                                                | $8.2 \text{ MHz} < f \le 25 \text{ MHz}$                                                                                                                                                                                                                                                                                                                 | 1.6 MHz $<$ f $\leq$ 3.2 MHz | K Factor = 1590 |  |  |  |  |  |

### SFR Definition 24.4. SMB0ADM: SMBus Slave Address Mask

| Bit   | 7 | 6         | 5 | 4   | 3 | 2 | 1 | 0   |  |  |

|-------|---|-----------|---|-----|---|---|---|-----|--|--|

| Name  |   | SLVM[6:0] |   |     |   |   |   |     |  |  |

| Туре  |   |           |   | R/W |   |   |   | R/W |  |  |

| Reset | 1 | 1         | 1 | 1   | 1 | 1 | 1 | 0   |  |  |

SFR Address = 0xCF

| Bit | Name      | Function                                                                                                                                                                                                                                                                           |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLVM[6:0] | SMBus Slave Address Mask.                                                                                                                                                                                                                                                          |

|     |           | Defines which bits of register SMB0ADR are compared with an incoming address byte, and which bits are ignored. Any bit set to 1 in SLVM[6:0] enables comparisons with the corresponding bit in SLV[6:0]. Bits set to 0 are ignored (can be either 0 or 1 in the incoming address). |

| 0   | EHACK     | Hardware Acknowledge Enable.                                                                                                                                                                                                                                                       |

|     |           | <ul> <li>Enables hardware acknowledgement of slave address and received data bytes.</li> <li>0: Firmware must manually acknowledge all incoming address and data bytes.</li> <li>1: Automatic Slave Address Recognition and Hardware Acknowledge is Enabled.</li> </ul>            |

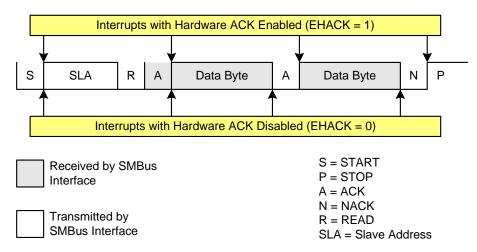

#### 24.5.2. Read Sequence (Master)

During a read sequence, an SMBus master reads data from a slave device. The master in this transfer will be a transmitter during the address byte, and a receiver during all data bytes. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 1 (READ). Serial data is then received from the slave on SDA while the SMBus outputs the serial clock. The slave transmits one or more bytes of serial data.

If hardware ACK generation is disabled, the ACKRQ is set to 1 and an interrupt is generated after each received byte. Software must write the ACK bit at that time to ACK or NACK the received byte.

With hardware ACK generation enabled, the SMBus hardware will automatically generate the ACK/NACK, and then post the interrupt. It is important to note that the appropriate ACK or NACK value should be set up by the software prior to receiving the byte when hardware ACK generation is enabled.

Writing a 1 to the ACK bit generates an ACK; writing a 0 generates a NACK. Software should write a 0 to the ACK bit for the last data transfer, to transmit a NACK. The interface exits Master Receiver Mode after the STO bit is set and a STOP is generated. The interface will switch to Master Transmitter Mode if SMB0-DAT is written while an active Master Receiver. Figure 24.6 shows a typical master read sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur at different places in the sequence, depending on whether hardware ACK generation is enabled. The interrupt occurs **before** the ACK with hardware ACK generation disabled, and **after** the ACK when hardware ACK generation is enabled.

Figure 24.6. Typical Master Read Sequence

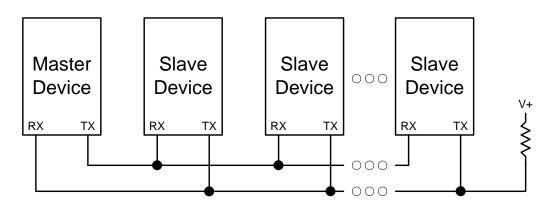

#### 25.3. Multiprocessor Communications

9-Bit UART mode supports multiprocessor communication between a master processor and one or more slave processors by special use of the ninth data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its ninth bit is logic 1; in a data byte, the ninth bit is always set to logic 0.

Setting the MCE0 bit (SCON0.5) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the ninth bit is logic 1 (RB80 = 1) signifying an address byte has been received. In the UART interrupt handler, software will compare the received address with the slave's own assigned 8-bit address. If the addresses match, the slave will clear its MCE0 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE0 bits set and do not generate interrupts on the reception of the following data byte(s) addressed slave resets its MCE0 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

Figure 25.6. UART Multi-Processor Mode Interconnect Diagram

## SFR Definition 26.1. SCON1: UART1 Control

| Bit   | 7    | 6     | 5     | 4    | 3    | 2    | 1   | 0   |

|-------|------|-------|-------|------|------|------|-----|-----|

| Name  | OVR1 | PERR1 | THRE1 | REN1 | TBX1 | RBX1 | TI1 | RI1 |

| Туре  | R/W  | R/W   | R     | R/W  | R/W  | R/W  | R/W | R/W |

| Reset | 0    | 0     | 1     | 0    | 0    | 0    | 0   | 0   |

#### SFR Address = 0xD2

| Bit | Name  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | OVR1  | <ul> <li>Receive FIFO Overrun Flag.</li> <li>This bit indicates a receive FIFO overrun condition, where an incoming character is discarded due to a full FIFO. This bit must be cleared to 0 by software.</li> <li>0: Receive FIFO Overrun has not occurred.</li> <li>1: Receive FIFO Overrun has occurred.</li> </ul>                                                                                                                                                                       |

| 6   | PERR1 | <ul> <li>Parity Error Flag.</li> <li>When parity is enabled, this bit indicates that a parity error has occurred. It is set to 1 when the parity of the oldest byte in the FIFO does not match the selected Parity Type. This bit must be cleared to 0 by software.</li> <li>0: Parity Error has not occurred.</li> <li>1: Parity Error has occurred.</li> </ul>                                                                                                                             |

| 5   | THRE1 | Transmit Holding Register Empty Flag.0: Transmit Holding Register not Empty - do not write to SBUF1.1: Transmit Holding Register Empty - it is safe to write to SBUF1.                                                                                                                                                                                                                                                                                                                       |

| 4   | REN1  | Receive Enable.<br>This bit enables/disables the UART receiver. When disabled, bytes can still be read from the receive FIFO.<br>0: UART1 reception disabled.<br>1: UART1 reception enabled.                                                                                                                                                                                                                                                                                                 |

| 3   | TBX1  | <b>Extra Transmission Bit.</b><br>The logic level of this bit will be assigned to the extra transmission bit when XBE1 = 1. This bit is not used when Parity is enabled.                                                                                                                                                                                                                                                                                                                     |

| 2   | RBX1  | <b>Extra Receive Bit.</b><br>RBX1 is assigned the value of the extra bit when XBE1 = 1. If XBE1 is cleared to 0, RBX1 is assigned the logic level of the first stop bit. This bit is not valid when Parity is enabled.                                                                                                                                                                                                                                                                       |

| 1   | TI1   | <b>Transmit Interrupt Flag.</b><br>Set to a 1 by hardware after data has been transmitted at the beginning of the STOP bit. When the UART1 interrupt is enabled, setting this bit causes the CPU to vector to the UART1 interrupt service routine. This bit must be cleared manually by software.                                                                                                                                                                                            |

| 0   | RI1   | <b>Receive Interrupt Flag.</b><br>Set to 1 by hardware when a byte of data has been received by UART1 (set at the STOP bit sampling time). When the UART1 interrupt is enabled, setting this bit to 1 causes the CPU to vector to the UART1 interrupt service routine. This bit must be cleared manually by software. Note that RI1 will remain set to '1' as long as there is still data in the UART FIFO. After the last byte has been shifted from the FIFO to SBUF1, RI1 can be cleared. |

## SFR Definition 26.6. SBRLL1: UART1 Baud Rate Generator Low Byte

| Bit   | 7                                             | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|-----------------------------------------------|---------------|---|---|---|---|---|---|--|--|--|

| Nam   | e                                             | SBRLL1[7:0]   |   |   |   |   |   |   |  |  |  |

| Туре  | 9                                             | R/W           |   |   |   |   |   |   |  |  |  |

| Rese  | et 0                                          | 0             | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

| SFR A | Address = 0xB                                 | 4             |   |   |   |   |   |   |  |  |  |

| Bit   | Name                                          | Name Function |   |   |   |   |   |   |  |  |  |

| 7.0   | SBRI   1[7:0] UART1 Roud Rote Relead Low Rite |               |   |   |   |   |   |   |  |  |  |

| ы   | Name        | i unction                                               |

|-----|-------------|---------------------------------------------------------|

| 7:0 | SBRLL1[7:0] | UART1 Baud Rate Reload Low Bits.                        |

|     |             | Low Byte of reload value for UART1 Baud Rate Generator. |

### SFR Definition 27.3. SPI0CKR: SPI0 Clock Rate

| Bit    | 7             | 6                                                                                         | 5                                                                | 4                                                                               | 3                            | 2                             | 1                                               | 0         |  |  |  |  |

|--------|---------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------|-------------------------------|-------------------------------------------------|-----------|--|--|--|--|

| Name   |               | SCR[7:0]                                                                                  |                                                                  |                                                                                 |                              |                               |                                                 |           |  |  |  |  |

| Туре   |               | R/W                                                                                       |                                                                  |                                                                                 |                              |                               |                                                 |           |  |  |  |  |

| Reset  | 0             | 0 0 0 0 0 0                                                                               |                                                                  |                                                                                 |                              |                               |                                                 |           |  |  |  |  |

| SFR Ac | ldress = 0xA2 | 2                                                                                         |                                                                  |                                                                                 |                              |                               |                                                 |           |  |  |  |  |

| Bit    | Name          |                                                                                           |                                                                  |                                                                                 | Functior                     | ı                             |                                                 |           |  |  |  |  |

| 7:0    | SCR[7:0]      | SPI0 Cloc                                                                                 | k Rate.                                                          |                                                                                 |                              |                               |                                                 |           |  |  |  |  |

|        |               | sion of the<br>the system<br>register.<br>f <sub>SCK</sub> =<br>for 0 <= SI<br>Example: I | system clo<br>clock freq<br>SY<br>$2 \times (SPI00$<br>PI0CKR <= | ck, and is gi<br>uency and S<br><u>SCLK</u><br>CKR[7:0] +<br>255<br>= 2 MHz and | ven in the fo<br>PIOCKR is t | bllowing equ<br>he 8-bit valu | quency is a c<br>ation, where<br>ue held in the | SYSCLK is |  |  |  |  |

### SFR Definition 27.4. SPI0DAT: SPI0 Data

| Bit   | 7 | 6            | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|-------|---|--------------|---|----|---|---|---|---|--|--|

| Name  |   | SPI0DAT[7:0] |   |    |   |   |   |   |  |  |

| Туре  |   |              |   | R/ | W |   |   |   |  |  |

| Reset | 0 | 0            | 0 | 0  | 0 | 0 | 0 | 0 |  |  |

SFR Address = 0xA3

| Bit | Name         | Function                                                                                                                                                                                                                                     |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SPI0DAT[7:0] | SPI0 Transmit and Receive Data.                                                                                                                                                                                                              |

|     |              | The SPI0DAT register is used to transmit and receive SPI0 data. Writing data to SPI0DAT places the data into the transmit buffer and initiates a transfer when in Master Mode. A read of SPI0DAT returns the contents of the receive buffer. |

### SFR Definition 28.6. TH0: Timer 0 High Byte

| Bit                | 7           | 6                                                        | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------------|-------------|----------------------------------------------------------|---|---|---|---|---|---|

| Nam                | me TH0[7:0] |                                                          |   |   |   |   |   |   |

| Туре               | e R/W       |                                                          |   |   |   |   |   |   |

| Rese               | et 0        | 0                                                        | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address = 0x8C |             |                                                          |   |   |   |   |   |   |

| Bit                | Name        | Function                                                 |   |   |   |   |   |   |

| 7:0                | TH0[7:0]    | Timer 0 High Byte.                                       |   |   |   |   |   |   |

|                    |             | The TH0 register is the high byte of the 16-bit Timer 0. |   |   |   |   |   |   |

## SFR Definition 28.7. TH1: Timer 1 High Byte

| Bit                | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------------|---------------|---|---|---|---|---|---|---|

| Name               | TH1[7:0]      |   |   |   |   |   |   |   |

| Туре               | R/W           |   |   |   |   |   |   |   |

| Reset              | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address = 0x8D |               |   |   |   |   |   |   |   |

| Bit                | Name Function |   |   |   |   |   |   |   |

| Bit | Name     | Function                                                 |

|-----|----------|----------------------------------------------------------|

| 7:0 | TH1[7:0] | Timer 1 High Byte.                                       |

|     |          | The TH1 register is the high byte of the 16-bit Timer 1. |

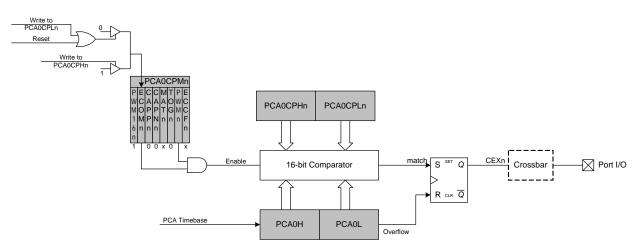

Figure 29.10. PCA 16-Bit PWM Mode

### 29.4. Watchdog Timer Mode

A programmable watchdog timer (WDT) function is available through the PCA Module 4. The WDT is used to generate a reset if the time between writes to the WDT update register (PCA0CPH4) exceed a specified limit. The WDT can be configured and enabled/disabled as needed by software.

With the WDTE bit set in the PCA0MD register, Module 4 operates as a watchdog timer (WDT). The Module 4 high byte is compared to the PCA counter high byte; the Module 4 low byte holds the offset to be used when WDT updates are performed. The Watchdog Timer is enabled on reset. Writes to some PCA registers are restricted while the Watchdog Timer is enabled. The WDT will generate a reset shortly after code begins execution. To avoid this reset, the WDT should be explicitly disabled (and optionally re-configured and re-enabled if it is used in the system).

#### 29.4.1. Watchdog Timer Operation

While the WDT is enabled:

- PCA counter is forced on.

- Writes to PCA0L and PCA0H are not allowed.

- PCA clock source bits (CPS2–CPS0) are frozen.

- PCA Idle control bit (CIDL) is frozen.

- Module 4 is forced into software timer mode.

- Writes to the Module 4 mode register (PCA0CPM4) are disabled.

While the WDT is enabled, writes to the CR bit will not change the PCA counter state; the counter will run until the WDT is disabled. The PCA counter run control bit (CR) will read zero if the WDT is enabled but user software has not enabled the PCA counter. If a match occurs between PCA0CPH4 and PCA0H while the WDT is enabled, a reset will be generated. To prevent a WDT reset, the WDT may be updated with a write of any value to PCA0CPH4. Upon a PCA0CPH4 write, PCA0H plus the offset held in PCA0CPL4 is loaded into PCA0CPH4 (See Figure 29.11).