Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                   |

|----------------------------|-------------------------------------------------------------------|

| Product Status             | Obsolete                                                          |

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 48 MIPS                                                           |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                            |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                        |

| Number of I/O              | 24                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                    |

| Program Memory Type        | OTP                                                               |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 3.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                      |

| Data Converters            | A/D 21x10b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 32-VFQFN Exposed Pad                                              |

| Supplier Device Package    | 32-QFN (5x5)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051t627-b-gmr |

### 3. Pin Definitions

Table 3.1. Pin Definitions for the C8051T620/1/6/7 & C8051T320/1/2/3

| Nama            | Pin Number |         |         | T                | Description                                                                                                                                                            |  |  |

|-----------------|------------|---------|---------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name            | 'T62x      | 'T320/2 | 'T321/3 | Туре             | Description                                                                                                                                                            |  |  |

| V <sub>DD</sub> | 7          | 6       | 6       |                  | Power Supply Voltage.                                                                                                                                                  |  |  |

| GND             | 3          | 3       | 3       |                  | Ground.                                                                                                                                                                |  |  |

| RST/            | 10         | 9       | 9       | D I/O            | Device Reset. Open-drain output of internal POR or V <sub>DD</sub> monitor. An external source can initiate a system reset by driving this pin low for at least 10 μs. |  |  |

| C2CK            |            |         |         | D I/O            | Clock signal for the C2 Debug Interface.                                                                                                                               |  |  |

| P3.0/           | 11         | 10      | 10      | D I/O            | Port 3.0.                                                                                                                                                              |  |  |

| C2D             |            |         |         | D I/O            | Bi-directional data signal for the C2 Debug Interface.                                                                                                                 |  |  |

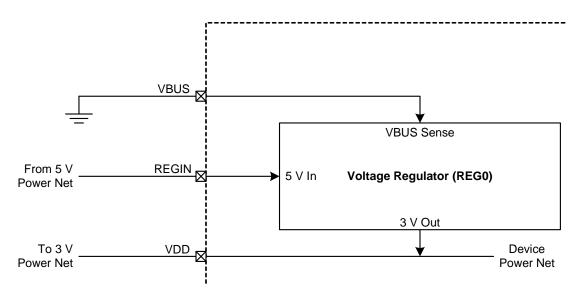

| REGIN           | 8          | 7       | 7       |                  | 5 V Regulator Input. This pin is the input to the on-chip voltage regulator.                                                                                           |  |  |

| VBUS            | 9          | 8       | 8       | D In             | VBUS Sense Input. This pin should be connected to the VBUS signal of a USB network. A 5 V signal on this pin indicates a USB network connection.                       |  |  |

| D+              | 4          | 4       | 4       | D I/O            | USB D+.                                                                                                                                                                |  |  |

| D-              | 5          | 5       | 5       | D I/O            | USB D                                                                                                                                                                  |  |  |

| V <sub>IO</sub> | 6          | -       | -       |                  | V I/O Supply Voltage Input. The voltage at this pin must be less than or equal to the Core Supply Voltage (V <sub>DD</sub> ).                                          |  |  |

| P0.0            | 2          | 2       | 2       | D I/O or<br>A In | Port 0.0.                                                                                                                                                              |  |  |

| P0.1            | 1          | 1       | 1       | D I/O or<br>A In | r Port 0.1.                                                                                                                                                            |  |  |

| P0.2            | 32         | 32      | 28      | D I/O or<br>A In | Port 0.2.                                                                                                                                                              |  |  |

| XTAL1           |            |         |         | A In             | External Clock Input. This pin is the external oscillator return for a crystal or resonator. See Oscillator Section.                                                   |  |  |

**Table 7.13. Comparator Electrical Characteristics**

$V_{DD}$  = 3.0 V, -40 to +85 °C unless otherwise noted.

| Parameters                                        | Test Condition        | Min      | Тур  | Max                    | Unit |

|---------------------------------------------------|-----------------------|----------|------|------------------------|------|

| Response Time:                                    | CP0+ - CP0- = 100 mV  | _        | 240  | _                      | ns   |

| Mode 0, Vcm* = 1.5 V                              | CP0+ - CP0- = -100 mV | _        | 240  | _                      | ns   |

| Response Time:                                    | CP0+ - CP0- = 100 mV  | _        | 400  | _                      | ns   |

| Mode 1, Vcm* = 1.5 V                              | CP0+ - CP0- = -100 mV | _        | 400  | _                      | ns   |

| Response Time:                                    | CP0+ - CP0- = 100 mV  | _        | 650  | _                      | ns   |

| Mode 2, Vcm* = 1.5 V                              | CP0+ - CP0- = -100 mV | _        | 1100 | _                      | ns   |

| Response Time:                                    | CP0+ - CP0- = 100 mV  | _        | 2000 | _                      | ns   |

| Mode 3, Vcm* = 1.5 V                              | CP0+ - CP0- = -100 mV | _        | 5500 | _                      | ns   |

| Common-Mode Rejection Ratio                       |                       | _        | 1.0  | 4                      | mV/V |

| Positive Hysteresis 1                             | CP0HYP1-0 = 00        | _        | 0    | 1                      | mV   |

| Positive Hysteresis 2                             | CP0HYP1-0 = 01        | 2        | 5    | 8                      | mV   |

| Positive Hysteresis 3                             | CP0HYP1-0 = 10        | 6        | 10   | 14                     | mV   |

| Positive Hysteresis 4                             | CP0HYP1-0 = 11        | 12       | 20   | 28                     | mV   |

| Negative Hysteresis 1                             | CP0HYN1-0 = 00        |          | 0    | 1                      | mV   |

| Negative Hysteresis 2                             | CP0HYN1-0 = 01        | 2        | 5    | 8                      | mV   |

| Negative Hysteresis 3                             | CP0HYN1-0 = 10        | 6        | 10   | 14                     | mV   |

| Negative Hysteresis 4                             | CP0HYN1-0 = 11        | 12       | 20   | 28                     | mV   |

| Inverting or Non-Inverting Input<br>Voltage Range |                       | -0.25    | _    | V <sub>DD</sub> + 0.25 | V    |

| Input Capacitance                                 |                       | _        | 4    | _                      | pF   |

| Input Offset Voltage                              |                       | -7.5     | _    | +7.5                   | mV   |

| Power Supply                                      |                       | <u>-</u> |      | -                      |      |

| Power Supply Rejection                            |                       | _        | 0.5  | _                      | mV/V |

| Power-up Time                                     |                       | _        | 10   | _                      | μs   |

| Supply Current at DC                              | Mode 0                | _        | 26   | 50                     | μΑ   |

|                                                   | Mode 1                | _        | 10   | 20                     | μΑ   |

|                                                   | Mode 2                | _        | 3    | 6                      | μΑ   |

|                                                   | Mode 3                | _        | 0.5  | 2                      | μA   |

| Note: Vcm is the common-mode vo                   | Itage on CP0+ and CP0 | •        |      | · '                    |      |

### SFR Definition 10.1. REF0CN: Reference Control

| Bit   | 7      | 6 | 5 | 4      | 3     | 2     | 1     | 0     |

|-------|--------|---|---|--------|-------|-------|-------|-------|

| Name  | REFBGS |   |   | REGOVR | REFSL | TEMPE | BIASE | REFBE |

| Туре  | R/W    | R | R | R/W    | R/W   | R/W   | R/W   | R/W   |

| Reset | 0      | 0 | 0 | 0      | 0     | 0     | 0     | 0     |

#### SFR Address = 0xD1

| Bit | Name   | Function                                                                                                                                                                                                                                                           |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | REFBGS | Reference Buffer Gain Select.  This bit selects between 1x and 2x gain for the on-chip voltage reference buffer.  0: 2x Gain  1: 1x Gain                                                                                                                           |

| 6:5 | Unused | Read = 00b; Write = don't care.                                                                                                                                                                                                                                    |

| 4   | REGOVR | Regulator Reference Override.  This bit "overrides" the REFSL bit, and allows the internal regulator to be used as a reference source.  0: The voltage reference source is selected by the REFSL bit.  1: The internal regulator is used as the voltage reference. |

| 3   | REFSL  | Voltage Reference Select.  This bit selects the ADCs voltage reference.  0: V <sub>REF</sub> pin used as voltage reference.  1: V <sub>DD</sub> used as voltage reference.                                                                                         |

| 2   | TEMPE  | Temperature Sensor Enable Bit.  0: Internal Temperature Sensor off.  1: Internal Temperature Sensor on.                                                                                                                                                            |

| 1   | BIASE  | Internal Analog Bias Generator Enable Bit.  0: Internal Bias Generator off.  1: Internal Bias Generator on.                                                                                                                                                        |

| 0   | REFBE  | On-chip Reference Buffer Enable Bit.  0: On-chip Reference Buffer off.  1: On-chip Reference Buffer on. Internal voltage reference driven on the V <sub>REF</sub> pin.                                                                                             |

Figure 11.4. REG0 Configuration: No USB Connection

Table 12.1. CIP-51 Instruction Set Summary

| Mnemonic              | Description                              | Bytes | Clock<br>Cycles |  |  |

|-----------------------|------------------------------------------|-------|-----------------|--|--|

| Arithmetic Operations | · ·                                      |       |                 |  |  |

| ADD A, Rn             | 1                                        | 1     |                 |  |  |

| ADD A, direct         | ADD A, direct Add direct byte to A       |       |                 |  |  |

| ADD A, @Ri            | Add indirect RAM to A                    | 1     | 2               |  |  |

| ADD A, #data          | Add immediate to A                       | 2     | 2               |  |  |

| ADDC A, Rn            | Add register to A with carry             | 1     | 1               |  |  |

| ADDC A, direct        | Add direct byte to A with carry          | 2     | 2               |  |  |

| ADDC A, @Ri           | Add indirect RAM to A with carry         | 1     | 2               |  |  |

| ADDC A, #data         | Add immediate to A with carry            | 2     | 2               |  |  |

| SUBB A, Rn            | Subtract register from A with borrow     | 1     | 1               |  |  |

| SUBB A, direct        | Subtract direct byte from A with borrow  | 2     | 2               |  |  |

| SUBB A, @Ri           | Subtract indirect RAM from A with borrow | 1     | 2               |  |  |

| SUBB A, #data         | Subtract immediate from A with borrow    | 2     | 2               |  |  |

| INC A                 | Increment A                              | 1     | 1               |  |  |

| INC Rn                | Increment register                       | 1     | 1               |  |  |

| INC direct            | Increment direct byte                    | 2     | 2               |  |  |

| INC @Ri               | Increment indirect RAM                   | 1     | 2               |  |  |

| DEC A                 | Decrement A                              | 1     | 1               |  |  |

| DEC Rn                | Decrement register                       | 1     | 1               |  |  |

| DEC direct            | Decrement direct byte                    | 2     | 2               |  |  |

| DEC @Ri               | Decrement indirect RAM                   | 1     | 2               |  |  |

| INC DPTR              | Increment Data Pointer                   | 1     | 1               |  |  |

| MUL AB                | Multiply A and B                         | 1     | 4               |  |  |

| DIV AB                | Divide A by B                            | 1     | 8               |  |  |

| DA A                  | Decimal adjust A                         | 1     | 1               |  |  |

| Logical Operations    |                                          | 1     |                 |  |  |

| ANL A, Rn             | AND Register to A                        | 1     | 1               |  |  |

| ANL A, direct         | AND direct byte to A                     | 2     | 2               |  |  |

| ANL A, @Ri            | AND indirect RAM to A                    | 1     | 2               |  |  |

| ANL A, #data          | AND immediate to A                       | 2     | 2               |  |  |

| ANL direct, A         | AND A to direct byte                     | 2     | 2               |  |  |

| ANL direct, #data     | AND immediate to direct byte             | 3     | 3               |  |  |

| ORL A, Rn             | OR Register to A                         | 1     | 1               |  |  |

### SFR Definition 12.6. PSW: Program Status Word

| Bit   | 7   | 6   | 5   | 4   | 3    | 2  | 1   | 0      |

|-------|-----|-----|-----|-----|------|----|-----|--------|

| Name  | CY  | AC  | F0  | RS[ | 1:0] | OV | F1  | PARITY |

| Туре  | R/W | R/W | R/W | R/  | R/W  |    | R/W | R      |

| Reset | 0   | 0   | 0   | 0   | 0    | 0  | 0   | 0      |

SFR Address = 0xD0; Bit-Addressable

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CY      | Carry Flag. This bit is set when the last arithmetic operation resulted in a carry (addition) or a borrow (subtraction). It is cleared to logic 0 by all other arithmetic operations.                                                                                                                                                                                                                         |

| 6   | AC      | Auxiliary Carry Flag.                                                                                                                                                                                                                                                                                                                                                                                         |

|     |         | This bit is set when the last arithmetic operation resulted in a carry into (addition) or a borrow from (subtraction) the high order nibble. It is cleared to logic 0 by all other arithmetic operations.                                                                                                                                                                                                     |

| 5   | F0      | User Flag 0.                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |         | This is a bit-addressable, general purpose flag for use under software control.                                                                                                                                                                                                                                                                                                                               |

| 4:3 | RS[1:0] | Register Bank Select.                                                                                                                                                                                                                                                                                                                                                                                         |

|     |         | These bits select which register bank is used during register accesses.  00: Bank 0, Addresses 0x00-0x07  01: Bank 1, Addresses 0x08-0x0F  10: Bank 2, Addresses 0x10-0x17  11: Bank 3, Addresses 0x18-0x1F                                                                                                                                                                                                   |

| 2   | OV      | Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                |

|     |         | <ul> <li>This bit is set to 1 under the following circumstances:</li> <li>An ADD, ADDC, or SUBB instruction causes a sign-change overflow.</li> <li>A MUL instruction results in an overflow (result is greater than 255).</li> <li>A DIV instruction causes a divide-by-zero condition.</li> <li>The OV bit is cleared to 0 by the ADD, ADDC, SUBB, MUL, and DIV instructions in all other cases.</li> </ul> |

| 1   | F1      | User Flag 1.                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |         | This is a bit-addressable, general purpose flag for use under software control.                                                                                                                                                                                                                                                                                                                               |

| 0   | PARITY  | Parity Flag.                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |         | This bit is set to logic 1 if the sum of the eight bits in the accumulator is odd and cleared if the sum is even.                                                                                                                                                                                                                                                                                             |

### 13. Prefetch Engine

The C8051T620/1/6/7 & C8051T320/1/2/3 family of devices incorporate a 2-byte prefetch engine. Because the access time of the EPROM memory is 40 ns, and the minimum instruction time is roughly 20 ns, the prefetch engine is necessary for full-speed code execution. Instructions are read from EPROM memory two bytes at a time by the prefetch engine and given to the CIP-51 processor core to execute. When running linear code (code without any jumps or branches), the prefetch engine allows instructions to be executed at full speed. When a code branch occurs, the processor may be stalled for up to two clock cycles while the next set of code bytes is retrieved from EPROM memory.

**Note:** The prefetch engine should be disabled when the device is in suspend mode to save power.

### SFR Definition 13.1. PFE0CN: Prefetch Engine Control

| Bit   | 7 | 6 | 5    | 4 | 3 | 2 | 1 | 0 |

|-------|---|---|------|---|---|---|---|---|

| Name  |   |   | PFEN |   |   |   |   |   |

| Туре  | R | R | R/W  | R | R | R | R | R |

| Reset | 0 | 0 | 1    | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0xAF

| Bit | Name   | Function                                                                                               |

|-----|--------|--------------------------------------------------------------------------------------------------------|

| 7:6 | Unused | Read = 00b, Write = don't care.                                                                        |

| 5   | PFEN   | Prefetch Enable.                                                                                       |

|     |        | This bit enables the prefetch engine.  0: Prefetch engine is disabled.  1: Prefetch engine is enabled. |

| 4:0 | Unused | Read = 00000b. Write = don't care.                                                                     |

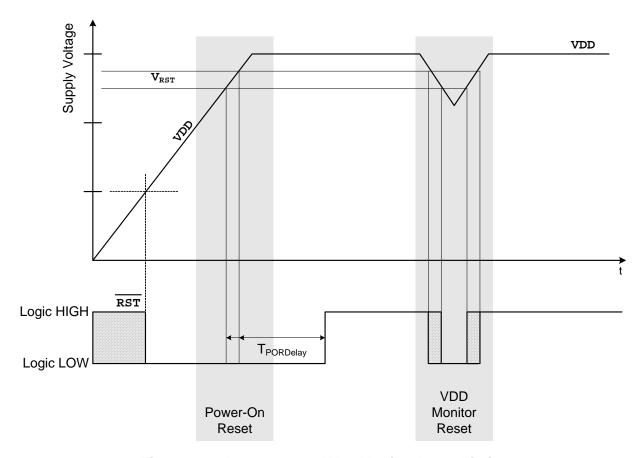

#### 20.1. Power-On Reset

During power-up, the device is held in a reset state and the  $\overline{RST}$  pin is driven low until  $V_{DD}$  settles above  $V_{RST}$ . A delay occurs before the device is released from reset; the delay decreases as the  $V_{DD}$  ramp time increases ( $V_{DD}$  ramp time is defined as how fast  $V_{DD}$  ramps from 0 V to  $V_{RST}$ ). Figure 20.2. plots the power-on and  $V_{DD}$  monitor event timing. The maximum  $V_{DD}$  ramp time is 1 ms; slower ramp times may cause the device to be released from reset before  $V_{DD}$  reaches the  $V_{RST}$  level. For ramp times less than 1 ms, the power-on reset delay ( $T_{PORDelay}$ ) is typically less than 0.3 ms.

On exit from a power-on or  $V_{DD}$  monitor reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. When PORSF is set, all of the other reset flags in the RSTSRC Register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000) software can read the PORSF flag to determine if a power-up was the cause of reset. The content of internal data memory should be assumed to be undefined after a power-on reset. The  $V_{DD}$  monitor is enabled following a power-on reset.

Figure 20.2. Power-On and V<sub>DD</sub> Monitor Reset Timing

#### 20.2. Power-Fail Reset / V<sub>DD</sub> Monitor

When a power-down transition or power irregularity causes  $V_{DD}$  to drop below  $V_{RST}$ , the power supply monitor will drive the  $\overline{RST}$  pin low and hold the CIP-51 in a reset state (see Figure 20.2). When  $V_{DD}$  returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state. Note that even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below

#### 20.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "29.4. Watchdog Timer Mode" on page 279; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The state of the RST pin is unaffected by this reset.

#### 20.7. EPROM Error Reset

If an EPROM program read or write targets an illegal address, a system reset is generated. This may occur due to any of the following:

- Programming hardware attempts to write or read an EPROM location which is above the user code space address limit.

- An EPROM read from firmware is attempted above user code space. This occurs when a MOVC operation is attempted above the user code space address limit.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above the user code space address limit.

The MEMERR bit (RSTSRC.6) is set following an EPROM error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

#### 20.8. Software Reset

Software may force a reset by writing a 1 to the SWRSF bit (RSTSRC.4). The SWRSF bit will read 1 following a software forced reset. The state of the RST pin is unaffected by this reset.

#### 20.9. USB Reset

Writing 1 to the USBRSF bit in register RSTSRC selects USB0 as a reset source. With USB0 selected as a reset source, a system reset will be generated when either of the following occur:

- RESET signaling is detected on the USB network. The USB Function Controller (USB0) must be enabled for RESET signaling to be detected. See Section "23. Universal Serial Bus Controller (USB0)" on page 160 for information on the USB Function Controller.

- 2. A falling or rising voltage on the VBUS pin matches the edge polarity selected by the VBPOL bit in register REG01CN. See Section "11. Voltage Regulators (REG0 and REG1)" on page 61 for details on the VBUS detection circuit.

The USBRSF bit will read 1 following a USB reset. The state of the /RST pin is unaffected by this reset.

#### 21.6.2. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 21.1, "RC Mode". The capacitor should be no greater than 100 pF; however, for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation, according to Equation , where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and R = the pull-up resistor value in  $k\Omega$ .

$$f = 1.23 \times 10^3 / (R \times C)$$

#### **Equation 21.1. RC Mode Oscillator Frequency**

For example: If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

$$f = 1.23(10^3) / RC = 1.23(10^3) / [246 \times 50] = 0.1 MHz = 100 kHz$$

Referring to the table in SFR Definition 21.6, the required XFCN setting is 010b.

#### 21.6.3. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 21.1, "C Mode". The capacitor should be no greater than 100 pF; however, for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation according to Equation , where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and  $V_{DD} = the$  MCU power supply in Volts.

$$f = (KF)/(C \times V_{DD})$$

#### **Equation 21.2. C Mode Oscillator Frequency**

For example: Assume  $V_{DD} = 3.0 \text{ V}$  and f = 150 kHz:

f = KF / (C x VDD) 0.150 MHz = KF / (C x 3.0)

Since the frequency of roughly 150 kHz is desired, select the K Factor from the table in SFR Definition 21.6 (OSCXCN) as KF = 22:

0.150 MHz = 22 / (C x 3.0) C x 3.0 = 22 / 0.150 MHz C = 146.6 / 3.0 pF = 48.8 pF

Therefore, the XFCN value to use in this example is 011b and C = 50 pF.

### USB Register Definition 23.20. EINCSRL: USB0 IN Endpoint Control Low

| Bit   | 7 | 6     | 5     | 4     | 3     | 2      | 1      | 0      |

|-------|---|-------|-------|-------|-------|--------|--------|--------|

| Name  |   | CLRDT | STSTL | SDSTL | FLUSH | UNDRUN | FIFONE | INPRDY |

| Туре  | R | W     | R/W   | R/W   | R/W   | R/W    | R/W    | R/W    |

| Reset | 0 | 0     | 0     | 0     | 0     | 0      | 0      | 0      |

USB Register Address = 0x11

| USDI | JSB Register Address = 0x11 |                                                                                                                                                                                                                                                                       |                                                                                |                                                                 |  |  |  |  |  |

|------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|--|

| Bit  | Name                        | Description                                                                                                                                                                                                                                                           | Write                                                                          | Read                                                            |  |  |  |  |  |

| 7    | Unused                      | Read = 0b. Write = don't                                                                                                                                                                                                                                              | Read = 0b. Write = don't care.                                                 |                                                                 |  |  |  |  |  |

| 6    | CLRDT                       | Clear Data Toggle Bit.                                                                                                                                                                                                                                                | Software should write 1 to this bit to reset the IN Endpoint data toggle to 0. | This bit always reads 0.                                        |  |  |  |  |  |

| 5    | STSTL                       | Sent Stall Bit.                                                                                                                                                                                                                                                       |                                                                                |                                                                 |  |  |  |  |  |

|      |                             |                                                                                                                                                                                                                                                                       | 1 when a STALL handshake s<br>Y bit cleared. This flag must be                 | signal is transmitted. The FIFO is a cleared by software.       |  |  |  |  |  |

| 4    | SDSTL                       | Send Stall.                                                                                                                                                                                                                                                           |                                                                                |                                                                 |  |  |  |  |  |

|      |                             |                                                                                                                                                                                                                                                                       |                                                                                | handshake in response to an IN ne STALL signal. This bit has no |  |  |  |  |  |

| 3    | FLUSH                       | FIFO Flush Bit.                                                                                                                                                                                                                                                       |                                                                                |                                                                 |  |  |  |  |  |

|      |                             | FIFO. The FIFO pointer                                                                                                                                                                                                                                                | nust write 1 to FLUSH for each                                                 | cleared. If the FIFO contains mul-                              |  |  |  |  |  |

| 2    | UNDRUN                      | Data Underrun Bit.                                                                                                                                                                                                                                                    |                                                                                |                                                                 |  |  |  |  |  |

|      |                             | The function of this bit depends on the IN Endpoint mode: ISO: Set when a zero-length packet is sent after an IN token is received while bit INPRDY = 0. Interrupt/Bulk: Set when a NAK is returned in response to an IN token. This bit must be cleared by software. |                                                                                |                                                                 |  |  |  |  |  |

| 1    | FIFONE                      | FIFO Not Empty.                                                                                                                                                                                                                                                       |                                                                                |                                                                 |  |  |  |  |  |

|      |                             | The IN Endpoint FIFO is empty.     The IN Endpoint FIFO contains one or more packets.                                                                                                                                                                                 |                                                                                |                                                                 |  |  |  |  |  |

| 0    | INPRDY                      | In Packet Ready.                                                                                                                                                                                                                                                      |                                                                                |                                                                 |  |  |  |  |  |

|      |                             | Hardware clears INPRD Double buffering is enable endpoint is in Isochronounext SOF is received.                                                                                                                                                                       | nabled) will be generated when hardware clears INPRDY as a result of a         |                                                                 |  |  |  |  |  |

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 24.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

Table 24.2. Minimum SDA Setup and Hold Times

| EXTHOLD | Minimum SDA Setup Time                                                  | Minimum SDA Hold Time |

|---------|-------------------------------------------------------------------------|-----------------------|

| 0       | T <sub>low</sub> – 4 system clocks<br>or<br>1 system clock + s/w delay* | 3 system clocks       |

| 1       | 11 system clocks                                                        | 12 system clocks      |

**Note:** Setup Time for ACK bit transmissions and the MSB of all data transfers. When using software acknowledgement, the s/w delay occurs between the time SMB0DAT or ACK is written and when SI is cleared. Note that if SI is cleared in the same write that defines the outgoing ACK value, s/w delay is zero.

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "24.3.4. SCL Low Timeout" on page 196). The SMBus interface will force Timer 3 to reload while SCL is high, and allow Timer 3 to count when SCL is low. The Timer 3 interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 24.4).

Table 24.3. Sources for Hardware Changes to SMB0CN

| Bit     | Set by Hardware When:                                                                                                                                                                                                                                                                                   | Cleared by Hardware When:                                                          |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| MASTER  | <ul><li>A START is generated.</li></ul>                                                                                                                                                                                                                                                                 | A STOP is generated.                                                               |

| MASTER  |                                                                                                                                                                                                                                                                                                         | Arbitration is lost.                                                               |

|         | ■ START is generated.                                                                                                                                                                                                                                                                                   | A START is detected.                                                               |

| TXMODE  | ■ SMB0DAT is written before the start of an                                                                                                                                                                                                                                                             | Arbitration is lost.                                                               |

| TAMODE  | SMBus frame.                                                                                                                                                                                                                                                                                            | <ul> <li>SMB0DAT is not written before the<br/>start of an SMBus frame.</li> </ul> |

| STA     | A START followed by an address byte is<br>received.                                                                                                                                                                                                                                                     | Must be cleared by software.                                                       |

| STO     | <ul><li>A STOP is detected while addressed as a slave.</li><li>Arbitration is lost due to a detected STOP.</li></ul>                                                                                                                                                                                    | A pending STOP is generated.                                                       |

| ACKRQ   | <ul> <li>A byte has been received and an ACK<br/>response value is needed (only when<br/>hardware ACK is not enabled).</li> </ul>                                                                                                                                                                       | After each ACK cycle.                                                              |

| ARBLOST | <ul> <li>A repeated START is detected as a MASTER when STA is low (unwanted repeated START).</li> <li>SCL is sensed low while attempting to generate a STOP or repeated START condition.</li> <li>SDA is sensed low while transmitting a 1</li> </ul>                                                   | ■ Each time SI is cleared.                                                         |

| ACK     | <ul><li>(excluding ACK bits).</li><li>The incoming ACK value is low (ACKNOWLEDGE).</li></ul>                                                                                                                                                                                                            | ■ The incoming ACK value is high (NOT ACKNOWLEDGE).                                |

| SI      | <ul> <li>A START has been generated.</li> <li>Lost arbitration.</li> <li>A byte has been transmitted and an ACK/NACK received.</li> <li>A byte has been received.</li> <li>A START or repeated START followed by a slave address + R/W has been received.</li> <li>A STOP has been received.</li> </ul> | ■ Must be cleared by software.                                                     |

#### 24.4.3. Hardware Slave Address Recognition

The SMBus hardware has the capability to automatically recognize incoming slave addresses and send an ACK without software intervention. Automatic slave address recognition is enabled by setting the EHACK bit in register SMB0ADM to 1. This will enable both automatic slave address recognition and automatic hardware ACK generation for received bytes (as a master or slave). More detail on automatic hardware ACK generation can be found in Section 24.4.2.2.

The registers used to define which address(es) are recognized by the hardware are the SMBus Slave Address register (SFR Definition 24.3) and the SMBus Slave Address Mask register (SFR Definition 24.4). A single address or range of addresses (including the General Call Address 0x00) can be specified using these two registers. The most-significant seven bits of the two registers are used to define which addresses will be ACKed. A 1 in bit positions of the slave address mask SLVM[6:0] enable a comparison between the received slave address and the hardware's slave address SLV[6:0] for those bits. A 0 in a bit of the slave address mask means that bit will be treated as a "don't care" for comparison purposes.

#### 26.3. Configuration and Operation

UART1 provides standard asynchronous, full duplex communication. It can operate in a point-to-point serial communications application, or as a node on a multi-processor serial interface. To operate in a point-to-point application, where there are only two devices on the serial bus, the MCE1 bit in SMOD1 should be cleared to 0. For operation as part of a multi-processor communications bus, the MCE1 and XBE1 bits should both be set to 1. In both types of applications, data is transmitted from the microcontroller on the TX1 pin, and received on the RX1 pin. The TX1 and RX1 pins are configured using the crossbar and the Port I/O registers, as detailed in Section "22. Port Input/Output" on page 138.

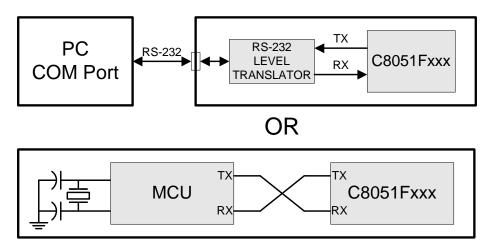

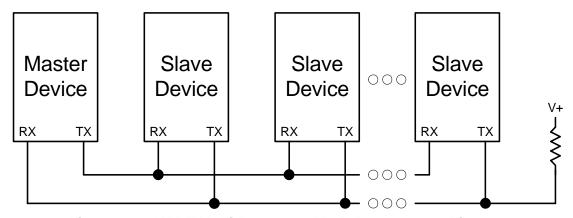

In typical UART communications, The transmit (TX) output of one device is connected to the receive (RX) input of the other device, either directly or through a bus transceiver, as shown in Figure 26.5.

Figure 26.5. Typical UART Interconnect Diagram

#### 26.3.1. Data Transmission

Data transmission is double-buffered, and begins when software writes a data byte to the SBUF1 register. Writing to SBUF1 places data in the Transmit Holding Register, and the Transmit Holding Register Empty flag (THRE1) will be cleared to 0. If the UARTs shift register is empty (i.e. no transmission is in progress) the data will be placed in the shift register, and the THRE1 bit will be set to 1. If a transmission is in progress, the data will remain in the Transmit Holding Register until the current transmission is complete. The TI1 Transmit Interrupt Flag (SCON1.1) will be set at the end of any transmission (the beginning of the stop-bit time). If enabled, an interrupt will occur when TI1 is set.

If the extra bit function is enabled (XBE1 = 1) and the parity function is disabled (PE1 = 0), the value of the TBX1 (SCON1.3) bit will be sent in the extra bit position. When the parity function is enabled (PE1 = 1), hardware will generate the parity bit according to the selected parity type (selected with S1PT[1:0]), and append it to the data field. Note: when parity is enabled, the extra bit function is not available.

#### 26.3.2. Data Reception

Data reception can begin any time after the REN1 Receive Enable bit (SCON1.4) is set to logic 1. After the stop bit is received, the data byte will be stored in the receive FIFO if the following conditions are met: the receive FIFO (3 bytes deep) must not be full, and the stop bit(s) must be logic 1. In the event that the receive FIFO is full, the incoming byte will be lost, and a Receive FIFO Overrun Error will be generated (OVR1 in register SCON1 will be set to logic 1). If the stop bit(s) were logic 0, the incoming data will not be stored in the receive FIFO. If the reception conditions are met, the data is stored in the receive FIFO, and the RI1 flag will be set. Note: when MCE1 = 1, RI1 will only be set if the extra bit was equal to 1. Data can be read from the receive FIFO by reading the SBUF1 register.

The SBUF1 register represents the oldest byte in the FIFO. After SBUF1 is read, the next byte in the FIFO is immediately loaded into SBUF1, and space is made available in the FIFO for another incoming byte. If enabled, an interrupt will occur when RI1 is set. RI1 can only be cleared to '0' by software when there is no more information in the FIFO. The recommended procedure to empty the FIFO contents is:

- 1. Clear RI1 to '0'

- 2. Read SBUF1

- 3. Check RI1, and repeat at Step 1 if RI1 is set to '1'.

If the extra bit function is enabled (XBE1 = 1) and the parity function is disabled (PE1 = 0), the extra bit for the oldest byte in the FIFO can be read from the RBX1 bit (SCON1.2). If the extra bit function is not enabled, the value of the stop bit for the oldest FIFO byte will be presented in RBX1. When the parity function is enabled (PE1 = 1), hardware will check the received parity bit against the selected parity type (selected with S1PT[1:0]) when receiving data. If a byte with parity error is received, the PERR1 flag will be set to 1. This flag must be cleared by software. Note: when parity is enabled, the extra bit function is not available.

#### 26.3.3. Multiprocessor Communications

UART1 supports multiprocessor communication between a master processor and one or more slave processors by special use of the extra data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its extra bit is logic 1; in a data byte, the extra bit is always set to logic 0.

Setting the MCE1 bit (SMOD1.7) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the extra bit is logic 1 (RBX1 = 1) signifying an address byte has been received. In the UART interrupt handler, software will compare the received address with the slave's own assigned address. If the addresses match, the slave will clear its MCE1 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE1 bits set and do not generate interrupts on the reception of the following data bytes, thereby ignoring the data. Once the entire message is received, the addressed slave resets its MCE1 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

Figure 26.6. UART Multi-Processor Mode Interconnect Diagram

**Table 27.1. SPI Slave Timing Parameters**

| Parameter         | Description                                   | Max                                                | Units                   |    |  |  |  |  |

|-------------------|-----------------------------------------------|----------------------------------------------------|-------------------------|----|--|--|--|--|

| Master Mode       | e Timing (See Figure 27.8 and Figure 27.9)    | 1                                                  |                         | I  |  |  |  |  |

| T <sub>MCKH</sub> | SCK High Time                                 | 1 x T <sub>SYSCLK</sub>                            | _                       | ns |  |  |  |  |

| T <sub>MCKL</sub> | SCK Low Time                                  | 1 x T <sub>SYSCLK</sub>                            | _                       | ns |  |  |  |  |

| T <sub>MIS</sub>  | MISO Valid to SCK Shift Edge                  | 1 x T <sub>SYSCLK</sub> + 20                       | _                       | ns |  |  |  |  |

| T <sub>MIH</sub>  | SCK Shift Edge to MISO Change                 | 0                                                  | _                       | ns |  |  |  |  |

| Slave Mode        | Timing (See Figure 27.10 and Figure 27.11)    | ,                                                  |                         |    |  |  |  |  |

| T <sub>SE</sub>   | NSS Falling to First SCK Edge                 | 2 x T <sub>SYSCLK</sub>                            | _                       | ns |  |  |  |  |

| T <sub>SD</sub>   | Last SCK Edge to NSS Rising                   | 2 x T <sub>SYSCLK</sub>                            | _                       | ns |  |  |  |  |

| T <sub>SEZ</sub>  | NSS Falling to MISO Valid                     | _                                                  | 4 x T <sub>SYSCLK</sub> | ns |  |  |  |  |

| T <sub>SDZ</sub>  | NSS Rising to MISO High-Z                     | _                                                  | 4 x T <sub>SYSCLK</sub> | ns |  |  |  |  |

| T <sub>CKH</sub>  | SCK High Time                                 | 5 x T <sub>SYSCLK</sub>                            | _                       | ns |  |  |  |  |

| T <sub>CKL</sub>  | SCK Low Time                                  | 5 x T <sub>SYSCLK</sub>                            | _                       | ns |  |  |  |  |

| T <sub>SIS</sub>  | MOSI Valid to SCK Sample Edge                 | 2 x T <sub>SYSCLK</sub>                            | _                       | ns |  |  |  |  |

| T <sub>SIH</sub>  | SCK Sample Edge to MOSI Change                | 2 x T <sub>SYSCLK</sub>                            | _                       | ns |  |  |  |  |

| T <sub>SOH</sub>  | SCK Shift Edge to MISO Change                 | _                                                  | 4 x T <sub>SYSCLK</sub> | ns |  |  |  |  |

| T <sub>SLH</sub>  | Last SCK Edge to MISO Change (CKPHA = 1 ONLY) | 6 x T <sub>SYSCLK</sub> 8 x T <sub>SYSCLK</sub> ns |                         |    |  |  |  |  |

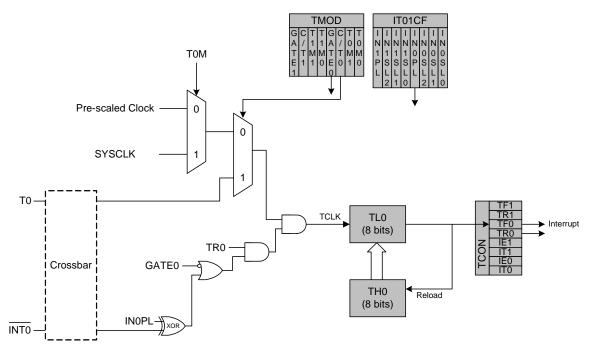

#### 28.1. Timer 0 and Timer 1

Each timer is implemented as a 16-bit register accessed as two separate bytes: a low byte (TL0 or TL1) and a high byte (TH0 or TH1). The Counter/Timer Control register (TCON) is used to enable Timer 0 and Timer 1 as well as indicate status. Timer 0 interrupts can be enabled by setting the ET0 bit in the IE register (Section "Note that the CPU is stalled during EPROM write operations and USB FIFO MOVX accesses (see Section "15.2.3. Accessing USB FIFO Space" on page 91). Interrupt service latency will be increased for interrupts occurring while the CPU is stalled. The latency for these situations will be determined by the standard interrupt service procedure (as described above) and the amount of time the CPU is stalled." on page 102); Timer 1 interrupts can be enabled by setting the ET1 bit in the IE register (Section "Note that the CPU is stalled during EPROM write operations and USB FIFO MOVX accesses (see Section "15.2.3. Accessing USB FIFO Space" on page 91). Interrupt service latency will be increased for interrupts occurring while the CPU is stalled. The latency for these situations will be determined by the standard interrupt service procedure (as described above) and the amount of time the CPU is stalled." on page 102). Both counter/timers operate in one of four primary modes selected by setting the Mode Select bits T1M1–T0M0 in the Counter/Timer Mode register (TMOD). Each timer can be configured independently. Each operating mode is described below.

#### 28.1.1. Mode 0: 13-bit Counter/Timer

Timer 0 and Timer 1 operate as 13-bit counter/timers in Mode 0. The following describes the configuration and operation of Timer 0. However, both timers operate identically, and Timer 1 is configured in the same manner as described for Timer 0.

The TH0 register holds the eight MSBs of the 13-bit counter/timer. TL0 holds the five LSBs in bit positions TL0.4–TL0.0. The three upper bits of TL0 (TL0.7–TL0.5) are indeterminate and should be masked out or ignored when reading. As the 13-bit timer register increments and overflows from 0x1FFF (all ones) to 0x0000, the timer overflow flag TF0 in TCON is set and an interrupt will occur if Timer 0 interrupts are enabled.

The C/T0 bit in the TMOD register selects the counter/timer's clock source. When C/T0 is set to logic 1, high-to-low transitions at the selected Timer 0 input pin (T0) increment the timer register (Refer to Section "22.3. Priority Crossbar Decoder" on page 142 for information on selecting and configuring external I/O pins). Clearing C/T selects the clock defined by the T0M bit in register CKCON. When T0M is set, Timer 0 is clocked by the source selected by the Clock Scale bits in CKCON (see SFR Definition 28.1).

Setting the TR0 bit (TCON.4) enables the timer when either GATE0 in the TMOD register is logic 0 or the input signal INT0 is active as defined by bit IN0PL in register IT01CF (see SFR Definition 17.7). Setting GATE0 to 1 allows the timer to be controlled by the external input signal INT0 (see Section "Note that the CPU is stalled during EPROM write operations and USB FIFO MOVX accesses (see Section "15.2.3. Accessing USB FIFO Space" on page 91). Interrupt service latency will be increased for interrupts occurring while the CPU is stalled. The latency for these situations will be determined by the standard interrupt service procedure (as described above) and the amount of time the CPU is stalled." on page 102), facilitating pulse width measurements

| TR0             | GATE0 | INT0 | Counter/Timer |

|-----------------|-------|------|---------------|

| 0               | Х     | Х    | Disabled      |

| 1               | 0     | Х    | Enabled       |

| 1               | 1     | 0    | Disabled      |

| 1               | 1     | 1    | Enabled       |

| Note: X = Don't | Care  |      |               |

Figure 28.2. T0 Mode 2 Block Diagram

#### 28.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates or overflow conditions for other peripherals. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

### SFR Definition 28.2. TCON: Timer Control

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name  | TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

| Туре  | R/W |

| Reset | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Address = 0x88; Bit-Addressable

| Bit | Name | Function                                                                                                                                                                                                                                                   |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF1  | Timer 1 Overflow Flag.  Set to 1 by hardware when Timer 1 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 1 interrupt service routine.                                                      |

| 6   | TR1  | Timer 1 Run Control.                                                                                                                                                                                                                                       |

|     |      | Timer 1 is enabled by setting this bit to 1.                                                                                                                                                                                                               |

| 5   | TF0  | Timer 0 Overflow Flag.                                                                                                                                                                                                                                     |

|     |      | Set to 1 by hardware when Timer 0 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine.                                                                              |

| 4   | TR0  | Timer 0 Run Control.                                                                                                                                                                                                                                       |

|     |      | Timer 0 is enabled by setting this bit to 1.                                                                                                                                                                                                               |

| 3   | IE1  | External Interrupt 1.                                                                                                                                                                                                                                      |

|     |      | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 1 service routine in edge-triggered mode.                    |

| 2   | IT1  | Interrupt 1 Type Select.                                                                                                                                                                                                                                   |

|     |      | This bit selects whether the configured INT1 interrupt will be edge or level sensitive.  INT1 is configured active low or high by the IN1PL bit in the IT01CF register (see SFR Definition 17.7).  0: INT1 is level triggered.  1: INT1 is edge triggered. |

| 1   | IE0  | External Interrupt 0.                                                                                                                                                                                                                                      |

|     |      | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 0 service routine in edge-triggered mode.                    |

| 0   | IT0  | Interrupt 0 Type Select.                                                                                                                                                                                                                                   |

|     |      | This bit selects whether the configured INT0 interrupt will be edge or level sensitive. INT0 is configured active low or high by the IN0PL bit in register IT01CF (see SFR Definition 17.7).  0: INT0 is level triggered.  1: INT0 is edge triggered.      |

Table 29.2. PCA0CPM and PCA0PWM Bit Settings for PCA Capture/Compare Modules

| Operational Mode                            |   |   | PCA0CPMn PCA0PWM |   |   |   |   |   |   |   |   |     |     |

|---------------------------------------------|---|---|------------------|---|---|---|---|---|---|---|---|-----|-----|

| Bit Number                                  |   | 6 | 5                | 4 | 3 | 2 | 1 | 0 | 7 | 6 | 5 | 4-2 | 1-0 |

| Capture triggered by positive edge on CEXn  | Х | Χ | 1                | 0 | 0 | 0 | 0 | Α | 0 | Χ | В | XXX | XX  |

| Capture triggered by negative edge on CEXn  | Х | Х | 0                | 1 | 0 | 0 | 0 | Α | 0 | Х | В | XXX | XX  |

| Capture triggered by any transition on CEXn | Х | Х | 1                | 1 | 0 | 0 | 0 | Α | 0 | Χ | В | XXX | XX  |

| Software Timer                              |   | С | 0                | 0 | 1 | 0 | 0 | Α | 0 | Х | В | XXX | XX  |

| High Speed Output                           | Х | С | 0                | 0 | 1 | 1 | 0 | Α | 0 | Χ | В | XXX | XX  |

| Frequency Output                            | Х | С | 0                | 0 | 0 | 1 | 1 | Α | 0 | Χ | В | XXX | XX  |

| 8-Bit Pulse Width Modulator (Note 7)        |   | С | 0                | 0 | Е | 0 | 1 | Α | 0 | Х | В | XXX | 00  |

| 9-Bit Pulse Width Modulator (Note 7)        |   | С | 0                | 0 | Е | 0 | 1 | Α | D | Х | В | XXX | 01  |

| 10-Bit Pulse Width Modulator (Note 7)       | 0 | С | 0                | 0 | Е | 0 | 1 | Α | D | Χ | В | XXX | 10  |

| 11-Bit Pulse Width Modulator (Note 7)       | 0 | С | 0                | 0 | Е | 0 | 1 | Α | D | Х | В | XXX | 11  |

| 16-Bit Pulse Width Modulator                |   | С | 0                | 0 | Е | 0 | 1 | Α | 0 | Х | В | XXX | XX  |

- 1. X = Don't Care (no functional difference for individual module if 1 or 0).

- 2. A = Enable interrupts for this module (PCA interrupt triggered on CCFn set to 1).

- 3. B = Enable 8th, 9th, 10th or 11th bit overflow interrupt (Depends on setting of CLSEL[1:0]).

- **4.** C = When set to 0, the digital comparator is off. For high speed and frequency output modes, the associated pin will not toggle. In any of the PWM modes, this generates a 0% duty cycle (output = 0).

- **5.** D = Selects whether the Capture/Compare register (0) or the Auto-Reload register (1) for the associated channel is accessed via addresses PCA0CPHn and PCA0CPLn.

- **6.** E = When set, a match event will cause the CCFn flag for the associated channel to be set.

- 7. All modules set to 8, 9, 10 or 11-bit PWM mode use the same cycle length setting.

#### 29.3.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes the PCA to capture the value of the PCA counter/timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. If both CAPPn and CAPNn bits are set to logic 1, then the state of the Port pin associated with CEXn can be read directly to determine whether a rising-edge or falling-edge caused the capture.