$\times$ FI

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Detailo                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                   |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | 10000                                                                      |

| Total RAM Bits                 | 221184                                                                     |

| Number of I/O                  | 244                                                                        |

| Number of Gates                | -                                                                          |

| Voltage - Supply               | 1.14V ~ 1.26V                                                              |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 388-BBGA                                                                   |

| Supplier Device Package        | 388-FPBGA (23x23)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfxp10e-3fn388i |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# LatticeXP Family Data Sheet Introduction

#### July 2007

### **Features**

#### ■ Non-volatile, Infinitely Reconfigurable

- Instant-on powers up in microseconds

- No external configuration memory

- Excellent design security, no bit stream to intercept

- Reconfigure SRAM based logic in milliseconds

- SRAM and non-volatile memory programmable through system configuration and JTAG ports

- Sleep Mode

- Allows up to 1000x static current reduction

- TransFR<sup>™</sup> Reconfiguration (TFR)

In-field logic update while system operates

- Extensive Density and Package Options

- 3.1K to 19.7K LUT4s

- 62 to 340 I/Os

- Density migration supported

#### Embedded and Distributed Memory

- 54 Kbits to 396 Kbits sysMEM<sup>™</sup> Embedded Block RAM

- Up to 79 Kbits distributed RAM

- Flexible memory resources:

- Distributed and block memory

#### ■ Flexible I/O Buffer

• Programmable sysIO<sup>™</sup> buffer supports wide range of interfaces:

Data Sheet DS1001

- LVCMOS 3.3/2.5/1.8/1.5/1.2

- LVTTL

- SSTL 18 Class I

- SSTL 3/2 Class I, II

- HSTL15 Class I, III

- HSTL 18 Class I, II, III

- PCI

- LVDS, Bus-LVDS, LVPECL, RSDS

- Dedicated DDR Memory Support

- Implements interface up to DDR333 (166MHz)

#### ■ sysCLOCK<sup>™</sup> PLLs

- Up to 4 analog PLLs per device

- Clock multiply, divide and phase shifting

- System Level Support

- IEEE Standard 1149.1 Boundary Scan, plus ispTRACY™ internal logic analyzer capability

- Onboard oscillator for configuration

- Devices operate with 3.3V, 2.5V, 1.8V or 1.2V power supply

| Device                       | LFXP3            | LFXP6            | LFXP10           | LFXP15           | LFXP20           |

|------------------------------|------------------|------------------|------------------|------------------|------------------|

| PFU/PFF Rows                 | 16               | 24               | 32               | 40               | 44               |

| PFU/PFF Columns              | 24               | 30               | 38               | 48               | 56               |

| PFU/PFF (Total)              | 384              | 720              | 1216             | 1932             | 2464             |

| LUTs (K)                     | 3                | 6                | 10               | 15               | 20               |

| Distributed RAM (KBits)      | 12               | 23               | 39               | 61               | 79               |

| EBR SRAM (KBits)             | 54               | 72               | 216              | 324              | 396              |

| EBR SRAM Blocks              | 6                | 8                | 24               | 36               | 44               |

| V <sub>CC</sub> Voltage      | 1.2/1.8/2.5/3.3V | 1.2/1.8/2.5/3.3V | 1.2/1.8/2.5/3.3V | 1.2/1.8/2.5/3.3V | 1.2/1.8/2.5/3.3V |

| PLLs                         | 2                | 2                | 4                | 4                | 4                |

| Max. I/O                     | 136              | 188              | 244              | 300              | 340              |

| Packages and I/O Combination | ons:             |                  |                  |                  |                  |

| 100-pin TQFP (14 x 14 mm)    | 62               |                  |                  |                  |                  |

| 144-pin TQFP (20 x 20 mm)    | 100              | 100              |                  |                  |                  |

| 208-pin PQFP (28 x 28 mm)    | 136              | 142              |                  |                  |                  |

| 256-ball fpBGA (17 x 17 mm)  |                  | 188              | 188              | 188              | 188              |

| 388-ball fpBGA (23 x 23 mm)  |                  |                  | 244              | 268              | 268              |

| 484-ball fpBGA (23 x 23 mm)  |                  |                  |                  | 300              | 340              |

#### Table 1-1. LatticeXP Family Selection Guide

© 2007 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# LatticeXP Family Data Sheet Architecture

July 2007

Data Sheet DS1001

### **Architecture Overview**

The LatticeXP architecture contains an array of logic blocks surrounded by Programmable I/O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM Embedded Block RAM (EBR) as shown in Figure 2-1.

On the left and right sides of the PFU array, there are Non-volatile Memory Blocks. In configuration mode this nonvolatile memory is programmed via the IEEE 1149.1 TAP port or the sysCONFIG<sup>™</sup> peripheral port. On power up, the configuration data is transferred from the Non-volatile Memory Blocks to the configuration SRAM. With this technology, expensive external configuration memories are not required and designs are secured from unauthorized read-back. This transfer of data from non-volatile memory to configuration SRAM via wide busses happens in microseconds, providing an "instant-on" capability that allows easy interfacing in many applications.

There are two kinds of logic blocks, the Programmable Functional Unit (PFU) and Programmable Functional unit without RAM/ROM (PFF). The PFU contains the building blocks for logic, arithmetic, RAM, ROM and register functions. The PFF block contains building blocks for logic, arithmetic and ROM functions. Both PFU and PFF blocks are optimized for flexibility, allowing complex designs to be implemented quickly and efficiently. Logic Blocks are arranged in a two-dimensional array. Only one type of block is used per row. The PFU blocks are used on the outside rows. The rest of the core consists of rows of PFF blocks interspersed with rows of PFU blocks. For every three rows of PFF blocks there is a row of PFU blocks.

Each PIC block encompasses two PIOs (PIO pairs) with their respective sysIO interfaces. PIO pairs on the left and right edges of the device can be configured as LVDS transmit/receive pairs. sysMEM EBRs are large dedicated fast memory blocks. They can be configured as RAM or ROM.

The PFU, PFF, PIC and EBR Blocks are arranged in a two-dimensional grid with rows and columns as shown in Figure 2-1. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

At the end of the rows containing the sysMEM Blocks are the sysCLOCK Phase Locked Loop (PLL) Blocks. These PLLs have multiply, divide and phase shifting capability; they are used to manage the phase relationship of the clocks. The LatticeXP architecture provides up to four PLLs per device.

Every device in the family has a JTAG Port with internal Logic Analyzer (ispTRACY) capability. The sysCONFIG port which allows for serial or parallel device configuration. The LatticeXP devices are available for operation from 3.3V, 2.5V, 1.8V and 1.2V power supplies, providing easy integration into the overall system.

<sup>© 2007</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

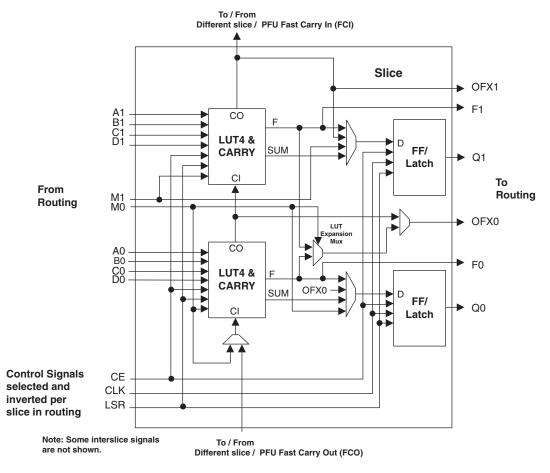

#### Slice

Each slice contains two LUT4 lookup tables feeding two registers (programmed to be in FF or Latch mode), and some associated logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/asynchronous), clock select, chip-select and wider RAM/ROM functions. Figure 2-3 shows an overview of the internal logic of the slice. The registers in the slice can be configured for positive/negative and edge/level clocks.

There are 14 input signals: 13 signals from routing and one from the carry-chain (from adjacent slice or PFU). There are 7 outputs: 6 to routing and one to carry-chain (to adjacent PFU). Table 2-1 lists the signals associated with each slice.

#### Figure 2-3. Slice Diagram

| Function | Туре             | Signal Names   | Description                                                          |

|----------|------------------|----------------|----------------------------------------------------------------------|

| Input    | Data signal      | A0, B0, C0, D0 | Inputs to LUT4                                                       |

| Input    | Data signal      | A1, B1, C1, D1 | Inputs to LUT4                                                       |

| Input    | Multi-purpose    | MO             | Multipurpose Input                                                   |

| Input    | Multi-purpose    | M1             | Multipurpose Input                                                   |

| Input    | Control signal   | CE             | Clock Enable                                                         |

| Input    | Control signal   | LSR            | Local Set/Reset                                                      |

| Input    | Control signal   | CLK            | System Clock                                                         |

| Input    | Inter-PFU signal | FCIN           | Fast Carry In <sup>1</sup>                                           |

| Output   | Data signals     | F0, F1         | LUT4 output register bypass signals                                  |

| Output   | Data signals     | Q0, Q1         | Register Outputs                                                     |

| Output   | Data signals     | OFX0           | Output of a LUT5 MUX                                                 |

| Output   | Data signals     | OFX1           | Output of a LUT6, LUT7, LUT8 <sup>2</sup> MUX depending on the slice |

| Output   | Inter-PFU signal | FCO            | For the right most PFU the fast carry chain output <sup>1</sup>      |

#### Table 2-1. Slice Signal Descriptions

1. See Figure 2-2 for connection details.

2. Requires two PFUs.

#### Modes of Operation

Each Slice is capable of four modes of operation: Logic, Ripple, RAM and ROM. The Slice in the PFF is capable of all modes except RAM. Table 2-2 lists the modes and the capability of the Slice blocks.

#### Table 2-2. Slice Modes

|           | Logic              | Ripple                | RAM     | ROM          |

|-----------|--------------------|-----------------------|---------|--------------|

| PFU Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | SP 16x2 | ROM 16x1 x 2 |

| PFF Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | N/A     | ROM 16x1 x 2 |

**Logic Mode:** In this mode, the LUTs in each Slice are configured as 4-input combinatorial lookup tables. A LUT4 can have 16 possible input combinations. Any logic function with four inputs can be generated by programming this lookup table. Since there are two LUT4s per Slice, a LUT5 can be constructed within one Slice. Larger lookup tables such as LUT6, LUT7 and LUT8 can be constructed by concatenating other Slices.

**Ripple Mode:** Ripple mode allows the efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each Slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Ripple mode multiplier building block

- Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Two additional signals: Carry Generate and Carry Propagate are generated per Slice in this mode, allowing fast arithmetic functions to be constructed by concatenating Slices.

**RAM Mode:** In this mode, distributed RAM can be constructed using each LUT block as a 16x1-bit memory. Through the combination of LUTs and Slices, a variety of different memories can be constructed.

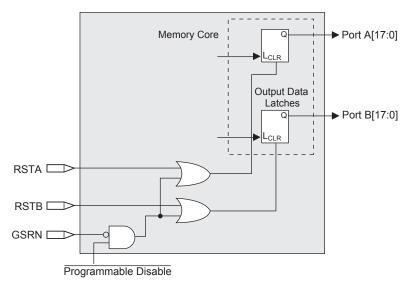

#### Figure 2-15. Memory Core Reset

For further information on sysMEM EBR block, see the details of additional technical documentation at the end of this data sheet.

#### EBR Asynchronous Reset

EBR asynchronous reset or GSR (if used) can only be applied if all clock enables are low for a clock cycle before the reset is applied and released a clock cycle after the reset is released, as shown in Figure 2-16. The GSR input to the EBR is always asynchronous.

#### Figure 2-16. EBR Asynchronous Reset (Including GSR) Timing Diagram

| Reset           |  |

|-----------------|--|

| Clock           |  |

| Clock<br>Enable |  |

If all clock enables remain enabled, the EBR asynchronous reset or GSR may only be applied and released after the EBR read and write clock inputs are in a steady state condition for a minimum of  $1/f_{MAX}$  (EBR clock). The reset release must adhere to the EBR synchronous reset setup time before the next active read or write clock edge.

If an EBR is pre-loaded during configuration, the GSR input must be disabled or the release of the GSR during device Wake Up must occur before the release of the device I/Os becoming active.

These instructions apply to all EBR RAM and ROM implementations.

Note that there are no reset restrictions if the EBR synchronous reset is used and the EBR GSR input is disabled.

### Programmable I/O Cells (PICs)

Each PIC contains two PIOs connected to their respective sysIO Buffers which are then connected to the PADs as shown in Figure 2-17. The PIO Block supplies the output data (DO) and the Tri-state control signal (TO) to sysIO buffer, and receives input from the buffer.

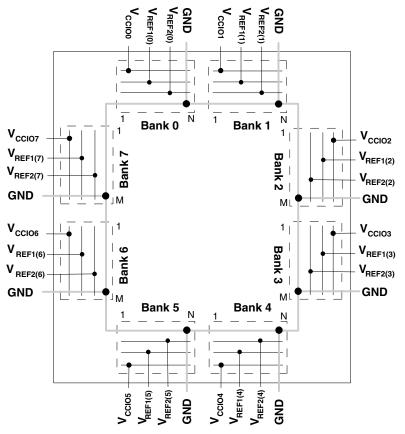

#### Figure 2-28. LatticeXP Banks

Note: N and M are the maximum number of I/Os per bank.

LatticeXP devices contain two types of sysIO buffer pairs.

#### 1. Top and Bottom sysIO Buffer Pair (Single-Ended Outputs Only)

The sysIO buffer pairs in the top and bottom banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (both ratioed and referenced). The referenced input buffer can also be configured as a differential input.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential input buffer and the comp (complementary) pad is associated with the negative side of the differential input buffer.

Only the I/Os on the top and bottom banks have PCI clamps. Note that the PCI clamp is enabled after  $V_{CC,}$   $V_{CCAUX}$  and  $V_{CCIO}$  are at valid operating levels and the device has been configured.

#### 2. Left and Right sysIO Buffer Pair (Differential and Single-Ended Outputs)

The sysIO buffer pairs in the left and right banks of the device consist of two single-ended output drivers, two sets of single-ended input buffers (both ratioed and referenced) and one differential output driver. The referenced input buffer can also be configured as a differential input. In these banks the two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential I/O, and the comp (complementary) pad is associated with the negative side of the differential I/O.

Select I/Os in the left and right banks have LVDS differential output drivers. Refer to the Logic Signal Connections tables for more information.

| Table 2-8. Supported | d Output Standards |

|----------------------|--------------------|

|----------------------|--------------------|

| Output Standard                       | Drive                      | V <sub>CCIO</sub> (Nom.) |

|---------------------------------------|----------------------------|--------------------------|

| Single-ended Interfaces               | · · ·                      |                          |

| LVTTL                                 | 4mA, 8mA, 12mA, 16mA, 20mA | 3.3                      |

| LVCMOS33                              | 4mA, 8mA, 12mA 16mA, 20mA  | 3.3                      |

| LVCMOS25                              | 4mA, 8mA, 12mA 16mA, 20mA  | 2.5                      |

| LVCMOS18                              | 4mA, 8mA, 12mA 16mA        | 1.8                      |

| LVCMOS15                              | 4mA, 8mA                   | 1.5                      |

| LVCMOS12                              | 2mA, 6mA                   | 1.2                      |

| LVCMOS33, Open Drain                  | 4mA, 8mA, 12mA 16mA, 20mA  | —                        |

| LVCMOS25, Open Drain                  | 4mA, 8mA, 12mA 16mA, 20mA  | —                        |

| LVCMOS18, Open Drain                  | 4mA, 8mA, 12mA 16mA        | _                        |

| LVCMOS15, Open Drain                  | 4mA, 8mA                   | _                        |

| LVCMOS12, Open Drain                  | 2mA. 6mA                   | —                        |

| PCI33                                 | N/A                        | 3.3                      |

| HSTL18 Class I, II, III               | N/A                        | 1.8                      |

| HSTL15 Class I, III                   | N/A                        | 1.5                      |

| SSTL3 Class I, II                     | N/A                        | 3.3                      |

| SSTL2 Class I, II                     | N/A                        | 2.5                      |

| SSTL18 Class I                        | N/A                        | 1.8                      |

| Differential Interfaces               | · · ·                      |                          |

| Differential SSTL3, Class I, II       | N/A                        | 3.3                      |

| Differential SSTL2, Class I, II       | N/A                        | 2.5                      |

| Differential SSTL18, Class I          | N/A                        | 1.8                      |

| Differential HSTL18, Class I, II, III | N/A                        | 1.8                      |

| Differential HSTL15, Class I, III     | N/A                        | 1.5                      |

| LVDS                                  | N/A                        | 2.5                      |

| BLVDS <sup>1</sup>                    | N/A                        | 2.5                      |

| LVPECL <sup>1</sup>                   | N/A                        | 3.3                      |

1. Emulated with external resistors.

### Hot Socketing

The LatticeXP devices have been carefully designed to ensure predictable behavior during power-up and powerdown. Power supplies can be sequenced in any order. During power up and power-down sequences, the I/Os remain in tristate until the power supply voltage is high enough to ensure reliable operation. In addition, leakage into I/O pins is controlled to within specified limits, which allows easy integration with the rest of the system. These capabilities make the LatticeXP ideal for many multiple power supply and hot-swap applications.

## Sleep Mode

The LatticeXP "C" devices ( $V_{CC} = 1.8/2.5/3.3V$ ) have a sleep mode that allows standby current to be reduced by up to three orders of magnitude during periods of system inactivity. Entry and exit to Sleep Mode is controlled by the SLEEPN pin.

During Sleep Mode, the FPGA logic is non-operational, registers and EBR contents are not maintained and I/Os are tri-stated. Do not enter Sleep Mode during device programming or configuration operation. In Sleep Mode, power supplies can be maintained in their normal operating range, eliminating the need for external switching of power supplies. Table 2-9 compares the characteristics of Normal, Off and Sleep Modes.

# sysIO Recommended Operating Conditions

|                     | V <sub>CCIO</sub> |      |       |       | V <sub>REF</sub> (V) |       |

|---------------------|-------------------|------|-------|-------|----------------------|-------|

| Standard            | Min.              | Тур. | Max.  | Min.  | Тур.                 | Max.  |

| LVCMOS 3.3          | 3.135             | 3.3  | 3.465 | —     | —                    | —     |

| LVCMOS 2.5          | 2.375             | 2.5  | 2.625 | —     | —                    | —     |

| LVCMOS 1.8          | 1.71              | 1.8  | 1.89  | —     | —                    | —     |

| LVCMOS 1.5          | 1.425             | 1.5  | 1.575 | —     | —                    | —     |

| LVCMOS 1.2          | 1.14              | 1.2  | 1.26  | —     | —                    | —     |

| LVTTL               | 3.135             | 3.3  | 3.465 | —     | —                    | —     |

| PCI33               | 3.135             | 3.3  | 3.465 | —     | —                    | —     |

| SSTL18 Class I      | 1.71              | 1.8  | 1.89  | 0.833 | 0.9                  | 0.969 |

| SSTL2 Class I, II   | 2.375             | 2.5  | 2.625 | 1.15  | 1.25                 | 1.35  |

| SSTL3 Class I, II   | 3.135             | 3.3  | 3.465 | 1.3   | 1.5                  | 1.7   |

| HSTL15 Class I      | 1.425             | 1.5  | 1.575 | 0.68  | 0.75                 | 0.9   |

| HSTL15 Class III    | 1.425             | 1.5  | 1.575 | —     | 0.9                  | —     |

| HSTL 18 Class I, II | 1.71              | 1.8  | 1.89  | —     | 0.9                  | —     |

| HSTL 18 Class III   | 1.71              | 1.8  | 1.89  | —     | 1.08                 | —     |

| LVDS                | 2.375             | 2.5  | 2.625 | —     | —                    | —     |

| LVPECL <sup>1</sup> | 3.135             | 3.3  | 3.465 | —     | —                    | —     |

| BLVDS <sup>1</sup>  | 2.375             | 2.5  | 2.625 | —     | —                    | —     |

1. Inputs on chip. Outputs are implemented with the addition of external resistors.

### sysIO Single-Ended DC Electrical Characteristics

| Input/Output     | V <sub>IL</sub> |                          | V <sub>IH</sub>          |          | V <sub>OL</sub> Max. | V <sub>OH</sub> Min.     | I <sub>OL</sub>     | I <sub>ОН</sub>          |

|------------------|-----------------|--------------------------|--------------------------|----------|----------------------|--------------------------|---------------------|--------------------------|

| Standard         | Min. (V)        | Max. (V)                 | Min. (V)                 | Max. (V) | (V)                  | (V)                      | (mA)                | (mA)                     |

| LVCMOS 3.3       | -0.3            | 0.8                      | 2.0                      | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 20, 16, 12,<br>8, 4 | -20, -16, -12,<br>-8, -4 |

|                  |                 |                          |                          |          | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                 | -0.1                     |

| LVTTL            | -0.3            | 0.8                      | 2.0                      | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 20, 16, 12,<br>8, 4 | -20, -16, -12,<br>-8, -4 |

|                  |                 |                          |                          |          | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                 | -0.1                     |

| LVCMOS 2.5       | -0.3            | 0.7                      | 1.7                      | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 20, 16, 12,<br>8, 4 | -20, -16, -12,<br>-8, -4 |

|                  |                 |                          |                          |          | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                 | -0.1                     |

| LVCMOS 1.8       | -0.3            | 0.35V <sub>CCIO</sub>    | 0.65V <sub>CCIO</sub>    | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 16, 12, 8, 4        | -16, -12, -8, -4         |

|                  | -0.5            | 0.32 A CCIO              | 0.03 A CCIO              | 5.0      | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                 | -0.1                     |

| LVCMOS 1.5       | -0.3            | 0.35V <sub>CCIO</sub>    | 0.65V <sub>CCIO</sub>    | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 8, 4                | -8, -4                   |

| 2000001.5        | -0.5            | 0.00 0.00                | 0.0340000                | 0.0      | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                 | -0.1                     |

| LVCMOS 1.2       | -0.3            | 0.42                     | 0.78                     | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 6, 2                | -6, -2                   |

| ("C" Version)    | -0.5            | 0.42                     | 0.70                     | 0.0      | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                 | -0.1                     |

| LVCMOS 1.2       | -0.3            | 0.35V <sub>CC</sub>      | 0.65V <sub>CC</sub>      | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 6, 2                | -6, -2                   |

| ("E" Version)    | -0.5            |                          |                          | 0.0      | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                 | -0.1                     |

| PCI              | -0.3            | 0.3V <sub>CCIO</sub>     | 0.5V <sub>CCIO</sub>     | 3.6      | $0.1V_{CCIO}$        | 0.9V <sub>CCIO</sub>     | 1.5                 | -0.5                     |

| SSTL3 class I    | -0.3            | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 3.6      | 0.7                  | V <sub>CCIO</sub> - 1.1  | 8                   | -8                       |

| SSTL3 class II   | -0.3            | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 3.6      | 0.5                  | V <sub>CCIO</sub> - 0.9  | 16                  | -16                      |

| SSTL2 class I    | -0.3            | V <sub>REF</sub> - 0.18  | V <sub>REF</sub> + 0.18  | 3.6      | 0.54                 | V <sub>CCIO</sub> - 0.62 | 7.6                 | -7.6                     |

| SSTL2 class II   | -0.3            | V <sub>REF</sub> - 0.18  | V <sub>REF</sub> + 0.18  | 3.6      | 0.35                 | V <sub>CCIO</sub> - 0.43 | 15.2                | -15.2                    |

| SSTL18 class I   | -0.3            | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 6.7                 | -6.7                     |

| HSTL15 class I   | -0.3            | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 8                   | -8                       |

| HSTL15 class III | -0.3            | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 24                  | -8                       |

| HSTL18 class I   | -0.3            | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 9.6                 | -9.6                     |

| HSTL18 class II  | -0.3            | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 16                  | -16                      |

| HSTL18 class III | -0.3            | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 24                  | -8                       |

1. The average DC current drawn by I/Os between GND connections, or between the last GND in an I/O bank and the end of an I/O bank, as shown in the logic signal connections table shall not exceed n \* 8mA. Where n is the number of I/Os between bank GND connections or between the last GND in a bank and the end of a bank.

### **Differential HSTL and SSTL**

Differential HSTL and SSTL outputs are implemented as a pair of complementary single-ended outputs. All allowable single-ended output classes (class I and class II) are supported in this mode.

### LVDS25E

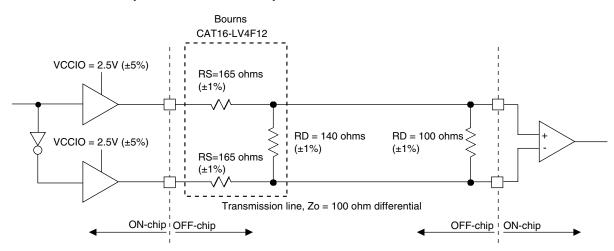

The top and bottom side of LatticeXP devices support LVDS outputs via emulated complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The scheme shown in Figure 3-1 is one possible solution for point-to-point signals.

Figure 3-1. LVDS25E Output Termination Example

#### Table 3-1. LVDS25E DC Conditions

| Parameter         | Description                 | Typical | Units |

|-------------------|-----------------------------|---------|-------|

| V <sub>OH</sub>   | Output high voltage         | 1.43    | V     |

| V <sub>OL</sub>   | Output low voltage          | 1.07    | V     |

| V <sub>OD</sub>   | Output differential voltage | 0.35    | V     |

| V <sub>CM</sub>   | Output common mode voltage  | 1.25    | V     |

| Z <sub>BACK</sub> | Back impedance              | 100     | ohms  |

| I <sub>DC</sub>   | DC output current           | 3.66    | mA    |

#### BLVDS

The LatticeXP devices support BLVDS standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel external resistor across the driver outputs. BLVDS is intended for use when multidrop and bi-directional multi-point differential signaling is required. The scheme shown in Figure 3-2 is one possible solution for bi-directional multi-point differential signals.

### LatticeXP External Switching Characteristics

|                       |                                                                   |                        | -     | 5    | -     | 4    | -     | 3    |          |

|-----------------------|-------------------------------------------------------------------|------------------------|-------|------|-------|------|-------|------|----------|

| Parameter             | Description                                                       | Device                 | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units    |

| General I/C           | Pin Parameters (Using Primary Clock wit                           | hout PLL) <sup>1</sup> |       |      |       |      |       |      |          |

|                       |                                                                   | LFXP3                  |       | 5.12 |       | 6.12 | _     | 7.43 | ns       |

|                       |                                                                   | LFXP6                  | —     | 5.30 | —     | 6.34 | -     | 7.69 | ns       |

| t <sub>CO</sub>       | Clock to Output - PIO Output Register                             | LFXP10                 | _     | 5.52 |       | 6.60 | —     | 8.00 | ns       |

|                       |                                                                   | LFXP15                 | _     | 5.72 |       | 6.84 | —     | 8.29 | ns       |

|                       |                                                                   | LFXP20                 | —     | 5.97 | —     | 7.14 | -     | 8.65 | ns       |

|                       |                                                                   | LFXP3                  | -0.40 | —    | -0.28 | —    | -0.16 | —    | ns       |

|                       |                                                                   | LFXP6                  | -0.33 | —    | -0.32 | —    | -0.30 | —    | ns       |

| t <sub>SU</sub>       | Clock to Data Setup - PIO Input Register                          | LFXP10                 | -0.61 | —    | -0.71 | —    | -0.81 | —    | ns       |

|                       |                                                                   | LFXP15                 | -0.71 |      | -0.77 | _    | -0.87 | _    | ns       |

|                       |                                                                   | LFXP20                 | -0.95 |      | -1.14 | _    | -1.35 | _    | ns       |

|                       |                                                                   | LFXP3                  | 2.10  |      | 2.50  | _    | 2.98  | _    | ns       |

|                       |                                                                   | LFXP6                  | 2.28  | —    | 2.72  | —    | 3.24  | —    | ns       |

| t <sub>H</sub>        | Clock to Data Hold - PIO Input Register                           | LFXP10                 | 3.02  | —    | 3.51  | —    | 3.71  | —    | ns       |

|                       |                                                                   | LFXP15                 | 2.70  |      | 3.22  | —    | 3.85  | —    | ns       |

|                       |                                                                   | LFXP20                 | 2.95  | _    | 3.52  | —    | 4.21  | _    | ns       |

|                       | Clock to Data Setup - PIO Input Register<br>with Input Data Delay | LFXP3                  | 2.38  |      | 2.49  | —    | 2.66  | —    | ns       |

|                       |                                                                   | LFXP6                  | 2.92  |      | 3.18  | —    | 3.42  | —    | ns       |

| t <sub>SU_DEL</sub>   |                                                                   | LFXP10                 | 2.72  | _    | 2.75  | —    | 2.84  | _    | ns       |

|                       |                                                                   | LFXP15                 | 2.99  |      | 3.13  | —    | 3.18  | —    | ns       |

|                       |                                                                   | LFXP20                 | 4.47  | _    | 4.56  | —    | 4.80  | —    | ns       |

|                       |                                                                   | LFXP3                  | -0.70 | _    | -0.80 | —    | -0.92 | _    | ns       |

|                       |                                                                   | LFXP6                  | -0.47 |      | -0.38 | —    | -0.31 | —    | ns       |

| t <sub>H_DEL</sub>    | Clock to Data Hold - PIO Input Register with<br>Input Data Delay  | LFXP10                 | -0.60 |      | -0.47 | —    | -0.32 | —    | ns       |

|                       |                                                                   | LFXP15                 | -1.05 | —    | -0.98 | —    | -1.01 | _    | ns       |

|                       |                                                                   | LFXP20                 | -0.80 | _    | -0.58 | —    | -0.31 | _    | ns       |

| f <sub>MAX_IO</sub>   | Clock Frequency of I/O and PFU Register                           | All                    | —     | 400  | _     | 360  | —     | 320  | MHz      |

|                       | n Parameters <sup>2</sup>                                         |                        | I     | l    | l     | I    |       | l    | L        |

| t <sub>DVADQ</sub>    | Data Valid After DQS (DDR Read)                                   | All                    | _     | 0.19 | —     | 0.19 | —     | 0.19 | UI       |

| t <sub>DVEDQ</sub>    | Data Hold After DQS (DDR Read)                                    | All                    | 0.67  |      | 0.67  | —    | 0.67  | —    | UI       |

| t <sub>DQVBS</sub>    | Data Valid Before DQS                                             | All                    | 0.20  | —    | 0.20  | —    | 0.20  | _    | UI       |

| t <sub>DQVAS</sub>    | Data Valid After DQS                                              | All                    | 0.20  |      | 0.20  |      | 0.20  | _    | UI       |

| f <sub>MAX_DDR</sub>  | DDR Clock Frequency                                               | All                    | 95    | 166  | 95    | 133  | 95    | 100  | MHz      |

|                       | nd Secondary Clocks                                               | 1                      | 1     | 1    | 1     | 1    | 1     | 1    | <u> </u> |

| f <sub>MAX_PRI</sub>  | Frequency for Primary Clock Tree                                  | All                    | —     | 450  | —     | 412  | —     | 375  | MHz      |

| t <sub>W_PRI</sub>    | Clock Pulse Width for Primary Clock                               | All                    | 1.19  | —    | 1.19  | —    | 1.19  | —    | ns       |

|                       |                                                                   | LFXP3/6/10/15          |       | 250  |       | 300  | —     | 350  | ps       |

| <sup>t</sup> SKEW_PRI | Primary Clock Skew within an I/O Bank                             | LFXP20                 |       | 300  |       | 350  | —     | 400  | ps       |

|                       |                                                                   | 1                      | 1     |      | 1     | 1    | 1     | 1    | 1        |

#### **Over Recommended Operating Conditions**

1. General timing numbers based on LVCMOS 2.5, 12mA.

2. DDR timing numbers based on SSTL I/O.

Timing v.F0.11

# LatticeXP Family Data Sheet Pinout Information

November 2007

Data Sheet DS1001

### **Signal Descriptions**

| Signal Name                                 | I/O    | Descriptions                                                                                                                                                                                                                                                          |  |  |  |  |

|---------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| General Purpose                             |        |                                                                                                                                                                                                                                                                       |  |  |  |  |

|                                             |        | [Edge] indicates the edge of the device on which the pad is located. Valid edge designations are L (Left), B (Bottom), R (Right), T (Top).                                                                                                                            |  |  |  |  |

|                                             |        | [Row/Column Number] indicates the PFU row or the column of the device on which the PIC exists. When Edge is T (Top) or (Bottom), only need to specify Row Number. When Edge is L (Left) or R (Right), only need to specify Column Number.                             |  |  |  |  |

| P[Edge] [Row/Column Number*]_[A/B]          | I/O    | [A/B] indicates the PIO within the PIC to which the pad is connected.                                                                                                                                                                                                 |  |  |  |  |

|                                             |        | Some of these user programmable pins are shared with special function pins. These pin when not used as special purpose pins can be programmed as $I/Os$ for user logic.                                                                                               |  |  |  |  |

|                                             |        | During configuration, the user-programmable I/Os are tri-stated with an inter-<br>nal pull-up resistor enabled. If any pin is not used (or not bonded to a pack-<br>age pin), it is also tri-stated with an internal pull-up resistor enabled after<br>configuration. |  |  |  |  |

| GSRN                                        | I      | Global RESET signal. (Active low). Any I/O pin can be configured to be GSRN.                                                                                                                                                                                          |  |  |  |  |

| NC                                          |        | No connect.                                                                                                                                                                                                                                                           |  |  |  |  |

| GND                                         | _      | GND - Ground. Dedicated Pins.                                                                                                                                                                                                                                         |  |  |  |  |

| V <sub>CC</sub>                             |        | VCC - The power supply pins for core logic. Dedicated Pins.                                                                                                                                                                                                           |  |  |  |  |

| V <sub>CCAUX</sub>                          | —      | $V_{CCAUX}$ - The Auxiliary power supply pin. It powers all the differential and referenced input buffers. Dedicated Pins.                                                                                                                                            |  |  |  |  |

| V <sub>CCP0</sub>                           |        | Voltage supply pins for ULM0PLL (and LLM1PLL <sup>1</sup> ).                                                                                                                                                                                                          |  |  |  |  |

| V <sub>CCP1</sub>                           | _      | Voltage supply pins for URM0PLL (and LRM1PLL <sup>1</sup> ).                                                                                                                                                                                                          |  |  |  |  |

| GNDP0                                       | _      | Ground pins for ULM0PLL (and LLM1PLL <sup>1</sup> ).                                                                                                                                                                                                                  |  |  |  |  |

| GNDP1                                       |        | Ground pins for URM0PLL (and LRM1PLL <sup>1</sup> ).                                                                                                                                                                                                                  |  |  |  |  |

| V <sub>CCIOx</sub>                          | _      | V <sub>CCIO</sub> - The power supply pins for I/O bank x. Dedicated Pins.                                                                                                                                                                                             |  |  |  |  |

| V <sub>REF1(x)</sub> , V <sub>REF2(x)</sub> | —      | Reference supply pins for I/O bank x. Pre-determined pins in each bank are assigned as $V_{\text{REF}}$ inputs. When not used, they may be used as I/O pins.                                                                                                          |  |  |  |  |

| PLL and Clock Functions (Used as user       | progra | ammable I/O pins when not in use for PLL or clock pins)                                                                                                                                                                                                               |  |  |  |  |

| [LOC][num]_PLL[T, C]_IN_A                   | _      | Reference clock (PLL) input Pads: ULM, LLM, URM, LRM, num = row from center, $T =$ true and $C =$ complement, index A, B, Cat each side.                                                                                                                              |  |  |  |  |

| [LOC][num]_PLL[T, C]_FB_A                   | _      | Optional feedback (PLL) input Pads: ULM, LLM, URM, LRM, num = row from center, $T =$ true and $C =$ complement, index A, B, Cat each side.                                                                                                                            |  |  |  |  |

| PCLK[T, C]_[n:0]_[3:0]                      | _      | Primary Clock Pads, T = true and C = complement, n per side, indexed by bank and 0,1, 2, 3 within bank.                                                                                                                                                               |  |  |  |  |

| [LOC]DQS[num]                               | _      | DQS input Pads: T (Top), R (Right), B (Bottom), L (Left), DQS, num = Ball function number. Any pad can be configured to be DQS output.                                                                                                                                |  |  |  |  |

<sup>© 2007</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### PICs and DDR Data (DQ) Pins Associated with the DDR Strobe (DQS) Pin

| PICs Associated<br>with DQS Strobe | PIO within PIC | Polarity   | DDR Strobe (DQS)<br>and Data (DQ) Pins |

|------------------------------------|----------------|------------|----------------------------------------|

| D[Edge] [p. 4]                     | А              | True       | DQ                                     |

| P[Edge] [n-4]                      | В              | Complement | DQ                                     |

| D[Edgo] [n 2]                      | А              | True       | DQ                                     |

| P[Edge] [n-3]                      | В              | Complement | DQ                                     |

| P[Edge] [n-2]                      | А              | True       | DQ                                     |

|                                    | В              | Complement | DQ                                     |

| P[Edge] [n-1]                      | A              | True       | DQ                                     |

| P[Edge] [n]                        | В              | Complement | DQ                                     |

|                                    | A              | True       | [Edge]DQSn                             |

| P[Edge] [n+1]                      | В              | Complement | DQ                                     |

|                                    | А              | True       | DQ                                     |

| P[Edge] [n+2]                      | В              | Complement | DQ                                     |

| D[Edgo] [n , 2]                    | А              | True       | DQ                                     |

| P[Edge] [n+3]                      | В              | Complement | DQ                                     |

Notes:

1. "n" is a row/column PIC number.

2. The DDR interface is designed for memories that support one DQS strobe per eight bits of data. In some packages, all the potential DDR data (DQ) pins may not be available.

3. The definition of the PIC numbering is provided in the Signal Names column of the Signal Descriptions table in this data sheet.

## Pin Information Summary<sup>1</sup> (Cont.)

|                                   |                         | XP        | 10        |           | XP15      |           |           | XP20      |           |

|-----------------------------------|-------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Pin Ty                            | pe                      | 256 fpBGA | 388 fpBGA | 256 fpBGA | 388 fpBGA | 484 fpBGA | 256 fpBGA | 388 fpBGA | 484 fpBGA |

| Single Ended User I/O             |                         | 188       | 244       | 188       | 268       | 300       | 188       | 268       | 340       |

| Differential Pai                  | r User I/O <sup>2</sup> | 76        | 104       | 76        | 112       | 128       | 76        | 112       | 144       |

| Configuration                     | Dedicated               | 11        | 11        | 11        | 11        | 11        | 11        | 11        | 11        |

| Configuration                     | Muxed                   | 14        | 14        | 14        | 14        | 14        | 14        | 14        | 14        |

| TAP                               | •                       | 5         | 5         | 5         | 5         | 5         | 5         | 5         | 5         |

| Dedicated<br>(total without s     | upplies)                | 6         | 6         | 6         | 6         | 6         | 6         | 6         | 6         |

| V <sub>CC</sub>                   |                         | 8         | 14        | 8         | 14        | 28        | 8         | 14        | 28        |

| V <sub>CCAUX</sub>                |                         | 4         | 4         | 4         | 4         | 12        | 4         | 4         | 12        |

| V <sub>CCPLL</sub>                |                         | 2         | 2         | 2         | 2         | 2         | 2         | 2         | 2         |

|                                   | Bank0                   | 2         | 5         | 2         | 5         | 4         | 2         | 5         | 4         |

|                                   | Bank1                   | 2         | 5         | 2         | 5         | 4         | 2         | 5         | 4         |

|                                   | Bank2                   | 2         | 4         | 2         | 4         | 4         | 2         | 4         | 4         |

| V                                 | Bank3                   | 2         | 4         | 2         | 4         | 4         | 2         | 4         | 4         |

| V <sub>CCIO</sub>                 | Bank4                   | 2         | 5         | 2         | 5         | 4         | 2         | 5         | 4         |

|                                   | Bank5                   | 2         | 5         | 2         | 5         | 4         | 2         | 5         | 4         |

|                                   | Bank6                   | 2         | 4         | 2         | 4         | 4         | 2         | 4         | 4         |

|                                   | Bank7                   | 2         | 4         | 2         | 4         | 4         | 2         | 4         | 4         |

| GND                               | •                       | 24        | 50        | 24        | 50        | 56        | 24        | 50        | 56        |

| GND <sub>PLL</sub>                |                         | 2         | 2         | 2         | 2         | 2         | 2         | 2         | 2         |

| NC                                |                         | 0         | 24        | 0         | 0         | 40        | 0         | 0         | 0         |

|                                   | Bank0                   | 26/11     | 33/14     | 26/11     | 39/16     | 40/17     | 26/11     | 39/16     | 47/20     |

|                                   | Bank1                   | 26/11     | 33/14     | 26/11     | 39/16     | 40/17     | 26/11     | 39/16     | 47/20     |

|                                   | Bank2                   | 21/8      | 28/12     | 21/8      | 28/12     | 35/15     | 21/8      | 28/12     | 38/16     |

| Single Ended/<br>Differential I/O | Bank3                   | 21/8      | 28/12     | 21/8      | 28/12     | 35/15     | 21/8      | 28/12     | 38/16     |

| per Bank <sup>2</sup>             | Bank4                   | 26/11     | 33/14     | 26/11     | 39/16     | 40/17     | 26/11     | 39/16     | 47/20     |

| ľ                                 | Bank5                   | 26/11     | 33/14     | 26/11     | 39/16     | 40/17     | 26/11     | 39/16     | 47/20     |

|                                   | Bank6                   | 21/8      | 28/12     | 21/8      | 28/12     | 35/15     | 21/8      | 28/12     | 38/16     |

|                                   | Bank7                   | 21/8      | 28/12     | 21/8      | 28/12     | 35/15     | 21/8      | 28/12     | 38/16     |

| V <sub>CCJ</sub>                  |                         | 1         | 1         | 1         | 1         | 1         | 1         | 1         | 1         |

1. During configuration the user-programmable I/Os are tri-stated with an internal pull-up resistor enabled. If any pin is not used (or not bonded to a package pin), it is also tri-stated with an internal pull-up resistor enabled after configuration.

2. The differential I/O per bank includes both dedicated LVDS and emulated LVDS pin pairs. Please see the Logic Signal Connections table for more information.

# LFXP15 & LFXP20 Logic Signal Connections: 256 fpBGA (Cont.)

|                |                  | LFXP15 |                | LFXP20           |                  |      |                |                  |

|----------------|------------------|--------|----------------|------------------|------------------|------|----------------|------------------|

| Ball<br>Number | Ball<br>Function | Bank   | Differential   | Dual<br>Function | Ball<br>Function | Bank | Differential   | Dual<br>Function |

| P16            | PR37B            | 3      | C <sup>3</sup> | -                | PR41B            | 3    | C <sup>3</sup> | -                |

| R16            | PR37A            | 3      | T <sup>3</sup> | DQS              | PR41A            | 3    | T <sup>3</sup> | DQS              |

| M15            | PR36B            | 3      | -              | -                | PR40B            | 3    | -              | -                |

| N14            | PR35A            | 3      | -              | VREF1_3          | PR39A            | 3    | -              | VREF1_3          |

| -              | GNDIO3           | 3      | -              | -                | GNDIO3           | 3    | -              | -                |

| M14            | PR33B            | 3      | С              | -                | PR37B            | 3    | С              | -                |

| L13            | PR33A            | 3      | Т              | -                | PR37A            | 3    | Т              | -                |

| L15            | PR32B            | 3      | C <sup>3</sup> | -                | PR36B            | 3    | C³             | -                |

| L14            | PR32A            | 3      | Т³             | -                | PR36A            | 3    | T <sup>3</sup> | -                |

| L12            | PR30A            | 3      | -              | -                | PR34A            | 3    | -              | -                |

| M16            | PR29B            | 3      | С              | RLM0_PLLC_IN_A   | PR33B            | 3    | С              | RLM0_PLLC_IN_A   |

| N16            | PR29A            | 3      | Т              | RLM0_PLLT_IN_A   | PR33A            | 3    | Т              | RLM0_PLLT_IN_A   |

| -              | GNDIO3           | 3      | -              | -                | GNDIO3           | 3    | -              | -                |

| K14            | PR28B            | 3      | C <sup>3</sup> | -                | PR32B            | 3    | C <sup>3</sup> | -                |

| K15            | PR28A            | 3      | T <sup>3</sup> | DQS              | PR32A            | 3    | T <sup>3</sup> | DQS              |

| K12            | PR27B            | 3      | -              | -                | PR31B            | 3    | -              | -                |

| K13            | PR26A            | 3      | -              | VREF2_3          | PR30A            | 3    | -              | VREF2_3          |

| L16            | PR25B            | 3      | C <sup>3</sup> | -                | PR29B            | 3    | C <sup>3</sup> | -                |

| K16            | PR25A            | 3      | T <sup>3</sup> | -                | PR29A            | 3    | T <sup>3</sup> | -                |

| -              | GNDIO3           | 3      | -              | -                | GNDIO3           | 3    | -              | -                |

| J15            | PR23B            | 3      | C <sup>3</sup> | -                | PR27B            | 3    | C <sup>3</sup> | -                |

| J14            | PR23A            | 3      | T <sup>3</sup> | -                | PR27A            | 3    | T <sup>3</sup> | -                |

| J13            | GNDP1            | -      | -              | -                | GNDP1            | -    | -              | -                |

| J12            | VCCP1            | -      | -              | -                | VCCP1            | -    | -              | -                |

| -              | GNDIO2           | 2      | -              | -                | GNDIO2           | 2    | -              | -                |

| J16            | PR21B            | 2      | С              | PCLKC2_0         | PR21B            | 2    | С              | PCLKC2_0         |

| H16            | PR21A            | 2      | Т              | PCLKT2_0         | PR21A            | 2    | Т              | PCLKT2_0         |

| H13            | PR20B            | 2      | C <sup>3</sup> | -                | PR20B            | 2    | C <sup>3</sup> | -                |

| H12            | PR20A            | 2      | T <sup>3</sup> | DQS              | PR20A            | 2    | T <sup>3</sup> | DQS              |

| H15            | PR19B            | 2      | -              | -                | PR19B            | 2    | -              | -                |

| H14            | PR18A            | 2      | -              | VREF1_2          | PR18A            | 2    | -              | VREF1_2          |

| -              | GNDIO2           | 2      | -              | -                | GNDIO2           | 2    | -              | -                |

| G15            | PR17B            | 2      | C <sup>3</sup> | -                | PR17B            | 2    | C³             | -                |

| G14            | PR17A            | 2      | T <sup>3</sup> | -                | PR17A            | 2    | T <sup>3</sup> | -                |

| G16            | PR16B            | 2      | С              | RUM0_PLLC_IN_A   | PR16B            | 2    | С              | RUM0_PLLC_IN_A   |

| F16            | PR16A            | 2      | Т              | RUM0_PLLT_IN_A   | PR16A            | 2    | Т              | RUM0_PLLT_IN_A   |

| G13            | PR15B            | 2      | -              | -                | PR15B            | 2    | -              | -                |

| -              | GNDIO2           | 2      | -              | -                | GNDIO2           | 2    | -              | -                |

| G12            | PR12B            | 2      | С              | -                | PR12B            | 2    | С              | -                |

| F13            | PR12A            | 2      | Т              | -                | PR12A            | 2    | Т              | -                |

| B16            | PR11B            | 2      | C <sup>3</sup> | -                | PR11B            | 2    | C <sup>3</sup> | -                |

| C16            | PR11A            | 2      | T <sup>3</sup> | DQS              | PR11A            | 2    | T <sup>3</sup> | DQS              |

# LFXP15 & LFXP20 Logic Signal Connections: 256 fpBGA (Cont.)

|                |                  |      | LFXP15       |                  | LFXP20           |      |              |                  |

|----------------|------------------|------|--------------|------------------|------------------|------|--------------|------------------|

| Ball<br>Number | Ball<br>Function | Bank | Differential | Dual<br>Function | Ball<br>Function | Bank | Differential | Dual<br>Function |

| L7             | VCCIO5           | 5    | -            | -                | VCCIO5           | 5    | -            | -                |

| L8             | VCCIO5           | 5    | -            | -                | VCCIO5           | 5    | -            | -                |

| J6             | VCCIO6           | 6    | -            | -                | VCCIO6           | 6    | -            | -                |

| K6             | VCCIO6           | 6    | -            | -                | VCCIO6           | 6    | -            | -                |

| G6             | VCCIO7           | 7    | -            | -                | VCCI07           | 7    | -            | -                |

| H6             | VCCIO7           | 7    | -            | -                | VCCI07           | 7    | -            | -                |

Applies to LFXP "C" only.

Applies to LFXP "E" only.

3. Supports dedicated LVDS outputs.

## LFXP10, LFXP15 & LFXP20 Logic Signal Connections: 388 fpBGA (Cont.)

|                | LFXP10           |      |       |               |                  | ;    | LFXP20 |               |                  |      |       |               |

|----------------|------------------|------|-------|---------------|------------------|------|--------|---------------|------------------|------|-------|---------------|

| Ball<br>Number | Ball<br>Function | Bank | Diff. | Dual Function | Ball<br>Function | Bank | Diff.  | Dual Function | Ball<br>Function | Bank | Diff. | Dual Function |

| G7             | VCCAUX           | -    | -     | -             | VCCAUX           | -    | -      | -             | VCCAUX           | -    | -     | -             |

| T16            | VCCAUX           | -    | -     | -             | VCCAUX           | -    | -      | -             | VCCAUX           | -    | -     | -             |

| T7             | VCCAUX           | -    | -     | -             | VCCAUX           | -    | -      | -             | VCCAUX           | -    | -     | -             |

| G10            | VCCIO0           | 0    | -     | -             | VCCIO0           | 0    | -      | -             | VCCIO0           | 0    | -     | -             |

| G11            | VCCIO0           | 0    | -     | -             | VCCIO0           | 0    | -      | -             | VCCIO0           | 0    | -     | -             |

| G8             | VCCIO0           | 0    | -     | -             | VCCIO0           | 0    | -      | -             | VCCIO0           | 0    | -     | -             |

| G9             | VCCIO0           | 0    | -     | -             | VCCIO0           | 0    | -      | -             | VCCIO0           | 0    | -     | -             |

| H8             | VCCIO0           | 0    | -     | -             | VCCIO0           | 0    | -      | -             | VCCIO0           | 0    | -     | -             |

| G12            | VCCIO1           | 1    | -     | -             | VCCIO1           | 1    | -      | -             | VCCIO1           | 1    | -     | -             |

| G13            | VCCIO1           | 1    | -     | -             | VCCIO1           | 1    | -      | -             | VCCIO1           | 1    | -     | -             |

| G14            | VCCIO1           | 1    | -     | -             | VCCIO1           | 1    | -      | -             | VCCIO1           | 1    | -     | -             |

| G15            | VCCIO1           | 1    | -     | -             | VCCIO1           | 1    | -      | -             | VCCIO1           | 1    | -     | -             |

| H15            | VCCIO1           | 1    | -     | -             | VCCIO1           | 1    | -      | -             | VCCIO1           | 1    | -     | -             |

| H16            | VCCIO2           | 2    | -     | -             | VCCIO2           | 2    | -      | -             | VCCIO2           | 2    | -     | -             |

| J16            | VCCIO2           | 2    | -     | -             | VCCIO2           | 2    | -      | -             | VCCIO2           | 2    | -     | -             |

| K16            | VCCIO2           | 2    | -     | -             | VCCIO2           | 2    | -      | -             | VCCIO2           | 2    | -     | -             |

| L16            | VCCIO2           | 2    | -     | -             | VCCIO2           | 2    | -      | -             | VCCIO2           | 2    | -     | -             |

| M16            | VCCIO3           | 3    | -     | -             | VCCIO3           | 3    | -      | -             | VCCIO3           | 3    | -     | -             |

| N16            | VCCIO3           | 3    | -     | -             | VCCIO3           | 3    | -      | -             | VCCIO3           | 3    | -     | -             |

| P16            | VCCIO3           | 3    | -     | -             | VCCIO3           | 3    | -      | -             | VCCIO3           | 3    | -     | -             |

| R16            | VCCIO3           | 3    | -     | -             | VCCIO3           | 3    | -      | -             | VCCIO3           | 3    | -     | -             |

| R15            | VCCIO4           | 4    | -     | -             | VCCIO4           | 4    | -      | -             | VCCIO4           | 4    | -     | -             |

| T12            | VCCIO4           | 4    | -     | -             | VCCIO4           | 4    | -      | -             | VCCIO4           | 4    | -     | -             |

| T13            | VCCIO4           | 4    | -     | -             | VCCIO4           | 4    | -      | -             | VCCIO4           | 4    | -     | -             |

| T14            | VCCIO4           | 4    | -     | -             | VCCIO4           | 4    | -      | -             | VCCIO4           | 4    | -     | -             |

| T15            | VCCIO4           | 4    | -     | -             | VCCIO4           | 4    | -      | -             | VCCIO4           | 4    | -     | -             |

| R8             | VCCIO5           | 5    | -     | -             | VCCIO5           | 5    | -      | -             | VCCIO5           | 5    | -     | -             |

| T10            | VCCIO5           | 5    | -     | -             | VCCIO5           | 5    | -      | -             | VCCIO5           | 5    | -     | -             |

| T11            | VCCIO5           | 5    | -     | -             | VCCIO5           | 5    | -      | -             | VCCIO5           | 5    | -     | -             |

| T8             | VCCIO5           | 5    | -     | -             | VCCIO5           | 5    | -      | -             | VCCIO5           | 5    | -     | -             |

| Т9             | VCCIO5           | 5    | -     | -             | VCCIO5           | 5    | -      | -             | VCCIO5           | 5    | -     | -             |

| M7             | VCCIO6           | 6    | -     | -             | VCCIO6           | 6    | -      | -             | VCCIO6           | 6    | -     | -             |

| N7             | VCCIO6           | 6    | -     | -             | VCCIO6           | 6    | -      | -             | VCCIO6           | 6    | -     | -             |

| P7             | VCCIO6           | 6    | -     | -             | VCCIO6           | 6    | -      | -             | VCCIO6           | 6    | -     | -             |

| R7             | VCCIO6           | 6    | -     | -             | VCCIO6           | 6    | -      | -             | VCCIO6           | 6    | -     | -             |

| H7             | VCCIO7           | 7    | -     | -             | VCCI07           | 7    | -      | -             | VCCIO7           | 7    | -     | -             |

| J7             | VCCIO7           | 7    | -     | -             | VCCI07           | 7    | -      | -             | VCCIO7           | 7    | -     | -             |

| K7             | VCCI07           | 7    | -     | -             | VCCI07           | 7    | -      | -             | VCCI07           | 7    | -     | -             |

| L7             | VCCI07           | 7    | -     | -             | VCCI07           | 7    | -      | -             | VCCIO7           | 7    | -     | -             |

1. Applies to LFXP "C" only.

2. Applies to LFXP "E" only.

3. Supports dedicated LVDS outputs.

# LFXP15 & LFXP20 Logic Signal Connections: 484 fpBGA (Cont.)

|                |                  | LFXP15 |                | LFXP20           |                  |      |                |                  |  |

|----------------|------------------|--------|----------------|------------------|------------------|------|----------------|------------------|--|

| Ball<br>Number | Ball<br>Function | Bank   | Differential   | Dual<br>Function | Ball<br>Function | Bank | Differential   | Dual<br>Function |  |

| R18            | PR38B            | 3      | С              | RLM0_PLLC_FB_A   | PR42B            | 3    | С              | RLM0_PLLC_FB_A   |  |

| R17            | PR38A            | 3      | Т              | RLM0_PLLT_FB_A   | PR42A            | 3    | Т              | RLM0_PLLT_FB_A   |  |

| Y22            | PR37B            | 3      | C <sup>3</sup> | -                | PR41B            | 3    | C <sup>3</sup> | -                |  |

| Y21            | PR37A            | 3      | T <sup>3</sup> | DQS              | PR41A            | 3    | T <sup>3</sup> | DQS              |  |

| W22            | PR36B            | 3      | -              | -                | PR40B            | 3    | -              | -                |  |

| W21            | PR35A            | 3      | -              | VREF1_3          | PR39A            | 3    | -              | VREF1_3          |  |

| P17            | PR34B            | 3      | C <sup>3</sup> | -                | PR38B            | 3    | C <sup>3</sup> | -                |  |

| P18            | PR34A            | 3      | T³             | -                | PR38A            | 3    | T <sup>3</sup> | -                |  |

| -              | GNDIO3           | 3      | -              | -                | GNDIO3           | 3    | -              | -                |  |

| R19            | PR33B            | 3      | С              | -                | PR37B            | 3    | С              | -                |  |

| R20            | PR33A            | 3      | Т              | -                | PR37A            | 3    | Т              | -                |  |

| V22            | PR32B            | 3      | C <sup>3</sup> | -                | PR36B            | 3    | C <sup>3</sup> | -                |  |

| V21            | PR32A            | 3      | T <sup>3</sup> | -                | PR36A            | 3    | T <sup>3</sup> | -                |  |

| U22            | PR30B            | 3      | C <sup>3</sup> | -                | PR34B            | 3    | C <sup>3</sup> | -                |  |

| U21            | PR30A            | 3      | T <sup>3</sup> | -                | PR34A            | 3    | T <sup>3</sup> | -                |  |

| P19            | PR29B            | 3      | С              | RLM0_PLLC_IN_A   | PR33B            | 3    | С              | RLM0_PLLC_IN_A   |  |

| P20            | PR29A            | 3      | Т              | RLM0_PLLT_IN_A   | PR33A            | 3    | Т              | RLM0_PLLT_IN_A   |  |

| -              | GNDIO3           | 3      | -              | -                | GNDIO3           | 3    | -              | -                |  |

| T22            | PR28B            | 3      | C <sup>3</sup> | -                | PR32B            | 3    | C <sup>3</sup> | -                |  |

| T21            | PR28A            | 3      | T <sup>3</sup> | DQS              | PR32A            | 3    | T <sup>3</sup> | DQS              |  |

| R22            | PR27B            | 3      | -              | -                | PR31B            | 3    | -              | -                |  |

| R21            | PR26A            | 3      | -              | VREF2_3          | PR30A            | 3    | -              | VREF2_3          |  |

| N19            | PR25B            | 3      | C <sup>3</sup> | -                | PR29B            | 3    | C <sup>3</sup> | -                |  |

| N20            | PR25A            | 3      | T <sup>3</sup> | -                | PR29A            | 3    | T <sup>3</sup> | -                |  |

| N18            | PR24B            | 3      | С              | -                | PR28B            | 3    | С              | -                |  |

| M18            | PR24A            | 3      | Т              | -                | PR28A            | 3    | Т              | -                |  |

| -              | GNDIO3           | 3      | -              | -                | GNDIO3           | 3    | -              | -                |  |

| P22            | PR23B            | 3      | C <sup>3</sup> | -                | PR27B            | 3    | C <sup>3</sup> | -                |  |

| P21            | PR23A            | 3      | T <sup>3</sup> | -                | PR27A            | 3    | T <sup>3</sup> | -                |  |

| N22            | -                | -      | -              | -                | PR26B            | 3    | C <sup>3</sup> | -                |  |

| N21            | -                | -      | -              | -                | PR26A            | 3    | T <sup>3</sup> | -                |  |

| M19            | -                | -      | -              | -                | PR25B            | 3    | -              | -                |  |

| M20            | GNDP1            | -      | -              | -                | GNDP1            | -    | -              | -                |  |

| L18            | VCCP1            | -      | -              | -                | VCCP1            | -    | -              | -                |  |

| M21            | -                | -      | -              | -                | PR24A            | 2    | -              | -                |  |