Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                  |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | 15000                                                                     |

| Total RAM Bits                 | 331776                                                                    |

| Number of I/O                  | 268                                                                       |

| Number of Gates                | -                                                                         |

| Voltage - Supply               | 1.71V ~ 3.465V                                                            |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                        |

| Package / Case                 | 388-BBGA                                                                  |

| Supplier Device Package        | 388-FPBGA (23x23)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfxp15c-3f388i |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# LatticeXP Family Data Sheet Architecture

July 2007

Data Sheet DS1001

### **Architecture Overview**

The LatticeXP architecture contains an array of logic blocks surrounded by Programmable I/O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM Embedded Block RAM (EBR) as shown in Figure 2-1.

On the left and right sides of the PFU array, there are Non-volatile Memory Blocks. In configuration mode this nonvolatile memory is programmed via the IEEE 1149.1 TAP port or the sysCONFIG<sup>™</sup> peripheral port. On power up, the configuration data is transferred from the Non-volatile Memory Blocks to the configuration SRAM. With this technology, expensive external configuration memories are not required and designs are secured from unauthorized read-back. This transfer of data from non-volatile memory to configuration SRAM via wide busses happens in microseconds, providing an "instant-on" capability that allows easy interfacing in many applications.

There are two kinds of logic blocks, the Programmable Functional Unit (PFU) and Programmable Functional unit without RAM/ROM (PFF). The PFU contains the building blocks for logic, arithmetic, RAM, ROM and register functions. The PFF block contains building blocks for logic, arithmetic and ROM functions. Both PFU and PFF blocks are optimized for flexibility, allowing complex designs to be implemented quickly and efficiently. Logic Blocks are arranged in a two-dimensional array. Only one type of block is used per row. The PFU blocks are used on the outside rows. The rest of the core consists of rows of PFF blocks interspersed with rows of PFU blocks. For every three rows of PFF blocks there is a row of PFU blocks.

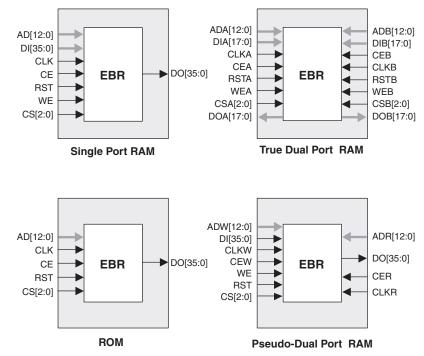

Each PIC block encompasses two PIOs (PIO pairs) with their respective sysIO interfaces. PIO pairs on the left and right edges of the device can be configured as LVDS transmit/receive pairs. sysMEM EBRs are large dedicated fast memory blocks. They can be configured as RAM or ROM.

The PFU, PFF, PIC and EBR Blocks are arranged in a two-dimensional grid with rows and columns as shown in Figure 2-1. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

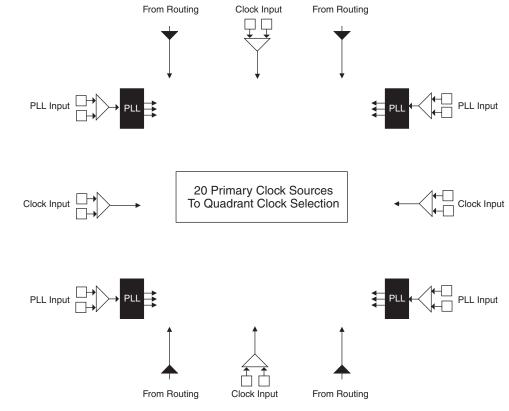

At the end of the rows containing the sysMEM Blocks are the sysCLOCK Phase Locked Loop (PLL) Blocks. These PLLs have multiply, divide and phase shifting capability; they are used to manage the phase relationship of the clocks. The LatticeXP architecture provides up to four PLLs per device.

Every device in the family has a JTAG Port with internal Logic Analyzer (ispTRACY) capability. The sysCONFIG port which allows for serial or parallel device configuration. The LatticeXP devices are available for operation from 3.3V, 2.5V, 1.8V and 1.2V power supplies, providing easy integration into the overall system.

<sup>© 2007</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

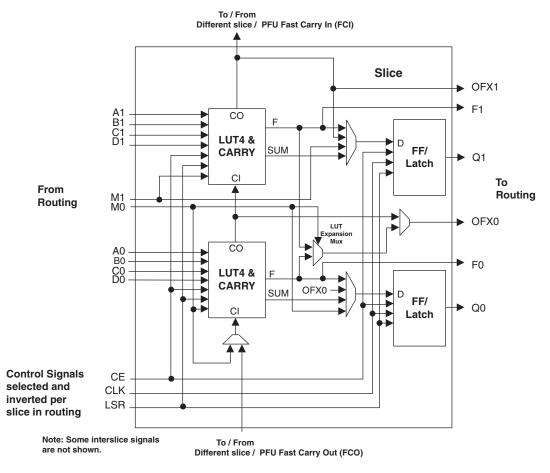

#### Slice

Each slice contains two LUT4 lookup tables feeding two registers (programmed to be in FF or Latch mode), and some associated logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/asynchronous), clock select, chip-select and wider RAM/ROM functions. Figure 2-3 shows an overview of the internal logic of the slice. The registers in the slice can be configured for positive/negative and edge/level clocks.

There are 14 input signals: 13 signals from routing and one from the carry-chain (from adjacent slice or PFU). There are 7 outputs: 6 to routing and one to carry-chain (to adjacent PFU). Table 2-1 lists the signals associated with each slice.

#### Figure 2-3. Slice Diagram

#### Figure 2-5. Primary Clock Sources

Note: Smaller devices have two PLLs.

### **Secondary Clock Sources**

LatticeXP devices have four secondary clock resources per quadrant. The secondary clock branches are tapped at every PFU. These secondary clock networks can also be used for controls and high fanout data. These secondary clocks are derived from four clock input pads and 16 routing signals as shown in Figure 2-6.

The EBR memory supports three forms of write behavior for single port or dual port operation:

- 1. **Normal** data on the output appears only during read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- 2. Write Through -ba copy of the input data appears at the output of the same port during a write cycle.bThis mode is supported for all data widths.

- 3. **Read-Before-Write** when new data is being written, the old content of the address appears at the output. This mode is supported for x9, x18 and x36 data widths.

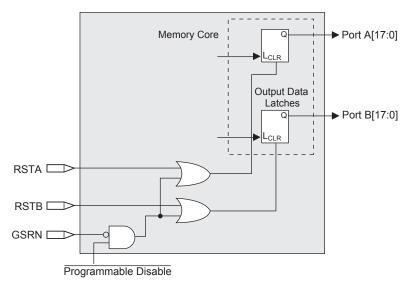

### **Memory Core Reset**

The memory array in the EBR utilizes latches at the A and B output ports. These latches can be reset asynchronously. RSTA and RSTB are local signals, which reset the output latches associated with Port A and Port B respectively. The Global Reset (GSRN) signal resets both ports. The output data latches and associated resets for both ports are as shown in Figure 2-15.

#### Figure 2-15. Memory Core Reset

For further information on sysMEM EBR block, see the details of additional technical documentation at the end of this data sheet.

### EBR Asynchronous Reset

EBR asynchronous reset or GSR (if used) can only be applied if all clock enables are low for a clock cycle before the reset is applied and released a clock cycle after the reset is released, as shown in Figure 2-16. The GSR input to the EBR is always asynchronous.

#### Figure 2-16. EBR Asynchronous Reset (Including GSR) Timing Diagram

| Reset           |  |

|-----------------|--|

| Clock           |  |

| Clock<br>Enable |  |

If all clock enables remain enabled, the EBR asynchronous reset or GSR may only be applied and released after the EBR read and write clock inputs are in a steady state condition for a minimum of  $1/f_{MAX}$  (EBR clock). The reset release must adhere to the EBR synchronous reset setup time before the next active read or write clock edge.

If an EBR is pre-loaded during configuration, the GSR input must be disabled or the release of the GSR during device Wake Up must occur before the release of the device I/Os becoming active.

These instructions apply to all EBR RAM and ROM implementations.

Note that there are no reset restrictions if the EBR synchronous reset is used and the EBR GSR input is disabled.

## Programmable I/O Cells (PICs)

Each PIC contains two PIOs connected to their respective sysIO Buffers which are then connected to the PADs as shown in Figure 2-17. The PIO Block supplies the output data (DO) and the Tri-state control signal (TO) to sysIO buffer, and receives input from the buffer.

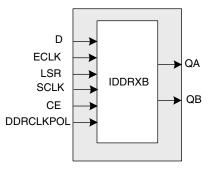

#### Figure 2-22. INDDRXB Primitive

#### **Output Register Block**

The output register block provides the ability to register signals from the core of the device before they are passed to the sysIO buffers. The block contains a register for SDR operation that is combined with an additional latch for DDR operation. Figure 2-23 shows the diagram of the Output Register Block.

In SDR mode, ONEG0 feeds one of the flip-flops that then feeds the output. The flip-flop can be configured as a Dtype or as a latch. In DDR mode, ONEG0 is fed into one register on the positive edge of the clock and OPOS0 is latched. A multiplexer running off the same clock selects the correct register for feeding to the output (D0).

Figure 2-24 shows the design tool DDR primitives. The SDR output register has reset and clock enable available. The additional register for DDR operation does not have reset or clock enable available.

### Polarity Control Logic

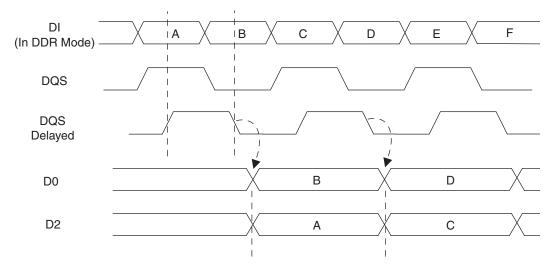

In a typical DDR Memory interface design, the phase relation between the incoming delayed DQS strobe and the internal system Clock (during the READ cycle) is unknown.

The LatticeXP family contains dedicated circuits to transfer data between these domains. To prevent setup and hold violations at the domain transfer between DQS (delayed) and the system Clock a clock polarity selector is used. This changes the edge on which the data is registered in the synchronizing registers in the input register block. This requires evaluation at the start of the each READ cycle for the correct clock polarity.

Prior to the READ operation in DDR memories DQS is in tristate (pulled by termination). The DDR memory device drives DQS low at the start of the preamble state. A dedicated circuit detects this transition. This signal is used to control the polarity of the clock to the synchronizing registers.

## sysIO Buffer

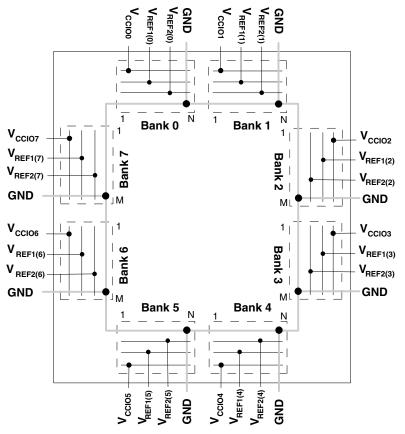

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in eight groups referred to as Banks. The sysIO buffers allow users to implement the wide variety of standards that are found in today's systems including LVCMOS, SSTL, HSTL, LVDS and LVPECL.

#### sysIO Buffer Banks

LatticeXP devices have eight sysIO buffer banks; each is capable of supporting multiple I/O standards. Each sysIO bank has its own I/O supply voltage ( $V_{CCIO}$ ), and two voltage references  $V_{REF1}$  and  $V_{REF2}$  resources allowing each bank to be completely independent from each other. Figure 2-28 shows the eight banks and their associated supplies.

In the LatticeXP devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS, PCI and PCI-X) are powered using  $V_{CCIO}$ . LVTTL, LVCMOS33, LVCMOS25 and LVCMOS12 can also be set as a fixed threshold input independent of  $V_{CCIO}$ . In addition to the bank  $V_{CCIO}$  supplies, the LatticeXP devices have a  $V_{CC}$  core logic power supply, and a  $V_{CCAUX}$  supply that power all differential and referenced buffers.

Each bank can support up to two separate VREF voltages, VREF1 and VREF2 that set the threshold for the referenced input buffers. In the LatticeXP devices, a dedicated pin in a bank can be configured to be a reference voltage supply pin. Each I/O is individually configurable based on the bank's supply and reference voltages.

#### Figure 2-28. LatticeXP Banks

Note: N and M are the maximum number of I/Os per bank.

LatticeXP devices contain two types of sysIO buffer pairs.

#### 1. Top and Bottom sysIO Buffer Pair (Single-Ended Outputs Only)

The sysIO buffer pairs in the top and bottom banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (both ratioed and referenced). The referenced input buffer can also be configured as a differential input.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential input buffer and the comp (complementary) pad is associated with the negative side of the differential input buffer.

Only the I/Os on the top and bottom banks have PCI clamps. Note that the PCI clamp is enabled after  $V_{CC,}$   $V_{CCAUX}$  and  $V_{CCIO}$  are at valid operating levels and the device has been configured.

#### 2. Left and Right sysIO Buffer Pair (Differential and Single-Ended Outputs)

The sysIO buffer pairs in the left and right banks of the device consist of two single-ended output drivers, two sets of single-ended input buffers (both ratioed and referenced) and one differential output driver. The referenced input buffer can also be configured as a differential input. In these banks the two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential I/O, and the comp (complementary) pad is associated with the negative side of the differential I/O.

Select I/Os in the left and right banks have LVDS differential output drivers. Refer to the Logic Signal Connections tables for more information.

# Programming and Erase Flash Supply Current<sup>1, 2, 3, 4, 5</sup>

| Symbol             | Parameter                                           | Device    | Тур.6 | Units |

|--------------------|-----------------------------------------------------|-----------|-------|-------|

|                    |                                                     | LFXP3E    | 30    | mA    |

|                    |                                                     | LFXP6E    | 40    | mA    |

|                    |                                                     | LFXP10E   | 50    | mA    |

|                    |                                                     | LFXP15E   | 60    | mA    |

|                    | Core Dower Supply                                   | LFXP20E   | 70    | mA    |

| Icc                | Core Power Supply                                   | LFXP3C    | 50    | mA    |

|                    |                                                     | LFXP6C    | 60    | mA    |

|                    |                                                     | LFXP10C   | 90    | mA    |

|                    |                                                     | LFXP15C   | 100   | mA    |

|                    |                                                     | LFXP20C   | 110   | mA    |

|                    |                                                     | LFXP3E/C  | 50    | mA    |

|                    |                                                     | LFXP6E/C  | 60    | mA    |

| I <sub>CCAUX</sub> | Auxiliary Power Supply<br>V <sub>CCAUX</sub> = 3.3V | LFXP10E/C | 90    | mA    |

|                    |                                                     | LFXP15E/C | 110   | mA    |

|                    |                                                     | LFXP20E/C | 130   | mA    |

| I <sub>CCJ</sub>   | V <sub>CCJ</sub> Power Supply <sup>7</sup>          | All       | 2     | mA    |

1. For further information on supply current, please see details of additional technical documentation at the end of this data sheet.

2. Assumes all outputs are tristated, all inputs are configured as LVCMOS and held at the  $V_{\mbox{CCIO}}$  or GND.

3. Blank user pattern; typical Flash pattern.

4. Bypass or decoupling capacitor across the supply.

5. JTAG programming is at 1MHz.

6.  $T_A=25^{\circ}C$ , power supplies at nominal voltage.

7. When programming via JTAG.

# sysIO Recommended Operating Conditions

|                     |       | V <sub>CCIO</sub> |       |       | V <sub>REF</sub> (V) |       |

|---------------------|-------|-------------------|-------|-------|----------------------|-------|

| Standard            | Min.  | Тур.              | Max.  | Min.  | Тур.                 | Max.  |

| LVCMOS 3.3          | 3.135 | 3.3               | 3.465 | —     | —                    | —     |

| LVCMOS 2.5          | 2.375 | 2.5               | 2.625 | —     | —                    | —     |

| LVCMOS 1.8          | 1.71  | 1.8               | 1.89  | —     | —                    | —     |

| LVCMOS 1.5          | 1.425 | 1.5               | 1.575 | —     | —                    | —     |

| LVCMOS 1.2          | 1.14  | 1.2               | 1.26  | —     | —                    | —     |

| LVTTL               | 3.135 | 3.3               | 3.465 | —     | —                    | —     |

| PCI33               | 3.135 | 3.3               | 3.465 | —     | —                    | —     |

| SSTL18 Class I      | 1.71  | 1.8               | 1.89  | 0.833 | 0.9                  | 0.969 |

| SSTL2 Class I, II   | 2.375 | 2.5               | 2.625 | 1.15  | 1.25                 | 1.35  |

| SSTL3 Class I, II   | 3.135 | 3.3               | 3.465 | 1.3   | 1.5                  | 1.7   |

| HSTL15 Class I      | 1.425 | 1.5               | 1.575 | 0.68  | 0.75                 | 0.9   |

| HSTL15 Class III    | 1.425 | 1.5               | 1.575 | —     | 0.9                  | —     |

| HSTL 18 Class I, II | 1.71  | 1.8               | 1.89  | —     | 0.9                  | —     |

| HSTL 18 Class III   | 1.71  | 1.8               | 1.89  | —     | 1.08                 | —     |

| LVDS                | 2.375 | 2.5               | 2.625 | —     | —                    | —     |

| LVPECL <sup>1</sup> | 3.135 | 3.3               | 3.465 | —     | —                    | —     |

| BLVDS <sup>1</sup>  | 2.375 | 2.5               | 2.625 | —     | —                    | —     |

1. Inputs on chip. Outputs are implemented with the addition of external resistors.

# **Signal Descriptions (Cont.)**

| achine.<br>ending<br>t is<br>rr-up<br>149.1. |

|----------------------------------------------|

| ending<br>t is<br>r-up<br>149.1.             |

| ending<br>t is<br>r-up<br>149.1.             |

| ending<br>t is<br>r-up<br>149.1.             |

|                                              |

| ng edge                                      |

| ng edge                                      |

| ng edge                                      |

|                                              |

| ng con-<br>hen this                          |

| has an                                       |

| ete, and                                     |

|                                              |

| ) pin.                                       |

| is                                           |

| is                                           |

| er pro-                                      |

| mmable                                       |

| g sys-                                       |

| ysCON-<br>on it is a                         |

| e device<br>/lode<br>not used                |

| as a<br>s recom-                             |

|                                              |

Applies tob LFXP10, LFXP15 and LFXP20 only.

Applies to LFXP "C" devices only.

Applies to LFXP "E" devices only.

# Pin Information Summary<sup>1</sup> (Cont.)

|                                       |                         | XP        | 10        |           | XP15      |           | XP20      |           |           |  |  |  |

|---------------------------------------|-------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--|--|--|

| Pin Ty                                | pe                      | 256 fpBGA | 388 fpBGA | 256 fpBGA | 388 fpBGA | 484 fpBGA | 256 fpBGA | 388 fpBGA | 484 fpBGA |  |  |  |

| Single Ended l                        | Jser I/O                | 188       | 244       | 188       | 268       | 300       | 188       | 268       | 340       |  |  |  |

| Differential Pai                      | r User I/O <sup>2</sup> | 76        | 104       | 76        | 112       | 128       | 76        | 112       | 144       |  |  |  |

| Configuration                         | Dedicated               | 11        | 11        | 11        | 11        | 11        | 11        | 11        | 11        |  |  |  |

| Configuration                         | Muxed                   | 14        | 14        | 14        | 14        | 14        | 14        | 14        | 14        |  |  |  |

| TAP                                   | •                       | 5         | 5         | 5         | 5         | 5         | 5         | 5         | 5         |  |  |  |

| Dedicated<br>(total without supplies) |                         | 6         | 6         | 6         | 6         | 6         | 6         | 6         | 6         |  |  |  |

| V <sub>CC</sub>                       |                         | 8         | 14        | 8         | 14        | 28        | 8         | 14        | 28        |  |  |  |

| V <sub>CCAUX</sub>                    |                         | 4         | 4         | 4         | 4         | 12        | 4         | 4         | 12        |  |  |  |

| V <sub>CCPLL</sub>                    |                         | 2         | 2         | 2         | 2         | 2         | 2         | 2         | 2         |  |  |  |

|                                       | Bank0                   | 2         | 5         | 2         | 5         | 4         | 2         | 5         | 4         |  |  |  |

| V                                     | Bank1                   | 2         | 5         | 2         | 5         | 4         | 2         | 5         | 4         |  |  |  |

|                                       | Bank2                   | 2         | 4         | 2         | 4         | 4         | 2         | 4         | 4         |  |  |  |

|                                       | Bank3                   | 2         | 4         | 2         | 4         | 4         | 2         | 4         | 4         |  |  |  |

| V <sub>CCIO</sub>                     | Bank4                   | 2         | 5         | 2         | 5         | 4         | 2         | 5         | 4         |  |  |  |

|                                       | Bank5                   | 2         | 5         | 2         | 5         | 4         | 2         | 5         | 4         |  |  |  |

|                                       | Bank6                   | 2         | 4         | 2         | 4         | 4         | 2         | 4         | 4         |  |  |  |

|                                       | Bank7                   | 2         | 4         | 2         | 4         | 4         | 2         | 4         | 4         |  |  |  |

| GND                                   | •                       | 24        | 50        | 24        | 50        | 56        | 24        | 50        | 56        |  |  |  |

| GND <sub>PLL</sub>                    |                         | 2         | 2         | 2         | 2         | 2         | 2         | 2         | 2         |  |  |  |

| NC                                    |                         | 0         | 24        | 0         | 0         | 40        | 0         | 0         | 0         |  |  |  |

|                                       | Bank0                   | 26/11     | 33/14     | 26/11     | 39/16     | 40/17     | 26/11     | 39/16     | 47/20     |  |  |  |

|                                       | Bank1                   | 26/11     | 33/14     | 26/11     | 39/16     | 40/17     | 26/11     | 39/16     | 47/20     |  |  |  |

|                                       | Bank2                   | 21/8      | 28/12     | 21/8      | 28/12     | 35/15     | 21/8      | 28/12     | 38/16     |  |  |  |

| Single Ended/<br>Differential I/O     | Bank3                   | 21/8      | 28/12     | 21/8      | 28/12     | 35/15     | 21/8      | 28/12     | 38/16     |  |  |  |

| per Bank <sup>2</sup>                 | Bank4                   | 26/11     | 33/14     | 26/11     | 39/16     | 40/17     | 26/11     | 39/16     | 47/20     |  |  |  |

| ľ                                     | Bank5                   | 26/11     | 33/14     | 26/11     | 39/16     | 40/17     | 26/11     | 39/16     | 47/20     |  |  |  |

|                                       | Bank6                   | 21/8      | 28/12     | 21/8      | 28/12     | 35/15     | 21/8      | 28/12     | 38/16     |  |  |  |

|                                       | Bank7                   | 21/8      | 28/12     | 21/8      | 28/12     | 35/15     | 21/8      | 28/12     | 38/16     |  |  |  |

| V <sub>CCJ</sub>                      |                         | 1         | 1         | 1         | 1         | 1         | 1         | 1         | 1         |  |  |  |

1. During configuration the user-programmable I/Os are tri-stated with an internal pull-up resistor enabled. If any pin is not used (or not bonded to a package pin), it is also tri-stated with an internal pull-up resistor enabled after configuration.

2. The differential I/O per bank includes both dedicated LVDS and emulated LVDS pin pairs. Please see the Logic Signal Connections table for more information.

# LFXP3 Logic Signal Connections: 100 TQFP (Cont.)

| Pin Number | Pin Function | Bank | Differential   | Dual Function  |

|------------|--------------|------|----------------|----------------|

| 44         | GNDIO4       | 4    | -              | -              |

| 45         | PB15A        | 4    | Т              | PCLKT4_0       |

| 46         | PB15B        | 4    | С              | PCLKC4_0       |

| 47         | VCCIO4       | 4    | -              | -              |

| 48         | PB19A        | 4    | Т              | DQS            |

| 49         | PB19B        | 4    | С              | VREF1_4        |

| 50         | PB24A        | 4    | -              | VREF2_4        |

| 51         | PR18B        | 3    | C <sup>3</sup> | -              |

| 52         | GNDIO3       | 3    | -              | -              |

| 53         | PR18A        | 3    | T <sup>3</sup> | -              |

| 54         | PR15B        | 3    | -              | VREF1_3        |

| 55         | PR14A        | 3    | -              | VREF2_3        |

| 56         | PR13B        | 3    | С              | -              |

| 57         | PR13A        | 3    | Т              | -              |

| 58         | VCCIO3       | 3    | -              | -              |

| 59         | GNDP1        | -    | -              | -              |

| 60         | VCCP1        | -    | -              | -              |

| 61         | PR9B         | 2    | С              | PCLKC2_0       |

| 62         | PR9A         | 2    | Т              | PCLKT2_0       |

| 63         | PR8B         | 2    | С              | RUM0_PLLC_IN_  |

| 64         | PR8A         | 2    | Т              | RUM0_PLLT_IN_/ |

| 65         | VCCIO2       | 2    | -              | -              |

| 66         | PR6B         | 2    | -              | VREF1_2        |

| 67         | PR5A         | 2    | -              | VREF2_2        |

| 68         | GNDIO2       | 2    | -              | -              |

| 69         | PR3B         | 2    | С              | RUM0_PLLC_FB_  |

| 70         | PR3A         | 2    | Т              | RUM0_PLLT_FB_  |

| 71         | VCCAUX       | -    | -              | -              |

| 72         | TDO          | -    | -              | -              |

| 73         | VCCJ         | -    | -              | -              |

| 74         | TDI          | -    | -              | -              |

| 75         | TMS          | -    | -              | -              |

| 76         | ТСК          | -    | -              | -              |

| 77         | VCC          | -    | -              | -              |

| 78         | PT24A        | 1    | -              | -              |

| 79         | PT23A        | 1    | -              | D0             |

| 80         | PT22B        | 1    | -              | D1             |

| 81         | PT21A        | 1    | -              | D2             |

| 82         | VCCIO1       | 1    | -              | -              |

| 83         | PT20B        | 1    | -              | D3             |

| 84         | GNDIO1       | 1    | -              | -              |

| 85         | PT17A        | 1    | -              | D4             |

| 86         | PT16A        | 1    | -              | D5             |

| 87         | PT15B        | 1    | -              | D6             |

# LFXP3 & LFXP6 Logic Signal Connections: 144 TQFP

| Pin    |                                       |      | LFXP3               |                | LFXP6                                 |      |                     |                      |  |  |

|--------|---------------------------------------|------|---------------------|----------------|---------------------------------------|------|---------------------|----------------------|--|--|

| Number | Pin Function                          | Bank | Differential        | Dual Function  | Pin Function                          | Bank | Differential        | <b>Dual Function</b> |  |  |

| 1      | PROGRAMN                              | 7    | -                   | -              | PROGRAMN                              | 7    | -                   | -                    |  |  |

| 2      | CCLK                                  | 7    | -                   | -              | CCLK                                  | 7    | -                   | -                    |  |  |

| 3      | GND                                   | -    | -                   | -              | GND                                   | -    | -                   | -                    |  |  |

| 4      | PL2A                                  | 7    | T <sup>3</sup>      | -              | PL2A                                  | 7    | T <sup>3</sup>      | -                    |  |  |

| 5      | PL2B                                  | 7    | C <sup>3</sup>      | -              | PL2B                                  | 7    | C <sup>3</sup>      | -                    |  |  |

| 6      | PL3A                                  | 7    | Т                   | LUM0_PLLT_FB_A | PL3A                                  | 7    | Т                   | LUM0_PLLT_FB_A       |  |  |

| 7      | PL3B                                  | 7    | С                   | LUM0_PLLC_FB_A | PL3B                                  | 7    | С                   | LUM0_PLLC_FB_A       |  |  |

| 8      | VCCIO7                                | 7    | -                   | -              | VCCIO7                                | 7    | -                   | -                    |  |  |

| 9      | PL5A                                  | 7    | -                   | VREF1_7        | PL5A                                  | 7    | -                   | VREF1_7              |  |  |

| 10     | PL6B                                  | 7    | -                   | VREF2_7        | PL6B                                  | 7    | -                   | VREF2_7              |  |  |

| 11     | GNDIO7                                | 7    | -                   | -              | GNDIO7                                | 7    | -                   | -                    |  |  |

| 12     | PL7A                                  | 7    | T <sup>3</sup>      | DQS            | PL7A                                  | 7    | T <sup>3</sup>      | DQS                  |  |  |

| 13     | PL7B                                  | 7    | C <sup>3</sup>      | -              | PL7B                                  | 7    | C <sup>3</sup>      | -                    |  |  |

| 14     | VCC                                   | -    | -                   | -              | VCC                                   | -    | -                   | -                    |  |  |

| 15     | PL8A                                  | 7    | Т                   | LUM0_PLLT_IN_A | PL8A                                  | 7    | Т                   | LUM0_PLLT_IN_A       |  |  |

| 16     | PL8B                                  | 7    | С                   | LUM0_PLLC_IN_A | PL8B                                  | 7    | С                   | LUM0_PLLC_IN_A       |  |  |

| 17     | PL9A                                  | 7    | T <sup>3</sup>      | -              | PL9A                                  | 7    | T <sup>3</sup>      | -                    |  |  |

| 18     | PL9B                                  | 7    | C <sup>3</sup>      | _              | PL9B                                  | 7    | C <sup>3</sup>      | -                    |  |  |

| 19     | VCCP0                                 | -    | -                   | <u>-</u>       | VCCP0                                 | -    | -                   | -                    |  |  |

| 20     | GNDP0                                 | -    | -                   | _              | GNDP0                                 | -    | -                   |                      |  |  |

| 21     | VCCIO6                                | 6    | -                   | -              | VCCIO6                                | 6    | -                   | -                    |  |  |

| 22     | PL11A                                 | 6    | T <sup>3</sup>      | _              | PL16A                                 | 6    | T <sup>3</sup>      | -                    |  |  |

| 23     | PL11B                                 | 6    | C <sup>3</sup>      |                | PL16B                                 | 6    | C <sup>3</sup>      | -                    |  |  |

| 23     | PL12A                                 | 6    | Т                   | PCLKT6_0       | PL17A                                 | 6    | Т                   | PCLKT6_0             |  |  |

| 24     | PL12A                                 | 6    | C                   | PCLKC6_0       | PL17B                                 | 6    | C                   | PCLKC6_0             |  |  |

| 26     | PL13A                                 | 6    | T <sup>3</sup>      |                | PL18A                                 | 6    | T <sup>3</sup>      | TOEROO_0             |  |  |

| 20     | PL13A<br>PL13B                        | 6    | C <sup>3</sup>      | -              | PL18A<br>PL18B                        | 6    | C <sup>3</sup>      | -                    |  |  |

| 28     | GNDIO6                                | 6    | -                   | -              | GNDIO6                                | 6    | -                   | -                    |  |  |

| 20     | PL14A                                 | 6    | -                   | VREF1_6        | PL22A                                 | 6    | -                   | VREF1_6              |  |  |

| 30     | PL14A<br>PL15B                        | 6    | -                   | VREF1_0        | PL22A<br>PL23B                        | 6    | -                   | VREF1_6              |  |  |

|        | PL15B<br>PL16A                        |      | -<br>T <sup>3</sup> | DQS            | PL23B<br>PL24A                        |      | -<br>T <sup>3</sup> | DQS                  |  |  |

| 31     | PL16A<br>PL16B                        | 6    | C <sup>3</sup>      |                |                                       | 6    | C <sup>3</sup>      | DQS                  |  |  |

| 32     |                                       | 6    |                     | -              | PL24B                                 | 6    |                     | -                    |  |  |

| 33     | PL17A                                 | 6    | -                   | -              | PL25A                                 | 6    | -                   | -                    |  |  |

| 34     | PL18A                                 | 6    | T <sup>3</sup>      | -              | PL26A                                 | 6    | T <sup>3</sup>      | -                    |  |  |

| 35     | PL18B                                 | 6    | C <sup>3</sup>      | -              | PL26B                                 | 6    | C <sup>3</sup>      | -                    |  |  |

| 36     | VCCAUX                                | -    | -                   | -              | VCCAUX                                | -    | -                   | -                    |  |  |

| 37     | SLEEPN <sup>1</sup> /TOE <sup>2</sup> | -    | -                   | -              | SLEEPN <sup>1</sup> /TOE <sup>2</sup> | -    | -                   | -                    |  |  |

| 38     | INITN                                 | 5    | -                   | -              | INITN                                 | 5    | -                   | -                    |  |  |

| 39     | VCC                                   | -    | -                   | -              | VCC                                   | -    | -                   | -                    |  |  |

| 40     | PB2B                                  | 5    | -                   | VREF1_5        | PB5B                                  | 5    | -                   | VREF1_5              |  |  |

| 41     | PB5B                                  | 5    | -                   | VREF2_5        | PB8B                                  | 5    | -                   | VREF2_5              |  |  |

| 42     | PB7A                                  | 5    | Т                   | -              | PB10A                                 | 5    | Т                   | -                    |  |  |

| 43     | PB7B                                  | 5    | С                   | -              | PB10B                                 | 5    | С                   | -                    |  |  |

| 44     | GNDIO5                                | 5    | -                   | -              | GNDIO5                                | 5    | -                   | -                    |  |  |

| 45     | PB9A                                  | 5    | -                   | -              | PB12A                                 | 5    | -                   | -                    |  |  |

| 46     | PB10B                                 | 5    | -                   | -              | PB13B                                 | 5    | -                   | -                    |  |  |

# LFXP10, LFXP15 & LFXP20 Logic Signal Connections: 388 fpBGA (Cont.)

|                | LFXP10           |      |       |               | LFXP15           |      |       |               | LFXP20           |      |       |               |

|----------------|------------------|------|-------|---------------|------------------|------|-------|---------------|------------------|------|-------|---------------|

| Ball<br>Number | Ball<br>Function | Bank | Diff. | Dual Function | Ball<br>Function | Bank | Diff. | Dual Function | Ball<br>Function | Bank | Diff. | Dual Function |

| Y10            | PB11B            | 5    | С     | -             | PB16B            | 5    | С     | -             | PB20B            | 5    | С     | -             |

| AA7            | PB12A            | 5    | Т     | -             | PB17A            | 5    | Т     | -             | PB21A            | 5    | Т     | -             |

| AB7            | PB12B            | 5    | С     | VREF2_5       | PB17B            | 5    | С     | VREF2_5       | PB21B            | 5    | С     | VREF2_5       |

| Y7             | PB13A            | 5    | Т     | -             | PB18A            | 5    | Т     | -             | PB22A            | 5    | Т     | -             |

| -              | GNDIO5           | 5    | -     | -             | GNDIO5           | 5    | -     | -             | GNDIO5           | 5    | -     | -             |

| AA8            | PB13B            | 5    | С     | -             | PB18B            | 5    | С     | -             | PB22B            | 5    | С     | -             |

| AB8            | PB14A            | 5    | Т     | -             | PB19A            | 5    | Т     | -             | PB23A            | 5    | Т     | -             |

| Y8             | PB14B            | 5    | С     | -             | PB19B            | 5    | С     | -             | PB23B            | 5    | С     | -             |

| AB9            | PB15A            | 5    | Т     | -             | PB20A            | 5    | Т     | -             | PB24A            | 5    | Т     | -             |

| AA9            | PB15B            | 5    | С     | -             | PB20B            | 5    | С     | -             | PB24B            | 5    | С     | -             |

| W10            | PB16A            | 5    | -     | -             | PB21A            | 5    | -     | -             | PB25A            | 5    | -     | -             |

| W11            | PB17B            | 5    | -     | -             | PB22B            | 5    | -     | -             | PB26B            | 5    | -     | -             |

| AB10           | PB18A            | 5    | Т     | DQS           | PB23A            | 5    | Т     | DQS           | PB27A            | 5    | Т     | DQS           |

| AA10           | PB18B            | 5    | С     | -             | PB23B            | 5    | С     | -             | PB27B            | 5    | С     | -             |

| -              | GNDIO5           | 5    | -     | -             | GNDIO5           | 5    | -     | -             | GNDIO5           | 5    | -     | -             |

| AA11           | PB19A            | 5    | Т     | -             | PB24A            | 5    | Т     | -             | PB28A            | 5    | Т     | -             |

| AB11           | PB19B            | 5    | С     | -             | PB24B            | 5    | С     | -             | PB28B            | 5    | С     | -             |

| Y11            | PB20A            | 5    | Т     | -             | PB25A            | 5    | Т     | -             | PB29A            | 5    | Т     | -             |

| Y12            | PB20B            | 5    | С     | -             | PB25B            | 5    | С     | -             | PB29B            | 5    | С     | -             |

| AB12           | PB21A            | 4    | Т     | -             | PB26A            | 4    | Т     | -             | PB30A            | 4    | Т     | -             |

| AA12           | PB21B            | 4    | С     | -             | PB26B            | 4    | С     | -             | PB30B            | 4    | С     | -             |

| AB13           | PB22A            | 4    | Т     | PCLKT4_0      | PB27A            | 4    | Т     | PCLKT4_0      | PB31A            | 4    | Т     | PCLKT4_0      |

| AA13           | PB22B            | 4    | С     | PCLKC4_0      | PB27B            | 4    | С     | PCLKC4_0      | PB31B            | 4    | С     | PCLKC4_0      |

| -              | GNDIO4           | 4    | -     | -             | GNDIO4           | 4    | -     | -             | GNDIO4           | 4    | -     |               |

| AA14           | PB23A            | 4    | Т     | -             | PB28A            | 4    | Т     | -             | PB32A            | 4    | Т     | -             |

| AB14           | PB23B            | 4    | С     | -             | PB28B            | 4    | С     | -             | PB32B            | 4    | С     | -             |

| W12            | PB24A            | 4    | -     | -             | PB29A            | 4    | -     | -             | PB33A            | 4    | -     | -             |

| W13            | PB25B            | 4    | -     | -             | PB30B            | 4    | -     | -             | PB34B            | 4    | -     | -             |

| AA15           | PB26A            | 4    | Т     | DQS           | PB31A            | 4    | Т     | DQS           | PB35A            | 4    | Т     | DQS           |

| AB15           | PB26B            | 4    | С     | VREF1_4       | PB31B            | 4    | С     | VREF1_4       | PB35B            | 4    | С     | VREF1_4       |

| AA16           | PB27A            | 4    | Т     | -             | PB32A            | 4    | Т     | -             | PB36A            | 4    | Т     | -             |

| AB16           | PB27B            | 4    | С     | -             | PB32B            | 4    | С     | -             | PB36B            | 4    | С     | -             |

| Y17            | PB28A            | 4    | Т     | -             | PB33A            | 4    | Т     | -             | PB37A            | 4    | Т     | -             |

| -              | GNDIO4           | 4    | -     | -             | GNDIO4           | 4    | -     | -             | GNDIO4           | 4    | -     | -             |

| AA17           | PB28B            | 4    | С     | -             | PB33B            | 4    | С     | -             | PB37B            | 4    | С     | -             |

| Y13            | PB29A            | 4    | Т     | -             | PB34A            | 4    | т     | -             | PB38A            | 4    | Т     | -             |

| Y14            | PB29B            | 4    | С     | -             | PB34B            | 4    | С     | -             | PB38B            | 4    | С     | -             |

| AB17           | PB30A            | 4    | Т     | -             | PB35A            | 4    | Т     | -             | PB39A            | 4    | Т     | -             |

| Y18            | PB30B            | 4    | С     | -             | PB35B            | 4    | С     | -             | PB39B            | 4    | С     | -             |

| AA18           | PB31A            | 4    | Т     | VREF2_4       | PB36A            | 4    | Т     | VREF2 4       | PB40A            | 4    | Т     | VREF2 4       |

| AB18           | PB31B            | 4    | С     | -             | PB36B            | 4    | С     | -             | PB40B            | 4    | С     | -             |

| Y19            | PB32A            | 4    | -     | -             | PB37A            | 4    | _     | -             | PB41A            | 4    | -     | -             |

| AB19           | PB33B            | 4    | -     | -             | PB38B            | 4    | -     | -             | PB42B            | 4    | -     | -             |

| -              | GNDIO4           | 4    | -     | -             | GNDIO4           | 4    | -     | _             | GNDIO4           | 4    | -     | -             |

| AA19           | PB34A            | 4    | Т     | DQS           | PB39A            | 4    | Т     | DQS           | PB43A            | 4    | Т     | DQS           |

| Y20            | PB34B            | 4    | C     | -             | PB39B            | 4    | C     | -             | PB43B            | 4    | C     | -             |

| W14            | PB35A            | 4    | T     | -             | PB40A            | 4    | T     | -             | PB44A            | 4    | T     | -             |

| W14<br>W15     | PB35B            | 4    | C     | -             | PB40B            | 4    | C     | -             | PB44B            | 4    | C     | -             |

| AB20           | PB36A            | 4    | T     | -             | PB41A            | 4    | T     | -             | PB45A            | 4    | T     | -             |

| AB20           | 1 DOUR           | -    | '     | -             |                  | 7    | '     | -             | 1 0404           | 7    | '     | -             |

# LFXP10, LFXP15 & LFXP20 Logic Signal Connections: 388 fpBGA (Cont.)

|        |                 | LFXP10 |      |               |          | ;    |      | LFXP20        |                |      |       |               |

|--------|-----------------|--------|------|---------------|----------|------|------|---------------|----------------|------|-------|---------------|

| Ball   |                 |        | Ball |               |          |      | Ball |               |                |      |       |               |

| Number | Function        | Bank   |      | Dual Function | Function | Bank |      | Dual Function | Function       | Bank | Diff. | Dual Function |

| C20    | PT38A           | 1      | Т    | -             | PT43A    | 1    | Т    | -             | PT47A          | 1    | Т     | -             |

| C21    | PT37B           | 1      | С    | -             | PT42B    | 1    | С    | -             | PT46B          | 1    | С     | -             |

| C22    | PT37A           | 1      | Т    | -             | PT42A    | 1    | Т    | -             | PT46A          | 1    | Т     | -             |

| B22    | PT36B           | 1      | С    | -             | PT41B    | 1    | С    | -             | PT45B          | 1    | С     | -             |

| A21    | PT36A           | 1      | Т    | -             | PT41A    | 1    | Т    | -             | PT45A          | 1    | Т     | -             |

| D15    | PT35B           | 1      | С    | -             | PT40B    | 1    | С    | -             | PT44B          | 1    | С     | -             |

| D14    | PT35A           | 1      | Т    | -             | PT40A    | 1    | Т    | -             | PT44A          | 1    | Т     | -             |

| B21    | PT34B           | 1      | С    | VREF1_1       | PT39B    | 1    | С    | VREF1_1       | PT43B          | 1    | С     | VREF1_1       |

| -      | GNDIO1          | 1      | -    | -             | GNDIO1   | 1    | -    | -             | GNDIO1         | 1    | -     | -             |

| A20    | PT34A           | 1      | Т    | DQS           | PT39A    | 1    | Т    | DQS           | PT43A          | 1    | Т     | DQS           |

| B20    | PT33B           | 1      | -    | -             | PT38B    | 1    | -    | -             | PT42B          | 1    | -     | -             |

| A19    | PT32A           | 1      | -    | -             | PT37A    | 1    | -    | -             | PT41A          | 1    | -     | -             |

| B19    | PT31B           | 1      | С    | -             | PT36B    | 1    | С    | -             | PT40B          | 1    | С     | -             |

| A18    | PT31A           | 1      | Т    | -             | PT36A    | 1    | Т    | -             | PT40A          | 1    | Т     | -             |

| C14    | PT30B           | 1      | С    | -             | PT35B    | 1    | С    | -             | PT39B          | 1    | С     | -             |

| C13    | PT30A           | 1      | Т    | D0            | PT35A    | 1    | Т    | D0            | PT39A          | 1    | Т     | D0            |

| B18    | PT29B           | 1      | С    | D1            | PT34B    | 1    | С    | D1            | PT38B          | 1    | С     | D1            |

| A17    | PT29A           | 1      | Т    | VREF2_1       | PT34A    | 1    | Т    | VREF2_1       | PT38A          | 1    | Т     | VREF2_1       |

| B17    | PT28B           | 1      | С    | -             | PT33B    | 1    | С    | -             | PT37B          | 1    | С     | -             |

| A16    | PT28A           | 1      | Т    | D2            | PT33A    | 1    | Т    | D2            | PT37A          | 1    | Т     | D2            |

| -      | GNDIO1          | 1      | -    |               | GNDIO1   | 1    | _    |               | GNDIO1         | 1    | -     |               |

| B16    | PT27B           | 1      | С    | D3            | PT32B    | 1    | С    | D3            | PT36B          | 1    | С     | D3            |

| A15    | PT27A           | 1      | T    | -             | PT32A    | 1    | T    | -             | PT36A          | 1    | T     | -             |

| B15    | PT26B           | 1      | C    | _             | PT31B    | 1    | C    | -             | PT35B          | 1    | C     | -             |

| A14    | PT26A           | 1      | T    | DQS           | PT31A    | 1    | Т    | DQS           | PT35A          | 1    | Т     | DQS           |

| D13    | PT25B           | 1      | -    | DQ3           | PT30B    | 1    | -    | -             | PT34B          | 1    | -     | -             |

| D13    | PT24A           | 1      | -    | -<br>D4       | PT29A    | 1    | -    | -<br>D4       | PT34B<br>PT33A | 1    | -     | -<br>D4       |

| B14    |                 | 1      | C    | -             |          |      | C    | -             | PT32B          | 1    | C     | -             |

|        | PT23B           | 1      | Т    |               | PT28B    | 1    | Т    |               |                |      | Т     |               |

| A13    | PT23A           |        | -    | D5            | PT28A    | 1    |      | D5            | PT32A          | 1    |       | D5            |

| -      | GNDIO1<br>PT22B | 1      |      | -             | GNDIO1   | 1    | -    | -             | GNDIO1         | 1    | -     | -             |

| B13    |                 | 1      | C    | D6            | PT27B    | 1    | C    | D6            | PT31B          | 1    | C     | D6            |

| A12    | PT22A           | 1      | T    | -             | PT27A    | 1    | Т    | -             | PT31A          | 1    | Т     | -             |

| B12    | PT21B           | 1      | C    | D7            | PT26B    | 1    | C    | D7            | PT30B          | 1    | C     | D7            |

| C12    | PT21A           | 1      | Т    | -             | PT26A    | 1    | Т    | -             | PT30A          | 1    | Т     | -             |

| C11    | PT20B           | 0      | С    | BUSY          | PT25B    | 0    | С    | BUSY          | PT29B          | 0    | С     | BUSY          |

| -      | GNDIO0          | 0      | -    | -             | GNDIO0   | 0    | -    | -             | GNDIO0         | 0    | -     | -             |

| B11    | PT20A           | 0      | Т    | CS1N          | PT25A    | 0    | Т    | CS1N          | PT29A          | 0    | Т     | CS1N          |

| A11    | PT19B           | 0      | С    | PCLKC0_0      | PT24B    | 0    | С    | PCLKC0_0      | PT28B          | 0    | С     | PCLKC0_0      |

| A10    | PT19A           | 0      | Т    | PCLKT0_0      | PT24A    | 0    | Т    | PCLKT0_0      | PT28A          | 0    | Т     | PCLKT0_0      |

| B10    | PT18B           | 0      | С    | -             | PT23B    | 0    | С    | -             | PT27B          | 0    | С     | -             |

| B9     | PT18A           | 0      | Т    | DQS           | PT23A    | 0    | Т    | DQS           | PT27A          | 0    | Т     | DQS           |

| D11    | PT17B           | 0      | -    | -             | PT22B    | 0    | -    | -             | PT26B          | 0    | -     | -             |

| D10    | PT16A           | 0      | -    | DOUT          | PT21A    | 0    | -    | DOUT          | PT25A          | 0    | -     | DOUT          |

| A9     | PT15B           | 0      | С    | -             | PT20B    | 0    | С    | -             | PT24B          | 0    | С     | -             |

| -      | GNDIO0          | 0      | -    | -             | GNDIO0   | 0    | -    | -             | GNDIO0         | 0    | -     | -             |

| C8     | PT15A           | 0      | Т    | WRITEN        | PT20A    | 0    | Т    | WRITEN        | PT24A          | 0    | Т     | WRITEN        |

| B8     | PT14B           | 0      | С    | -             | PT19B    | 0    | С    | -             | PT23B          | 0    | С     | -             |

| A8     | PT14A           | 0      | Т    | VREF1_0       | PT19A    | 0    | Т    | VREF1_0       | PT23A          | 0    | Т     | VREF1_0       |

| C7     | PT13B           | 0      | С    | -             | PT18B    | 0    | С    | -             | PT22B          | 0    | С     | -             |

## **Thermal Management**

Thermal management is recommended as part of any sound FPGA design methodology. To assess the thermal characteristics of a system, Lattice specifies a maximum allowable junction temperature in all device data sheets. Designers must complete a thermal analysis of their specific design to ensure that the device and package do not exceed the junction temperature limits. Refer to the Thermal Management document to find the device/package specific thermal values.

### For Further Information

For further information regarding Thermal Management, refer to the following located on the Lattice website at <u>www.latticesemi.com</u>.

- Thermal Management document

- Technical Note TN1052 Power Estimation and Management for LatticeECP/EC and LatticeXP Devices

- Power Calculator tool included with Lattice's ispLEVER design tool, or as a standalone download from

<u>www.latticesemi.com/software</u>

| Part Number   | I/Os | Voltage | Grade | Package | Pins | Temp. | LUTs |  |  |  |  |  |

|---------------|------|---------|-------|---------|------|-------|------|--|--|--|--|--|

| LFXP6E-3F256C | 188  | 1.2V    | -3    | fpBGA   | 256  | COM   | 5.8K |  |  |  |  |  |

| LFXP6E-4F256C | 188  | 1.2V    | -4    | fpBGA   | 256  | COM   | 5.8K |  |  |  |  |  |

| LFXP6E-5F256C | 188  | 1.2V    | -5    | fpBGA   | 256  | COM   | 5.8K |  |  |  |  |  |

| LFXP6E-3Q208C | 142  | 1.2V    | -3    | PQFP    | 208  | COM   | 5.8K |  |  |  |  |  |

| LFXP6E-4Q208C | 142  | 1.2V    | -4    | PQFP    | 208  | COM   | 5.8K |  |  |  |  |  |

| LFXP6E-5Q208C | 142  | 1.2V    | -5    | PQFP    | 208  | COM   | 5.8K |  |  |  |  |  |

| LFXP6E-3T144C | 100  | 1.2V    | -3    | TQFP    | 144  | COM   | 5.8K |  |  |  |  |  |

| LFXP6E-4T144C | 100  | 1.2V    | -4    | TQFP    | 144  | COM   | 5.8K |  |  |  |  |  |

| LFXP6E-5T144C | 100  | 1.2V    | -5    | TQFP    | 144  | COM   | 5.8K |  |  |  |  |  |

| Part Number    | l/Os | Voltage | Grade | Package | Pins | Temp. | LUTs |

|----------------|------|---------|-------|---------|------|-------|------|

| LFXP10E-3F388C | 244  | 1.2V    | -3    | fpBGA   | 388  | COM   | 9.7K |

| LFXP10E-4F388C | 244  | 1.2V    | -4    | fpBGA   | 388  | COM   | 9.7K |

| LFXP10E-5F388C | 244  | 1.2V    | -5    | fpBGA   | 388  | COM   | 9.7K |

| LFXP10E-3F256C | 188  | 1.2V    | -3    | fpBGA   | 256  | COM   | 9.7K |

| LFXP10E-4F256C | 188  | 1.2V    | -4    | fpBGA   | 256  | COM   | 9.7K |

| LFXP10E-5F256C | 188  | 1.2V    | -5    | fpBGA   | 256  | COM   | 9.7K |

| Part Number    | I/Os | Voltage | Grade | Package | Pins | Temp. | LUTs  |

|----------------|------|---------|-------|---------|------|-------|-------|

| LFXP15E-3F484C | 300  | 1.2V    | -3    | fpBGA   | 484  | COM   | 15.5K |

| LFXP15E-4F484C | 300  | 1.2V    | -4    | fpBGA   | 484  | COM   | 15.5K |

| LFXP15E-5F484C | 300  | 1.2V    | -5    | fpBGA   | 484  | COM   | 15.5K |

| LFXP15E-3F388C | 268  | 1.2V    | -3    | fpBGA   | 388  | COM   | 15.5K |

| LFXP15E-4F388C | 268  | 1.2V    | -4    | fpBGA   | 388  | COM   | 15.5K |

| LFXP15E-5F388C | 268  | 1.2V    | -5    | fpBGA   | 388  | COM   | 15.5K |

| LFXP15E-3F256C | 188  | 1.2V    | -3    | fpBGA   | 256  | COM   | 15.5K |

| LFXP15E-4F256C | 188  | 1.2V    | -4    | fpBGA   | 256  | COM   | 15.5K |

| LFXP15E-5F256C | 188  | 1.2V    | -5    | fpBGA   | 256  | COM   | 15.5K |

### Commercial (Cont.)

| Part Number    | l/Os | Voltage | Grade | Package | Pins | Temp. | LUTs  |

|----------------|------|---------|-------|---------|------|-------|-------|

| LFXP15E-3F484I | 300  | 1.2V    | -3    | fpBGA   | 484  | IND   | 15.5K |

| LFXP15E-4F484I | 300  | 1.2V    | -4    | fpBGA   | 484  | IND   | 15.5K |

| LFXP15E-3F388I | 268  | 1.2V    | -3    | fpBGA   | 388  | IND   | 15.5K |

| LFXP15E-4F388I | 268  | 1.2V    | -4    | fpBGA   | 388  | IND   | 15.5K |

| LFXP15E-3F256I | 188  | 1.2V    | -3    | fpBGA   | 256  | IND   | 15.5K |

| LFXP15E-4F256I | 188  | 1.2V    | -4    | fpBGA   | 256  | IND   | 15.5K |

#### Industrial (Cont.)

| Part Number    | I/Os | Voltage | Grade | Package | Pins | Temp. | LUTs  |

|----------------|------|---------|-------|---------|------|-------|-------|

| LFXP20E-3F484I | 340  | 1.2V    | -3    | fpBGA   | 484  | IND   | 19.7K |

| LFXP20E-4F484I | 340  | 1.2V    | -4    | fpBGA   | 484  | IND   | 19.7K |

| LFXP20E-3F388I | 268  | 1.2V    | -3    | fpBGA   | 388  | IND   | 19.7K |

| LFXP20E-4F388I | 268  | 1.2V    | -4    | fpBGA   | 388  | IND   | 19.7K |

| LFXP20E-3F256I | 188  | 1.2V    | -3    | fpBGA   | 256  | IND   | 19.7K |

| LFXP20E-4F256I | 188  | 1.2V    | -4    | fpBGA   | 256  | IND   | 19.7K |

# LatticeXP Family Data Sheet Revision History

November 2007

### **Revision History**

Data Sheet DS1001

| Date              | Version | Section                             | Change Summary                                                                                                                                                                                                                 |  |  |  |  |  |

|-------------------|---------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| February 2005     | 01.0    | —                                   | Initial release.                                                                                                                                                                                                               |  |  |  |  |  |

| April 2005        | 01.1    | Architecture                        | EBR memory support section updated with clarification.                                                                                                                                                                         |  |  |  |  |  |

| May 2005 01.2     |         | Introduction                        | Added TransFR Reconfiguration to Features section.                                                                                                                                                                             |  |  |  |  |  |

|                   |         | Architecture                        | Added TransFR section.                                                                                                                                                                                                         |  |  |  |  |  |

| June 2005         | 01.3    | Pinout Information                  | Added pinout information for LFXP3, LFXP6, LFXP15 and LFXP20.                                                                                                                                                                  |  |  |  |  |  |

| July 2005         | 02.0    | Introduction                        | Updated XP6, XP15 and XP20 EBR SRAM Bits and Block numbers.                                                                                                                                                                    |  |  |  |  |  |

|                   |         | Architecture                        | Updated Per Quadrant Primary Clock Selection figure.                                                                                                                                                                           |  |  |  |  |  |

|                   |         |                                     | Added Typical I/O Behavior During Power-up section.                                                                                                                                                                            |  |  |  |  |  |

|                   |         |                                     | Updated Device Configuration section under Configuration and Testing.                                                                                                                                                          |  |  |  |  |  |

|                   |         | DC and Switching                    | Clarified Hot Socketing Specification                                                                                                                                                                                          |  |  |  |  |  |

|                   |         | Characteristics                     | Updated Supply Current (Standby) Table                                                                                                                                                                                         |  |  |  |  |  |

|                   |         |                                     | Updated Initialization Supply Current Table                                                                                                                                                                                    |  |  |  |  |  |

|                   |         |                                     | Added Programming and Erase Flash Supply Current table                                                                                                                                                                         |  |  |  |  |  |

|                   |         |                                     | Added LVDS Emulation section. Updated LVDS25E Output Termination<br>Example figure and LVDS25E DC Conditions table.                                                                                                            |  |  |  |  |  |

|                   |         |                                     | Updated Differential LVPECL diagram and LVPECL DC Conditions table.                                                                                                                                                            |  |  |  |  |  |

|                   |         |                                     | Deleted 5V Tolerant Input Buffer section. Updated RSDS figure and RSDS DC Conditions table.                                                                                                                                    |  |  |  |  |  |

|                   |         |                                     | Updated sysCONFIG Port Timing Specifications                                                                                                                                                                                   |  |  |  |  |  |

|                   |         |                                     | Updated JTAG Port Timing Specifications. Added Flash Download Time table.                                                                                                                                                      |  |  |  |  |  |

|                   |         | Pinout Information                  | Updated Signal Descriptions table.                                                                                                                                                                                             |  |  |  |  |  |

|                   |         |                                     | Updated Logic Signal Connections Dual Function column.                                                                                                                                                                         |  |  |  |  |  |

|                   |         | Ordering Information                | Added lead-free ordering part numbers.                                                                                                                                                                                         |  |  |  |  |  |

| July 2005         | 02.1    | DC and Switching<br>Characteristics | Clarification of Flash Programming Junction Temperature                                                                                                                                                                        |  |  |  |  |  |

| August 2005       | 02.2    | Introduction                        | Added Sleep Mode feature.                                                                                                                                                                                                      |  |  |  |  |  |

|                   |         | Architecture                        | Added Sleep Mode section.                                                                                                                                                                                                      |  |  |  |  |  |

|                   |         | DC and Switching                    | Added Sleep Mode Supply Current Table                                                                                                                                                                                          |  |  |  |  |  |

|                   |         | Characteristics                     | Added Sleep Mode Timing section                                                                                                                                                                                                |  |  |  |  |  |

|                   |         | Pinout Information                  | Added SLEEPN and TOE signal names, descriptions and footnotes.                                                                                                                                                                 |  |  |  |  |  |

|                   |         |                                     | Added SLEEPN and TOE to pinout information and footnotes.                                                                                                                                                                      |  |  |  |  |  |

|                   |         |                                     | Added footnote 3 to Logic Signal Connections tables for clarification on emulated LVDS output.                                                                                                                                 |  |  |  |  |  |

| September 2005 03 | 03.0    | Architecture                        | Added clarification of PCI clamp.                                                                                                                                                                                              |  |  |  |  |  |

|                   |         |                                     | Added clarification to SLEEPN Pin Characteristics section.                                                                                                                                                                     |  |  |  |  |  |

|                   |         | DC and Switching<br>Characteristics | DC Characteristics, added footnote 4 for clarification. Updated Supply<br>Current (Sleep Mode), Supply Current (Standby), Initialization Supply<br>Current, and Programming and Erase Flash Supply Current typical<br>numbers. |  |  |  |  |  |

© 2007 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.