Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                   |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | 15000                                                                      |

| Total RAM Bits                 | 331776                                                                     |

| Number of I/O                  | 300                                                                        |

| Number of Gates                | -                                                                          |

| Voltage - Supply               | 1.14V ~ 1.26V                                                              |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 484-BBGA                                                                   |

| Supplier Device Package        | 484-FPBGA (23x23)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfxp15e-3fn484i |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Introduction

The LatticeXP family of FPGA devices combine logic gates, embedded memory and high performance I/Os in a single architecture that is both non-volatile and infinitely reconfigurable to support cost-effective system designs.

The re-programmable non-volatile technology used in the LatticeXP family is the next generation ispXP<sup>™</sup> technology. With this technology, expensive external configuration memories are not required and designs are secured from unauthorized read-back. In addition, instant-on capability allows for easy interfacing in many applications.

The ispLEVER<sup>®</sup> design tool from Lattice allows large complex designs to be efficiently implemented using the LatticeXP family of FPGA devices. Synthesis library support for LatticeXP is available for popular logic synthesis tools. The ispLEVER tool uses the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the LatticeXP device. The ispLEVER tool extracts the timing from the routing and backannotates it into the design for timing verification.

Lattice provides many pre-designed IP (Intellectual Property) ispLeverCORE<sup>™</sup> modules for the LatticeXP family. By using these IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

### Lattice Semiconductor

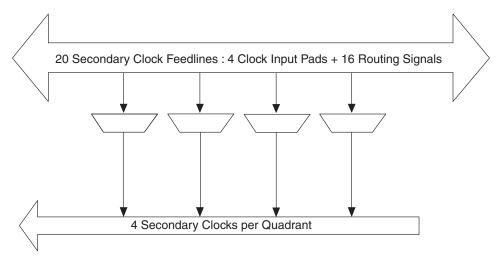

#### Figure 2-8. Per Quadrant Secondary Clock Selection

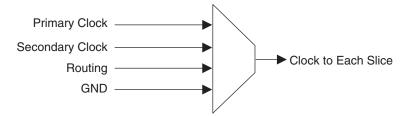

#### Figure 2-9. Slice Clock Selection

### sysCLOCK Phase Locked Loops (PLLs)

The PLL clock input, from pin or routing, feeds into an input clock divider. There are three sources of feedback signals to the feedback divider: from CLKOP (PLL internal), from clock net (CLKOP or CLKOS) or from a user clock (PIN or logic). There is a PLL\_LOCK signal to indicate that VCO has locked on to the input clock signal. Figure 2-10 shows the sysCLOCK PLL diagram.

The setup and hold times of the device can be improved by programming a delay in the feedback or input path of the PLL which will advance or delay the output clock with reference to the input clock. This delay can be either programmed during configuration or can be adjusted dynamically. In dynamic mode, the PLL may lose lock after adjustment and not relock until the t<sub>LOCK</sub> parameter has been satisfied. Additionally, the phase and duty cycle block allows the user to adjust the phase and duty cycle of the CLKOS output.

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. Each PLL has four dividers associated with it: input clock divider, feedback divider, post scalar divider and secondary clock divider. The input clock divider is used to divide the input clock signal, while the feedback divider is used to multiply the input clock signal. The post scalar divider allows the VCO to operate at higher frequencies than the clock output, thereby increasing the frequency range. The secondary divider is used to derive lower frequency outputs.

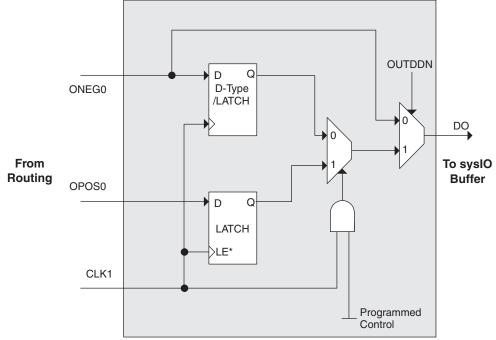

Figure 2-23. Output Register Block

\*Latch is transparent when input is low.

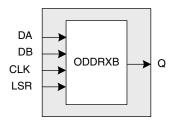

### Figure 2-24. ODDRXB Primitive

### Tristate Register Block

The tristate register block provides the ability to register tri-state control signals from the core of the device before they are passed to the sysIO buffers. The block contains a register for SDR operation and an additional latch for DDR operation. Figure 2-25 shows the diagram of the Tristate Register Block.

In SDR mode, ONEG1 feeds one of the flip-flops that then feeds the output. The flip-flop can be configured a Dtype or latch. In DDR mode, ONEG1 is fed into one register on the positive edge of the clock and OPOS1 is latched. A multiplexer running off the same clock selects the correct register for feeding to the output (D0).

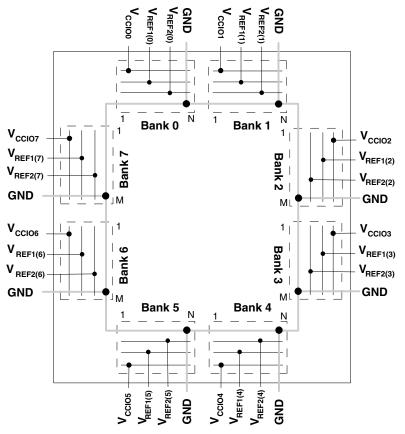

#### Figure 2-28. LatticeXP Banks

Note: N and M are the maximum number of I/Os per bank.

LatticeXP devices contain two types of sysIO buffer pairs.

#### 1. Top and Bottom sysIO Buffer Pair (Single-Ended Outputs Only)

The sysIO buffer pairs in the top and bottom banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (both ratioed and referenced). The referenced input buffer can also be configured as a differential input.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential input buffer and the comp (complementary) pad is associated with the negative side of the differential input buffer.

Only the I/Os on the top and bottom banks have PCI clamps. Note that the PCI clamp is enabled after  $V_{CC,}$   $V_{CCAUX}$  and  $V_{CCIO}$  are at valid operating levels and the device has been configured.

#### 2. Left and Right sysIO Buffer Pair (Differential and Single-Ended Outputs)

The sysIO buffer pairs in the left and right banks of the device consist of two single-ended output drivers, two sets of single-ended input buffers (both ratioed and referenced) and one differential output driver. The referenced input buffer can also be configured as a differential input. In these banks the two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential I/O, and the comp (complementary) pad is associated with the negative side of the differential I/O.

Select I/Os in the left and right banks have LVDS differential output drivers. Refer to the Logic Signal Connections tables for more information.

#### Typical I/O Behavior During Power-up

The internal power-on-reset (POR) signal is deactivated when  $V_{CC}$  and  $V_{CCAUX}$  have reached satisfactory levels. After the POR signal is deactivated, the FPGA core logic becomes active. It is the user's responsibility to ensure that all other  $V_{CCIO}$  banks are active with valid input logic levels to properly control the output logic states of all the I/O banks that are critical to the application. The default configuration of the I/O pins in a blank device is tri-state with a weak pull-up to VCCIO. The I/O pins will not take on the user configuration until VCC, VCCAUX and VCCIO have reached satisfactory levels at which time the I/Os will take on the user-configured settings.

The V<sub>CC</sub> and V<sub>CCAUX</sub> supply the power to the FPGA core fabric, whereas the V<sub>CCIO</sub> supplies power to the I/O buffers. In order to simplify system design while providing consistent and predictable I/O behavior, it is recommended that the I/O buffers be powered-up prior to the FPGA core fabric. V<sub>CCIO</sub> supplies should be powered up before or together with the V<sub>CC</sub> and V<sub>CCAUX</sub> supplies.

#### **Supported Standards**

The LatticeXP sysIO buffer supports both single-ended and differential standards. Single-ended standards can be further subdivided into LVCMOS, LVTTL and other standards. The buffers support the LVTTL, LVCMOS 1.2, 1.5, 1.8, 2.5 and 3.3V standards. In the LVCMOS and LVTTL modes, the buffer has individually configurable options for drive strength, bus maintenance (weak pull-up, weak pull-down, or a bus-keeper latch) and open drain. Other single-ended standards supported include SSTL and HSTL. Differential standards supported include LVDS, BLVDS, LVPECL, differential SSTL and differential HSTL. Tables 2-7 and 2-8 show the I/O standards (together with their supply and reference voltages) supported by the LatticeXP devices. For further information on utilizing the sysIO buffer to support a variety of standards please see the details of additional technical documentation at the end of this data sheet.

| Input Standard                       | V <sub>REF</sub> (Nom.) | V <sub>CCIO</sub> <sup>1</sup> (Nom.) |

|--------------------------------------|-------------------------|---------------------------------------|

| Single Ended Interfaces              |                         | · ·                                   |

| LVTTL                                | —                       | —                                     |

| LVCMOS33 <sup>2</sup>                | —                       | —                                     |

| LVCMOS25 <sup>2</sup>                | —                       | —                                     |

| LVCMOS18                             | —                       | 1.8                                   |

| LVCMOS15                             | —                       | 1.5                                   |

| LVCMOS12 <sup>2</sup>                | —                       | _                                     |

| PCI                                  | —                       | 3.3                                   |

| HSTL18 Class I, II                   | 0.9                     | _                                     |

| HSTL18 Class III                     | 1.08                    | _                                     |

| HSTL15 Class I                       | 0.75                    | —                                     |

| HSTL15 Class III                     | 0.9                     | —                                     |

| SSTL3 Class I, II                    | 1.5                     | _                                     |

| SSTL2 Class I, II                    | 1.25                    | —                                     |

| SSTL18 Class I                       | 0.9                     | —                                     |

| Differential Interfaces              |                         | · ·                                   |

| Differential SSTL18 Class I          | —                       | —                                     |

| Differential SSTL2 Class I, II       | —                       | _                                     |

| Differential SSTL3 Class I, II       | —                       | _                                     |

| Differential HSTL15 Class I, III     | —                       | —                                     |

| Differential HSTL18 Class I, II, III | _                       | -                                     |

| LVDS, LVPECL                         | _                       | _                                     |

| BLVDS                                | —                       | —                                     |

#### Table 2-7. Supported Input Standards

1. When not specified  $V_{\mbox{CCIO}}$  can be set anywhere in the valid operating range.

2. JTAG inputs do not have a fixed threshold option and always follow  $V_{\mbox{CCJ.}}$

## sysIO Differential Electrical Characteristics LVDS

| Parameter<br>Symbol                | Parameter Description                          | Test Conditions                               | Min.                | Тур. | Max.  | Units |

|------------------------------------|------------------------------------------------|-----------------------------------------------|---------------------|------|-------|-------|

| V <sub>INP,</sub> V <sub>INM</sub> | Input Voltage                                  |                                               | 0                   | _    | 2.4   | V     |

| V <sub>THD</sub>                   | Differential Input Threshold                   |                                               | +/-100              | _    | _     | mV    |

|                                    |                                                | $100mV \le V_{THD}$                           | V <sub>THD</sub> /2 | 1.2  | 1.8   | V     |

| V <sub>CM</sub>                    | Input Common Mode Voltage                      | $200mV \le V_{THD}$                           | V <sub>THD</sub> /2 | 1.2  | 1.9   | V     |

|                                    |                                                | $350mV \le V_{THD}$                           | V <sub>THD</sub> /2 | 1.2  | 2.0   | V     |

| I <sub>IN</sub>                    | Input current                                  | Power on or power off                         |                     |      | +/-10 | μA    |

| V <sub>OH</sub>                    | Output high voltage for $V_{OP}$ or $V_{OM}$   | R <sub>T</sub> = 100 ohms                     | _                   | 1.38 | 1.60  | V     |

| V <sub>OL</sub>                    | Output low voltage for $V_{OP}$ or $V_{OM}$    | R <sub>T</sub> = 100 ohms                     | 0.9V                | 1.03 | —     | V     |

| V <sub>OD</sub>                    | Output voltage differential                    | $(V_{OP} - V_{OM}), R_T = 100 \text{ ohms}$   | 250                 | 350  | 450   | mV    |

| $\Delta V_{OD}$                    | Change in V <sub>OD</sub> between high and low |                                               | _                   | _    | 50    | mV    |

| V <sub>OS</sub>                    | Output voltage offset                          | $(V_{OP} - V_{OM})/2, R_T = 100 \text{ ohms}$ | 1.125               | 1.25 | 1.375 | V     |

| $\Delta V_{OS}$                    | Change in V <sub>OS</sub> between H and L      |                                               | —                   | _    | 50    | mV    |

| I <sub>OSD</sub>                   | Output short circuit current                   | V <sub>OD</sub> = 0V Driver outputs shorted   | _                   | _    | 6     | mA    |

### **Over Recommended Operating Conditions**

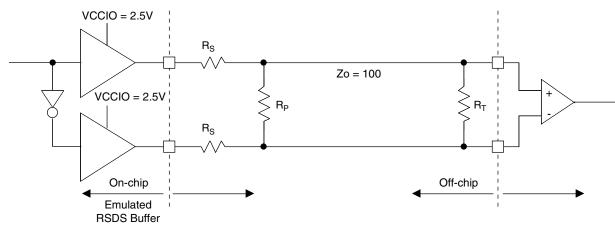

### Figure 3-4. RSDS (Reduced Swing Differential Standard)

#### Table 3-4. RSDS DC Conditions

| Parameter         | Description                 | Typical | Units |

|-------------------|-----------------------------|---------|-------|

| Z <sub>OUT</sub>  | Output impedance            | 20      | ohms  |

| R <sub>S</sub>    | Driver series resistor      | 300     | ohms  |

| R <sub>P</sub>    | Driver parallel resistor    | 121     | ohms  |

| R <sub>T</sub>    | Receiver termination        | 100     | ohms  |

| V <sub>OH</sub>   | Output high voltage         | 1.35    | V     |

| V <sub>OL</sub>   | Output low voltage          | 1.15    | V     |

| V <sub>OD</sub>   | Output differential voltage | 0.20    | V     |

| V <sub>CM</sub>   | Output common mode voltage  | 1.25    | V     |

| Z <sub>BACK</sub> | Back impedance              | 101.5   | ohms  |

| I <sub>DC</sub>   | DC output current           | 3.66    | mA    |

## Typical Building Block Function Performance<sup>1</sup>

### Pin-to-Pin Performance (LVCMOS25 12 mA Drive)

| Function        | -5 Timing | Units |

|-----------------|-----------|-------|

| Basic Functions |           |       |

| 16-bit decoder  | 6.1       | ns    |

| 32-bit decoder  | 7.3       | ns    |

| 64-bit decoder  | 8.2       | ns    |

| 4:1 MUX         | 4.9       | ns    |

| 8:1 MUX         | 5.3       | ns    |

| 16:1 MUX        | 5.7       | ns    |

| 32:1 MUX        | 6.3       | ns    |

### **Register to Register Performance**

| Function                       | -5 Timing | Units |

|--------------------------------|-----------|-------|

| Basic Functions                |           |       |

| 16-bit decoder                 | 351       | MHz   |

| 32-bit decoder                 | 248       | MHz   |

| 64-bit decoder                 | 237       | MHz   |

| 4:1 MUX                        | 590       | MHz   |

| 8:1 MUX                        | 523       | MHz   |

| 16:1 MUX                       | 434       | MHz   |

| 32:1 MUX                       | 355       | MHz   |

| 8-bit adder                    | 343       | MHz   |

| 16-bit adder                   | 292       | MHz   |

| 64-bit adder                   | 130       | MHz   |

| 16-bit counter                 | 388       | MHz   |

| 32-bit counter                 | 295       | MHz   |

| 64-bit counter                 | 200       | MHz   |

| 64-bit accumulator             | 164       | MHz   |

| Embedded Memory Functions      |           |       |

| Single Port RAM 256x36 bits    | 254       | MHz   |

| True-Dual Port RAM 512x18 bits | 254       | MHz   |

| Distributed Memory Functions   |           |       |

| 16x2 SP RAM                    | 434       | MHz   |

| 64x2 SP RAM                    | 332       | MHz   |

| 128x4 SP RAM                   | 235       | MHz   |

| 32x2 PDP RAM                   | 322       | MHz   |

| 64x4 PDP RAM                   | 291       | MHz   |

1. These timing numbers were generated using the ispLEVER design tool. Exact performance may vary with design and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

Timing v.F0.11

## **Derating Logic Timing**

Logic timing provided in the following sections of this data sheet and in the ispLEVER design tools are worst case numbers in the operating range. Actual delays at nominal temperature and voltage for best-case process can be much better than the values given in the tables. The ispLEVER design tool from Lattice can provide logic timing numbers at a particular temperature and voltage.

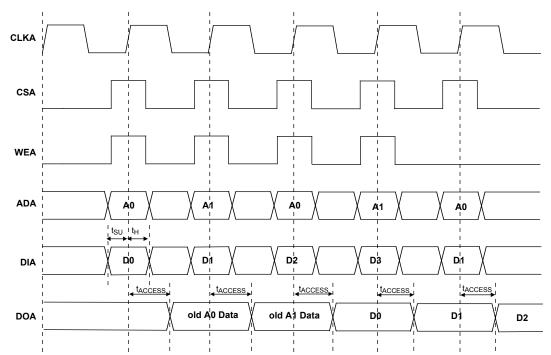

Figure 3-10. Read Before Write (SP Read/Write on Port A, Input Registers Only)

Note: Input data and address are registered at the positive edge of the clock and output data appears after the positive of the clock.

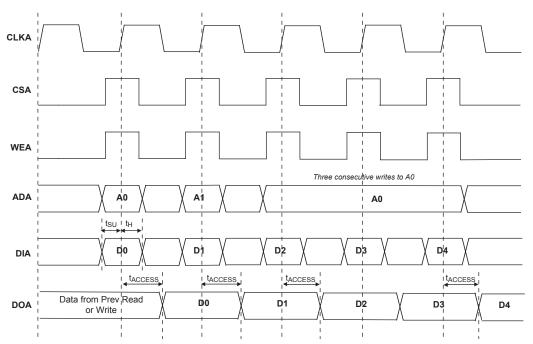

Figure 3-11. Write Through (SP Read/Write On Port A, Input Registers Only)

Note: Input data and address are registered at the positive edge of the clock and output data appears after the positive of the clock.

## LatticeXP Family Timing Adders<sup>1</sup> (Continued)

| Buffer Type   | Description                    | -5   | -4   | -3   | Units |

|---------------|--------------------------------|------|------|------|-------|

| HSTL15_I      | HSTL_15 class I                | 0.2  | 0.2  | 0.2  | ns    |

| HSTL15_III    | HSTL_15 class III              | 0.2  | 0.2  | 0.2  | ns    |

| HSTL15D_I     | Differential HSTL 15 class I   | 0.2  | 0.2  | 0.2  | ns    |

| HSTL15D_III   | Differential HSTL 15 class III | 0.2  | 0.2  | 0.2  | ns    |

| SSTL33_I      | SSTL_3 class I                 | 0.1  | 0.1  | 0.1  | ns    |

| SSTL33_II     | SSTL_3 class II                | 0.3  | 0.3  | 0.3  | ns    |

| SSTL33D_I     | Differential SSTL_3 class I    | 0.1  | 0.1  | 0.1  | ns    |

| SSTL33D_II    | Differential SSTL_3 class II   | 0.3  | 0.3  | 0.3  | ns    |

| SSTL25_I      | SSTL_2 class I                 | -0.1 | -0.1 | -0.1 | ns    |

| SSTL25_II     | SSTL_2 class II                | 0.3  | 0.3  | 0.3  | ns    |

| SSTL25D_I     | Differential SSTL_2 class I    | -0.1 | -0.1 | -0.1 | ns    |

| SSTL25D_II    | Differential SSTL_2 class II   | 0.3  | 0.3  | 0.3  | ns    |

| SSTL18_I      | SSTL_1.8 class I               | 0.1  | 0.1  | 0.1  | ns    |

| SSTL18D_I     | Differential SSTL_1.8 class I  | 0.1  | 0.1  | 0.1  | ns    |

| VTTL33_4mA    | LVTTL 4mA drive                | 0.8  | 0.8  | 0.8  | ns    |

| VTTL33_8mA    | LVTTL 8mA drive                | 0.5  | 0.5  | 0.5  | ns    |

| VTTL33_12mA   | LVTTL 12mA drive               | 0.3  | 0.3  | 0.3  | ns    |

| VTTL33_16mA   | LVTTL 16mA drive               | 0.4  | 0.4  | 0.4  | ns    |

| VTTL33_20mA   | LVTTL 20mA drive               | 0.3  | 0.3  | 0.3  | ns    |

| VCMOS33_2mA   | LVCMOS 3.3 2mA drive           | 0.8  | 0.8  | 0.8  | ns    |

| VCMOS33_4mA   | LVCMOS 3.3 4mA drive           | 0.8  | 0.8  | 0.8  | ns    |

| VCMOS33_8mA   | LVCMOS 3.3 8mA drive           | 0.5  | 0.5  | 0.5  | ns    |

| VCMOS33_12mA  | LVCMOS 3.3 12mA drive          | 0.3  | 0.3  | 0.3  | ns    |

| LVCMOS33_16mA | LVCMOS 3.3 16mA drive          | 0.4  | 0.4  | 0.4  | ns    |

| LVCMOS33_20mA | LVCMOS 3.3 20mA drive          | 0.3  | 0.3  | 0.3  | ns    |

| LVCMOS25_2mA  | LVCMOS 2.5 2mA drive           | 0.7  | 0.7  | 0.7  | ns    |

| LVCMOS25_4mA  | LVCMOS 2.5 4mA drive           | 0.7  | 0.7  | 0.7  | ns    |

| VCMOS25_8mA   | LVCMOS 2.5 8mA drive           | 0.4  | 0.4  | 0.4  | ns    |

| VCMOS25_12mA  | LVCMOS 2.5 12mA drive          | 0.0  | 0.0  | 0.0  | ns    |

| VCMOS25_16mA  | LVCMOS 2.5 16mA drive          | 0.2  | 0.2  | 0.2  | ns    |

| VCMOS25_20mA  | LVCMOS 2.5 20mA drive          | 0.4  | 0.4  | 0.4  | ns    |

| VCMOS18_2mA   | LVCMOS 1.8 2mA drive           | 0.6  | 0.6  | 0.6  | ns    |

| VCMOS18_4mA   | LVCMOS 1.8 4mA drive           | 0.6  | 0.6  | 0.6  | ns    |

|               | LVCMOS 1.8 8mA drive           | 0.4  | 0.4  | 0.4  | ns    |

| VCMOS18_12mA  | LVCMOS 1.8 12mA drive          | 0.2  | 0.2  | 0.2  | ns    |

| VCMOS18_16mA  | LVCMOS 1.8 16mA drive          | 0.2  | 0.2  | 0.2  | ns    |

|               | LVCMOS 1.5 2mA drive           | 0.6  | 0.6  | 0.6  | ns    |

|               | LVCMOS 1.5 4mA drive           | 0.6  | 0.6  | 0.6  | ns    |

|               | LVCMOS 1.5 8mA drive           | 0.2  | 0.2  | 0.2  | ns    |

| VCMOS12_2mA   | LVCMOS 1.2 2mA drive           | 0.4  | 0.4  | 0.4  | ns    |

| LVCMOS12_6mA  | LVCMOS 1.2 6mA drive           | 0.4  | 0.4  | 0.4  | ns    |

| PCI33         | PCI33                          | 0.3  | 0.3  | 0.3  | ns    |

1. General timing numbers based on LVCMOS 2.5, 12mA.

Timing v.F0.11

# LatticeXP Family Data Sheet Pinout Information

November 2007

Data Sheet DS1001

## **Signal Descriptions**

| Signal Name                                 | I/O    | Descriptions                                                                                                                                                                                                                                                          |

|---------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Purpose                             |        |                                                                                                                                                                                                                                                                       |

|                                             |        | [Edge] indicates the edge of the device on which the pad is located. Valid edge designations are L (Left), B (Bottom), R (Right), T (Top).                                                                                                                            |

|                                             |        | [Row/Column Number] indicates the PFU row or the column of the device on which the PIC exists. When Edge is T (Top) or (Bottom), only need to specify Row Number. When Edge is L (Left) or R (Right), only need to specify Column Number.                             |

| P[Edge] [Row/Column Number*]_[A/B]          | I/O    | [A/B] indicates the PIO within the PIC to which the pad is connected.                                                                                                                                                                                                 |

|                                             |        | Some of these user programmable pins are shared with special function pins. These pin when not used as special purpose pins can be programmed as $I/Os$ for user logic.                                                                                               |

|                                             |        | During configuration, the user-programmable I/Os are tri-stated with an inter-<br>nal pull-up resistor enabled. If any pin is not used (or not bonded to a pack-<br>age pin), it is also tri-stated with an internal pull-up resistor enabled after<br>configuration. |

| GSRN                                        | I      | Global RESET signal. (Active low). Any I/O pin can be configured to be GSRN.                                                                                                                                                                                          |

| NC                                          |        | No connect.                                                                                                                                                                                                                                                           |

| GND                                         | _      | GND - Ground. Dedicated Pins.                                                                                                                                                                                                                                         |

| V <sub>CC</sub>                             |        | VCC - The power supply pins for core logic. Dedicated Pins.                                                                                                                                                                                                           |

| V <sub>CCAUX</sub>                          | —      | $V_{CCAUX}$ - The Auxiliary power supply pin. It powers all the differential and referenced input buffers. Dedicated Pins.                                                                                                                                            |

| V <sub>CCP0</sub>                           |        | Voltage supply pins for ULM0PLL (and LLM1PLL <sup>1</sup> ).                                                                                                                                                                                                          |

| V <sub>CCP1</sub>                           |        | Voltage supply pins for URM0PLL (and LRM1PLL <sup>1</sup> ).                                                                                                                                                                                                          |

| GNDP0                                       | _      | Ground pins for ULM0PLL (and LLM1PLL <sup>1</sup> ).                                                                                                                                                                                                                  |

| GNDP1                                       |        | Ground pins for URM0PLL (and LRM1PLL <sup>1</sup> ).                                                                                                                                                                                                                  |

| V <sub>CCIOx</sub>                          | _      | V <sub>CCIO</sub> - The power supply pins for I/O bank x. Dedicated Pins.                                                                                                                                                                                             |

| V <sub>REF1(x)</sub> , V <sub>REF2(x)</sub> | —      | Reference supply pins for I/O bank x. Pre-determined pins in each bank are assigned as $V_{\text{REF}}$ inputs. When not used, they may be used as I/O pins.                                                                                                          |

| PLL and Clock Functions (Used as user       | progra | ammable I/O pins when not in use for PLL or clock pins)                                                                                                                                                                                                               |

| [LOC][num]_PLL[T, C]_IN_A                   | _      | Reference clock (PLL) input Pads: ULM, LLM, URM, LRM, num = row from center, $T =$ true and $C =$ complement, index A, B, Cat each side.                                                                                                                              |

| [LOC][num]_PLL[T, C]_FB_A                   | _      | Optional feedback (PLL) input Pads: ULM, LLM, URM, LRM, num = row from center, $T =$ true and $C =$ complement, index A, B, Cat each side.                                                                                                                            |

| PCLK[T, C]_[n:0]_[3:0]                      | _      | Primary Clock Pads, T = true and C = complement, n per side, indexed by bank and 0,1, 2, 3 within bank.                                                                                                                                                               |

| [LOC]DQS[num]                               | _      | DQS input Pads: T (Top), R (Right), B (Bottom), L (Left), DQS, num = Ball function number. Any pad can be configured to be DQS output.                                                                                                                                |

<sup>© 2007</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## **Power Supply and NC Connections**

| Signals            | 100 TQFP                                             | 144 TQFP                                                               | 208 PQFP                                                                                                                          | 256 fpBGA                                                                                                                         | 388 fpBGA                                                                                                                                                                                                                                                                                             | 484 fpBGA                                                                                                                                                                                                                                                                                                                          |

|--------------------|------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub>    | 28, 77                                               | 14, 39, 73, 112                                                        | 19, 35, 53, 80, 107,<br>151, 158, 182                                                                                             | D4, D13, E5, E12,<br>M5, M12, N4, N13                                                                                             | H9, J8, J15, K8,<br>K15, L8, L15, M8,<br>M15, N8, N15, P8,<br>P15, R9                                                                                                                                                                                                                                 | F10, F13, G9, G10,<br>G13, G14, H8,<br>H15, J7, J16, K6,<br>K7, K16, K17, N6,<br>N7, N16, N17, P7,<br>P16, R8, R15, T9,<br>T10, T13, T14,<br>U10, U13                                                                                                                                                                              |

| V <sub>CCIO0</sub> | 94                                                   | 133                                                                    | 189, 199                                                                                                                          | F7, F8                                                                                                                            | G8, G9, G10, G11,<br>H8                                                                                                                                                                                                                                                                               | F11, G11, H10,<br>H11                                                                                                                                                                                                                                                                                                              |

| V <sub>CCIO1</sub> | 82                                                   | 119                                                                    | 167, 177                                                                                                                          | F9, F10                                                                                                                           | G12, G13, G14,<br>G15, H15                                                                                                                                                                                                                                                                            | F12, G12, H12,<br>H13                                                                                                                                                                                                                                                                                                              |

| V <sub>CCIO2</sub> | 65                                                   | 98                                                                     | 140, 149                                                                                                                          | G11, H11                                                                                                                          | H16, J16, K16, L16                                                                                                                                                                                                                                                                                    | K15, L15, L16, L17                                                                                                                                                                                                                                                                                                                 |

| V <sub>CCIO3</sub> | 58                                                   | 88                                                                     | 115, 125                                                                                                                          | J11, K11                                                                                                                          | M16, N16, P16,<br>R16                                                                                                                                                                                                                                                                                 | M15, M16, M17,<br>N15                                                                                                                                                                                                                                                                                                              |

| V <sub>CCIO4</sub> | 47                                                   | 61, 68                                                                 | 87, 97                                                                                                                            | L9, L10                                                                                                                           | R15, T12, T13,<br>T14, T15                                                                                                                                                                                                                                                                            | R12, R13, T12,<br>U12                                                                                                                                                                                                                                                                                                              |

| V <sub>CCIO5</sub> | 38                                                   | 49                                                                     | 64, 74                                                                                                                            | L7, L8                                                                                                                            | R8, T8, T9, T10,<br>T11                                                                                                                                                                                                                                                                               | R10, R11, T11,<br>U11                                                                                                                                                                                                                                                                                                              |

| V <sub>CCIO6</sub> | 22                                                   | 21                                                                     | 28, 41                                                                                                                            | J6, K6                                                                                                                            | M7, N7, P7, R7                                                                                                                                                                                                                                                                                        | M6, M7, M8, N8                                                                                                                                                                                                                                                                                                                     |

| V <sub>CCIO7</sub> | 7                                                    | 8                                                                      | 13, 23                                                                                                                            | G6, H6                                                                                                                            | H7, J7, K7, L7                                                                                                                                                                                                                                                                                        | K8, L6, L7, L8                                                                                                                                                                                                                                                                                                                     |

| V <sub>CCJ</sub>   | 73                                                   | 108                                                                    | 154                                                                                                                               | D16                                                                                                                               | E20                                                                                                                                                                                                                                                                                                   | E20                                                                                                                                                                                                                                                                                                                                |

| V <sub>CCP0</sub>  | 17                                                   | 19                                                                     | 25                                                                                                                                | H4                                                                                                                                | M2                                                                                                                                                                                                                                                                                                    | L5                                                                                                                                                                                                                                                                                                                                 |

| V <sub>CCP1</sub>  | 60                                                   | 91                                                                     | 128                                                                                                                               | J12                                                                                                                               | M21                                                                                                                                                                                                                                                                                                   | L18                                                                                                                                                                                                                                                                                                                                |

| V <sub>CCAUX</sub> | 25, 71                                               | 36, 106                                                                | 50, 152                                                                                                                           | E4, E13, M4, M13                                                                                                                  | G7, G16, T7, T16                                                                                                                                                                                                                                                                                      | G7, G8, G15, G16,<br>H7, H16, R7, R16,<br>T7, T8, T15, T16                                                                                                                                                                                                                                                                         |

| GND <sup>1</sup>   | 10, 18, 21, 33, 43,<br>44, 52, 59, 68, 84,<br>90, 99 | 3, 11, 20, 28, 44,<br>54, 56, 64, 75, 85,<br>90, 101, 121, 127,<br>136 | 5, 7, 16, 26, 38, 47,<br>49, 59, 69, 79, 82,<br>92, 106, 109, 118,<br>121, 127, 130, 135,<br>143, 163, 172, 181,<br>184, 194, 207 | A1, A16, F6, F11,<br>G7, G8, G9, G10,<br>H5, H7, H8, H9,<br>H10, J7, J8, J9,<br>J10, J13, K7, K8,<br>K9, K10, L6, L11,<br>T1, T16 | A1, A22, H10, H11,<br>H12, H13, H14, J9,<br>J10, J11, J12, J13,<br>J14, K9, K10, K11,<br>K12, K13, K14, L9,<br>L10, L11, L12, L13,<br>L14, M9, M10,<br>M11, M12, M13,<br>M14, N1, N9, N10,<br>N11, N12, N13,<br>N14, N22, P9, P10,<br>P11, P12, P13,<br>P14, R10, R11,<br>R12, R13, R14,<br>AB1, AB22 | A1, A2, A21, A22,<br>B1, B22, H9, H14,<br>J8, J9, J10, J11,<br>J12, J13, J14, J15,<br>K9, K10, K11, K12,<br>K13, K14, L9, L10,<br>L11, L12, L13, L14,<br>M9, M10, M11,<br>M12, M13, M14,<br>M20, N2, N9, N10,<br>N11, N12, N13,<br>N14, P8, P9, P10,<br>P11, P12, P13,<br>P14, P15, R9, R14,<br>AA1, AA22, AB1,<br>AB2, AB21, AB22 |

| NC <sup>2</sup>    |                                                      |                                                                        | XP3: 27, 33, 34,<br>129, 133, 134                                                                                                 |                                                                                                                                   | XP10: C2, C15,<br>C16, C17, D4, D5,<br>D6, D7, D16, D17,<br>E4, E19, W3, W4,<br>W7, W17, W18,<br>W19, W20, Y3,<br>Y15, Y16, AA1,<br>AA2                                                                                                                                                               | XP15: B21, C4, C5,<br>C6, C18, C19, C20,<br>C21, D6, D18, E4,<br>E6, E18, F6, L1,<br>L19, L20, M1, M2,<br>M19, M21, N1,<br>N21, N22, P1, P2,<br>U5, U6, U17, U18,<br>V5, V6, V17, V18,<br>W17, W18, W19,<br>Y3, Y4, Y5                                                                                                             |

All grounds must be electrically connected at the board level.

NC pins should not be connected to any active signals, V<sub>CC</sub> or GND.

## LFXP3 & LFXP6 Logic Signal Connections: 144 TQFP (Cont.)

| Pin    | LFXP3        |      |              |               |              |      | LFXP6        |               |

|--------|--------------|------|--------------|---------------|--------------|------|--------------|---------------|

| Number | Pin Function | Bank | Differential | Dual Function | Pin Function | Bank | Differential | Dual Function |

| 139    | PT6A         | 0    | -            | DI            | PT9A         | 0    | -            | DI            |

| 140    | PT5A         | 0    | -            | CSN           | PT8A         | 0    | -            | CSN           |

| 141    | PT3B         | 0    | -            | VREF2_0       | PT6B         | 0    | -            | VREF2_0       |

| 142    | CFG0         | 0    | -            | -             | CFG0         | 0    | -            | -             |

| 143    | CFG1         | 0    | -            | -             | CFG1         | 0    | -            | -             |

| 144    | DONE         | 0    | -            | -             | DONE         | 0    | -            | -             |

1. Applies to LFXP "C" only.

2. Applies to LFXP "E" only.

3. Supports dedicated LVDS outputs.

## LFXP6 & LFXP10 Logic Signal Connections: 256 fpBGA (Cont.)

|                |                  |      | LFXP6          |                  |                  |      | LFXP10         |                  |

|----------------|------------------|------|----------------|------------------|------------------|------|----------------|------------------|

| Ball<br>Number | Ball<br>Function | Bank | Differential   | Dual<br>Function | Ball<br>Function | Bank | Differential   | Dual<br>Function |

| R8             | PB16A            | 5    | Т              | -                | PB20A            | 5    | Т              | -                |

| Т9             | PB16B            | 5    | С              | -                | PB20B            | 5    | С              | -                |

| R9             | PB17A            | 4    | Т              | -                | PB21A            | 4    | Т              | -                |

| -              | GNDIO4           | 4    | -              | -                | GNDIO4           | 4    | -              | -                |

| P9             | PB17B            | 4    | С              | -                | PB21B            | 4    | С              | -                |

| T10            | PB18A            | 4    | Т              | PCLKT4_0         | PB22A            | 4    | Т              | PCLKT4_0         |

| T11            | PB18B            | 4    | С              | PCLKC4_0         | PB22B            | 4    | С              | PCLKC4_0         |

| R10            | PB19A            | 4    | Т              | -                | PB23A            | 4    | Т              | -                |

| P10            | PB19B            | 4    | С              | -                | PB23B            | 4    | С              | -                |

| N9             | PB20A            | 4    | -              | -                | PB24A            | 4    | -              | -                |

| M9             | PB21B            | 4    | -              | -                | PB25B            | 4    | -              | -                |

| R12            | PB22A            | 4    | Т              | DQS              | PB26A            | 4    | Т              | DQS              |

| -              | GNDIO4           | 4    | -              | -                | GNDIO4           | 4    | -              | -                |

| T12            | PB22B            | 4    | С              | VREF1_4          | PB26B            | 4    | С              | VREF1_4          |

| P13            | PB23A            | 4    | Т              | -                | PB27A            | 4    | Т              | -                |

| R13            | PB23B            | 4    | С              | -                | PB27B            | 4    | С              | -                |

| M11            | PB24A            | 4    | Т              | -                | PB28A            | 4    | Т              | -                |

| N11            | PB24B            | 4    | С              | -                | PB28B            | 4    | С              | -                |

| N10            | PB25A            | 4    | Т              | -                | PB29A            | 4    | Т              | -                |

| M10            | PB25B            | 4    | С              | -                | PB29B            | 4    | С              | -                |

| T13            | PB26A            | 4    | Т              | -                | PB30A            | 4    | Т              | -                |

| -              | GNDIO4           | 4    | -              | -                | GNDIO4           | 4    | -              | -                |

| P14            | PB26B            | 4    | С              | -                | PB30B            | 4    | С              | -                |

| R11            | PB27A            | 4    | Т              | VREF2_4          | PB31A            | 4    | Т              | VREF2_4          |

| P12            | PB27B            | 4    | С              | -                | PB31B            | 4    | С              | -                |

| T14            | PB28A            | 4    | -              | -                | PB32A            | 4    | -              | -                |

| R14            | PB29B            | 4    | -              | -                | PB33B            | 4    | -              | -                |

| P11            | PB30A            | 4    | Т              | DQS              | PB34A            | 4    | Т              | DQS              |

| N12            | PB30B            | 4    | С              | -                | PB34B            | 4    | С              | -                |

| T15            | PB31A            | 4    | Т              | -                | PB35A            | 4    | Т              | -                |

| -              | GNDIO4           | 4    | -              | -                | GNDIO4           | 4    | -              | -                |

| R15            | PB31B            | 4    | С              | -                | PB35B            | 4    | С              | -                |

| -              | GNDIO3           | 3    | -              | -                | GNDIO3           | 3    | -              | -                |

| P15            | PR26B            | 3    | C <sup>3</sup> | -                | PR34B            | 3    | С              | RLM0_PLLC_FB_A   |

| N15            | PR26A            | 3    | T <sup>3</sup> | -                | PR34A            | 3    | Т              | RLM0_PLLT_FB_A   |

| P16            | PR24B            | 3    | C <sup>3</sup> | -                | PR33B            | 3    | C <sup>3</sup> | -                |

| R16            | PR24A            | 3    | T <sup>3</sup> | DQS              | PR33A            | 3    | T <sup>3</sup> | DQS              |

| M15            | PR15B            | 3    | -              | -                | PR32B            | 3    | -              | -                |

| N14            | PR23B            | 3    | -              | VREF1_3          | PR31A            | 3    | -              | VREF1_3          |

| -              | GNDIO3           | 3    | -              | -                | GNDIO3           | 3    | -              | -                |

| M14            | PR25B            | 3    | С              | -                | PR29B            | 3    | С              | -                |

| L13            | PR25A            | 3    | Т              | -                | PR29A            | 3    | Т              | -                |

## LFXP10, LFXP15 & LFXP20 Logic Signal Connections: 388 fpBGA

|        |          | L    | .FXP1          | 0              | _        | 1    | _FXP1          | 5              | LFXP20   |      | )              |                |

|--------|----------|------|----------------|----------------|----------|------|----------------|----------------|----------|------|----------------|----------------|

| Ball   | Ball     |      |                |                | Ball     |      |                |                | Ball     |      |                |                |

| Number | Function | Bank | Diff.          | Dual Function  | Function | Bank | Diff.          | Dual Function  | Function | Bank | Diff.          | Dual Function  |

| F4     | PROGRAMN | 7    | -              | -              | PROGRAMN | 7    | -              | -              | PROGRAMN | 7    | -              | -              |

| G4     | CCLK     | 7    | -              | -              | CCLK     | 7    | -              | -              | CCLK     | 7    | -              | -              |

| -      | GNDIO7   | 7    | -              | -              | GNDIO7   | 7    | -              | -              | GNDIO7   | 7    | -              | -              |

| D2     | PL2A     | 7    | T <sup>3</sup> | -              | PL6A     | 7    | T <sup>3</sup> | -              | PL6A     | 7    | T <sup>3</sup> | -              |

| D1     | PL2B     | 7    | C <sup>3</sup> | -              | PL6B     | 7    | C <sup>3</sup> | -              | PL6B     | 7    | C <sup>3</sup> | -              |

| -      | GNDIO7   | 7    | -              | -              | GNDIO7   | 7    | -              | -              | GNDIO7   | 7    | -              | -              |

| E2     | PL3A     | 7    | Т              | LUM0_PLLT_FB_A | PL7A     | 7    | Т              | LUM0_PLLT_FB_A | PL7A     | 7    | Т              | LUM0_PLLT_FB_A |

| E3     | PL3B     | 7    | С              | LUM0_PLLC_FB_A | PL7B     | 7    | С              | LUM0_PLLC_FB_A | PL7B     | 7    | С              | LUM0_PLLC_FB_A |

| F3     | PL4A     | 7    | T <sup>3</sup> | -              | PL8A     | 7    | T <sup>3</sup> | -              | PL8A     | 7    | T <sup>3</sup> | -              |

| F2     | PL4B     | 7    | C <sup>3</sup> | -              | PL8B     | 7    | C <sup>3</sup> | -              | PL8B     | 7    | C <sup>3</sup> | -              |

| H4     | PL5A     | 7    | -              | -              | PL9A     | 7    | -              | -              | PL9A     | 7    | -              | -              |

| H3     | PL6B     | 7    | -              | VREF1_7        | PL10B    | 7    | -              | VREF1_7        | PL10B    | 7    | -              | VREF1_7        |

| G3     | PL7A     | 7    | Т³             | DQS            | PL11A    | 7    | T <sup>3</sup> | DQS            | PL11A    | 7    | Т³             | DQS            |

| G2     | PL7B     | 7    | C <sup>3</sup> | -              | PL11B    | 7    | C <sup>3</sup> | -              | PL11B    | 7    | C <sup>3</sup> | -              |

| -      | GNDIO7   | 7    | -              | -              | GNDIO7   | 7    | -              | -              | GNDIO7   | 7    | -              | -              |

| F1     | PL8A     | 7    | Т              | -              | PL12A    | 7    | Т              | -              | PL12A    | 7    | Т              | -              |

| E1     | PL8B     | 7    | С              | -              | PL12B    | 7    | С              | -              | PL12B    | 7    | С              | -              |

| J4     | PL9A     | 7    | T <sup>3</sup> | -              | PL13A    | 7    | T <sup>3</sup> | -              | PL13A    | 7    | T <sup>3</sup> | -              |

| K4     | PL9B     | 7    | C <sup>3</sup> | -              | PL13B    | 7    | C <sup>3</sup> | -              | PL13B    | 7    | C <sup>3</sup> | -              |

| G1     | PL11A    | 7    | Т³             | -              | PL15A    | 7    | T <sup>3</sup> | -              | PL15A    | 7    | T <sup>3</sup> | -              |

| H2     | PL11B    | 7    | C <sup>3</sup> | -              | PL15B    | 7    | C <sup>3</sup> | -              | PL15B    | 7    | C <sup>3</sup> | -              |

| -      | GNDIO7   | 7    | -              | -              | GNDIO7   | 7    | -              | -              | GNDIO7   | 7    | -              | -              |

| J2     | PL12A    | 7    | Т              | LUM0_PLLT_IN_A | PL16A    | 7    | Т              | LUM0_PLLT_IN_A | PL16A    | 7    | Т              | LUM0_PLLT_IN_A |

| H1     | PL12B    | 7    | С              | LUM0_PLLC_IN_A | PL16B    | 7    | С              | LUM0_PLLC_IN_A | PL16B    | 7    | С              | LUM0_PLLC_IN_A |

| J1     | PL13A    | 7    | T <sup>3</sup> | -              | PL17A    | 7    | T <sup>3</sup> | -              | PL17A    | 7    | T <sup>3</sup> | -              |

| K2     | PL13B    | 7    | C³             | -              | PL17B    | 7    | C <sup>3</sup> | -              | PL17B    | 7    | C <sup>3</sup> | -              |

| K3     | PL14A    | 7    | -              | VREF2_7        | PL18A    | 7    | -              | VREF2_7        | PL18A    | 7    | -              | VREF2_7        |

| J3     | PL15B    | 7    | -              | -              | PL19B    | 7    | -              | -              | PL19B    | 7    | -              | -              |

| K1     | PL16A    | 7    | T <sup>3</sup> | DQS            | PL20A    | 7    | T <sup>3</sup> | DQS            | PL20A    | 7    | T <sup>3</sup> | DQS            |

| -      | GNDIO7   | 7    | -              | -              | GNDIO7   | 7    | -              | -              | GNDIO7   | 7    | -              | -              |

| L2     | PL16B    | 7    | C <sup>3</sup> | -              | PL20B    | 7    | C <sup>3</sup> | -              | PL20B    | 7    | C <sup>3</sup> | -              |

| L3     | PL17A    | 7    | Т              | -              | PL21A    | 7    | Т              | -              | PL21A    | 7    | Т              | -              |

| L4     | PL17B    | 7    | С              | -              | PL21B    | 7    | С              | -              | PL21B    | 7    | С              | -              |

| L1     | PL18A    | 7    | Т³             | -              | PL22A    | 7    | T <sup>3</sup> | -              | PL22A    | 7    | T <sup>3</sup> | -              |

| M1     | PL18B    | 7    | C <sup>3</sup> | -              | PL22B    | 7    | C <sup>3</sup> | -              | PL22B    | 7    | C <sup>3</sup> | -              |

| M2     | VCCP0    | -    | -              | -              | VCCP0    | -    | -              | -              | VCCP0    | -    | -              | -              |

| N1     | GNDP0    | -    | -              | -              | GNDP0    | -    | -              | -              | GNDP0    | -    | -              | -              |

| M3     | PL19A    | 6    | T <sup>3</sup> | -              | PL23A    | 6    | T <sup>3</sup> | -              | PL27A    | 6    | T <sup>3</sup> | -              |

| M4     | PL19B    | 6    | C <sup>3</sup> | -              | PL23B    | 6    | C <sup>3</sup> | -              | PL27B    | 6    | C <sup>3</sup> | -              |

| P1     | PL20A    | 6    | Т              | PCLKT6_0       | PL24A    | 6    | Т              | PCLKT6_0       | PL28A    | 6    | Т              | PCLKT6_0       |

| -      | GNDIO6   | 6    | -              | -              | GNDIO6   | 6    | -              | -              | GNDIO6   | 6    | -              | -              |

| N2     | PL20B    | 6    | С              | PCLKC6_0       | PL24B    | 6    | С              | PCLKC6_0       | PL28B    | 6    | С              | PCLKC6_0       |

| R1     | PL21A    | 6    | Т³             | -              | PL25A    | 6    | T <sup>3</sup> | -              | PL29A    | 6    | T <sup>3</sup> | -              |

| P2     | PL21B    | 6    | C <sup>3</sup> | -              | PL25B    | 6    | C <sup>3</sup> | -              | PL29B    | 6    | C <sup>3</sup> | -              |

| N3     | PL22A    | 6    | -              | -              | PL26A    | 6    | -              | -              | PL30A    | 6    | -              | -              |

| N4     | PL23B    | 6    | -              | VREF1_6        | PL27B    | 6    | -              | VREF1_6        | PL31B    | 6    | -              | VREF1_6        |

| T1     | PL24A    | 6    | T <sup>3</sup> | DQS            | PL28A    | 6    | T <sup>3</sup> | DQS            | PL32A    | 6    | T <sup>3</sup> | DQS            |

| R2     | PL24B    | 6    | C <sup>3</sup> |                | PL28B    | 6    | C <sup>3</sup> |                | PL32B    | 6    | C <sup>3</sup> |                |

| -      | GNDIO6   | 6    | -              | -              | GNDIO6   | 6    | -              | -              | GNDIO6   | 6    | -              | -              |

## LFXP15 & LFXP20 Logic Signal Connections: 484 fpBGA (Cont.)

|                |                  |      | LFXP15       |                  | LFXP20           |      |              |                  |  |  |  |

|----------------|------------------|------|--------------|------------------|------------------|------|--------------|------------------|--|--|--|

| Ball<br>Number | Ball<br>Function | Bank | Differential | Dual<br>Function | Ball<br>Function | Bank | Differential | Dual<br>Function |  |  |  |

| B3             | PT8B             | 0    | С            | -                | PT12B            | 0    | С            | -                |  |  |  |

| A3             | PT8A             | 0    | Т            | -                | PT12A            | 0    | Т            | -                |  |  |  |

| -              | GNDIO0           | 0    | -            | -                | GNDIO0           | 0    | -            | -                |  |  |  |

| D7             | PT7B             | 0    | С            | -                | PT11B            | 0    | С            | -                |  |  |  |

| C7             | PT7A             | 0    | Т            | DQS              | PT11A            | 0    | Т            | DQS              |  |  |  |

| B2             | PT6B             | 0    | -            | -                | PT10B            | 0    | -            | -                |  |  |  |

| C2             | PT5A             | 0    | -            | -                | PT9A             | 0    | -            | -                |  |  |  |

| C3             | PT4B             | 0    | С            | -                | PT8B             | 0    | С            | -                |  |  |  |

| D3             | PT4A             | 0    | Т            | -                | PT8A             | 0    | Т            | -                |  |  |  |

| F7             | PT3B             | 0    | С            | -                | PT7B             | 0    | С            | -                |  |  |  |

| E7             | PT3A             | 0    | Т            | -                | PT7A             | 0    | Т            | -                |  |  |  |

| -              | GNDIO0           | 0    | -            | -                | GNDIO0           | 0    | -            | -                |  |  |  |

| C6             | -                | -    | -            | -                | PT6B             | 0    | С            | -                |  |  |  |

| D6             | -                | -    | -            | -                | PT6A             | 0    | Т            | -                |  |  |  |

| C5             | -                | -    | -            | -                | PT5B             | 0    | С            | -                |  |  |  |

| C4             | -                | -    | -            | -                | PT5A             | 0    | Т            | -                |  |  |  |

| F6             | -                | -    | -            | -                | PT4B             | 0    | С            | -                |  |  |  |

| E6             | -                | -    | -            | -                | PT4A             | 0    | Т            | -                |  |  |  |

| -              | GNDIO0           | 0    | -            | -                | GNDIO0           | 0    | -            | -                |  |  |  |

| E4             | -                | -    | -            | -                | PT3B             | 0    | -            | -                |  |  |  |

| E5             | CFG0             | 0    | -            | -                | CFG0             | 0    | -            | -                |  |  |  |

| D4             | CFG1             | 0    | -            | -                | CFG1             | 0    | -            | -                |  |  |  |

| D5             | DONE             | 0    | -            | -                | DONE             | 0    | -            | -                |  |  |  |

| A1             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| A2             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| A21            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| A22            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| AA1            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| AA22           | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| AB1            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| AB2            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| AB21           | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| AB22           | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| B1             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| B22            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| H14            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| H9             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| J10            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| J11            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| J12            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| J13            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

| J14            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |  |

|                | induction (contri) |         |       |         |      |       |       |  |  |  |

|----------------|--------------------|---------|-------|---------|------|-------|-------|--|--|--|

| Part Number    | l/Os               | Voltage | Grade | Package | Pins | Temp. | LUTs  |  |  |  |

| LFXP15E-3F484I | 300                | 1.2V    | -3    | fpBGA   | 484  | IND   | 15.5K |  |  |  |

| LFXP15E-4F484I | 300                | 1.2V    | -4    | fpBGA   | 484  | IND   | 15.5K |  |  |  |

| LFXP15E-3F388I | 268                | 1.2V    | -3    | fpBGA   | 388  | IND   | 15.5K |  |  |  |

| LFXP15E-4F388I | 268                | 1.2V    | -4    | fpBGA   | 388  | IND   | 15.5K |  |  |  |

| LFXP15E-3F256I | 188                | 1.2V    | -3    | fpBGA   | 256  | IND   | 15.5K |  |  |  |

| LFXP15E-4F256I | 188                | 1.2V    | -4    | fpBGA   | 256  | IND   | 15.5K |  |  |  |

#### Industrial (Cont.)

| Part Number    | l/Os | Voltage | Grade | Package | Pins | Temp. | LUTs  |

|----------------|------|---------|-------|---------|------|-------|-------|

| LFXP20E-3F484I | 340  | 1.2V    | -3    | fpBGA   | 484  | IND   | 19.7K |

| LFXP20E-4F484I | 340  | 1.2V    | -4    | fpBGA   | 484  | IND   | 19.7K |

| LFXP20E-3F388I | 268  | 1.2V    | -3    | fpBGA   | 388  | IND   | 19.7K |

| LFXP20E-4F388I | 268  | 1.2V    | -4    | fpBGA   | 388  | IND   | 19.7K |

| LFXP20E-3F256I | 188  | 1.2V    | -3    | fpBGA   | 256  | IND   | 19.7K |

| LFXP20E-4F256I | 188  | 1.2V    | -4    | fpBGA   | 256  | IND   | 19.7K |

| Part Number     | I/Os | Voltage      | Grade | Package | Pins | Temp. | LUTs |  |  |

|-----------------|------|--------------|-------|---------|------|-------|------|--|--|

| LFXP10C-3FN388I | 244  | 1.8/2.5/3.3V | -3    | fpBGA   | 388  | IND   | 9.7K |  |  |

| LFXP10C-4FN388I | 244  | 1.8/2.5/3.3V | -4    | fpBGA   | 388  | IND   | 9.7K |  |  |

| LFXP10C-3FN256I | 188  | 1.8/2.5/3.3V | -3    | fpBGA   | 256  | IND   | 9.7K |  |  |

| LFXP10C-4FN256I | 188  | 1.8/2.5/3.3V | -4    | fpBGA   | 256  | IND   | 9.7K |  |  |

### Industrial (Cont.)

| Part Number     | l/Os | Voltage      | Grade | Package | Pins | Temp. | LUTs  |

|-----------------|------|--------------|-------|---------|------|-------|-------|

| LFXP15C-3FN484I | 300  | 1.8/2.5/3.3V | -3    | fpBGA   | 484  | IND   | 15.5K |

| LFXP15C-4FN484I | 300  | 1.8/2.5/3.3V | -4    | fpBGA   | 484  | IND   | 15.5K |

| LFXP15C-3FN388I | 268  | 1.8/2.5/3.3V | -3    | fpBGA   | 388  | IND   | 15.5K |

| LFXP15C-4FN388I | 268  | 1.8/2.5/3.3V | -4    | fpBGA   | 388  | IND   | 15.5K |

| LFXP15C-3FN256I | 188  | 1.8/2.5/3.3V | -3    | fpBGA   | 256  | IND   | 15.5K |

| LFXP15C-4FN256I | 188  | 1.8/2.5/3.3V | -4    | fpBGA   | 256  | IND   | 15.5K |

| Part Number     | I/Os | Voltage      | Grade | Package | Pins | Temp. | LUTs  |

|-----------------|------|--------------|-------|---------|------|-------|-------|

| LFXP20C-3FN484I | 340  | 1.8/2.5/3.3V | -3    | fpBGA   | 484  | IND   | 19.7K |

| LFXP20C-4FN484I | 340  | 1.8/2.5/3.3V | -4    | fpBGA   | 484  | IND   | 19.7K |

| LFXP20C-3FN388I | 268  | 1.8/2.5/3.3V | -3    | fpBGA   | 388  | IND   | 19.7K |

| LFXP20C-4FN388I | 268  | 1.8/2.5/3.3V | -4    | fpBGA   | 388  | IND   | 19.7K |

| LFXP20C-3FN256I | 188  | 1.8/2.5/3.3V | -3    | fpBGA   | 256  | IND   | 19.7K |

| LFXP20C-4FN256I | 188  | 1.8/2.5/3.3V | -4    | fpBGA   | 256  | IND   | 19.7K |

| Part Number    | I/Os | Voltage | Grade | Package | Pins | Temp. | LUTs |

|----------------|------|---------|-------|---------|------|-------|------|

| LFXP3E-3QN208I | 136  | 1.2V    | -3    | PQFP    | 208  | IND   | 3.1K |

| LFXP3E-4QN208I | 136  | 1.2V    | -4    | PQFP    | 208  | IND   | 3.1K |

| LFXP3E-3TN144I | 100  | 1.2V    | -3    | TQFP    | 144  | IND   | 3.1K |

| LFXP3E-4TN144I | 100  | 1.2V    | -4    | TQFP    | 144  | IND   | 3.1K |

| LFXP3E-3TN100I | 62   | 1.2V    | -3    | TQFP    | 100  | IND   | 3.1K |

| LFXP3E-4TN100I | 62   | 1.2V    | -4    | TQFP    | 100  | IND   | 3.1K |

| Part Number    | I/Os | Voltage | Grade | Package | Pins | Temp. | LUTs |

|----------------|------|---------|-------|---------|------|-------|------|

| LFXP6E-3FN256I | 188  | 1.2V    | -3    | fpBGA   | 256  | IND   | 5.8K |

| LFXP6E-4FN256I | 188  | 1.2V    | -4    | fpBGA   | 256  | IND   | 5.8K |

| LFXP6E-3QN208I | 142  | 1.2V    | -3    | PQFP    | 208  | IND   | 5.8K |

| LFXP6E-4QN208I | 142  | 1.2V    | -4    | PQFP    | 208  | IND   | 5.8K |