Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                  |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | 15000                                                                     |

| Total RAM Bits                 | 331776                                                                    |

| Number of I/O                  | 188                                                                       |

| Number of Gates                | -                                                                         |

| Voltage - Supply               | 1.14V ~ 1.26V                                                             |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                           |

| Package / Case                 | 256-BGA                                                                   |

| Supplier Device Package        | 256-FPBGA (17x17)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfxp15e-4f256c |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

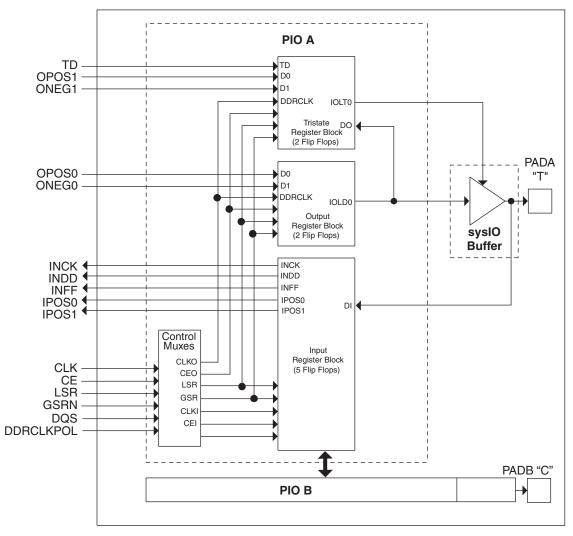

#### Figure 2-17. PIC Diagram

In the LatticeXP family, seven PIOs or four (3.5) PICs are grouped together to provide two LVDS differential pairs, one PIC pair and one single I/O, as shown in Figure 2-18.

Two adjacent PIOs can be joined to provide a differential I/O pair (labeled as "T" and "C"). The PAD Labels "T" and "C" distinguish the two PIOs. Only the PIO pairs on the left and right edges of the device can be configured as LVDS transmit/receive pairs.

One of every 14 PIOs (a group of 8 PICs) contains a delay element to facilitate the generation of DQS signals as shown in Figure 2-19. The DQS signal feeds the DQS bus which spans the set of 13 PIOs (8 PICs). The DQS signal from the bus is used to strobe the DDR data from the memory into input register blocks. This interface is designed for memories that support one DQS strobe per eight bits of data.

The exact DQS pins are shown in a dual function in the Logic Signal Connections table in this data sheet. Additional detail is provided in the Signal Descriptions table in this data sheet.

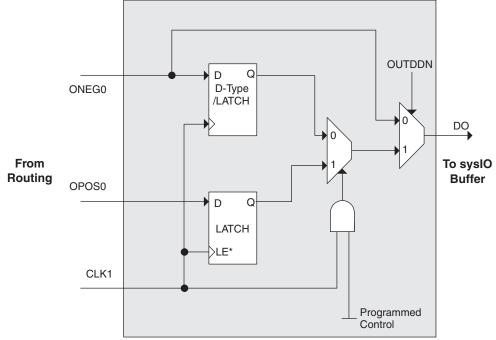

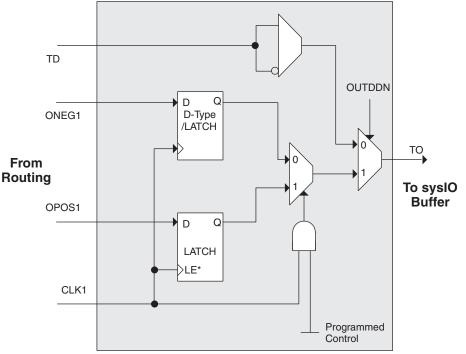

Figure 2-23. Output Register Block

\*Latch is transparent when input is low.

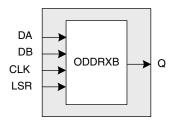

### Figure 2-24. ODDRXB Primitive

### Tristate Register Block

The tristate register block provides the ability to register tri-state control signals from the core of the device before they are passed to the sysIO buffers. The block contains a register for SDR operation and an additional latch for DDR operation. Figure 2-25 shows the diagram of the Tristate Register Block.

In SDR mode, ONEG1 feeds one of the flip-flops that then feeds the output. The flip-flop can be configured a Dtype or latch. In DDR mode, ONEG1 is fed into one register on the positive edge of the clock and OPOS1 is latched. A multiplexer running off the same clock selects the correct register for feeding to the output (D0).

Figure 2-25. Tristate Register Block

\*Latch is transparent when input is low.

### Control Logic Block

The control logic block allows the selection and modification of control signals for use in the PIO block. A clock is selected from one of the clock signals provided from the general purpose routing and a DQS signal provided from the programmable DQS pin. The clock can optionally be inverted.

The clock enable and local reset signals are selected from the routing and optionally inverted. The global tristate signal is passed through this block.

## DDR Memory Support

Implementing high performance DDR memory interfaces requires dedicated DDR register structures in the input (for read operations) and in the output (for write operations). As indicated in the PIO Logic section, the LatticeXP devices provide this capability. In addition to these registers, the LatticeXP devices contain two elements to simplify the design of input structures for read operations: the DQS delay block and polarity control logic.

### DLL Calibrated DQS Delay Block

Source Synchronous interfaces generally require the input clock to be adjusted in order to correctly capture data at the input register. For most interfaces a PLL is used for this adjustment, however in DDR memories the clock (referred to as DQS) is not free running so this approach cannot be used. The DQS Delay block provides the required clock alignment for DDR memory interfaces.

The DQS signal (selected PIOs only) feeds from the PAD through a DQS delay element to a dedicated DQS routing resource. The DQS signal also feeds the polarity control logic which controls the polarity of the clock to the sync registers in the input register blocks. Figures 2-26 and 2-27 show how the polarity control logic are routed to the PIOs.

The temperature, voltage and process variations of the DQS delay block are compensated by a set of calibration (6-bit bus) signals from two DLLs on opposite sides of the device. Each DLL compensates DQS Delays in its half of the device as shown in Figure 2-27. The DLL loop is compensated for temperature, voltage and process variations by the system clock and feedback loop.

### Polarity Control Logic

In a typical DDR Memory interface design, the phase relation between the incoming delayed DQS strobe and the internal system Clock (during the READ cycle) is unknown.

The LatticeXP family contains dedicated circuits to transfer data between these domains. To prevent setup and hold violations at the domain transfer between DQS (delayed) and the system Clock a clock polarity selector is used. This changes the edge on which the data is registered in the synchronizing registers in the input register block. This requires evaluation at the start of the each READ cycle for the correct clock polarity.

Prior to the READ operation in DDR memories DQS is in tristate (pulled by termination). The DDR memory device drives DQS low at the start of the preamble state. A dedicated circuit detects this transition. This signal is used to control the polarity of the clock to the synchronizing registers.

## sysIO Buffer

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in eight groups referred to as Banks. The sysIO buffers allow users to implement the wide variety of standards that are found in today's systems including LVCMOS, SSTL, HSTL, LVDS and LVPECL.

### sysIO Buffer Banks

LatticeXP devices have eight sysIO buffer banks; each is capable of supporting multiple I/O standards. Each sysIO bank has its own I/O supply voltage ( $V_{CCIO}$ ), and two voltage references  $V_{REF1}$  and  $V_{REF2}$  resources allowing each bank to be completely independent from each other. Figure 2-28 shows the eight banks and their associated supplies.

In the LatticeXP devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS, PCI and PCI-X) are powered using  $V_{CCIO}$ . LVTTL, LVCMOS33, LVCMOS25 and LVCMOS12 can also be set as a fixed threshold input independent of  $V_{CCIO}$ . In addition to the bank  $V_{CCIO}$  supplies, the LatticeXP devices have a  $V_{CC}$  core logic power supply, and a  $V_{CCAUX}$  supply that power all differential and referenced buffers.

Each bank can support up to two separate VREF voltages, VREF1 and VREF2 that set the threshold for the referenced input buffers. In the LatticeXP devices, a dedicated pin in a bank can be configured to be a reference voltage supply pin. Each I/O is individually configurable based on the bank's supply and reference voltages.

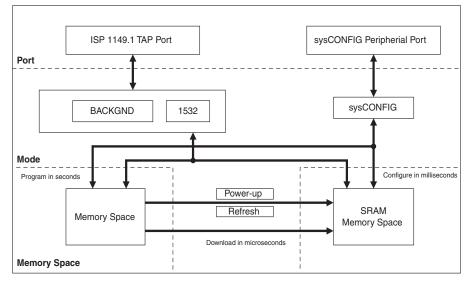

Figure 2-29 provides a pictorial representation of the different programming ports and modes available in the LatticeXP devices.

On power-up, the FPGA SRAM is ready to be configured with the sysCONFIG port active. The IEEE 1149.1 serial mode can be activated any time after power-up by sending the appropriate command through the TAP port.

#### Leave Alone I/O

When using 1532 mode for non-volatile memory programming, users may specify I/Os as high, low, tristated or held at current value. This provides excellent flexibility for implementing systems where reprogramming occurs on-the-fly.

#### TransFR (Transparent Field Reconfiguration)

TransFR (TFR) is a unique Lattice technology that allows users to update their logic in the field without interrupting system operation using a single ispVM command. See Lattice technical note #TN1087, *Minimizing System Interruption During Configuration Using TransFR Technology*, for details.

#### Security

The LatticeXP devices contain security bits that, when set, prevent the readback of the SRAM configuration and non-volatile memory spaces. Once set, the only way to clear security bits is to erase the memory space.

For more information on device configuration, please see details of additional technical documentation at the end of this data sheet.

#### Figure 2-29. ispXP Block Diagram

### Internal Logic Analyzer Capability (ispTRACY)

All LatticeXP devices support an internal logic analyzer diagnostic feature. The diagnostic features provide capabilities similar to an external logic analyzer, such as programmable event and trigger condition and deep trace memory. This feature is enabled by Lattice's ispTRACY. The ispTRACY utility is added into the user design at compile time.

For more information on ispTRACY, please see information regarding additional technical documentation at the end of this data sheet.

### Oscillator

Every LatticeXP device has an internal CMOS oscillator which is used to derive a master serial clock for configuration. The oscillator and the master serial clock run continuously in the configuration mode. The default value of the

# Programming and Erase Flash Supply Current<sup>1, 2, 3, 4, 5</sup>

| Symbol             | Parameter                                           | Device    | Тур.6 | Units |

|--------------------|-----------------------------------------------------|-----------|-------|-------|

|                    |                                                     | LFXP3E    | 30    | mA    |

|                    |                                                     | LFXP6E    | 40    | mA    |

|                    |                                                     | LFXP10E   | 50    | mA    |

|                    |                                                     | LFXP15E   | 60    | mA    |

|                    | Core Dower Supply                                   | LFXP20E   | 70    | mA    |

| Icc                | Core Power Supply                                   | LFXP3C    | 50    | mA    |

|                    |                                                     | LFXP6C    | 60    | mA    |

|                    |                                                     | LFXP10C   | 90    | mA    |

|                    |                                                     | LFXP15C   | 100   | mA    |

|                    |                                                     | LFXP20C   | 110   | mA    |

|                    |                                                     | LFXP3E/C  | 50    | mA    |

|                    |                                                     | LFXP6E/C  | 60    | mA    |

| I <sub>CCAUX</sub> | Auxiliary Power Supply<br>V <sub>CCAUX</sub> = 3.3V | LFXP10E/C | 90    | mA    |

|                    |                                                     | LFXP15E/C | 110   | mA    |

|                    |                                                     | LFXP20E/C | 130   | mA    |

| I <sub>CCJ</sub>   | V <sub>CCJ</sub> Power Supply <sup>7</sup>          | All       | 2     | mA    |

1. For further information on supply current, please see details of additional technical documentation at the end of this data sheet.

2. Assumes all outputs are tristated, all inputs are configured as LVCMOS and held at the  $V_{\mbox{CCIO}}$  or GND.

3. Blank user pattern; typical Flash pattern.

4. Bypass or decoupling capacitor across the supply.

5. JTAG programming is at 1MHz.

6.  $T_A=25^{\circ}C$ , power supplies at nominal voltage.

7. When programming via JTAG.

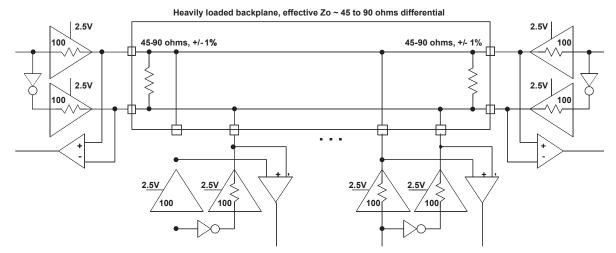

### Figure 3-2. BLVDS Multi-point Output Example

#### Table 3-2. BLVDS DC Conditions<sup>1</sup>

|                     |                             | Тур     | ical    |       |

|---------------------|-----------------------------|---------|---------|-------|

| Symbol              | Description                 | Zo = 45 | Zo = 90 | Units |

| Z <sub>OUT</sub>    | Output impedance            | 100     | 100     | ohms  |

| R <sub>TLEFT</sub>  | Left end termination        | 45      | 90      | ohms  |

| R <sub>TRIGHT</sub> | Right end termination       | 45      | 90      | ohms  |

| V <sub>OH</sub>     | Output high voltage         | 1.375   | 1.48    | V     |

| V <sub>OL</sub>     | Output low voltage          | 1.125   | 1.02    | V     |

| V <sub>OD</sub>     | Output differential voltage | 0.25    | 0.46    | V     |

| V <sub>CM</sub>     | Output common mode voltage  | 1.25    | 1.25    | V     |

| I <sub>DC</sub>     | DC output current           | 11.2    | 10.2    | mA    |

#### **Over Recommended Operating Conditions**

1. For input buffer, see LVDS table.

## LatticeXP Family Timing Adders<sup>1</sup>

| <b>Over Recommended</b> | Operating | Conditions |

|-------------------------|-----------|------------|

|-------------------------|-----------|------------|

| Buffer Type      | Description                    | -5   | -4   | -3   | Units |

|------------------|--------------------------------|------|------|------|-------|

| Input Adjusters  |                                |      |      |      |       |

| LVDS25E          | LVDS 2.5 Emulated              | 0.5  | 0.5  | 0.5  | ns    |

| LVDS25           | LVDS                           | 0.4  | 0.4  | 0.4  | ns    |

| BLVDS25          | BLVDS                          | 0.5  | 0.5  | 0.5  | ns    |

| LVPECL33         | LVPECL                         | 0.6  | 0.6  | 0.6  | ns    |

| HSTL18_I         | HSTL_18 class I                | 0.4  | 0.4  | 0.4  | ns    |

| HSTL18_II        | HSTL_18 class II               | 0.4  | 0.4  | 0.4  | ns    |

| HSTL18_III       | HSTL_18 class III              | 0.4  | 0.4  | 0.4  | ns    |

| HSTL18D_I        | Differential HSTL 18 class I   | 0.4  | 0.4  | 0.4  | ns    |

| HSTL18D_II       | Differential HSTL 18 class II  | 0.4  | 0.4  | 0.4  | ns    |

| HSTL18D_III      | Differential HSTL 18 class III | 0.4  | 0.4  | 0.4  | ns    |

| HSTL15_I         | HSTL_15 class I                | 0.5  | 0.5  | 0.5  | ns    |

| HSTL15_III       | HSTL_15 class III              | 0.5  | 0.5  | 0.5  | ns    |

| HSTL15D_I        | Differential HSTL 15 class I   | 0.5  | 0.5  | 0.5  | ns    |

| HSTL15D_III      | Differential HSTL 15 class III | 0.5  | 0.5  | 0.5  | ns    |

| SSTL33_I         | SSTL_3 class I                 | 0.6  | 0.6  | 0.6  | ns    |

| SSTL33_II        | SSTL_3 class II                | 0.6  | 0.6  | 0.6  | ns    |

| SSTL33D_I        | Differential SSTL_3 class I    | 0.6  | 0.6  | 0.6  | ns    |

| SSTL33D_II       | Differential SSTL_3 class II   | 0.6  | 0.6  | 0.6  | ns    |

| SSTL25_I         | SSTL_2 class I                 | 0.5  | 0.5  | 0.5  | ns    |

| SSTL25_II        | SSTL_2 class II                | 0.5  | 0.5  | 0.5  | ns    |

| SSTL25D_I        | Differential SSTL_2 class I    | 0.5  | 0.5  | 0.5  | ns    |

| SSTL25D_II       | Differential SSTL_2 class II   | 0.5  | 0.5  | 0.5  | ns    |

| SSTL18_I         | SSTL_18 class I                | 0.5  | 0.5  | 0.5  | ns    |

| SSTL18D_I        | Differential SSTL_18 class I   | 0.5  | 0.5  | 0.5  | ns    |

| LVTTL33          | LVTTL                          | 0.2  | 0.2  | 0.2  | ns    |

| LVCMOS33         | LVCMOS 3.3                     | 0.2  | 0.2  | 0.2  | ns    |

| LVCMOS25         | LVCMOS 2.5                     | 0.0  | 0.0  | 0.0  | ns    |

| LVCMOS18         | LVCMOS 1.8                     | 0.1  | 0.1  | 0.1  | ns    |

| LVCMOS15         | LVCMOS 1.5                     | 0.1  | 0.1  | 0.1  | ns    |

| LVCMOS12         | LVCMOS 1.2                     | 0.1  | 0.1  | 0.1  | ns    |

| PCI33            | PCI                            | 0.2  | 0.2  | 0.2  | ns    |

| Output Adjusters | 5                              |      |      | 1    | •     |

| LVDS25E          | LVDS 2.5 Emulated              | 0.3  | 0.3  | 0.3  | ns    |

| LVDS25           | LVDS 2.5                       | 0.3  | 0.3  | 0.3  | ns    |

| BLVDS25          | BLVDS 2.5                      | 0.3  | 0.3  | 0.3  | ns    |

| LVPECL33         | LVPECL 3.3                     | 0.1  | 0.1  | 0.1  | ns    |

| HSTL18_I         | HSTL_18 class I                | 0.1  | 0.1  | 0.1  | ns    |

| HSTL18_II        | HSTL_18 class II               | 0.1  | 0.1  | 0.1  | ns    |

| HSTL18_III       | HSTL_18 class III              | 0.2  | 0.2  | 0.2  | ns    |

| HSTL18D_I        | Differential HSTL 18 class I   | 0.1  | 0.1  | 0.1  | ns    |

| HSTL18D_II       | Differential HSTL 18 class II  | -0.1 | -0.1 | -0.1 | ns    |

| HSTL18D_III      | Differential HSTL 18 class III | 0.2  | 0.2  | 0.2  | ns    |

# LatticeXP Family Data Sheet Pinout Information

November 2007

Data Sheet DS1001

## **Signal Descriptions**

| Signal Name                                 | I/O    | Descriptions                                                                                                                                                                                                                                                          |

|---------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Purpose                             |        |                                                                                                                                                                                                                                                                       |

|                                             |        | [Edge] indicates the edge of the device on which the pad is located. Valid edge designations are L (Left), B (Bottom), R (Right), T (Top).                                                                                                                            |

|                                             |        | [Row/Column Number] indicates the PFU row or the column of the device on which the PIC exists. When Edge is T (Top) or (Bottom), only need to specify Row Number. When Edge is L (Left) or R (Right), only need to specify Column Number.                             |

| P[Edge] [Row/Column Number*]_[A/B]          | I/O    | [A/B] indicates the PIO within the PIC to which the pad is connected.                                                                                                                                                                                                 |

|                                             |        | Some of these user programmable pins are shared with special function pins. These pin when not used as special purpose pins can be programmed as $I/Os$ for user logic.                                                                                               |

|                                             |        | During configuration, the user-programmable I/Os are tri-stated with an inter-<br>nal pull-up resistor enabled. If any pin is not used (or not bonded to a pack-<br>age pin), it is also tri-stated with an internal pull-up resistor enabled after<br>configuration. |

| GSRN                                        | I      | Global RESET signal. (Active low). Any I/O pin can be configured to be GSRN.                                                                                                                                                                                          |

| NC                                          |        | No connect.                                                                                                                                                                                                                                                           |

| GND                                         | _      | GND - Ground. Dedicated Pins.                                                                                                                                                                                                                                         |

| V <sub>CC</sub>                             |        | VCC - The power supply pins for core logic. Dedicated Pins.                                                                                                                                                                                                           |

| V <sub>CCAUX</sub>                          | —      | $V_{CCAUX}$ - The Auxiliary power supply pin. It powers all the differential and referenced input buffers. Dedicated Pins.                                                                                                                                            |

| V <sub>CCP0</sub>                           |        | Voltage supply pins for ULM0PLL (and LLM1PLL <sup>1</sup> ).                                                                                                                                                                                                          |

| V <sub>CCP1</sub>                           |        | Voltage supply pins for URM0PLL (and LRM1PLL <sup>1</sup> ).                                                                                                                                                                                                          |

| GNDP0                                       | _      | Ground pins for ULM0PLL (and LLM1PLL <sup>1</sup> ).                                                                                                                                                                                                                  |

| GNDP1                                       |        | Ground pins for URM0PLL (and LRM1PLL <sup>1</sup> ).                                                                                                                                                                                                                  |

| V <sub>CCIOx</sub>                          | _      | V <sub>CCIO</sub> - The power supply pins for I/O bank x. Dedicated Pins.                                                                                                                                                                                             |

| V <sub>REF1(x)</sub> , V <sub>REF2(x)</sub> | —      | Reference supply pins for I/O bank x. Pre-determined pins in each bank are assigned as $V_{\text{REF}}$ inputs. When not used, they may be used as I/O pins.                                                                                                          |

| PLL and Clock Functions (Used as user       | progra | ammable I/O pins when not in use for PLL or clock pins)                                                                                                                                                                                                               |

| [LOC][num]_PLL[T, C]_IN_A                   | _      | Reference clock (PLL) input Pads: ULM, LLM, URM, LRM, num = row from center, $T =$ true and $C =$ complement, index A, B, Cat each side.                                                                                                                              |

| [LOC][num]_PLL[T, C]_FB_A                   | _      | Optional feedback (PLL) input Pads: ULM, LLM, URM, LRM, num = row from center, $T =$ true and $C =$ complement, index A, B, Cat each side.                                                                                                                            |

| PCLK[T, C]_[n:0]_[3:0]                      | _      | Primary Clock Pads, T = true and C = complement, n per side, indexed by bank and 0,1, 2, 3 within bank.                                                                                                                                                               |

| [LOC]DQS[num]                               | _      | DQS input Pads: T (Top), R (Right), B (Bottom), L (Left), DQS, num = Ball function number. Any pad can be configured to be DQS output.                                                                                                                                |

<sup>© 2007</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## LFXP3 & LFXP6 Logic Signal Connections: 208 PQFP (Cont.)

| Pin    |                                       |      | LFXP3          |               | LFXP6                                 |      |                |               |  |  |

|--------|---------------------------------------|------|----------------|---------------|---------------------------------------|------|----------------|---------------|--|--|

| Number | Pin Function                          | Bank | Differential   | Dual Function | Pin Function                          | Bank | Differential   | Dual Function |  |  |

| 47     | GNDIO6                                | 6    | -              | -             | GNDIO6                                | 6    | -              | -             |  |  |

| 48     | PL18B                                 | 6    | C <sup>3</sup> | -             | PL26B                                 | 6    | C <sup>3</sup> | -             |  |  |

| 49     | GND                                   | -    | -              | -             | GND                                   | -    | -              | -             |  |  |

| 50     | VCCAUX                                | -    | -              | -             | VCCAUX                                | -    | -              | -             |  |  |

| 51     | SLEEPN <sup>1</sup> /TOE <sup>2</sup> | -    | -              | -             | SLEEPN <sup>1</sup> /TOE <sup>2</sup> | -    | -              | -             |  |  |

| 52     | INITN                                 | 5    | -              | -             | INITN                                 | 5    | -              | -             |  |  |

| 53     | VCC                                   | -    | -              | -             | VCC                                   | -    | -              | -             |  |  |

| 54     | PB2B                                  | 5    | -              | VREF1_5       | PB5B                                  | 5    | -              | VREF1_5       |  |  |

| 55     | PB3A                                  | 5    | Т              | -             | PB6A                                  | 5    | Т              | DQS           |  |  |

| 56     | PB3B                                  | 5    | С              | -             | PB6B                                  | 5    | С              | -             |  |  |

| 57     | PB4A                                  | 5    | Т              | -             | PB7A                                  | 5    | Т              | -             |  |  |

| 58     | PB4B                                  | 5    | С              | -             | PB7B                                  | 5    | С              | -             |  |  |

| 59     | GNDIO5                                | 5    | -              | -             | GNDIO5                                | 5    | -              | -             |  |  |

| 60     | PB5A                                  | 5    | Т              | -             | PB8A                                  | 5    | Т              | -             |  |  |

| 61     | PB5B                                  | 5    | С              | VREF2_5       | PB8B                                  | 5    | С              | VREF2_5       |  |  |

| 62     | PB6A                                  | 5    | Т              | -             | PB9A                                  | 5    | Т              | -             |  |  |

| 63     | PB6B                                  | 5    | С              | -             | PB9B                                  | 5    | С              | -             |  |  |

| 64     | VCCIO5                                | 5    | -              | -             | VCCIO5                                | 5    | -              | -             |  |  |

| 65     | PB7A                                  | 5    | Т              | -             | PB10A                                 | 5    | Т              | -             |  |  |

| 66     | PB7B                                  | 5    | С              | -             | PB10B                                 | 5    | С              | -             |  |  |

| 67     | PB8A                                  | 5    | Т              | -             | PB11A                                 | 5    | Т              | -             |  |  |

| 68     | PB8B                                  | 5    | С              | -             | PB11B                                 | 5    | С              | -             |  |  |

| 69     | GNDIO5                                | 5    | -              | -             | GNDIO5                                | 5    | -              | -             |  |  |

| 70     | PB9A                                  | 5    | -              | -             | PB12A                                 | 5    | -              | -             |  |  |

| 71     | PB10B                                 | 5    | -              | -             | PB13B                                 | 5    | -              | -             |  |  |

| 72     | PB11A                                 | 5    | Т              | DQS           | PB14A                                 | 5    | Т              | DQS           |  |  |

| 73     | PB11B                                 | 5    | С              | -             | PB14B                                 | 5    | С              | -             |  |  |

| 74     | VCCIO5                                | 5    | -              | -             | VCCIO5                                | 5    | -              | -             |  |  |

| 75     | PB12A                                 | 5    | Т              | -             | PB15A                                 | 5    | Т              | -             |  |  |

| 76     | PB12B                                 | 5    | С              | -             | PB15B                                 | 5    | С              | -             |  |  |

| 77     | PB13A                                 | 5    | Т              | -             | PB16A                                 | 5    | Т              | -             |  |  |

| 78     | PB13B                                 | 5    | С              | -             | PB16B                                 | 5    | С              | -             |  |  |

| 79     | GND                                   | -    | -              | -             | GND                                   | -    | -              | -             |  |  |

| 80     | VCC                                   | -    | -              | -             | VCC                                   | -    | -              | -             |  |  |

| 81     | PB14A                                 | 4    | Т              | -             | PB17A                                 | 4    | Т              | -             |  |  |

| 82     | GNDIO4                                | 4    | -              | -             | GNDIO4                                | 4    | -              | -             |  |  |

| 83     | PB14B                                 | 4    | С              | -             | PB17B                                 | 4    | С              | -             |  |  |

| 84     | PB15A                                 | 4    | Т              | PCLKT4_0      | PB18A                                 | 4    | Т              | PCLKT4_0      |  |  |

| 85     | PB15B                                 | 4    | С              | PCLKC4_0      | PB18B                                 | 4    | С              | PCLKC4_0      |  |  |

| 86     | PB16A                                 | 4    | Т              | -             | PB19A                                 | 4    | Т              | -             |  |  |

| 87     | VCCIO4                                | 4    | -              | -             | VCCIO4                                | 4    | -              | -             |  |  |

| 88     | PB16B                                 | 4    | С              | -             | PB19B                                 | 4    | С              | -             |  |  |

| 89     | PB17A                                 | 4    | -              | -             | PB20A                                 | 4    | -              | -             |  |  |

| 90     | PB18B                                 | 4    | -              | -             | PB21B                                 | 4    | -              | -             |  |  |

| 91     | PB19A                                 | 4    | Т              | DQS           | PB22A                                 | 4    | Т              | DQS           |  |  |

| 92     | GNDIO4                                | 4    | -              | -             | GNDIO4                                | 4    | -              | -             |  |  |

## LFXP3 & LFXP6 Logic Signal Connections: 208 PQFP (Cont.)

| Pin    |              |      | LFXP3          |                    | LFXP6        |      |                |                      |  |  |

|--------|--------------|------|----------------|--------------------|--------------|------|----------------|----------------------|--|--|

| Number | Pin Function | Bank | Differential   | Dual Function      | Pin Function | Bank | Differential   | <b>Dual Function</b> |  |  |

| 93     | PB19B        | 4    | С              | VREF1_4            | PB22B        | 4    | С              | VREF1_4              |  |  |

| 94     | PB20A        | 4    | Т              | -                  | PB23A        | 4    | Т              | -                    |  |  |

| 95     | PB20B        | 4    | С              | -                  | - PB23B 4 C  |      | -              |                      |  |  |

| 96     | PB21A        | 4    | Т              | -                  | PB24A        | 4    | Т              | -                    |  |  |

| 97     | VCCIO4       | 4    | -              | -                  | VCCIO4       | 4    | -              | -                    |  |  |

| 98     | PB21B        | 4    | С              | -                  | PB24B        | 4    | С              | -                    |  |  |

| 99     | PB22A        | 4    | Т              | -                  | PB25A        | 4    | Т              | -                    |  |  |

| 100    | PB22B        | 4    | С              | -                  | PB25B        | 4    | С              | -                    |  |  |

| 101    | PB23A        | 4    | Т              | -                  | PB26A        | 4    | Т              | -                    |  |  |

| 102    | PB23B        | 4    | С              | -                  | PB26B        | 4    | С              | -                    |  |  |

| 103    | PB24A        | 4    | Т              | VREF2_4            | PB27A        | 4    | -              | VREF2_4              |  |  |

| 104    | PB24B        | 4    | С              | -                  | PB30A        | 4    | Т              | DQS                  |  |  |

| 105    | PB25A        | 4    | -              | -                  | PB30B        | 4    | С              | -                    |  |  |

| 106    | GND          | -    | -              | -                  | GND          | -    | -              | -                    |  |  |

| 107    | VCC          | -    | -              | -                  | VCC          | -    | -              | -                    |  |  |

| 108    | PR18B        | 3    | C <sup>3</sup> | -                  | PR26B        | 3    | C <sup>3</sup> | -                    |  |  |

| 109    | GNDIO3       | 3    | -              | -                  | GNDIO3       | 3    | -              | -                    |  |  |

| 110    | PR18A        | 3    | T <sup>3</sup> | -                  | PR26A        | 3    | T <sup>3</sup> | -                    |  |  |

| 111    | PR17B        | 3    | С              | -                  | PR25B        | 3    | С              | -                    |  |  |

| 112    | PR17A        | 3    | Т              | -                  | PR25A        | 3    | Т              | -                    |  |  |

| 113    | PR16B        | 3    | C <sup>3</sup> | -                  | PR24B        | 3    | C <sup>3</sup> | -                    |  |  |

| 114    | PR16A        | 3    | T <sup>3</sup> | DQS                | PR24A        | 3    | T <sup>3</sup> | DQS                  |  |  |

| 115    | VCCIO3       | 3    | -              | -                  | VCCIO3       | 3    | -              | -                    |  |  |

| 116    | PR15B        | 3    | -              | VREF1_3            | PR23B        | 3    | -              | VREF1_3              |  |  |

| 117    | PR14A        | 3    | -              | VREF2_3            | PR22A        | 3    | -              | VREF2_3              |  |  |

| 118    | GNDIO3       | 3    | -              | -                  | GNDIO3       | 3    | -              | -                    |  |  |

| 119    | PR13B        | 3    | С              | -                  | PR21B        | 3    | C <sup>3</sup> | -                    |  |  |

| 120    | PR13A        | 3    | Т              | -                  | PR21A        | 3    | T <sup>3</sup> | -                    |  |  |

| 121    | GND          | -    | -              | -                  | GND          | -    | -              | -                    |  |  |

| 122    | PR12B        | 3    | С              | -                  | PR20B        | 3    | С              | -                    |  |  |

| 123    | PR12A        | 3    | Т              | -                  | PR20A        | 3    | Т              | -                    |  |  |

| 124    | PR11B        | 3    | С              | -                  | PR19B        | 3    | C <sup>3</sup> | -                    |  |  |

| 125    | VCCIO3       | 3    | -              | -                  | VCCIO3       | 3    | -              | -                    |  |  |

| 126    | PR11A        | 3    | Т              | -                  | PR19A        | 3    | T <sup>3</sup> | -                    |  |  |

| 127    | GNDP1        | -    | -              | -                  | GNDP1        | -    | -              | -                    |  |  |

| 128    | VCCP1        | -    | -              | -                  | VCCP1        | -    | -              | -                    |  |  |

| 129    | NC           | -    | -              | -                  | PR13A        | 2    | -              | -                    |  |  |

| 130    | GND          | -    | -              | -                  | GND          | -    | -              | -                    |  |  |

| 131    | PR9B         | 2    | С              | PCLKC2_0           | PR12B        | 2    | С              | PCLKC2_0             |  |  |

| 132    | PR9A         | 2    | Т              | PCLKT2_0           | PR12A        | 2    | Т              | PCLKT2_0             |  |  |

| 133    | NC           | -    | -              | -                  | PR11B        | 2    | C <sup>3</sup> | -                    |  |  |

| 134    | NC           | -    | -              | -                  | PR11A        | 2    | T <sup>3</sup> | -                    |  |  |

| 135    | GNDIO2       | 2    | -              | -                  | GNDIO2       | 2    | -              | -                    |  |  |

| 136    | PR8B         | 2    | С              | RUM0_PLLC_IN_A     | PR8B         | 2    | С              | RUM0_PLLC_IN_/       |  |  |

| 137    | PR8A         | 2    | Т              | <br>RUM0_PLLT_IN_A | PR8A         | 2    | Т              | <br>RUM0_PLLT_IN_A   |  |  |

| 138    | PR7B         | 2    | C <sup>3</sup> |                    | PR7B         | 2    | C <sup>3</sup> |                      |  |  |

## LFXP6 & LFXP10 Logic Signal Connections: 256 fpBGA (Cont.)

|                |                  |      | LFXP6          |                  | LFXP10           |      |                |                  |  |  |

|----------------|------------------|------|----------------|------------------|------------------|------|----------------|------------------|--|--|

| Ball<br>Number | Ball<br>Function | Bank | Differential   | Dual<br>Function | Ball<br>Function | Bank | Differential   | Dual<br>Function |  |  |

| R8             | PB16A            | 5    | Т              | -                | PB20A            | 5    | Т              | -                |  |  |

| Т9             | PB16B            | 5    | С              | -                | PB20B            | 5    | С              | -                |  |  |

| R9             | PB17A            | 4    | Т              | -                | PB21A            | 4    | Т              | -                |  |  |

| -              | GNDIO4           | 4    | -              | -                | GNDIO4           | 4    | -              | -                |  |  |

| P9             | PB17B            | 4    | С              | -                | PB21B            | 4    | С              | -                |  |  |

| T10            | PB18A            | 4    | Т              | PCLKT4_0         | PB22A            | 4    | Т              | PCLKT4_0         |  |  |

| T11            | PB18B            | 4    | C              | PCLKC4_0         | PB22B            | 4    | С              | PCLKC4_0         |  |  |

| R10            | PB19A            | 4    | Т              | -                | PB23A            | 4    | Т              | -                |  |  |

| P10            | PB19B            | 4    | С              | -                | PB23B            | 4    | С              | -                |  |  |

| N9             | PB20A            | 4    | -              | -                | PB24A            | 4    | -              | -                |  |  |

| M9             | PB21B            | 4    | -              | -                | PB25B            | 4    | -              | -                |  |  |

| R12            | PB22A            | 4    | Т              | DQS              | PB26A            | 4    | Т              | DQS              |  |  |

| -              | GNDIO4           | 4    | -              | -                | GNDIO4           | 4    | -              | -                |  |  |

| T12            | PB22B            | 4    | С              | VREF1_4          | PB26B            | 4    | С              | VREF1_4          |  |  |

| P13            | PB23A            | 4    | Т              | -                | PB27A            | 4    | Т              | -                |  |  |

| R13            | PB23B            | 4    | С              | -                | PB27B            | 4    | С              | -                |  |  |

| M11            | PB24A            | 4    | Т              | -                | PB28A            | 4    | Т              | -                |  |  |

| N11            | PB24B            | 4    | С              | -                | PB28B            | 4    | С              | -                |  |  |

| N10            | PB25A            | 4    | Т              | -                | PB29A            | 4    | Т              | -                |  |  |

| M10            | PB25B            | 4    | С              | -                | PB29B            | 4    | С              | -                |  |  |

| T13            | PB26A            | 4    | Т              | -                | PB30A            | 4    | Т              | -                |  |  |

| -              | GNDIO4           | 4    | -              | -                | GNDIO4           | 4    | -              | -                |  |  |

| P14            | PB26B            | 4    | С              | -                | PB30B            | 4    | С              | -                |  |  |

| R11            | PB27A            | 4    | Т              | VREF2_4          | PB31A            | 4    | Т              | VREF2_4          |  |  |

| P12            | PB27B            | 4    | С              | -                | PB31B            | 4    | С              | -                |  |  |

| T14            | PB28A            | 4    | -              | -                | PB32A            | 4    | -              | -                |  |  |

| R14            | PB29B            | 4    | -              | -                | PB33B            | 4    | -              | -                |  |  |

| P11            | PB30A            | 4    | Т              | DQS              | PB34A            | 4    | Т              | DQS              |  |  |

| N12            | PB30B            | 4    | С              | -                | PB34B            | 4    | С              | -                |  |  |

| T15            | PB31A            | 4    | Т              | -                | PB35A            | 4    | Т              | -                |  |  |

| -              | GNDIO4           | 4    | -              | -                | GNDIO4           | 4    | -              | -                |  |  |

| R15            | PB31B            | 4    | С              | -                | PB35B            | 4    | С              | -                |  |  |

| -              | GNDIO3           | 3    | -              | -                | GNDIO3           | 3    | -              | -                |  |  |

| P15            | PR26B            | 3    | C <sup>3</sup> | -                | PR34B            | 3    | С              | RLM0_PLLC_FB_A   |  |  |

| N15            | PR26A            | 3    | T <sup>3</sup> | -                | PR34A            | 3    | Т              | RLM0_PLLT_FB_A   |  |  |

| P16            | PR24B            | 3    | C <sup>3</sup> | -                | PR33B            | 3    | C <sup>3</sup> | -                |  |  |

| R16            | PR24A            | 3    | T <sup>3</sup> | DQS              | PR33A            | 3    | T <sup>3</sup> | DQS              |  |  |

| M15            | PR15B            | 3    | -              | -                | PR32B            | 3    | -              | -                |  |  |

| N14            | PR23B            | 3    | -              | VREF1_3          | PR31A            | 3    | -              | VREF1_3          |  |  |

| -              | GNDIO3           | 3    | -              | -                | GNDIO3           | 3    | -              | -                |  |  |

| M14            | PR25B            | 3    | С              | -                | PR29B            | 3    | С              | -                |  |  |

| L13            | PR25A            | 3    | Т              | -                | PR29A            | 3    | Т              | -                |  |  |

## LFXP10, LFXP15 & LFXP20 Logic Signal Connections: 388 fpBGA (Cont.)

|           |          | L    | FXP10 | )             |          | LFXP15   |       |               | LFXP20   |      |       |               |

|-----------|----------|------|-------|---------------|----------|----------|-------|---------------|----------|------|-------|---------------|

| Ball      | Ball     |      |       |               | Ball     |          |       |               | Ball     |      |       |               |

| Number    | Function | Bank |       | Dual Function | Function | Bank     | Diff. | Dual Function | Function | Bank | Diff. | Dual Function |

| A7        | PT13A    | 0    | Т     | DI            | PT18A    | 0        | Т     | DI            | PT22A    | 0    | Т     | DI            |

| B7        | PT12B    | 0    | С     | -             | PT17B    | 0        | С     | -             | PT21B    | 0    | С     | -             |

| C6        | PT12A    | 0    | Т     | CSN           | PT17A    | 0        | Т     | CSN           | PT21A    | 0    | Т     | CSN           |

| C10       | PT11B    | 0    | С     | -             | PT16B    | 0        | С     | -             | PT20B    | 0    | С     | -             |

| C9        | PT11A    | 0    | Т     | -             | PT16A    | 0        | Т     | -             | PT20A    | 0    | Т     | -             |

| A6        | PT10B    | 0    | С     | VREF2_0       | PT15B    | 0        | С     | VREF2_0       | PT19B    | 0    | С     | VREF2_0       |

| B6        | PT10A    | 0    | Т     | DQS           | PT15A    | 0        | Т     | DQS           | PT19A    | 0    | Т     | DQS           |

| A5        | PT9B     | 0    | -     | -             | PT14B    | 0        | -     | -             | PT18B    | 0    | -     | -             |

| B5        | PT8A     | 0    | -     | -             | PT13A    | 0        | -     | -             | PT17A    | 0    | -     | -             |

| -         | GNDIO0   | 0    | -     | -             | GNDIO0   | 0        | -     | -             | GNDIO0   | 0    | -     | -             |

| C5        | PT7B     | 0    | С     | -             | PT12B    | 0        | С     | -             | PT16B    | 0    | С     | -             |

| A4        | PT7A     | 0    | Т     | -             | PT12A    | 0        | Т     | -             | PT16A    | 0    | Т     | -             |

| D9        | PT6B     | 0    | С     | -             | PT11B    | 0        | С     | -             | PT15B    | 0    | С     | -             |

| D8        | PT6A     | 0    | Т     | -             | PT11A    | 0        | Т     | -             | PT15A    | 0    | Т     | -             |

| B4        | PT5B     | 0    | С     | -             | PT10B    | 0        | С     | -             | PT14B    | 0    | С     | -             |

| A2        | PT5A     | 0    | Т     | -             | PT10A    | 0        | Т     | -             | PT14A    | 0    | Т     | -             |

| A3        | PT4B     | 0    | С     | -             | PT9B     | 0        | С     | -             | PT13B    | 0    | С     | -             |

| B3        | PT4A     | 0    | Т     | -             | PT9A     | 0        | Т     | -             | PT13A    | 0    | Т     | -             |

| C4        | PT3B     | 0    | С     | -             | PT8B     | 0        | С     | -             | PT12B    | 0    | С     | -             |

| C3        | PT3A     | 0    | Т     | -             | PT8A     | 0        | Т     | -             | PT12A    | 0    | Т     | -             |

| -         | GNDIO0   | 0    | -     | -             | GNDIO0   | 0        | -     | -             | GNDIO0   | 0    | -     | -             |

| C2        | -        | -    | -     | -             | PT7B     | 0        | С     | -             | PT11B    | 0    | С     | -             |

| D3        | PT2A     | 0    | -     | -             | PT7A     | 0        | Т     | DQS           | PT11A    | 0    | Т     | DQS           |

| D7        | -        | -    | -     | -             | PT6B     | 0        | -     | -             | PT10B    | 0    | -     | -             |

| D6        | -        | -    | -     | -             | PT5A     | 0        | -     | -             | PT9A     | 0    | -     | -             |

| E4        | -        | -    | -     | -             | PT4B     | 0        | С     | -             | PT8B     | 0    | С     | -             |

| D4        | -        | -    | -     | -             | PT4A     | 0        | Т     | -             | PT8A     | 0    | Т     | -             |

| D5        | -        | -    | -     | -             | PT3B     | 0        | -     | -             | PT7B     | 0    | -     | -             |

| -         | GNDIO0   | 0    | -     | -             | GNDIO0   | 0        | -     | -             | GNDIO0   | 0    | -     | -             |

| -         | GNDIO0   | 0    | -     | -             | GNDIO0   | 0        | -     | -             | GNDIO0   | 0    | -     | -             |

| C1        | CFG0     | 0    | -     | -             | CFG0     | 0        | -     | -             | CFG0     | 0    | -     | -             |

| B2        | CFG1     | 0    | -     | -             | CFG1     | 0        | -     | -             | CFG1     | 0    | -     | -             |

| B1        | DONE     | 0    | -     | -             | DONE     | 0        | -     | -             | DONE     | 0    | -     | -             |

| A1        | GND      | -    | -     | -             | GND      | -        | -     | -             | GND      | -    | -     | -             |

| A22       | GND      | -    | -     | -             | GND      | -        | -     | -             | GND      | -    | -     | -             |

| AB1       | GND      | -    | -     | -             | GND      | -        | -     | -             | GND      | -    | -     | -             |

| AB22      | GND      | -    | -     | -             | GND      | -        | -     | -             | GND      | -    | -     | -             |

| H10       | GND      | -    | -     | -             | GND      | -        | -     | -             | GND      | -    | -     | -             |

| H11       | GND      | -    | -     | -             | GND      | -        | -     | -             | GND      | -    | -     | -             |

| H12       | GND      | -    | -     | -             | GND      | -        | -     | -             | GND      | -    | -     | -             |

| H13       | GND      | -    | -     | -             | GND      | -        | -     | -             | GND      | -    | -     | -             |

| H14       | GND      | -    | -     | -             | GND      | -        | -     | -             | GND      | -    | -     | -             |

| J10       | GND      | -    | -     | -             | GND      | -        | -     | -             | GND      | -    | -     | -             |

| J11       | GND      | -    | -     | -             | GND      | -        | -     | -             | GND      | -    | -     | -             |

| J12       | GND      | -    | -     | -             | GND      | -        | -     | -             | GND      | -    | -     | -             |

| J12       | GND      | -    | -     | -             | GND      | -        | -     | -             | GND      | -    | -     | -             |

| J13       | GND      | -    | -     | -             | GND      | -        | -     | -             | GND      | -    | -     | -             |

| J14<br>J9 | GND      | -    | -     | -             | GND      | -        | -     | -             | GND      | -    | -     | -             |

| 59<br>K10 | GND      | -    | -     | -             | GND      | -        | -     |               | GND      | -    | -     | -             |

| N10       | GND      | -    |       | -             | GND      | <u> </u> | -     | -             | GND      | I -  | -     | -             |

## LFXP15 & LFXP20 Logic Signal Connections: 484 fpBGA (Cont.)

|                |                                           |      | LFXP15         |                  | LFXP20                                    |      |                |                  |  |  |

|----------------|-------------------------------------------|------|----------------|------------------|-------------------------------------------|------|----------------|------------------|--|--|

| Ball<br>Number | Ball<br>Function                          | Bank | Differential   | Dual<br>Function | Ball<br>Function                          | Bank | Differential   | Dual<br>Function |  |  |

| T6             | PL41A                                     | 6    | Т              | -                | PL45A                                     | 6    | Т              | -                |  |  |

| T5             | PL41B                                     | 6    | С              | -                | PL45B                                     | 6    | С              | -                |  |  |

| -              | GNDIO6                                    | 6    | -              | -                | GNDIO6                                    | 6    | -              | -                |  |  |

| U3             | PL42A                                     | 6    | T <sup>3</sup> | -                | PL46A                                     | 6    | T <sup>3</sup> | -                |  |  |

| U4             | PL42B                                     | 6    | C <sup>3</sup> | -                | PL46B                                     | 6    | C <sup>3</sup> | -                |  |  |

| V4             | PL43A                                     | 6    | -              | -                | PL47A                                     | 6    | -              | -                |  |  |

| W4             | SLEEPN <sup>1</sup> /<br>TOE <sup>2</sup> | -    | -              | -                | SLEEPN <sup>1</sup> /<br>TOE <sup>2</sup> | -    | -              | -                |  |  |

| W5             | INITN                                     | 5    | -              | -                | INITN                                     | 5    | -              | -                |  |  |

| Y3             | -                                         | -    | -              | -                | PB3B                                      | 5    | -              | -                |  |  |

| -              | GNDIO5                                    | 5    | -              | -                | GNDIO5                                    | 5    | -              | -                |  |  |

| U5             | -                                         | -    | -              | -                | PB4A                                      | 5    | Т              | -                |  |  |

| V5             | -                                         | -    | -              | -                | PB4B                                      | 5    | С              | -                |  |  |

| Y4             | -                                         | -    | -              | -                | PB5A                                      | 5    | Т              | -                |  |  |

| Y5             | -                                         | -    | -              | -                | PB5B                                      | 5    | С              | -                |  |  |

| V6             | -                                         | -    | -              | -                | PB6A                                      | 5    | Т              | -                |  |  |

| -              | GNDIO5                                    | 5    | -              | -                | GNDIO5                                    | 5    | -              | -                |  |  |

| U6             | -                                         | -    | -              | -                | PB6B                                      | 5    | С              | -                |  |  |

| W6             | PB3A                                      | 5    | Т              | -                | PB7A                                      | 5    | Т              | -                |  |  |

| Y6             | PB3B                                      | 5    | С              | -                | PB7B                                      | 5    | С              | -                |  |  |

| AA2            | PB4A                                      | 5    | Т              | -                | PB8A                                      | 5    | Т              | -                |  |  |

| AA3            | PB4B                                      | 5    | С              | -                | PB8B                                      | 5    | С              | -                |  |  |

| V7             | PB5A                                      | 5    | -              | -                | PB9A                                      | 5    | -              | -                |  |  |

| U7             | PB6B                                      | 5    | -              | -                | PB10B                                     | 5    | -              | -                |  |  |

| Y7             | PB7A                                      | 5    | Т              | DQS              | PB11A                                     | 5    | Т              | DQS              |  |  |

| W7             | PB7B                                      | 5    | С              | -                | PB11B                                     | 5    | С              | -                |  |  |

| AA4            | PB8A                                      | 5    | Т              | -                | PB12A                                     | 5    | Т              | -                |  |  |

| -              | GNDIO5                                    | 5    | -              | -                | GNDIO5                                    | 5    | -              | -                |  |  |

| AA5            | PB8B                                      | 5    | С              | -                | PB12B                                     | 5    | С              | -                |  |  |

| AB3            | PB9A                                      | 5    | Т              | -                | PB13A                                     | 5    | Т              | -                |  |  |

| AB4            | PB9B                                      | 5    | С              | -                | PB13B                                     | 5    | С              | -                |  |  |

| AA6            | PB10A                                     | 5    | Т              | -                | PB14A                                     | 5    | Т              | -                |  |  |

| AA7            | PB10B                                     | 5    | С              | -                | PB14B                                     | 5    | С              | -                |  |  |

| U8             | PB11A                                     | 5    | Т              | -                | PB15A                                     | 5    | Т              | -                |  |  |

| V8             | PB11B                                     | 5    | С              | -                | PB15B                                     | 5    | С              | -                |  |  |

| Y8             | PB12A                                     | 5    | Т              | VREF1_5          | PB16A                                     | 5    | Т              | VREF1_5          |  |  |

| -              | GNDIO5                                    | 5    | -              | -                | GNDIO5                                    | 5    | -              | -                |  |  |

| W8             | PB12B                                     | 5    | С              | -                | PB16B                                     | 5    | С              | -                |  |  |

| V9             | PB13A                                     | 5    | -              | -                | PB17A                                     | 5    | -              | -                |  |  |

| U9             | PB14B                                     | 5    | -              | -                | PB18B                                     | 5    | -              | -                |  |  |

| Y9             | PB15A                                     | 5    | Т              | DQS              | PB19A                                     | 5    | Т              | DQS              |  |  |

| W9             | PB15B                                     | 5    | С              | -                | PB19B                                     | 5    | С              | -                |  |  |

## LFXP15 & LFXP20 Logic Signal Connections: 484 fpBGA (Cont.)

|                |                  |      | LFXP15         |                            | LFXP20           |                |                |                  |  |  |

|----------------|------------------|------|----------------|----------------------------|------------------|----------------|----------------|------------------|--|--|

| Ball<br>Number | Ball<br>Function | Bank | Differential   | Dual<br>Function           | Ball<br>Function | Bank           | Differential   | Dual<br>Function |  |  |

| J21            | PR20B            | 2    | C <sup>3</sup> | -                          | PR20B            | 2              | C <sup>3</sup> | -                |  |  |

| J22            | PR20A            | 2    | T <sup>3</sup> | DQS PR20A 2 T <sup>3</sup> |                  | T <sup>3</sup> | DQS            |                  |  |  |

| K18            | PR19B            | 2    | -              | -                          | PR19B            | 2              | -              | -                |  |  |

| K19            | PR18A            | 2    | -              | VREF1_2                    | PR18A            | 2              | -              | VREF1_2          |  |  |

| -              | GNDIO2           | 2    | -              | -                          | GNDIO2           | 2              | -              | -                |  |  |

| K21            | PR17B            | 2    | C <sup>3</sup> | -                          | PR17B            | 2              | C <sup>3</sup> | -                |  |  |

| K20            | PR17A            | 2    | Т³             | -                          | PR17A            | 2              | T <sup>3</sup> | -                |  |  |

| H21            | PR16B            | 2    | С              | RUM0_PLLC_IN_A             | PR16B            | 2              | С              | RUM0_PLLC_IN_A   |  |  |

| H22            | PR16A            | 2    | Т              | RUM0_PLLT_IN_A             | PR16A            | 2              | Т              | RUM0_PLLT_IN_A   |  |  |

| J20            | PR15B            | 2    | C <sup>3</sup> | -                          | PR15B            | 2              | C <sup>3</sup> | -                |  |  |

| J19            | PR15A            | 2    | T <sup>3</sup> | -                          | PR15A            | 2              | T <sup>3</sup> | -                |  |  |

| -              | GNDIO2           | 2    | -              | -                          | GNDIO2           | 2              | -              | -                |  |  |

| J17            | PR13B            | 2    | C <sup>3</sup> | -                          | PR13B            | 2              | C <sup>3</sup> | -                |  |  |

| J18            | PR13A            | 2    | T <sup>3</sup> | -                          | PR13A            | 2              | T <sup>3</sup> | -                |  |  |

| G21            | PR12B            | 2    | С              | -                          | PR12B            | 2              | С              | -                |  |  |

| G22            | PR12A            | 2    | Т              | -                          | PR12A            | 2              | Т              | -                |  |  |

| F21            | PR11B            | 2    | C <sup>3</sup> | -                          | PR11B            | 2              | C <sup>3</sup> | -                |  |  |

| F22            | PR11A            | 2    | T <sup>3</sup> | DQS                        | PR11A            | 2              | T <sup>3</sup> | DQS              |  |  |

| -              | GNDIO2           | 2    | -              | -                          | GNDIO2           | 2              | -              | -                |  |  |

| H20            | PR10B            | 2    | -              | -                          | PR10B            | 2              | -              | -                |  |  |

| H19            | PR9A             | 2    | -              | VREF2_2                    | PR9A             | 2              | -              | VREF2_2          |  |  |

| H17            | PR8B             | 2    | C <sup>3</sup> | -                          | PR8B             | 2              | C <sup>3</sup> | -                |  |  |

| H18            | PR8A             | 2    | T <sup>3</sup> | -                          | PR8A             | 2              | T <sup>3</sup> | -                |  |  |

| E21            | PR7B             | 2    | С              | RUM0_PLLC_FB_A             | PR7B             | 2              | С              | RUM0_PLLC_FB_A   |  |  |

| E22            | PR7A             | 2    | Т              | RUM0_PLLT_FB_A             | PR7A             | 2              | Т              | RUM0_PLLT_FB_A   |  |  |

| D21            | PR6B             | 2    | C <sup>3</sup> | -                          | PR6B             | 2              | C <sup>3</sup> | -                |  |  |

| D22            | PR6A             | 2    | T <sup>3</sup> | -                          | PR6A             | 2              | T <sup>3</sup> | -                |  |  |

| G20            | PR5B             | 2    | C <sup>3</sup> | -                          | PR5B             | 2              | C <sup>3</sup> | -                |  |  |

| G19            | PR5A             | 2    | T <sup>3</sup> | -                          | PR5A             | 2              | T <sup>3</sup> | -                |  |  |

| G17            | PR4B             | 2    | С              | -                          | PR4B             | 2              | С              | -                |  |  |

| G18            | PR4A             | 2    | Т              | -                          | PR4A             | 2              | Т              | -                |  |  |

| -              | GNDIO2           | 2    | -              | -                          | GNDIO2           | 2              | -              | -                |  |  |

| F18            | PR3B             | 2    | C <sup>3</sup> | -                          | PR3B             | 2              | C <sup>3</sup> | -                |  |  |

| F19            | PR3A             | 2    | T <sup>3</sup> | -                          | PR3A             | 2              | T <sup>3</sup> | -                |  |  |

| C22            | PR2B             | 2    | -              | -                          | PR2B             | 2              | -              | -                |  |  |

| F20            | TDO              | -    | -              | -                          | TDO              | -              | -              | -                |  |  |

| E20            | VCCJ             | -    | -              | -                          | VCCJ             | -              | -              | -                |  |  |

| D19            | TDI              | -    | -              | -                          | TDI              | -              | -              | -                |  |  |

| E19            | TMS              | -    | -              | -                          | TMS              | -              | -              | -                |  |  |

| D20            | TCK              | -    | -              | -                          | TCK              | -              | -              | -                |  |  |

| C20            | -                | -    | -              | -                          | PT56A            | 1              | -              | -                |  |  |

| -              | GNDIO1           | 1    | -              | -                          | GNDIO1           | 1              | -              | -                |  |  |

## LFXP15 & LFXP20 Logic Signal Connections: 484 fpBGA (Cont.)

|                |                  |      | LFXP15       |                  |                  | LFXP20 |              |                  |  |  |  |

|----------------|------------------|------|--------------|------------------|------------------|--------|--------------|------------------|--|--|--|

| Ball<br>Number | Ball<br>Function | Bank | Differential | Dual<br>Function | Ball<br>Function | Bank   | Differential | Dual<br>Function |  |  |  |

| G9             | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| H15            | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| H8             | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| J16            | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| J7             | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| K16            | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| K17            | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| K6             | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| K7             | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| N16            | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| N17            | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| N6             | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| N7             | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| P16            | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| P7             | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| R15            | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| R8             | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| T10            | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| T13            | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| T14            | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| Т9             | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |