Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                                  |

|--------------------------------|---------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | 20000                                                                     |

| Total RAM Bits                 | 405504                                                                    |

| Number of I/O                  | 340                                                                       |

| Number of Gates                | -                                                                         |

| Voltage - Supply               | 1.14V ~ 1.26V                                                             |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                           |

| Package / Case                 | 484-BBGA                                                                  |

| Supplier Device Package        | 484-FPBGA (23x23)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfxp20e-5f484c |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

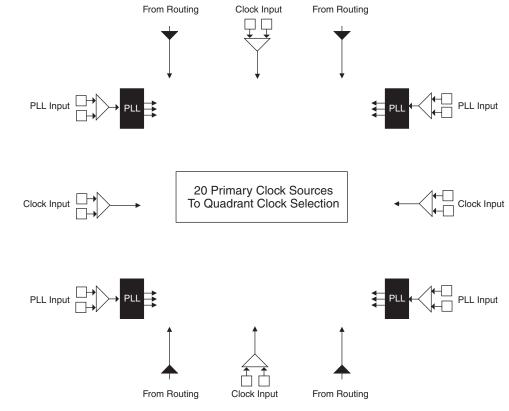

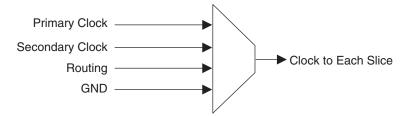

### Figure 2-5. Primary Clock Sources

Note: Smaller devices have two PLLs.

## **Secondary Clock Sources**

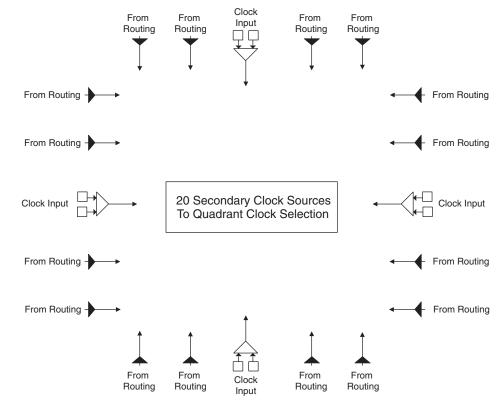

LatticeXP devices have four secondary clock resources per quadrant. The secondary clock branches are tapped at every PFU. These secondary clock networks can also be used for controls and high fanout data. These secondary clocks are derived from four clock input pads and 16 routing signals as shown in Figure 2-6.

## Lattice Semiconductor

#### Figure 2-6. Secondary Clock Sources

## **Clock Routing**

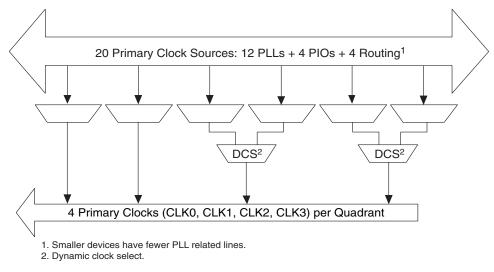

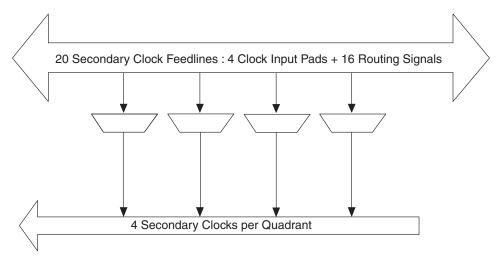

The clock routing structure in LatticeXP devices consists of four Primary Clock lines and a Secondary Clock network per quadrant. The primary clocks are generated from MUXs located in each quadrant. Figure 2-7 shows this clock routing. The four secondary clocks are generated from MUXs located in each quadrant as shown in Figure 2-8. Each slice derives its clock from the primary clock lines, secondary clock lines and routing as shown in Figure 2-9.

## Lattice Semiconductor

#### Figure 2-8. Per Quadrant Secondary Clock Selection

#### Figure 2-9. Slice Clock Selection

## sysCLOCK Phase Locked Loops (PLLs)

The PLL clock input, from pin or routing, feeds into an input clock divider. There are three sources of feedback signals to the feedback divider: from CLKOP (PLL internal), from clock net (CLKOP or CLKOS) or from a user clock (PIN or logic). There is a PLL\_LOCK signal to indicate that VCO has locked on to the input clock signal. Figure 2-10 shows the sysCLOCK PLL diagram.

The setup and hold times of the device can be improved by programming a delay in the feedback or input path of the PLL which will advance or delay the output clock with reference to the input clock. This delay can be either programmed during configuration or can be adjusted dynamically. In dynamic mode, the PLL may lose lock after adjustment and not relock until the t<sub>LOCK</sub> parameter has been satisfied. Additionally, the phase and duty cycle block allows the user to adjust the phase and duty cycle of the CLKOS output.

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. Each PLL has four dividers associated with it: input clock divider, feedback divider, post scalar divider and secondary clock divider. The input clock divider is used to divide the input clock signal, while the feedback divider is used to multiply the input clock signal. The post scalar divider allows the VCO to operate at higher frequencies than the clock output, thereby increasing the frequency range. The secondary divider is used to derive lower frequency outputs.

For more information on the PLL, please see details of additional technical documentation at the end of this data sheet.

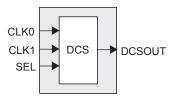

## **Dynamic Clock Select (DCS)**

The DCS is a global clock buffer with smart multiplexer functions. It takes two independent input clock sources and outputs a clock signal without any glitches or runt pulses. This is achieved irrespective of where the select signal is toggled. There are eight DCS blocks per device, located in pairs at the center of each side. Figure 2-12 illustrates the DCS Block Macro.

### Figure 2-12. DCS Block Primitive

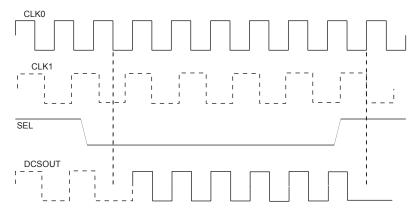

Figure 2-13 shows timing waveforms of the default DCS operating mode. The DCS block can be programmed to other modes. For more information on the DCS, please see details of additional technical documentation at the end of this data sheet.

### Figure 2-13. DCS Waveforms

## sysMEM Memory

The LatticeXP family of devices contain a number of sysMEM Embedded Block RAM (EBR). The EBR consists of a 9-Kbit RAM, with dedicated input and output registers.

## sysMEM Memory Block

The sysMEM block can implement single port, dual port or pseudo dual port memories. Each block can be used in a variety of depths and widths as shown in Table 2-6.

Table 2-6. sysMEM Block Configurations

| Memory Mode      | Configurations                                                           |

|------------------|--------------------------------------------------------------------------|

| Single Port      | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |

| True Dual Port   | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18             |

| Pseudo Dual Port | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |

## Bus Size Matching

All of the multi-port memory modes support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1 and so on. Although the word size and number of words for each port varies, this mapping scheme applies to each port.

## **RAM Initialization and ROM Operation**

If desired, the contents of the RAM can be pre-loaded during device configuration. By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

## **Memory Cascading**

Larger and deeper blocks of RAMs can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

## Single, Dual and Pseudo-Dual Port Modes

Figure 2-14 shows the four basic memory configurations and their input/output names. In all the sysMEM RAM modes the input data and address for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the output.

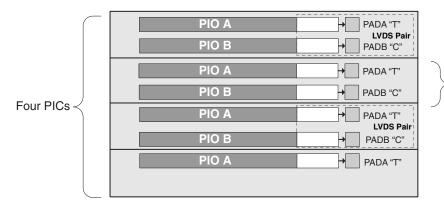

### Figure 2-18. Group of Seven PIOs

One PIO Pair

#### Figure 2-19. DQS Routing

|          | PIO A<br>PIO B |                                                                                                                                                                                                                        | PADA "T"<br>LVDS Pair<br>PADB "C"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | PIO A          | `                                                                                                                                                                                                                      | PADA "T"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>→</b> | PIO B          | <b>←</b>                                                                                                                                                                                                               | PADB "C"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          | PIO A          |                                                                                                                                                                                                                        | PADA "T"<br>LVDS Pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          | PIO B          | <u> </u>                                                                                                                                                                                                               | PADB "C"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          | PIO A          | F.                                                                                                                                                                                                                     | PADA "T"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>→</b> | PIO B          | <b>►</b>                                                                                                                                                                                                               | PADB "C"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| →        | PIO A          | sysIO<br>Buffer<br>Delay                                                                                                                                                                                               | signed DQS Pin<br>PADA "T"<br>LVDS Pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <b>→</b> | PIO B          | •                                                                                                                                                                                                                      | PADB "C"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>→</b> | PIO A          | +                                                                                                                                                                                                                      | PADA "T"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |                |                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| →        | PIO B          |                                                                                                                                                                                                                        | PADB "C"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |                | <ul> <li>→ PIO B</li> <li>→ PIO A</li> <li>→ PIO B</li> <li>→ PIO B</li> <li>→ PIO A</li> <li>→ PIO B</li> <li>→ PIO A</li> </ul> | $ \begin{array}{c} \rightarrow & \text{PIO B} \\ \hline & \text{PIO A} \\ \hline & \text{PIO B} \\ \hline & \text{PIO A} \\ \hline & \text{PIO B} \\ \hline & \text{PIO B} \\ \hline & \text{PIO A} \\ \hline & \text{PIO A} \\ \hline & \text{PIO A} \\ \hline & \text{PIO B} \\ \hline & \text{PIO B} \\ \hline & \text{PIO B} \\ \hline & \text{PIO A} \\ \hline \end{array}$ |

## ΡΙΟ

The PIO contains four blocks: an input register block, output register block, tristate register block and a control logic block. These blocks contain registers for both single data rate (SDR) and double data rate (DDR) operation along with the necessary clock and selection logic. Programmable delay lines used to shift incoming clock and data signals are also included in these blocks.

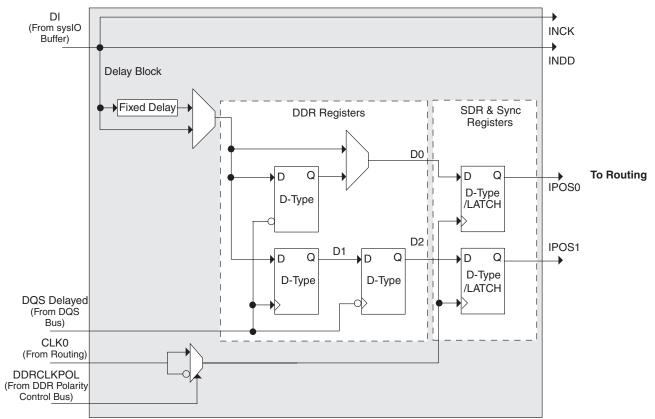

#### Input Register Block

The input register block contains delay elements and registers that can be used to condition signals before they are passed to the device core. Figure 2-20 shows the diagram of the input register block.

Input signals are fed from the sysIO buffer to the input register block (as signal DI). If desired the input signal can bypass the register and delay elements and be used directly as a combinatorial signal (INDD), a clock (INCK) and

## Lattice Semiconductor

in selected blocks the input to the DQS delay block. If one of the bypass options is not chosen, the signal first passes through an optional delay block. This delay, if selected, ensures no positive input-register hold-time requirement when using a global clock.

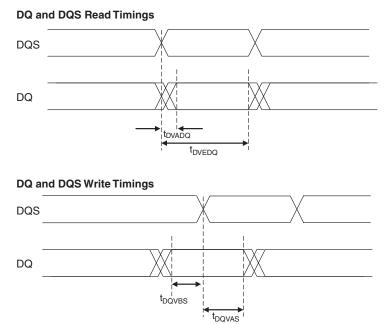

The input block allows two modes of operation. In the single data rate (SDR) the data is registered, by one of the registers in the single data rate sync register block, with the system clock. In the DDR Mode two registers are used to sample the data on the positive and negative edges of the DQS signal creating two data streams, D0 and D2. These two data streams are synchronized with the system clock before entering the core. Further discussion on this topic is in the DDR Memory section of this data sheet.

Figure 2-21 shows the input register waveforms for DDR operation and Figure 2-22 shows the design tool primitives. The SDR/SYNC registers have reset and clock enable available.

The signal DDRCLKPOL controls the polarity of the clock used in the synchronization registers. It ensures adequate timing when data is transferred from the DQS to the system clock domain. For further discussion of this topic, see the DDR memory section of this data sheet.

#### Figure 2-20. Input Register Diagram

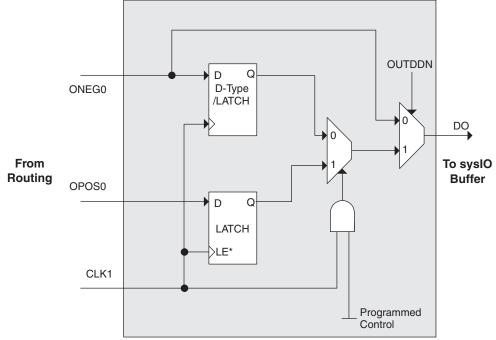

Figure 2-23. Output Register Block

\*Latch is transparent when input is low.

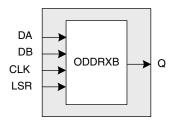

## Figure 2-24. ODDRXB Primitive

## Tristate Register Block

The tristate register block provides the ability to register tri-state control signals from the core of the device before they are passed to the sysIO buffers. The block contains a register for SDR operation and an additional latch for DDR operation. Figure 2-25 shows the diagram of the Tristate Register Block.

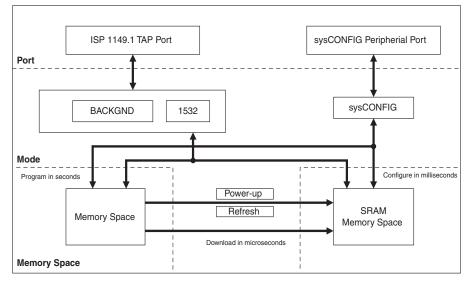

In SDR mode, ONEG1 feeds one of the flip-flops that then feeds the output. The flip-flop can be configured a Dtype or latch. In DDR mode, ONEG1 is fed into one register on the positive edge of the clock and OPOS1 is latched. A multiplexer running off the same clock selects the correct register for feeding to the output (D0). Figure 2-29 provides a pictorial representation of the different programming ports and modes available in the LatticeXP devices.

On power-up, the FPGA SRAM is ready to be configured with the sysCONFIG port active. The IEEE 1149.1 serial mode can be activated any time after power-up by sending the appropriate command through the TAP port.

#### Leave Alone I/O

When using 1532 mode for non-volatile memory programming, users may specify I/Os as high, low, tristated or held at current value. This provides excellent flexibility for implementing systems where reprogramming occurs on-the-fly.

#### TransFR (Transparent Field Reconfiguration)

TransFR (TFR) is a unique Lattice technology that allows users to update their logic in the field without interrupting system operation using a single ispVM command. See Lattice technical note #TN1087, *Minimizing System Interruption During Configuration Using TransFR Technology*, for details.

#### Security

The LatticeXP devices contain security bits that, when set, prevent the readback of the SRAM configuration and non-volatile memory spaces. Once set, the only way to clear security bits is to erase the memory space.

For more information on device configuration, please see details of additional technical documentation at the end of this data sheet.

### Figure 2-29. ispXP Block Diagram

## Internal Logic Analyzer Capability (ispTRACY)

All LatticeXP devices support an internal logic analyzer diagnostic feature. The diagnostic features provide capabilities similar to an external logic analyzer, such as programmable event and trigger condition and deep trace memory. This feature is enabled by Lattice's ispTRACY. The ispTRACY utility is added into the user design at compile time.

For more information on ispTRACY, please see information regarding additional technical documentation at the end of this data sheet.

### Oscillator

Every LatticeXP device has an internal CMOS oscillator which is used to derive a master serial clock for configuration. The oscillator and the master serial clock run continuously in the configuration mode. The default value of the

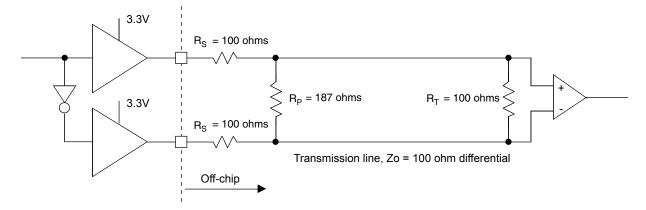

## LVPECL

The LatticeXP devices support differential LVPECL standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The LVPECL input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-3 is one possible solution for point-to-point signals.

### Figure 3-3. Differential LVPECL

| Symbol            | Description                 | Typical | Units |

|-------------------|-----------------------------|---------|-------|

| Z <sub>OUT</sub>  | Output impedance            | 100     | ohms  |

| R <sub>P</sub>    | Driver parallel resistor    | 187     | ohms  |

| R <sub>S</sub>    | Driver series resistor      | 100     | ohms  |

| R <sub>T</sub>    | Receiver termination        | 100     | ohms  |

| V <sub>OH</sub>   | Output high voltage         | 2.03    | V     |

| V <sub>OL</sub>   | Output low voltage          | 1.27    | V     |

| V <sub>OD</sub>   | Output differential voltage | 0.76    | V     |

| V <sub>CM</sub>   | Output common mode voltage  | 1.65    | V     |

| Z <sub>BACK</sub> | Back impedance              | 85.7    | ohms  |

| I <sub>DC</sub>   | DC output current           | 12.7    | mA    |

#### **Over Recommended Operating Conditions**

1. For input buffer, see LVDS table.

For further information on LVPECL, BLVDS and other differential interfaces please see details of additional technical documentation at the end of the data sheet.

## RSDS

The LatticeXP devices support differential RSDS standard. This standard is emulated using complementary LVC-MOS outputs in conjunction with a parallel resistor across the driver outputs. The RSDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-4 is one possible solution for RSDS standard implementation. Use LVDS25E mode with suggested resistors for RSDS operation. Resistor values in Figure 3-4 are industry standard values for 1% resistors.

## Figure 3-5. DDR Timings

# LatticeXP Family Timing Adders<sup>1</sup> (Continued)

| Buffer Type   | Description                         | -5   | -4   | -3   | Units |

|---------------|-------------------------------------|------|------|------|-------|

| HSTL15_I      | HSTL_15 class I                     | 0.2  | 0.2  | 0.2  | ns    |

| HSTL15_III    | HSTL_15 class III                   | 0.2  | 0.2  | 0.2  | ns    |

| HSTL15D_I     | L15D_I Differential HSTL 15 class I |      | 0.2  | 0.2  | ns    |

| HSTL15D_III   | Differential HSTL 15 class III      | 0.2  | 0.2  | 0.2  | ns    |

| SSTL33_I      | SSTL_3 class I                      | 0.1  | 0.1  | 0.1  | ns    |

| SSTL33_II     | SSTL_3 class II                     | 0.3  | 0.3  | 0.3  | ns    |

| SSTL33D_I     | Differential SSTL_3 class I         | 0.1  | 0.1  | 0.1  | ns    |

| SSTL33D_II    | Differential SSTL_3 class II        | 0.3  | 0.3  | 0.3  | ns    |

| SSTL25_I      | SSTL_2 class I                      | -0.1 | -0.1 | -0.1 | ns    |

| SSTL25_II     | SSTL_2 class II                     | 0.3  | 0.3  | 0.3  | ns    |

| SSTL25D_I     | Differential SSTL_2 class I         | -0.1 | -0.1 | -0.1 | ns    |

| SSTL25D_II    | Differential SSTL_2 class II        | 0.3  | 0.3  | 0.3  | ns    |

| SSTL18_I      | SSTL_1.8 class I                    | 0.1  | 0.1  | 0.1  | ns    |

| SSTL18D_I     | Differential SSTL_1.8 class I       | 0.1  | 0.1  | 0.1  | ns    |

| VTTL33_4mA    | LVTTL 4mA drive                     | 0.8  | 0.8  | 0.8  | ns    |

| VTTL33_8mA    | LVTTL 8mA drive                     | 0.5  | 0.5  | 0.5  | ns    |

| VTTL33_12mA   | LVTTL 12mA drive                    | 0.3  | 0.3  | 0.3  | ns    |

| VTTL33_16mA   | LVTTL 16mA drive                    | 0.4  | 0.4  | 0.4  | ns    |

| VTTL33_20mA   | LVTTL 20mA drive                    | 0.3  | 0.3  | 0.3  | ns    |

| VCMOS33_2mA   | LVCMOS 3.3 2mA drive                | 0.8  | 0.8  | 0.8  | ns    |

| VCMOS33_4mA   | LVCMOS 3.3 4mA drive                | 0.8  | 0.8  | 0.8  | ns    |

| VCMOS33_8mA   | LVCMOS 3.3 8mA drive                | 0.5  | 0.5  | 0.5  | ns    |

| VCMOS33_12mA  | LVCMOS 3.3 12mA drive               | 0.3  | 0.3  | 0.3  | ns    |

| LVCMOS33_16mA | LVCMOS 3.3 16mA drive               | 0.4  | 0.4  | 0.4  | ns    |

| LVCMOS33_20mA | LVCMOS 3.3 20mA drive               | 0.3  | 0.3  | 0.3  | ns    |

| LVCMOS25_2mA  | LVCMOS 2.5 2mA drive                | 0.7  | 0.7  | 0.7  | ns    |

| LVCMOS25_4mA  | LVCMOS 2.5 4mA drive                | 0.7  | 0.7  | 0.7  | ns    |

| VCMOS25_8mA   | LVCMOS 2.5 8mA drive                | 0.4  | 0.4  | 0.4  | ns    |

| VCMOS25_12mA  | LVCMOS 2.5 12mA drive               | 0.0  | 0.0  | 0.0  | ns    |

| VCMOS25_16mA  | LVCMOS 2.5 16mA drive               | 0.2  | 0.2  | 0.2  | ns    |

| VCMOS25_20mA  | LVCMOS 2.5 20mA drive               | 0.4  | 0.4  | 0.4  | ns    |

| VCMOS18_2mA   | LVCMOS 1.8 2mA drive                | 0.6  | 0.6  | 0.6  | ns    |

| VCMOS18_4mA   | LVCMOS 1.8 4mA drive                | 0.6  | 0.6  | 0.6  | ns    |

|               | LVCMOS 1.8 8mA drive                | 0.4  | 0.4  | 0.4  | ns    |

| VCMOS18_12mA  | LVCMOS 1.8 12mA drive               | 0.2  | 0.2  | 0.2  | ns    |

| VCMOS18_16mA  | LVCMOS 1.8 16mA drive               | 0.2  | 0.2  | 0.2  | ns    |

|               | LVCMOS 1.5 2mA drive                | 0.6  | 0.6  | 0.6  | ns    |

|               | LVCMOS 1.5 4mA drive                | 0.6  | 0.6  | 0.6  | ns    |

|               | LVCMOS 1.5 8mA drive                | 0.2  | 0.2  | 0.2  | ns    |

| VCMOS12_2mA   | LVCMOS 1.2 2mA drive                | 0.4  | 0.4  | 0.4  | ns    |

| LVCMOS12_6mA  | LVCMOS 1.2 6mA drive                | 0.4  | 0.4  | 0.4  | ns    |

| PCI33         | PCI33                               | 0.3  | 0.3  | 0.3  | ns    |

1. General timing numbers based on LVCMOS 2.5, 12mA.

Timing v.F0.11

# LFXP3 Logic Signal Connections: 100 TQFP

| Pin Number | Pin Function                          | Bank | Differential   | Dual Function  |

|------------|---------------------------------------|------|----------------|----------------|

| 1          | CFG1                                  | 0    | -              | -              |

| 2          | DONE                                  | 0    | -              | -              |

| 3          | PROGRAMN                              | 7    | -              | -              |

| 4          | CCLK                                  | 7    | -              | -              |

| 5          | PL3A                                  | 7    | Т              | LUM0_PLLT_FB_A |

| 6          | PL3B                                  | 7    | С              | LUM0_PLLC_FB_A |

| 7          | VCCI07                                | 7    | -              | -              |

| 8          | PL5A                                  | 7    | -              | VREF1_7        |

| 9          | PL6B                                  | 7    | -              | VREF2_7        |

| 10         | GNDIO7                                | 7    | -              | -              |

| 11         | PL7A                                  | 7    | T <sup>3</sup> | DQS            |

| 12         | PL7B                                  | 7    | C <sup>3</sup> | -              |

| 13         | PL8A                                  | 7    | Т              | LUM0_PLLT_IN_A |

| 14         | PL8B                                  | 7    | С              | LUM0_PLLC_IN_A |

| 15         | PL9A                                  | 7    | T <sup>3</sup> | -              |

| 16         | PL9B                                  | 7    | C <sup>3</sup> | -              |

| 17         | VCCP0                                 | -    | -              | -              |

| 18         | GNDP0                                 | -    | -              | -              |

| 19         | PL12A                                 | 6    | Т              | PCLKT6_0       |

| 20         | PL12B                                 | 6    | С              | PCLKC6_0       |

| 21         | GNDIO6                                | 6    | -              | -              |

| 22         | VCCIO6                                | 6    | -              | -              |

| 23         | PL18A                                 | 6    | T <sup>3</sup> | -              |

| 24         | PL18B                                 | 6    | C <sup>3</sup> | -              |

| 25         | VCCAUX                                | -    | -              | -              |

| 26         | SLEEPN <sup>1</sup> /TOE <sup>2</sup> | -    | -              | -              |

| 27         | INITN                                 | 5    | -              | -              |

| 28         | VCC                                   | -    | -              | -              |

| 29         | PB2B                                  | 5    | -              | VREF1_5        |

| 30         | PB5B                                  | 5    | -              | VREF2_5        |

| 31         | PB8A                                  | 5    | Т              | -              |

| 32         | PB8B                                  | 5    | С              | -              |

| 33         | GNDIO5                                | 5    | -              | -              |

| 34         | PB9A                                  | 5    | -              | -              |

| 35         | PB10B                                 | 5    | -              | -              |

| 36         | PB11A                                 | 5    | Т              | DQS            |

| 37         | PB11B                                 | 5    | С              | -              |

| 38         | VCCIO5                                | 5    | -              | -              |

| 39         | PB12A                                 | 5    | Т              | -              |

| 40         | PB12B                                 | 5    | C              | -              |

| 41         | PB13A                                 | 5    | T              | -              |

| 42         | PB13B                                 | 5    | C              | -              |

| 43         | GND                                   | -    | -              | -              |

# LFXP6 & LFXP10 Logic Signal Connections: 256 fpBGA (Cont.)

|                |                  |      | LFXP6          |                  | LFXP10           |      |                |                  |  |

|----------------|------------------|------|----------------|------------------|------------------|------|----------------|------------------|--|

| Ball<br>Number | Ball<br>Function | Bank | Differential   | Dual<br>Function | Ball<br>Function | Bank | Differential   | Dual<br>Function |  |

| L15            | PR21B            | 3    | C <sup>3</sup> | -                | PR28B            | 3    | C <sup>3</sup> | -                |  |

| L14            | PR21A            | 3    | Т³             | -                | PR28A            | 3    | T <sup>3</sup> | -                |  |

| -              | GNDIO3           | 3    | -              | -                | GNDIO3           | 3    | -              | -                |  |

| L12            | PR17B            | 3    | С              | -                | PR26A            | 3    | -              | -                |  |

| M16            | PR20B            | 3    | С              | -                | PR25B            | 3    | С              | RLM0_PLLC_IN_A   |  |

| N16            | PR20A            | 3    | Т              | -                | PR25A            | 3    | Т              | RLM0_PLLT_IN_A   |  |

| K14            | PR19B            | 3    | C <sup>3</sup> | -                | PR24B            | 3    | C <sup>3</sup> | -                |  |

| K15            | PR19A            | 3    | T <sup>3</sup> | -                | PR24A            | 3    | T <sup>3</sup> | DQS              |  |

| K12            | PR17A            | 3    | Т              | -                | PR23B            | 3    | -              | -                |  |

| K13            | PR22A            | 3    | -              | VREF2_3          | PR22A            | 3    | -              | VREF2_3          |  |

| -              | GNDIO3           | 3    | -              | -                | GNDIO3           | 3    | -              | -                |  |

| L16            | PR18B            | 3    | C <sup>3</sup> | -                | PR21B            | 3    | C <sup>3</sup> | -                |  |

| K16            | PR18A            | 3    | T <sup>3</sup> | -                | PR21A            | 3    | T <sup>3</sup> | -                |  |

| J15            | PR16B            | 3    | C <sup>3</sup> | -                | PR19B            | 3    | C <sup>3</sup> | -                |  |

| J14            | PR16A            | 3    | T <sup>3</sup> | -                | PR19A            | 3    | T <sup>3</sup> | -                |  |

| J13            | GNDP1            | -    | -              | -                | GNDP1            | -    | -              | -                |  |

| J12            | VCCP1            | -    | -              | -                | VCCP1            | -    | -              | -                |  |

| -              | GNDIO2           | 2    | -              | -                | GNDIO2           | 2    | -              | -                |  |

| J16            | PR12B            | 2    | С              | PCLKC2_0         | PR17B            | 2    | С              | PCLKC2_0         |  |

| H16            | PR12A            | 2    | Т              | PCLKT2_0         | PR17A            | 2    | Т              | PCLKT2_0         |  |

| H13            | PR13B            | 2    | C <sup>3</sup> | -                | PR16B            | 2    | C <sup>3</sup> | -                |  |

| H12            | PR13A            | 2    | T <sup>3</sup> | -                | PR16A            | 2    | T <sup>3</sup> | DQS              |  |

| H15            | PR2B             | 2    | C <sup>3</sup> | -                | PR15B            | 2    | -              | -                |  |

| H14            | PR6B             | 2    | -              | VREF1_2          | PR14A            | 2    | -              | VREF1_2          |  |

| -              | GNDIO2           | 2    | -              | -                | GNDIO2           | 2    | -              | -                |  |

| G15            | PR11B            | 2    | C <sup>3</sup> | -                | PR13B            | 2    | C <sup>3</sup> | -                |  |

| G14            | PR11A            | 2    | Т³             | -                | PR13A            | 2    | T <sup>3</sup> | -                |  |

| G16            | PR8B             | 2    | С              | RUM0_PLLC_IN_A   | PR12B            | 2    | С              | RUM0_PLLC_IN_A   |  |

| F16            | PR8A             | 2    | Т              | RUM0_PLLT_IN_A   | PR12A            | 2    | Т              | RUM0_PLLT_IN_A   |  |

| G13            | PR2A             | 2    | T <sup>3</sup> | -                | PR11B            | 2    | -              | -                |  |

| -              | GNDIO2           | 2    | -              | -                | GNDIO2           | 2    | -              | -                |  |

| G12            | PR9B             | 2    | C <sup>3</sup> | -                | PR8B             | 2    | С              | -                |  |

| F13            | PR9A             | 2    | T³             | -                | PR8A             | 2    | Т              | -                |  |

| B16            | PR7B             | 2    | C <sup>3</sup> | -                | PR7B             | 2    | C <sup>3</sup> | -                |  |

| C16            | PR7A             | 2    | T <sup>3</sup> | DQS              | PR7A             | 2    | T <sup>3</sup> | DQS              |  |

| F15            | PR14A            | 2    | -              | -                | PR6B             | 2    | -              | -                |  |

| E15            | PR5A             | 2    | -              | VREF2_2          | PR5A             | 2    | -              | VREF2_2          |  |

| -              | GNDIO2           | 2    | -              | -                | GNDIO2           | 2    | -              | -                |  |

| F14            | PR4B             | 2    | C <sup>3</sup> | -                | PR4B             | 2    | C <sup>3</sup> | -                |  |

| E14            | PR4A             | 2    | T <sup>3</sup> | -                | PR4A             | 2    | T <sup>3</sup> | -                |  |

| D15            | PR3B             | 2    | С              | RUM0_PLLC_FB_A   | PR3B             | 2    | С              | RUM0_PLLC_FB_A   |  |

| C15            | PR3A             | 2    | T              | RUM0_PLLT_FB_A   | PR3A             | 2    | Т              | RUM0_PLLT_FB_A   |  |

# LFXP6 & LFXP10 Logic Signal Connections: 256 fpBGA (Cont.)

|                | LFXP6            |      |              |                  | LFXP10           |      |              |                  |  |

|----------------|------------------|------|--------------|------------------|------------------|------|--------------|------------------|--|

| Ball<br>Number | Ball<br>Function | Bank | Differential | Dual<br>Function | Ball<br>Function | Bank | Differential | Dual<br>Function |  |

| E8             | PT13B            | 0    | -            | -                | PT17B            | 0    | -            | -                |  |

| D8             | PT12A            | 0    | -            | DOUT             | PT16A            | 0    | -            | DOUT             |  |

| A6             | PT11B            | 0    | С            | -                | PT15B            | 0    | С            | -                |  |

| -              | GNDIO0           | 0    | -            | -                | GNDIO0           | 0    | -            | -                |  |

| C6             | PT11A            | 0    | Т            | WRITEN           | PT15A            | 0    | Т            | WRITEN           |  |

| E7             | PT10B            | 0    | С            | -                | PT14B            | 0    | С            | -                |  |

| D7             | PT10A            | 0    | Т            | VREF1_0          | PT14A            | 0    | Т            | VREF1_0          |  |

| A5             | PT9B             | 0    | С            | -                | PT13B            | 0    | С            | -                |  |

| B5             | PT9A             | 0    | Т            | DI               | PT13A            | 0    | Т            | DI               |  |

| A4             | PT8B             | 0    | С            | -                | PT12B            | 0    | С            | -                |  |

| B6             | PT8A             | 0    | Т            | CSN              | PT12A            | 0    | Т            | CSN              |  |

| E6             | PT7B             | 0    | С            | -                | PT11B            | 0    | С            | -                |  |

| -              | GNDIO0           | 0    | -            | -                | GNDIO0           | 0    | -            | -                |  |

| D6             | PT7A             | 0    | Т            | -                | PT11A            | 0    | Т            | -                |  |

| D5             | PT6B             | 0    | С            | VREF2_0          | PT10B            | 0    | С            | VREF2_0          |  |

| A3             | PT6A             | 0    | Т            | DQS              | PT10A            | 0    | Т            | DQS              |  |

| B3             | PT5B             | 0    | -            | -                | PT9B             | 0    | -            | -                |  |

| B2             | PT4A             | 0    | -            | -                | PT8A             | 0    | -            | -                |  |

| A2             | PT3B             | 0    | С            | -                | PT7B             | 0    | С            | -                |  |

| B1             | PT3A             | 0    | Т            | -                | PT7A             | 0    | Т            | -                |  |

| F5             | PT2B             | 0    | С            | -                | PT6B             | 0    | С            | -                |  |

| -              | GNDIO0           | 0    | -            | -                | GNDIO0           | 0    | -            | -                |  |

| C5             | PT2A             | 0    | Т            | -                | PT6A             | 0    | Т            | -                |  |

| C4             | CFG0             | 0    | -            | -                | CFG0             | 0    | -            | -                |  |

| B4             | CFG1             | 0    | -            | -                | CFG1             | 0    | -            | -                |  |

| C3             | DONE             | 0    | -            | -                | DONE             | 0    | -            | -                |  |

| A1             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |

| A16            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |

| F11            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |

| F6             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |

| G10            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |

| G7             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |

| G8             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |

| G9             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |

| H10            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |

| H7             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |

| H8             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |

| H9             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |

| J10            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |

| J7             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |

| J8             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |

| J9             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |

# LFXP15 & LFXP20 Logic Signal Connections: 484 fpBGA (Cont.)

|                |                                           |      | LFXP15         |                  | LFXP20                                    |      |                |                  |  |

|----------------|-------------------------------------------|------|----------------|------------------|-------------------------------------------|------|----------------|------------------|--|

| Ball<br>Number | Ball<br>Function                          | Bank | Differential   | Dual<br>Function | Ball<br>Function                          | Bank | Differential   | Dual<br>Function |  |

| T6             | PL41A                                     | 6    | Т              | -                | PL45A                                     | 6    | Т              | -                |  |

| T5             | PL41B                                     | 6    | С              | -                | PL45B                                     | 6    | С              | -                |  |

| -              | GNDIO6                                    | 6    | -              | -                | GNDIO6                                    | 6    | -              | -                |  |

| U3             | PL42A                                     | 6    | T <sup>3</sup> | -                | PL46A                                     | 6    | T <sup>3</sup> | -                |  |

| U4             | PL42B                                     | 6    | C <sup>3</sup> | -                | PL46B                                     | 6    | C <sup>3</sup> | -                |  |

| V4             | PL43A                                     | 6    | -              | -                | PL47A                                     | 6    | -              | -                |  |

| W4             | SLEEPN <sup>1</sup> /<br>TOE <sup>2</sup> | -    | -              | -                | SLEEPN <sup>1</sup> /<br>TOE <sup>2</sup> | -    | -              | -                |  |

| W5             | INITN                                     | 5    | -              | -                | INITN                                     | 5    | -              | -                |  |

| Y3             | -                                         | -    | -              | -                | PB3B                                      | 5    | -              | -                |  |

| -              | GNDIO5                                    | 5    | -              | -                | GNDIO5                                    | 5    | -              | -                |  |

| U5             | -                                         | -    | -              | -                | PB4A                                      | 5    | Т              | -                |  |

| V5             | -                                         | -    | -              | -                | PB4B                                      | 5    | С              | -                |  |

| Y4             | -                                         | -    | -              | -                | PB5A                                      | 5    | Т              | -                |  |

| Y5             | -                                         | -    | -              | -                | PB5B                                      | 5    | С              | -                |  |

| V6             | -                                         | -    | -              | -                | PB6A                                      | 5    | Т              | -                |  |

| -              | GNDIO5                                    | 5    | -              | -                | GNDIO5                                    | 5    | -              | -                |  |

| U6             | -                                         | -    | -              | -                | PB6B                                      | 5    | С              | -                |  |

| W6             | PB3A                                      | 5    | Т              | -                | PB7A                                      | 5    | Т              | -                |  |

| Y6             | PB3B                                      | 5    | С              | -                | PB7B                                      | 5    | С              | -                |  |

| AA2            | PB4A                                      | 5    | Т              | -                | PB8A                                      | 5    | Т              | -                |  |

| AA3            | PB4B                                      | 5    | С              | -                | PB8B                                      | 5    | С              | -                |  |

| V7             | PB5A                                      | 5    | -              | -                | PB9A                                      | 5    | -              | -                |  |

| U7             | PB6B                                      | 5    | -              | -                | PB10B                                     | 5    | -              | -                |  |

| Y7             | PB7A                                      | 5    | Т              | DQS              | PB11A                                     | 5    | Т              | DQS              |  |

| W7             | PB7B                                      | 5    | С              | -                | PB11B                                     | 5    | С              | -                |  |

| AA4            | PB8A                                      | 5    | Т              | -                | PB12A                                     | 5    | Т              | -                |  |

| -              | GNDIO5                                    | 5    | -              | -                | GNDIO5                                    | 5    | -              | -                |  |

| AA5            | PB8B                                      | 5    | С              | -                | PB12B                                     | 5    | С              | -                |  |

| AB3            | PB9A                                      | 5    | Т              | -                | PB13A                                     | 5    | Т              | -                |  |

| AB4            | PB9B                                      | 5    | С              | -                | PB13B                                     | 5    | С              | -                |  |

| AA6            | PB10A                                     | 5    | Т              | -                | PB14A                                     | 5    | Т              | -                |  |

| AA7            | PB10B                                     | 5    | С              | -                | PB14B                                     | 5    | С              | -                |  |

| U8             | PB11A                                     | 5    | Т              | -                | PB15A                                     | 5    | Т              | -                |  |

| V8             | PB11B                                     | 5    | С              | -                | PB15B                                     | 5    | С              | -                |  |

| Y8             | PB12A                                     | 5    | Т              | VREF1_5          | PB16A                                     | 5    | Т              | VREF1_5          |  |

| -              | GNDIO5                                    | 5    | -              | -                | GNDIO5                                    | 5    | -              | -                |  |

| W8             | PB12B                                     | 5    | С              | -                | PB16B                                     | 5    | С              | -                |  |

| V9             | PB13A                                     | 5    | -              | -                | PB17A                                     | 5    | -              | -                |  |

| U9             | PB14B                                     | 5    | -              | -                | PB18B                                     | 5    | -              | -                |  |

| Y9             | PB15A                                     | 5    | Т              | DQS              | PB19A                                     | 5    | Т              | DQS              |  |

| W9             | PB15B                                     | 5    | С              | -                | PB19B                                     | 5    | С              | -                |  |

# LFXP15 & LFXP20 Logic Signal Connections: 484 fpBGA (Cont.)

|                |                  |      | LFXP15         |                  | LFXP20           |      |                |                  |  |

|----------------|------------------|------|----------------|------------------|------------------|------|----------------|------------------|--|

| Ball<br>Number | Ball<br>Function | Bank | Differential   | Dual<br>Function | Ball<br>Function | Bank | Differential   | Dual<br>Function |  |

| R18            | PR38B            | 3    | С              | RLM0_PLLC_FB_A   | PR42B            | 3    | С              | RLM0_PLLC_FB_A   |  |

| R17            | PR38A            | 3    | Т              | RLM0_PLLT_FB_A   | PR42A            | 3    | Т              | RLM0_PLLT_FB_A   |  |

| Y22            | PR37B            | 3    | C <sup>3</sup> | -                | PR41B            | 3    | C <sup>3</sup> | -                |  |

| Y21            | PR37A            | 3    | T <sup>3</sup> | DQS              | PR41A            | 3    | T <sup>3</sup> | DQS              |  |

| W22            | PR36B            | 3    | -              | -                | PR40B            | 3    | -              | -                |  |

| W21            | PR35A            | 3    | -              | VREF1_3          | PR39A            | 3    | -              | VREF1_3          |  |

| P17            | PR34B            | 3    | C <sup>3</sup> | -                | PR38B            | 3    | C <sup>3</sup> | -                |  |

| P18            | PR34A            | 3    | T³             | -                | PR38A            | 3    | T <sup>3</sup> | -                |  |

| -              | GNDIO3           | 3    | -              | -                | GNDIO3           | 3    | -              | -                |  |

| R19            | PR33B            | 3    | С              | -                | PR37B            | 3    | С              | -                |  |

| R20            | PR33A            | 3    | Т              | -                | PR37A            | 3    | Т              | -                |  |

| V22            | PR32B            | 3    | C <sup>3</sup> | -                | PR36B            | 3    | C <sup>3</sup> | -                |  |

| V21            | PR32A            | 3    | T <sup>3</sup> | -                | PR36A            | 3    | T <sup>3</sup> | -                |  |

| U22            | PR30B            | 3    | C <sup>3</sup> | -                | PR34B            | 3    | C <sup>3</sup> | -                |  |

| U21            | PR30A            | 3    | T <sup>3</sup> | -                | PR34A            | 3    | T <sup>3</sup> | -                |  |

| P19            | PR29B            | 3    | С              | RLM0_PLLC_IN_A   | PR33B            | 3    | С              | RLM0_PLLC_IN_A   |  |

| P20            | PR29A            | 3    | Т              | RLM0_PLLT_IN_A   | PR33A            | 3    | Т              | RLM0_PLLT_IN_A   |  |

| -              | GNDIO3           | 3    | -              | -                | GNDIO3           | 3    | -              | -                |  |

| T22            | PR28B            | 3    | C <sup>3</sup> | -                | PR32B            | 3    | C <sup>3</sup> | -                |  |

| T21            | PR28A            | 3    | T <sup>3</sup> | DQS              | PR32A            | 3    | T <sup>3</sup> | DQS              |  |

| R22            | PR27B            | 3    | -              | -                | PR31B            | 3    | -              | -                |  |

| R21            | PR26A            | 3    | -              | VREF2_3          | PR30A            | 3    | -              | VREF2_3          |  |

| N19            | PR25B            | 3    | C <sup>3</sup> | -                | PR29B            | 3    | C <sup>3</sup> | -                |  |

| N20            | PR25A            | 3    | T <sup>3</sup> | -                | PR29A            | 3    | T <sup>3</sup> | -                |  |

| N18            | PR24B            | 3    | С              | -                | PR28B            | 3    | С              | -                |  |

| M18            | PR24A            | 3    | Т              | -                | PR28A            | 3    | Т              | -                |  |

| -              | GNDIO3           | 3    | -              | -                | GNDIO3           | 3    | -              | -                |  |

| P22            | PR23B            | 3    | C <sup>3</sup> | -                | PR27B            | 3    | C <sup>3</sup> | -                |  |

| P21            | PR23A            | 3    | T <sup>3</sup> | -                | PR27A            | 3    | T <sup>3</sup> | -                |  |

| N22            | -                | -    | -              | -                | PR26B            | 3    | C <sup>3</sup> | -                |  |

| N21            | -                | -    | -              | -                | PR26A            | 3    | T <sup>3</sup> | -                |  |

| M19            | -                | -    | -              | -                | PR25B            | 3    | -              | -                |  |

| M20            | GNDP1            | -    | -              | -                | GNDP1            | -    | -              | -                |  |

| L18            | VCCP1            | -    | -              | -                | VCCP1            | -    | -              | -                |  |

| M21            | -                | -    | -              | -                | PR24A            | 2    | -              | -                |  |

| M22            | PR22B            | 2    | C <sup>3</sup> | -                | PR23B            | 2    | C <sup>3</sup> | -                |  |

| L22            | PR22A            | 2    | T <sup>3</sup> | -                | PR23A            | 2    | T <sup>3</sup> | -                |  |

| -              | GNDIO2           | 2    | -              | -                | GNDIO2           | 2    | -              | -                |  |

| L19            | -                | -    | -              | -                | PR22B            | 2    | C <sup>3</sup> | -                |  |

| L20            | -                | -    | -              | -                | PR22A            | 2    | T <sup>3</sup> | -                |  |

| L21            | PR21B            | 2    | С              | PCLKC2_0         | PR21B            | 2    | С              | PCLKC2_0         |  |

| K22            | PR21A            | 2    | Т              | PCLKT2_0         | PR21A            | 2    | Т              | PCLKT2_0         |  |

# LFXP15 & LFXP20 Logic Signal Connections: 484 fpBGA (Cont.)

|                | LFXP15           |      |              |                  | LFXP20           |      |              |                  |  |  |

|----------------|------------------|------|--------------|------------------|------------------|------|--------------|------------------|--|--|

| Ball<br>Number | Ball<br>Function | Bank | Differential | Dual<br>Function | Ball<br>Function | Bank | Differential | Dual<br>Function |  |  |

| A14            | PT30B            | 1    | -            | -                | PT34B            | 1    | -            | -                |  |  |

| B14            | PT29A            | 1    | -            | D4               | PT33A            | 1    | -            | D4               |  |  |

| C12            | PT28B            | 1    | С            | -                | PT32B            | 1    | С            | -                |  |  |

| B12            | PT28A            | 1    | Т            | D5               | PT32A            | 1    | Т            | D5               |  |  |

| -              | GNDIO1           | 1    | -            | -                | GNDIO1           | 1    | -            | -                |  |  |

| D12            | PT27B            | 1    | C            | D6               | PT31B            | 1    | С            | D6               |  |  |

| E12            | PT27A            | 1    | Т            | -                | PT31A            | 1    | Т            | -                |  |  |

| A13            | PT26B            | 1    | C            | D7               | PT30B            | 1    | С            | D7               |  |  |

| A12            | PT26A            | 1    | Т            | -                | PT30A            | 1    | Т            | -                |  |  |

| A11            | PT25B            | 0    | C            | BUSY             | PT29B            | 0    | С            | BUSY             |  |  |

| -              | GNDIO0           | 0    | -            | -                | GNDIO0           | 0    | -            | -                |  |  |

| A10            | PT25A            | 0    | Т            | CS1N             | PT29A            | 0    | Т            | CS1N             |  |  |

| D11            | PT24B            | 0    | С            | PCLKC0_0         | PT28B            | 0    | С            | PCLKC0_0         |  |  |

| E11            | PT24A            | 0    | Т            | PCLKT0_0         | PT28A            | 0    | Т            | PCLKT0_0         |  |  |

| B11            | PT23B            | 0    | С            | -                | PT27B            | 0    | С            | -                |  |  |

| C11            | PT23A            | 0    | Т            | DQS              | PT27A            | 0    | Т            | DQS              |  |  |

| B9             | PT22B            | 0    | -            | -                | PT26B            | 0    | -            | -                |  |  |

| A9             | PT21A            | 0    | -            | DOUT             | PT25A            | 0    | -            | DOUT             |  |  |

| B8             | PT20B            | 0    | С            | -                | PT24B            | 0    | С            | -                |  |  |

| -              | GNDIO0           | 0    | -            | -                | GNDIO0           | 0    | -            | -                |  |  |

| A8             | PT20A            | 0    | Т            | WRITEN           | PT24A            | 0    | Т            | WRITEN           |  |  |

| E10            | PT19B            | 0    | С            | -                | PT23B            | 0    | С            | -                |  |  |

| D10            | PT19A            | 0    | Т            | VREF1_0          | PT23A            | 0    | Т            | VREF1_0          |  |  |

| C10            | PT18B            | 0    | С            | -                | PT22B            | 0    | С            | -                |  |  |

| B10            | PT18A            | 0    | Т            | DI               | PT22A            | 0    | Т            | DI               |  |  |

| B7             | PT17B            | 0    | С            | -                | PT21B            | 0    | С            | -                |  |  |

| A7             | PT17A            | 0    | Т            | CSN              | PT21A            | 0    | Т            | CSN              |  |  |

| C9             | PT16B            | 0    | С            | -                | PT20B            | 0    | С            | -                |  |  |

| D9             | PT16A            | 0    | Т            | -                | PT20A            | 0    | Т            | -                |  |  |

| B6             | PT15B            | 0    | С            | VREF2_0          | PT19B            | 0    | С            | VREF2_0          |  |  |

| A6             | PT15A            | 0    | Т            | DQS              | PT19A            | 0    | Т            | DQS              |  |  |

| F9             | PT14B            | 0    | -            | -                | PT18B            | 0    | -            | -                |  |  |

| E9             | PT13A            | 0    | -            | -                | PT17A            | 0    | -            | -                |  |  |

| -              | GNDIO0           | 0    | -            | -                | GNDIO0           | 0    | -            | -                |  |  |

| B5             | PT12B            | 0    | С            | -                | PT16B            | 0    | С            | -                |  |  |

| A5             | PT12A            | 0    | Т            | -                | PT16A            | 0    | Т            | -                |  |  |

| C8             | PT11B            | 0    | С            | -                | PT15B            | 0    | С            | -                |  |  |

| D8             | PT11A            | 0    | Т            | -                | PT15A            | 0    | Т            | -                |  |  |

| B4             | PT10B            | 0    | С            | -                | PT14B            | 0    | С            | -                |  |  |

| A4             | PT10A            | 0    | Т            | -                | PT14A            | 0    | Т            | -                |  |  |

| F8             | PT9B             | 0    | С            | -                | PT13B            | 0    | С            | -                |  |  |

| E8             | PT9A             | 0    | Т            | -                | PT13A            | 0    | Т            | -                |  |  |

## **Conventional Packaging**

|               | Commercial |              |       |         |      |       |      |  |  |  |  |

|---------------|------------|--------------|-------|---------|------|-------|------|--|--|--|--|

| Part Number   | I/Os       | Voltage      | Grade | Package | Pins | Temp. | LUTs |  |  |  |  |

| LFXP3C-3Q208C | 136        | 1.8/2.5/3.3V | -3    | PQFP    | 208  | COM   | 3.1K |  |  |  |  |

| LFXP3C-4Q208C | 136        | 1.8/2.5/3.3V | -4    | PQFP    | 208  | COM   | 3.1K |  |  |  |  |

| LFXP3C-5Q208C | 136        | 1.8/2.5/3.3V | -5    | PQFP    | 208  | COM   | 3.1K |  |  |  |  |

| LFXP3C-3T144C | 100        | 1.8/2.5/3.3V | -3    | TQFP    | 144  | COM   | 3.1K |  |  |  |  |

| LFXP3C-4T144C | 100        | 1.8/2.5/3.3V | -4    | TQFP    | 144  | COM   | 3.1K |  |  |  |  |

| LFXP3C-5T144C | 100        | 1.8/2.5/3.3V | -5    | TQFP    | 144  | COM   | 3.1K |  |  |  |  |

| LFXP3C-3T100C | 62         | 1.8/2.5/3.3V | -3    | TQFP    | 100  | COM   | 3.1K |  |  |  |  |

| LFXP3C-4T100C | 62         | 1.8/2.5/3.3V | -4    | TQFP    | 100  | COM   | 3.1K |  |  |  |  |

| LFXP3C-5T100C | 62         | 1.8/2.5/3.3V | -5    | TQFP    | 100  | COM   | 3.1K |  |  |  |  |

| Part Number   | I/Os | Voltage      | Grade | Package | Pins | Temp. | LUTs |

|---------------|------|--------------|-------|---------|------|-------|------|

| LFXP6C-3F256C | 188  | 1.8/2.5/3.3V | -3    | fpBGA   | 256  | COM   | 5.8K |

| LFXP6C-4F256C | 188  | 1.8/2.5/3.3V | -4    | fpBGA   | 256  | COM   | 5.8K |

| LFXP6C-5F256C | 188  | 1.8/2.5/3.3V | -5    | fpBGA   | 256  | COM   | 5.8K |

| LFXP6C-3Q208C | 142  | 1.8/2.5/3.3V | -3    | PQFP    | 208  | COM   | 5.8K |

| LFXP6C-4Q208C | 142  | 1.8/2.5/3.3V | -4    | PQFP    | 208  | COM   | 5.8K |

| LFXP6C-5Q208C | 142  | 1.8/2.5/3.3V | -5    | PQFP    | 208  | COM   | 5.8K |

| LFXP6C-3T144C | 100  | 1.8/2.5/3.3V | -3    | TQFP    | 144  | COM   | 5.8K |

| LFXP6C-4T144C | 100  | 1.8/2.5/3.3V | -4    | TQFP    | 144  | COM   | 5.8K |

| LFXP6C-5T144C | 100  | 1.8/2.5/3.3V | -5    | TQFP    | 144  | COM   | 5.8K |

| Part Number    | I/Os | Voltage      | Grade | Package | Pins | Temp. | LUTs |

|----------------|------|--------------|-------|---------|------|-------|------|

| LFXP10C-3F388C | 244  | 1.8/2.5/3.3V | -3    | fpBGA   | 388  | COM   | 9.7K |

| LFXP10C-4F388C | 244  | 1.8/2.5/3.3V | -4    | fpBGA   | 388  | COM   | 9.7K |

| LFXP10C-5F388C | 244  | 1.8/2.5/3.3V | -5    | fpBGA   | 388  | COM   | 9.7K |

| LFXP10C-3F256C | 188  | 1.8/2.5/3.3V | -3    | fpBGA   | 256  | COM   | 9.7K |

| LFXP10C-4F256C | 188  | 1.8/2.5/3.3V | -4    | fpBGA   | 256  | COM   | 9.7K |

| LFXP10C-5F256C | 188  | 1.8/2.5/3.3V | -5    | fpBGA   | 256  | COM   | 9.7K |

| Part Number    | I/Os | Voltage      | Grade | Package | Pins | Temp. | LUTs  |  |  |  |  |

|----------------|------|--------------|-------|---------|------|-------|-------|--|--|--|--|

| LFXP15C-3F484I | 300  | 1.8/2.5/3.3V | -3    | fpBGA   | 484  | IND   | 15.5K |  |  |  |  |

| LFXP15C-4F484I | 300  | 1.8/2.5/3.3V | -4    | fpBGA   | 484  | IND   | 15.5K |  |  |  |  |

| LFXP15C-3F388I | 268  | 1.8/2.5/3.3V | -3    | fpBGA   | 388  | IND   | 15.5K |  |  |  |  |

| LFXP15C-4F388I | 268  | 1.8/2.5/3.3V | -4    | fpBGA   | 388  | IND   | 15.5K |  |  |  |  |

| LFXP15C-3F256I | 188  | 1.8/2.5/3.3V | -3    | fpBGA   | 256  | IND   | 15.5K |  |  |  |  |

| LFXP15C-4F256I | 188  | 1.8/2.5/3.3V | -4    | fpBGA   | 256  | IND   | 15.5K |  |  |  |  |

### Industrial (Cont.)

| Part Number    | I/Os | Voltage      | Grade | Package | Pins | Temp. | LUTs  |

|----------------|------|--------------|-------|---------|------|-------|-------|

| LFXP20C-3F484I | 340  | 1.8/2.5/3.3V | -3    | fpBGA   | 484  | IND   | 19.7K |

| LFXP20C-4F484I | 340  | 1.8/2.5/3.3V | -4    | fpBGA   | 484  | IND   | 19.7K |

| LFXP20C-3F388I | 268  | 1.8/2.5/3.3V | -3    | fpBGA   | 388  | IND   | 19.7K |

| LFXP20C-4F388I | 268  | 1.8/2.5/3.3V | -4    | fpBGA   | 388  | IND   | 19.7K |

| LFXP20C-3F256I | 188  | 1.8/2.5/3.3V | -3    | fpBGA   | 256  | IND   | 19.7K |

| LFXP20C-4F256I | 188  | 1.8/2.5/3.3V | -4    | fpBGA   | 256  | IND   | 19.7K |

| Part Number   | I/Os | Voltage | Grade | Package | Pins | Temp. | LUTs |

|---------------|------|---------|-------|---------|------|-------|------|

| LFXP3E-3Q208I | 136  | 1.2V    | -3    | PQFP    | 208  | IND   | 3.1K |

| LFXP3E-4Q208I | 136  | 1.2V    | -4    | PQFP    | 208  | IND   | 3.1K |

| LFXP3E-3T144I | 100  | 1.2V    | -3    | TQFP    | 144  | IND   | 3.1K |

| LFXP3E-4T144I | 100  | 1.2V    | -4    | TQFP    | 144  | IND   | 3.1K |

| LFXP3E-3T100I | 62   | 1.2V    | -3    | TQFP    | 100  | IND   | 3.1K |

| LFXP3E-4T100I | 62   | 1.2V    | -4    | TQFP    | 100  | IND   | 3.1K |

| Part Number   | I/Os | Voltage | Grade | Package | Pins | Temp. | LUTs |

|---------------|------|---------|-------|---------|------|-------|------|

| LFXP6E-3F256I | 188  | 1.2V    | -3    | fpBGA   | 256  | IND   | 5.8K |

| LFXP6E-4F256I | 188  | 1.2V    | -4    | fpBGA   | 256  | IND   | 5.8K |

| LFXP6E-3Q208I | 142  | 1.2V    | -3    | PQFP    | 208  | IND   | 5.8K |

| LFXP6E-4Q208I | 142  | 1.2V    | -4    | PQFP    | 208  | IND   | 5.8K |

| LFXP6E-3T144I | 100  | 1.2V    | -3    | TQFP    | 144  | IND   | 5.8K |

| LFXP6E-4T144I | 100  | 1.2V    | -4    | TQFP    | 144  | IND   | 5.8K |

| Part Number    | l/Os | Voltage | Grade | Package | Pins | Temp. | LUTs |

|----------------|------|---------|-------|---------|------|-------|------|

| LFXP10E-3F388I | 244  | 1.2V    | -3    | fpBGA   | 388  | IND   | 9.7K |

| LFXP10E-4F388I | 244  | 1.2V    | -4    | fpBGA   | 388  | IND   | 9.7K |