Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Detans                         |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                   |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | 20000                                                                      |

| Total RAM Bits                 | 405504                                                                     |

| Number of I/O                  | 188                                                                        |

| Number of Gates                | -                                                                          |

| Voltage - Supply               | 1.14V ~ 1.26V                                                              |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                            |

| Package / Case                 | 256-BGA                                                                    |

| Supplier Device Package        | 256-FPBGA (17x17)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfxp20e-5fn256c |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Lattice Semiconductor

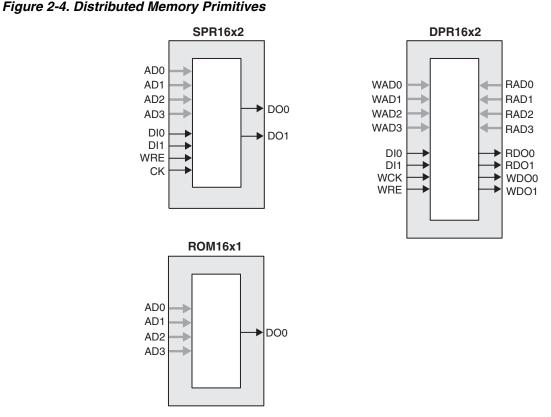

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of Slices required to implement different distributed RAM primitives. Figure 2-4 shows the distributed memory primitive block diagrams. Dual port memories involve the pairing of two Slices, one Slice functions as the read-write port. The other companion Slice supports the read-only port. For more information on RAM mode in LatticeXP devices, please see details of additional technical documentation at the end of this data sheet.

#### Table 2-3. Number of Slices Required for Implementing Distributed RAM

|                                                  | SPR16x2 | DPR16x2 |  |  |  |  |  |

|--------------------------------------------------|---------|---------|--|--|--|--|--|

| Number of Slices                                 | 1       | 2       |  |  |  |  |  |

| Note: SPR = Single Port RAM, DPR = Dual Port RAM |         |         |  |  |  |  |  |

| <br>District of Manager |  |

|-------------------------|--|

|                         |  |

|                         |  |

**ROM Mode:** The ROM mode uses the same principal as the RAM modes, but without the Write port. Pre-loading is accomplished through the programming interface during configuration.

#### **PFU Modes of Operation**

Slices can be combined within a PFU to form larger functions. Table 2-4 tabulates these modes and documents the functionality possible at the PFU level.

#### Table 2-4. PFU Modes of Operation

| Logic                      | Ripple            | RAM <sup>1</sup>           | ROM         |

|----------------------------|-------------------|----------------------------|-------------|

| LUT 4x8 or<br>MUX 2x1 x 8  | 2-bit Add x 4     | SPR16x2 x 4<br>DPR16x2 x 2 | ROM16x1 x 8 |

| LUT 5x4 or<br>MUX 4x1 x 4  | 2-bit Sub v /     |                            | ROM16x2 x 4 |

| LUT 6x 2 or<br>MUX 8x1 x 2 | 2-bit Counter x 4 | SPR16x8 x 1                | ROM16x4 x 2 |

| LUT 7x1 or<br>MUX 16x1 x 1 | 2-bit Comp x 4    |                            | ROM16x8 x 1 |

1. These modes are not available in PFF blocks

## Routing

There are many resources provided in the LatticeXP devices to route signals individually or as buses with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The inter-PFU connections are made with x1 (spans two PFU), x2 (spans three PFU) and x6 (spans seven PFU). The x1 and x2 connections provide fast and efficient connections in horizontal, vertical and diagonal directions. The x2 and x6 resources are buffered allowing both short and long connections routing between PFUs.

The ispLEVER design tool takes the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

## **Clock Distribution Network**

The clock inputs are selected from external I/O, the sysCLOCK<sup>™</sup> PLLs or routing. These clock inputs are fed through the chip via a clock distribution system.

### **Primary Clock Sources**

LatticeXP devices derive clocks from three primary sources: PLL outputs, dedicated clock inputs and routing. LatticeXP devices have two to four sysCLOCK PLLs, located on the left and right sides of the device. There are four dedicated clock inputs, one on each side of the device. Figure 2-5 shows the 20 primary clock sources. For more information on the PLL, please see details of additional technical documentation at the end of this data sheet.

## **Dynamic Clock Select (DCS)**

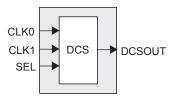

The DCS is a global clock buffer with smart multiplexer functions. It takes two independent input clock sources and outputs a clock signal without any glitches or runt pulses. This is achieved irrespective of where the select signal is toggled. There are eight DCS blocks per device, located in pairs at the center of each side. Figure 2-12 illustrates the DCS Block Macro.

#### Figure 2-12. DCS Block Primitive

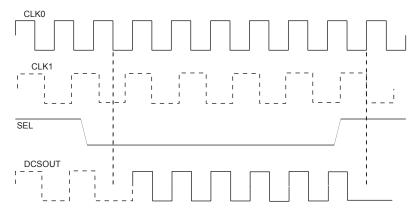

Figure 2-13 shows timing waveforms of the default DCS operating mode. The DCS block can be programmed to other modes. For more information on the DCS, please see details of additional technical documentation at the end of this data sheet.

#### Figure 2-13. DCS Waveforms

## sysMEM Memory

The LatticeXP family of devices contain a number of sysMEM Embedded Block RAM (EBR). The EBR consists of a 9-Kbit RAM, with dedicated input and output registers.

### sysMEM Memory Block

The sysMEM block can implement single port, dual port or pseudo dual port memories. Each block can be used in a variety of depths and widths as shown in Table 2-6.

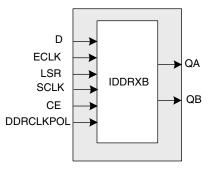

#### Figure 2-22. INDDRXB Primitive

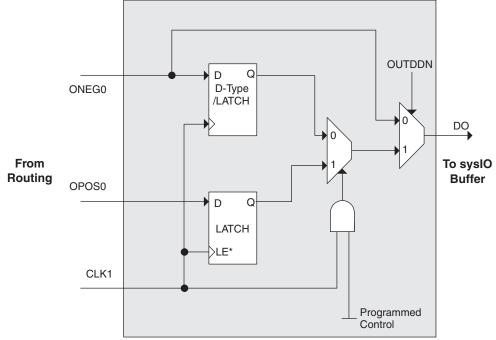

#### **Output Register Block**

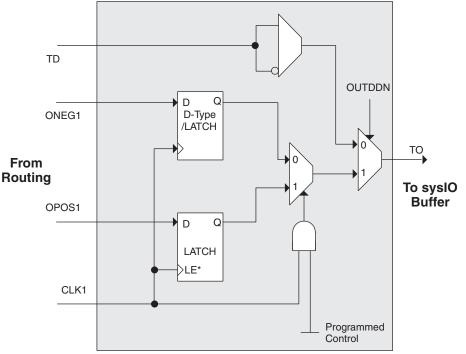

The output register block provides the ability to register signals from the core of the device before they are passed to the sysIO buffers. The block contains a register for SDR operation that is combined with an additional latch for DDR operation. Figure 2-23 shows the diagram of the Output Register Block.

In SDR mode, ONEG0 feeds one of the flip-flops that then feeds the output. The flip-flop can be configured as a Dtype or as a latch. In DDR mode, ONEG0 is fed into one register on the positive edge of the clock and OPOS0 is latched. A multiplexer running off the same clock selects the correct register for feeding to the output (D0).

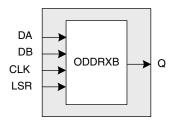

Figure 2-24 shows the design tool DDR primitives. The SDR output register has reset and clock enable available. The additional register for DDR operation does not have reset or clock enable available.

Figure 2-23. Output Register Block

\*Latch is transparent when input is low.

### Figure 2-24. ODDRXB Primitive

### Tristate Register Block

The tristate register block provides the ability to register tri-state control signals from the core of the device before they are passed to the sysIO buffers. The block contains a register for SDR operation and an additional latch for DDR operation. Figure 2-25 shows the diagram of the Tristate Register Block.

In SDR mode, ONEG1 feeds one of the flip-flops that then feeds the output. The flip-flop can be configured a Dtype or latch. In DDR mode, ONEG1 is fed into one register on the positive edge of the clock and OPOS1 is latched. A multiplexer running off the same clock selects the correct register for feeding to the output (D0).

Figure 2-25. Tristate Register Block

\*Latch is transparent when input is low.

#### Control Logic Block

The control logic block allows the selection and modification of control signals for use in the PIO block. A clock is selected from one of the clock signals provided from the general purpose routing and a DQS signal provided from the programmable DQS pin. The clock can optionally be inverted.

The clock enable and local reset signals are selected from the routing and optionally inverted. The global tristate signal is passed through this block.

## DDR Memory Support

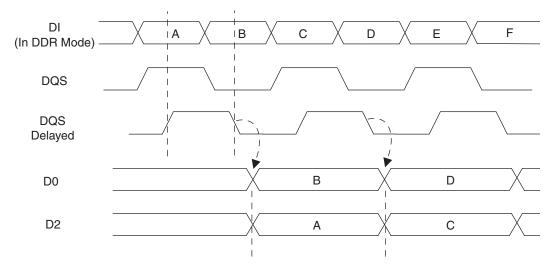

Implementing high performance DDR memory interfaces requires dedicated DDR register structures in the input (for read operations) and in the output (for write operations). As indicated in the PIO Logic section, the LatticeXP devices provide this capability. In addition to these registers, the LatticeXP devices contain two elements to simplify the design of input structures for read operations: the DQS delay block and polarity control logic.

## DLL Calibrated DQS Delay Block

Source Synchronous interfaces generally require the input clock to be adjusted in order to correctly capture data at the input register. For most interfaces a PLL is used for this adjustment, however in DDR memories the clock (referred to as DQS) is not free running so this approach cannot be used. The DQS Delay block provides the required clock alignment for DDR memory interfaces.

The DQS signal (selected PIOs only) feeds from the PAD through a DQS delay element to a dedicated DQS routing resource. The DQS signal also feeds the polarity control logic which controls the polarity of the clock to the sync registers in the input register blocks. Figures 2-26 and 2-27 show how the polarity control logic are routed to the PIOs.

The temperature, voltage and process variations of the DQS delay block are compensated by a set of calibration (6-bit bus) signals from two DLLs on opposite sides of the device. Each DLL compensates DQS Delays in its half of the device as shown in Figure 2-27. The DLL loop is compensated for temperature, voltage and process variations by the system clock and feedback loop.

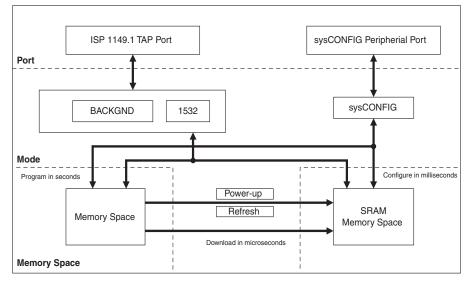

Figure 2-29 provides a pictorial representation of the different programming ports and modes available in the LatticeXP devices.

On power-up, the FPGA SRAM is ready to be configured with the sysCONFIG port active. The IEEE 1149.1 serial mode can be activated any time after power-up by sending the appropriate command through the TAP port.

#### Leave Alone I/O

When using 1532 mode for non-volatile memory programming, users may specify I/Os as high, low, tristated or held at current value. This provides excellent flexibility for implementing systems where reprogramming occurs on-the-fly.

#### TransFR (Transparent Field Reconfiguration)

TransFR (TFR) is a unique Lattice technology that allows users to update their logic in the field without interrupting system operation using a single ispVM command. See Lattice technical note #TN1087, *Minimizing System Interruption During Configuration Using TransFR Technology*, for details.

#### Security

The LatticeXP devices contain security bits that, when set, prevent the readback of the SRAM configuration and non-volatile memory spaces. Once set, the only way to clear security bits is to erase the memory space.

For more information on device configuration, please see details of additional technical documentation at the end of this data sheet.

#### Figure 2-29. ispXP Block Diagram

## Internal Logic Analyzer Capability (ispTRACY)

All LatticeXP devices support an internal logic analyzer diagnostic feature. The diagnostic features provide capabilities similar to an external logic analyzer, such as programmable event and trigger condition and deep trace memory. This feature is enabled by Lattice's ispTRACY. The ispTRACY utility is added into the user design at compile time.

For more information on ispTRACY, please see information regarding additional technical documentation at the end of this data sheet.

#### Oscillator

Every LatticeXP device has an internal CMOS oscillator which is used to derive a master serial clock for configuration. The oscillator and the master serial clock run continuously in the configuration mode. The default value of the master serial clock is 2.5MHz. Table 2-10 lists all the available Master Serial Clock frequencies. When a different Master Serial Clock is selected during the design process, the following sequence takes place:

- 1. User selects a different Master Serial Clock frequency for configuration.

- 2. During configuration the device starts with the default (2.5MHz) Master Serial Clock frequency.

- 3. The clock configuration settings are contained in the early configuration bit stream.

- 4. The Master Serial Clock frequency changes to the selected frequency once the clock configuration bits are received.

For further information on the use of this oscillator for configuration, please see details of additional technical documentation at the end of this data sheet.

Table 2-10. Selectable Master Serial Clock (CCLK) Frequencies During Configuration

| CCLK (MHz)       | CCLK (MHz) | CCLK (MHz) |

|------------------|------------|------------|

| 2.5 <sup>1</sup> | 13         | 45         |

| 4.3              | 15         | 51         |

| 5.4              | 20         | 55         |

| 6.9              | 26         | 60         |

| 8.1              | 30         | 130        |

| 9.2              | 34         | —          |

| 10.0             | 41         | —          |

| 1. Default       | •          | •          |

## **Density Shifting**

The LatticeXP family has been designed to ensure that different density devices in the same package have the same pin-out. Furthermore, the architecture ensures a high success rate when performing design migration from lower density parts to higher density parts. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case.

# Supply Current (Standby)<sup>1, 2, 3, 4</sup>

| Symbol             | Parameter                                           | Device    | Typ.⁵ | Units |

|--------------------|-----------------------------------------------------|-----------|-------|-------|

|                    |                                                     | LFXP3E    | 15    | mA    |

|                    |                                                     | LFXP6E    | 20    | mA    |

|                    |                                                     | LFXP10E   | 35    | mA    |

|                    |                                                     | LFXP15E   | 45    | mA    |

| I                  | Coro Power Supply                                   | LFXP20E   | 55    | mA    |

| I <sub>CC</sub>    | Core Power Supply                                   | LFXP3C    | 35    | mA    |

|                    |                                                     | LFXP6C    | 40    | mA    |

|                    |                                                     | LFXP10C   | 70    | mA    |

|                    |                                                     | LFXP15C   | 80    | mA    |

|                    |                                                     | LFXP20C   | 90    | mA    |

| I <sub>CCP</sub>   | PLL Power Supply<br>(per PLL)                       | All       | 8     | mA    |

|                    |                                                     | LFXP3E/C  | 22    | mA    |

|                    |                                                     | LFXP6E/C  | 22    | mA    |

| I <sub>CCAUX</sub> | Auxiliary Power Supply<br>V <sub>CCAUX</sub> = 3.3V | LFXP10E/C | 30    | mA    |

|                    |                                                     | LFXP15E/C | 30    | mA    |

|                    |                                                     | LFXP20E/C | 30    | mA    |

| Iccio              | Bank Power Supply <sup>6</sup>                      | All       | 2     | mA    |

| I <sub>CCJ</sub>   | V <sub>CCJ</sub> Power Supply                       | All       | 1     | mA    |

### **Over Recommended Operating Conditions**

1. For further information on supply current, please see details of additional technical documentation at the end of this data sheet.

2. Assumes all outputs are tristated, all inputs are configured as LVCMOS and held at the VCCIO or GND.

3. Frequency 0MHz.

4. User pattern: blank.

5.  $T_A=25^{\circ}C$ , power supplies at nominal voltage.

6. Per bank.

# Programming and Erase Flash Supply Current<sup>1, 2, 3, 4, 5</sup>

| Symbol             | Parameter                                           | Device    | Тур.6 | Units |

|--------------------|-----------------------------------------------------|-----------|-------|-------|

|                    |                                                     | LFXP3E    | 30    | mA    |

|                    |                                                     | LFXP6E    | 40    | mA    |

|                    |                                                     | LFXP10E   | 50    | mA    |

|                    |                                                     | LFXP15E   | 60    | mA    |

|                    | Core Dower Supply                                   | LFXP20E   | 70    | mA    |

| Icc                | Core Power Supply                                   | LFXP3C    | 50    | mA    |

|                    |                                                     | LFXP6C    | 60    | mA    |

|                    |                                                     | LFXP10C   | 90    | mA    |

|                    |                                                     | LFXP15C   | 100   | mA    |

|                    |                                                     | LFXP20C   | 110   | mA    |

|                    |                                                     | LFXP3E/C  | 50    | mA    |

|                    |                                                     | LFXP6E/C  | 60    | mA    |

| I <sub>CCAUX</sub> | Auxiliary Power Supply<br>V <sub>CCAUX</sub> = 3.3V | LFXP10E/C | 90    | mA    |

|                    |                                                     | LFXP15E/C | 110   | mA    |

|                    |                                                     | LFXP20E/C | 130   | mA    |

| I <sub>CCJ</sub>   | V <sub>CCJ</sub> Power Supply <sup>7</sup>          | All       | 2     | mA    |

1. For further information on supply current, please see details of additional technical documentation at the end of this data sheet.

2. Assumes all outputs are tristated, all inputs are configured as LVCMOS and held at the  $V_{\mbox{CCIO}}$  or GND.

3. Blank user pattern; typical Flash pattern.

4. Bypass or decoupling capacitor across the supply.

5. JTAG programming is at 1MHz.

6.  $T_A=25^{\circ}C$ , power supplies at nominal voltage.

7. When programming via JTAG.

## sysIO Recommended Operating Conditions

|                     |       | V <sub>CCIO</sub> |       |       | V <sub>REF</sub> (V) |       |

|---------------------|-------|-------------------|-------|-------|----------------------|-------|

| Standard            | Min.  | Тур.              | Max.  | Min.  | Тур.                 | Max.  |

| LVCMOS 3.3          | 3.135 | 3.3               | 3.465 | —     | —                    | —     |

| LVCMOS 2.5          | 2.375 | 2.5               | 2.625 | —     | —                    | —     |

| LVCMOS 1.8          | 1.71  | 1.8               | 1.89  | —     | —                    | —     |

| LVCMOS 1.5          | 1.425 | 1.5               | 1.575 | —     | —                    | —     |

| LVCMOS 1.2          | 1.14  | 1.2               | 1.26  | —     | —                    | —     |

| LVTTL               | 3.135 | 3.3               | 3.465 | —     | —                    | —     |

| PCI33               | 3.135 | 3.3               | 3.465 | —     | —                    | —     |

| SSTL18 Class I      | 1.71  | 1.8               | 1.89  | 0.833 | 0.9                  | 0.969 |

| SSTL2 Class I, II   | 2.375 | 2.5               | 2.625 | 1.15  | 1.25                 | 1.35  |

| SSTL3 Class I, II   | 3.135 | 3.3               | 3.465 | 1.3   | 1.5                  | 1.7   |

| HSTL15 Class I      | 1.425 | 1.5               | 1.575 | 0.68  | 0.75                 | 0.9   |

| HSTL15 Class III    | 1.425 | 1.5               | 1.575 | —     | 0.9                  | —     |

| HSTL 18 Class I, II | 1.71  | 1.8               | 1.89  | —     | 0.9                  | —     |

| HSTL 18 Class III   | 1.71  | 1.8               | 1.89  | —     | 1.08                 | —     |

| LVDS                | 2.375 | 2.5               | 2.625 | —     | —                    | —     |

| LVPECL <sup>1</sup> | 3.135 | 3.3               | 3.465 | —     | —                    | —     |

| BLVDS <sup>1</sup>  | 2.375 | 2.5               | 2.625 | —     | —                    | —     |

1. Inputs on chip. Outputs are implemented with the addition of external resistors.

## **Derating Logic Timing**

Logic timing provided in the following sections of this data sheet and in the ispLEVER design tools are worst case numbers in the operating range. Actual delays at nominal temperature and voltage for best-case process can be much better than the values given in the tables. The ispLEVER design tool from Lattice can provide logic timing numbers at a particular temperature and voltage.

## **Signal Descriptions (Cont.)**

| Signal Name                           | I/O     | Descriptions                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test and Programming (Dedicated pins. | Pull-up | b is enabled on input pins during configuration.)                                                                                                                                                                                                                                                                               |

| TMS                                   | I       | Test Mode Select input, used to control the 1149.1 state machine.                                                                                                                                                                                                                                                               |

| тск                                   | I       | Test Clock input pin, used to clock the 1149.1 state machine.                                                                                                                                                                                                                                                                   |

| TDI                                   | I       | Test Data in pin, used to load data into device using 1149.1 state machine.<br>After power-up, this TAP port can be activated for configuration by sending<br>appropriate command. (Note: once a configuration port is selected it is<br>locked. Another configuration port cannot be selected until the power-up<br>sequence). |

| TDO                                   | 0       | Output pin -Test Data out pin used to shift data out of device using 1149.1.                                                                                                                                                                                                                                                    |

| V <sub>CCJ</sub>                      | —       | V <sub>CCJ</sub> - The power supply pin for JTAG Test Access Port.                                                                                                                                                                                                                                                              |

| Configuration Pads (used during sysCO | NFIG)   |                                                                                                                                                                                                                                                                                                                                 |

| CFG[1:0]                              | I       | Mode pins used to specify configuration modes values latched on rising edge of INITN. During configuration, a pull-up is enabled.                                                                                                                                                                                               |

| INITN                                 | I/O     | Open Drain pin - Indicates the FPGA is ready to be configured. During con-<br>figuration, a pull-up is enabled. If CFG1 and CFG0 are high (SDM) then this<br>pin is pulled low.                                                                                                                                                 |

| PROGRAMN                              | I       | Initiates configuration sequence when asserted low. This pin always has an active pull-up.                                                                                                                                                                                                                                      |

| DONE                                  | I/O     | Open Drain pin - Indicates that the configuration sequence is complete, and the startup sequence is in progress.                                                                                                                                                                                                                |

| CCLK                                  | I/O     | Configuration Clock for configuring an FPGA in sysCONFIG mode.                                                                                                                                                                                                                                                                  |

| BUSY                                  | I/O     | Generally not used. After configuration it is a user-programmable I/O pin.                                                                                                                                                                                                                                                      |

| CSN                                   | I       | sysCONFIG chip select (Active low). During configuration, a pull-up is enabled. After configuration it is user a programmable I/O pin.                                                                                                                                                                                          |

| CS1N                                  | I       | sysCONFIG chip select (Active Low). During configuration, a pull-up is enabled. After configuration it is user programmable I/O pin                                                                                                                                                                                             |

| WRITEN                                | I       | Write Data on Parallel port (Active low). After configuration it is a user pro-<br>grammable I/O pin                                                                                                                                                                                                                            |

| D[7:0]                                | I/O     | sysCONFIG Port Data I/O. After configuration these are user programmable I/O pins.                                                                                                                                                                                                                                              |

| DOUT, CSON                            | 0       | Output for serial configuration data (rising edge of CCLK) when using sys-<br>CONFIG port. After configuration, it is a user-programmable I/O pin.                                                                                                                                                                              |

| DI                                    | I       | Input for serial configuration data (clocked with CCLK) when using sysCON-<br>FIG port. During configuration, a pull-up is enabled. After configuration it is a user-programmable I/O pin.                                                                                                                                      |

| SLEEPN <sup>2</sup>                   | I       | Sleep Mode pin - Active low sleep pin.b When this pin is held high, the device operates normally.b When driven low, the device moves into Sleep Mode after a specified time. This pin has a weak internal pull-up, but when not used an external pull-up to $V_{CC}$ is recommended.                                            |

| TOE <sup>3</sup>                      | I       | Test Output Enable tri-states all I/O pins when driven low. This pin has a weak internal pull-up, but when not used an external pull-up to $V_{\rm CC}$ is recommended.                                                                                                                                                         |

Applies tob LFXP10, LFXP15 and LFXP20 only.

Applies to LFXP "C" devices only.

Applies to LFXP "E" devices only.

## LFXP3 & LFXP6 Logic Signal Connections: 208 PQFP (Cont.)

| Pin    |                                       |      | LFXP3          |               | LFXP6                                 |      |                |               |

|--------|---------------------------------------|------|----------------|---------------|---------------------------------------|------|----------------|---------------|

| Number | Pin Function                          | Bank | Differential   | Dual Function | Pin Function                          | Bank | Differential   | Dual Function |

| 47     | GNDIO6                                | 6    | -              | -             | GNDIO6                                | 6    | -              | -             |

| 48     | PL18B                                 | 6    | C <sup>3</sup> | -             | PL26B                                 | 6    | C <sup>3</sup> | -             |

| 49     | GND                                   | -    | -              | -             | GND                                   | -    | -              | -             |

| 50     | VCCAUX                                | -    | -              | -             | VCCAUX                                | -    | -              | -             |

| 51     | SLEEPN <sup>1</sup> /TOE <sup>2</sup> | -    | -              | -             | SLEEPN <sup>1</sup> /TOE <sup>2</sup> | -    | -              | -             |

| 52     | INITN                                 | 5    | -              | -             | INITN                                 | 5    | -              | -             |

| 53     | VCC                                   | -    | -              | -             | VCC                                   | -    | -              | -             |

| 54     | PB2B                                  | 5    | -              | VREF1_5       | PB5B                                  | 5    | -              | VREF1_5       |

| 55     | PB3A                                  | 5    | Т              | -             | PB6A                                  | 5    | Т              | DQS           |

| 56     | PB3B                                  | 5    | С              | -             | PB6B                                  | 5    | С              | -             |

| 57     | PB4A                                  | 5    | Т              | -             | PB7A                                  | 5    | Т              | -             |

| 58     | PB4B                                  | 5    | С              | -             | PB7B                                  | 5    | С              | -             |

| 59     | GNDIO5                                | 5    | -              | -             | GNDIO5                                | 5    | -              | -             |

| 60     | PB5A                                  | 5    | Т              | -             | PB8A                                  | 5    | Т              | -             |

| 61     | PB5B                                  | 5    | С              | VREF2_5       | PB8B                                  | 5    | С              | VREF2_5       |

| 62     | PB6A                                  | 5    | Т              | -             | PB9A                                  | 5    | Т              | -             |

| 63     | PB6B                                  | 5    | С              | -             | PB9B                                  | 5    | С              | -             |

| 64     | VCCIO5                                | 5    | -              | -             | VCCIO5                                | 5    | -              | -             |

| 65     | PB7A                                  | 5    | Т              | -             | PB10A                                 | 5    | Т              | -             |

| 66     | PB7B                                  | 5    | С              | -             | PB10B                                 | 5    | С              | -             |

| 67     | PB8A                                  | 5    | Т              | -             | PB11A                                 | 5    | Т              | -             |

| 68     | PB8B                                  | 5    | С              | -             | PB11B                                 | 5    | С              | -             |

| 69     | GNDIO5                                | 5    | -              | -             | GNDIO5                                | 5    | -              | -             |

| 70     | PB9A                                  | 5    | -              | -             | PB12A                                 | 5    | -              | -             |

| 71     | PB10B                                 | 5    | -              | -             | PB13B                                 | 5    | -              | -             |

| 72     | PB11A                                 | 5    | Т              | DQS           | PB14A                                 | 5    | Т              | DQS           |

| 73     | PB11B                                 | 5    | С              | -             | PB14B                                 | 5    | С              | -             |

| 74     | VCCIO5                                | 5    | -              | -             | VCCIO5                                | 5    | -              | -             |

| 75     | PB12A                                 | 5    | Т              | -             | PB15A                                 | 5    | Т              | -             |

| 76     | PB12B                                 | 5    | С              | -             | PB15B                                 | 5    | С              | -             |

| 77     | PB13A                                 | 5    | Т              | -             | PB16A                                 | 5    | Т              | -             |

| 78     | PB13B                                 | 5    | С              | -             | PB16B                                 | 5    | С              | -             |

| 79     | GND                                   | -    | -              | -             | GND                                   | -    | -              | -             |

| 80     | VCC                                   | -    | -              | -             | VCC                                   | -    | -              | -             |

| 81     | PB14A                                 | 4    | Т              | -             | PB17A                                 | 4    | Т              | -             |

| 82     | GNDIO4                                | 4    | -              | -             | GNDIO4                                | 4    | -              | -             |

| 83     | PB14B                                 | 4    | С              | -             | PB17B                                 | 4    | С              | -             |

| 84     | PB15A                                 | 4    | Т              | PCLKT4_0      | PB18A                                 | 4    | Т              | PCLKT4_0      |

| 85     | PB15B                                 | 4    | С              | PCLKC4_0      | PB18B                                 | 4    | С              | PCLKC4_0      |

| 86     | PB16A                                 | 4    | Т              | -             | PB19A                                 | 4    | Т              | -             |

| 87     | VCCIO4                                | 4    | -              | -             | VCCIO4                                | 4    | -              | -             |

| 88     | PB16B                                 | 4    | С              | -             | PB19B                                 | 4    | С              | -             |

| 89     | PB17A                                 | 4    | -              | -             | PB20A                                 | 4    | -              | -             |

| 90     | PB18B                                 | 4    | -              | -             | PB21B                                 | 4    | -              | -             |

| 91     | PB19A                                 | 4    | Т              | DQS           | PB22A                                 | 4    | Т              | DQS           |

| 92     | GNDIO4                                | 4    | -              | -             | GNDIO4                                | 4    | -              | -             |

|                |                                       |      | LFXP15         |                  | LFXP20                                |      |                |                  |

|----------------|---------------------------------------|------|----------------|------------------|---------------------------------------|------|----------------|------------------|

| Ball<br>Number | Ball<br>Function                      | Bank | Differential   | Dual<br>Function | Ball<br>Function                      | Bank | Differential   | Dual<br>Function |

| L4             | PL32A                                 | 6    | -              | -                | PL36A                                 | 6    | -              | -                |

| -              | GNDIO6                                | 6    | -              | -                | GNDIO6                                | 6    | -              | -                |

| K4             | PL33A                                 | 6    | Т              | -                | PL37A                                 | 6    | Т              | -                |

| K5             | PL33B                                 | 6    | С              | -                | PL37B                                 | 6    | С              | -                |

| N1             | PL35A                                 | 6    | -              | VREF2_6          | PL39A                                 | 6    | -              | VREF2_6          |

| N2             | PL36B                                 | 6    | -              | -                | PL40B                                 | 6    | -              | -                |

| P1             | PL37A                                 | 6    | Т³             | DQS              | PL41A                                 | 6    | T <sup>3</sup> | DQS              |

| P2             | PL37B                                 | 6    | C <sup>3</sup> | -                | PL41B                                 | 6    | C³             | -                |

| -              | GNDIO6                                | 6    | -              | -                | GNDIO6                                | 6    | -              | -                |

| L5             | PL38A                                 | 6    | Т              | LLM0_PLLT_FB_A   | PL42A                                 | 6    | Т              | LLM0_PLLT_FB_A   |

| M6             | PL38B                                 | 6    | С              | LLM0_PLLC_FB_A   | PL42B                                 | 6    | С              | LLM0_PLLC_FB_A   |

| M3             | PL39A                                 | 6    | T <sup>3</sup> | -                | PL43A                                 | 6    | T <sup>3</sup> | -                |

| N3             | PL39B                                 | 6    | C <sup>3</sup> | -                | PL43B                                 | 6    | C <sup>3</sup> | -                |

| -              | GNDIO6                                | 6    | -              | -                | GNDIO6                                | 6    | -              | -                |

| P4             | SLEEPN <sup>1</sup> /TOE <sup>2</sup> | -    | -              | -                | SLEEPN <sup>1</sup> /TOE <sup>2</sup> | -    | -              | -                |

| P3             | INITN                                 | 5    | -              | -                | INITN                                 | 5    | -              | -                |

| -              | GNDIO5                                | 5    | -              | -                | GNDIO5                                | 5    | -              | -                |

| -              | GNDIO5                                | 5    | -              | -                | GNDIO5                                | 5    | -              | -                |

| -              | GNDIO5                                | 5    | -              | -                | GNDIO5                                | 5    | -              | -                |

| R4             | PB11A                                 | 5    | Т              | -                | PB15A                                 | 5    | Т              | -                |

| N5             | PB11B                                 | 5    | С              | -                | PB15B                                 | 5    | С              | -                |

| P5             | PB12A                                 | 5    | Т              | VREF1_5          | PB16A                                 | 5    | Т              | VREF1_5          |

| -              | GNDIO5                                | 5    | -              | -                | GNDIO5                                | 5    | -              | -                |

| R1             | PB12B                                 | 5    | С              | -                | PB16B                                 | 5    | С              | -                |

| N6             | PB13A                                 | 5    | -              | -                | PB17A                                 | 5    | -              | -                |

| M7             | PB14B                                 | 5    | -              | -                | PB18B                                 | 5    | -              | -                |

| R2             | PB15A                                 | 5    | Т              | DQS              | PB19A                                 | 5    | Т              | DQS              |

| T2             | PB15B                                 | 5    | С              | -                | PB19B                                 | 5    | С              | -                |

| R3             | PB16A                                 | 5    | Т              | -                | PB20A                                 | 5    | Т              | -                |

| Т3             | PB16B                                 | 5    | С              | -                | PB20B                                 | 5    | С              | -                |

| T4             | PB17A                                 | 5    | Т              | -                | PB21A                                 | 5    | Т              | -                |

| R5             | PB17B                                 | 5    | С              | VREF2_5          | PB21B                                 | 5    | С              | VREF2_5          |

| N7             | PB18A                                 | 5    | Т              | -                | PB22A                                 | 5    | Т              | -                |

| -              | GNDIO5                                | 5    | -              | -                | GNDIO5                                | 5    | -              | -                |

| M8             | PB18B                                 | 5    | С              | -                | PB22B                                 | 5    | С              | -                |

| T5             | PB19A                                 | 5    | Т              | -                | PB23A                                 | 5    | Т              | -                |

| P6             | PB19B                                 | 5    | С              | -                | PB23B                                 | 5    | С              | -                |

| T6             | PB20A                                 | 5    | Т              | -                | PB24A                                 | 5    | Т              | -                |

| R6             | PB20B                                 | 5    | С              | -                | PB24B                                 | 5    | С              | -                |

| P7             | PB21A                                 | 5    | -              | -                | PB25A                                 | 5    | -              | -                |

| N8             | PB22B                                 | 5    | -              | -                | PB26B                                 | 5    | -              | -                |

| R7             | PB23A                                 | 5    | Т              | DQS              | PB27A                                 | 5    | Т              | DQS              |

|                |                  |      | LFXP15       |                  | LFXP20           |      |              |                  |

|----------------|------------------|------|--------------|------------------|------------------|------|--------------|------------------|

| Ball<br>Number | Ball<br>Function | Bank | Differential | Dual<br>Function | Ball<br>Function | Bank | Differential | Dual<br>Function |

| T7             | PB23B            | 5    | С            | -                | PB27B            | 5    | С            | -                |

| -              | GNDIO5           | 5    | -            | -                | GNDIO5           | 5    | -            | -                |

| P8             | PB24A            | 5    | Т            | -                | PB28A            | 5    | Т            | -                |

| T8             | PB24B            | 5    | С            | -                | PB28B            | 5    | С            | -                |

| R8             | PB25A            | 5    | Т            | -                | PB29A            | 5    | Т            | -                |

| Т9             | PB25B            | 5    | С            | -                | PB29B            | 5    | С            | -                |

| R9             | PB26A            | 4    | Т            | -                | PB30A            | 4    | Т            | -                |

| P9             | PB26B            | 4    | С            | -                | PB30B            | 4    | С            | -                |

| T10            | PB27A            | 4    | Т            | PCLKT4_0         | PB31A            | 4    | Т            | PCLKT4_0         |

| T11            | PB27B            | 4    | С            | PCLKC4_0         | PB31B            | 4    | С            | PCLKC4_0         |

| -              | GNDIO4           | 4    | -            | -                | GNDIO4           | 4    | -            | -                |

| R10            | PB28A            | 4    | Т            | -                | PB32A            | 4    | Т            | -                |

| P10            | PB28B            | 4    | С            | -                | PB32B            | 4    | С            | -                |

| N9             | PB29A            | 4    | -            | -                | PB33A            | 4    | -            | -                |

| M9             | PB30B            | 4    | -            | -                | PB34B            | 4    | -            | -                |

| R12            | PB31A            | 4    | Т            | DQS              | PB35A            | 4    | Т            | DQS              |

| T12            | PB31B            | 4    | С            | VREF1_4          | PB35B            | 4    | С            | VREF1_4          |

| P13            | PB32A            | 4    | Т            | -                | PB36A            | 4    | Т            | -                |

| R13            | PB32B            | 4    | С            | -                | PB36B            | 4    | С            | -                |

| M11            | PB33A            | 4    | Т            | -                | PB37A            | 4    | Т            | -                |

| -              | GNDIO4           | 4    | -            | -                | GNDIO4           | 4    | -            | -                |

| N11            | PB33B            | 4    | С            | -                | PB37B            | 4    | С            | -                |

| N10            | PB34A            | 4    | Т            | -                | PB38A            | 4    | Т            | -                |

| M10            | PB34B            | 4    | С            | -                | PB38B            | 4    | С            | -                |

| T13            | PB35A            | 4    | Т            | -                | PB39A            | 4    | Т            | -                |

| P14            | PB35B            | 4    | С            | -                | PB39B            | 4    | С            | -                |

| R11            | PB36A            | 4    | Т            | VREF2_4          | PB40A            | 4    | Т            | VREF2_4          |

| P12            | PB36B            | 4    | С            | -                | PB40B            | 4    | С            | -                |

| T14            | PB37A            | 4    | -            | -                | PB41A            | 4    | -            | -                |

| R14            | PB38B            | 4    | -            | -                | PB42B            | 4    | -            | -                |

| -              | GNDIO4           | 4    | -            | -                | GNDIO4           | 4    | -            | -                |

| P11            | PB39A            | 4    | Т            | DQS              | PB43A            | 4    | Т            | DQS              |

| N12            | PB39B            | 4    | С            | -                | PB43B            | 4    | С            | -                |

| T15            | PB40A            | 4    | Т            | -                | PB44A            | 4    | Т            | -                |

| R15            | PB40B            | 4    | С            | -                | PB44B            | 4    | С            | -                |

| -              | GNDIO4           | 4    | -            | -                | GNDIO4           | 4    | -            | -                |

| -              | GNDIO4           | 4    | -            | -                | GNDIO4           | 4    | -            | -                |

| -              | GNDIO4           | 4    | -            | -                | GNDIO4           | 4    | -            | -                |

| -              | GNDIO3           | 3    | -            | -                | GNDIO3           | 3    | -            | -                |

| -              | GNDIO3           | 3    | -            | -                | GNDIO3           | 3    | -            | -                |

| P15            | PR38B            | 3    | С            | RLM0_PLLC_FB_A   | PR42B            | 3    | С            | RLM0_PLLC_FB_/   |

| N15            | PR38A            | 3    | T            | RLM0_PLLT_FB_A   | PR42A            | 3    | T            | RLM0_PLLT_FB_A   |

|                |                  |      | LFXP15       |                  |                  | LFXP20 |              |                  |  |  |  |

|----------------|------------------|------|--------------|------------------|------------------|--------|--------------|------------------|--|--|--|

| Ball<br>Number | Ball<br>Function | Bank | Differential | Dual<br>Function | Ball<br>Function | Bank   | Differential | Dual<br>Function |  |  |  |

| G10            | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| G7             | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| G8             | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| G9             | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| H10            | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| H7             | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| H8             | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| H9             | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| J10            | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| J7             | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| J8             | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| J9             | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| K10            | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| K7             | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| K8             | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| K9             | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| L11            | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| <br>L6         | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| <br>T1         | GND              | -    | -            | -                | GND              | -      | -            |                  |  |  |  |

| T16            | GND              | -    | -            | -                | GND              | -      | -            | -                |  |  |  |

| D13            | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| D4             | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| E12            | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| E5             | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| M12            | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| M5             | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| N13            | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| N4             | VCC              | -    | -            | -                | VCC              | -      | -            | -                |  |  |  |

| E13            | VCCAUX           | -    | _            | _                | VCCAUX           | -      | _            | -                |  |  |  |

| E4             | VCCAUX           | -    | _            |                  | VCCAUX           | -      | _            |                  |  |  |  |

| M13            | VCCAUX           | -    | -            | -                | VCCAUX           | -      | -            | -                |  |  |  |

| M10<br>M4      | VCCAUX           | -    | _            | -                | VCCAUX           | -      | -            | -                |  |  |  |

| F7             | VCCIO0           | 0    | -            | -                | VCCIO0           | 0      |              |                  |  |  |  |

| F8             | VCCIO0           | 0    | -            | -                | VCCIO0           | 0      | -            | -                |  |  |  |

| F10            | VCCIO1           | 1    | _            | -                | VCCIO1           | 1      | -            | -                |  |  |  |

| F9             | VCCIO1           | 1    | -            | -                | VCCIO1           | 1      |              | -                |  |  |  |

| G11            | VCCIO1           | 2    | -            | -                | VCCIO1<br>VCCIO2 | 2      | -            | -                |  |  |  |

| H11            | VCCIO2<br>VCCIO2 | 2    | -            | -                | VCCIO2<br>VCCIO2 | 2      | -            | -                |  |  |  |

| J11            | VCCIO2<br>VCCIO3 | 3    | -            | -                | VCCIO2<br>VCCIO3 | 3      |              |                  |  |  |  |

| K11            | VCCIO3           | 3    | -            | -                | VCCIO3           | 3      | -            | -                |  |  |  |

| L10            | VCCIO3           | 4    | -            | -                | VCCIO3<br>VCCIO4 | 4      | -            | -                |  |  |  |

|                |                  |      |              |                  |                  |        | -            | -                |  |  |  |

| L9             | VCCIO4           | 4    | -            | -                | VCCIO4           | 4      | -            | -                |  |  |  |

|                |                  |      | LFXP15       |                  | LFXP20           |      |              |                  |  |  |

|----------------|------------------|------|--------------|------------------|------------------|------|--------------|------------------|--|--|

| Ball<br>Number | Ball<br>Function | Bank | Differential | Dual<br>Function | Ball<br>Function | Bank | Differential | Dual<br>Function |  |  |

| L7             | VCCIO5           | 5    | -            | -                | VCCIO5           | 5    | -            | -                |  |  |

| L8             | VCCIO5           | 5    | -            | -                | VCCIO5           | 5    | -            | -                |  |  |

| J6             | VCCIO6           | 6    | -            | -                | VCCIO6           | 6    | -            | -                |  |  |

| K6             | VCCIO6           | 6    | -            | -                | VCCIO6           | 6    | -            | -                |  |  |

| G6             | VCCIO7           | 7    | -            | -                | VCCI07           | 7    | -            | -                |  |  |

| H6             | VCCIO7           | 7    | -            | -                | VCCI07           | 7    | -            | -                |  |  |

Applies to LFXP "C" only.

Applies to LFXP "E" only.

3. Supports dedicated LVDS outputs.

## **Thermal Management**

Thermal management is recommended as part of any sound FPGA design methodology. To assess the thermal characteristics of a system, Lattice specifies a maximum allowable junction temperature in all device data sheets. Designers must complete a thermal analysis of their specific design to ensure that the device and package do not exceed the junction temperature limits. Refer to the Thermal Management document to find the device/package specific thermal values.

### For Further Information

For further information regarding Thermal Management, refer to the following located on the Lattice website at <u>www.latticesemi.com</u>.

- Thermal Management document

- Technical Note TN1052 Power Estimation and Management for LatticeECP/EC and LatticeXP Devices

- Power Calculator tool included with Lattice's ispLEVER design tool, or as a standalone download from

<u>www.latticesemi.com/software</u>

| Part Number     | I/Os | Voltage      | Grade | Package | Pins | Temp. | LUTs |  |  |

|-----------------|------|--------------|-------|---------|------|-------|------|--|--|

| LFXP10C-3FN388I | 244  | 1.8/2.5/3.3V | -3    | fpBGA   | 388  | IND   | 9.7K |  |  |

| LFXP10C-4FN388I | 244  | 1.8/2.5/3.3V | -4    | fpBGA   | 388  | IND   | 9.7K |  |  |

| LFXP10C-3FN256I | 188  | 1.8/2.5/3.3V | -3    | fpBGA   | 256  | IND   | 9.7K |  |  |

| LFXP10C-4FN256I | 188  | 1.8/2.5/3.3V | -4    | fpBGA   | 256  | IND   | 9.7K |  |  |

### Industrial (Cont.)

| Part Number     | l/Os | Voltage      | Grade | Package | Pins | Temp. | LUTs  |

|-----------------|------|--------------|-------|---------|------|-------|-------|

| LFXP15C-3FN484I | 300  | 1.8/2.5/3.3V | -3    | fpBGA   | 484  | IND   | 15.5K |

| LFXP15C-4FN484I | 300  | 1.8/2.5/3.3V | -4    | fpBGA   | 484  | IND   | 15.5K |

| LFXP15C-3FN388I | 268  | 1.8/2.5/3.3V | -3    | fpBGA   | 388  | IND   | 15.5K |

| LFXP15C-4FN388I | 268  | 1.8/2.5/3.3V | -4    | fpBGA   | 388  | IND   | 15.5K |

| LFXP15C-3FN256I | 188  | 1.8/2.5/3.3V | -3    | fpBGA   | 256  | IND   | 15.5K |

| LFXP15C-4FN256I | 188  | 1.8/2.5/3.3V | -4    | fpBGA   | 256  | IND   | 15.5K |

| Part Number     | l/Os | Voltage      | Grade | Package | Pins | Temp. | LUTs  |

|-----------------|------|--------------|-------|---------|------|-------|-------|

| LFXP20C-3FN484I | 340  | 1.8/2.5/3.3V | -3    | fpBGA   | 484  | IND   | 19.7K |

| LFXP20C-4FN484I | 340  | 1.8/2.5/3.3V | -4    | fpBGA   | 484  | IND   | 19.7K |

| LFXP20C-3FN388I | 268  | 1.8/2.5/3.3V | -3    | fpBGA   | 388  | IND   | 19.7K |

| LFXP20C-4FN388I | 268  | 1.8/2.5/3.3V | -4    | fpBGA   | 388  | IND   | 19.7K |

| LFXP20C-3FN256I | 188  | 1.8/2.5/3.3V | -3    | fpBGA   | 256  | IND   | 19.7K |

| LFXP20C-4FN256I | 188  | 1.8/2.5/3.3V | -4    | fpBGA   | 256  | IND   | 19.7K |

| Part Number    | I/Os | Voltage | Grade | Package | Pins | Temp. | LUTs |

|----------------|------|---------|-------|---------|------|-------|------|

| LFXP3E-3QN208I | 136  | 1.2V    | -3    | PQFP    | 208  | IND   | 3.1K |

| LFXP3E-4QN208I | 136  | 1.2V    | -4    | PQFP    | 208  | IND   | 3.1K |

| LFXP3E-3TN144I | 100  | 1.2V    | -3    | TQFP    | 144  | IND   | 3.1K |

| LFXP3E-4TN144I | 100  | 1.2V    | -4    | TQFP    | 144  | IND   | 3.1K |

| LFXP3E-3TN100I | 62   | 1.2V    | -3    | TQFP    | 100  | IND   | 3.1K |

| LFXP3E-4TN100I | 62   | 1.2V    | -4    | TQFP    | 100  | IND   | 3.1K |

| Part Number    | I/Os | Voltage | Grade | Package | Pins | Temp. | LUTs |

|----------------|------|---------|-------|---------|------|-------|------|

| LFXP6E-3FN256I | 188  | 1.2V    | -3    | fpBGA   | 256  | IND   | 5.8K |

| LFXP6E-4FN256I | 188  | 1.2V    | -4    | fpBGA   | 256  | IND   | 5.8K |

| LFXP6E-3QN208I | 142  | 1.2V    | -3    | PQFP    | 208  | IND   | 5.8K |

| LFXP6E-4QN208I | 142  | 1.2V    | -4    | PQFP    | 208  | IND   | 5.8K |

| LFXP6E-3TN144I | 100  | 1.2V    | -3    | TQFP    | 144  | IND   | 5.8K |

| LFXP6E-4TN144I | 100  | 1.2V    | -4    | TQFP    | 144  | IND   | 5.8K |