Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                                  |

|--------------------------------|---------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | 6000                                                                      |

| Total RAM Bits                 | 73728                                                                     |

| Number of I/O                  | 188                                                                       |

| Number of Gates                | -                                                                         |

| Voltage - Supply               | 1.14V ~ 1.26V                                                             |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                           |

| Package / Case                 | 256-BGA                                                                   |

| Supplier Device Package        | 256-FPBGA (17x17)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfxp6e-5fn256c |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

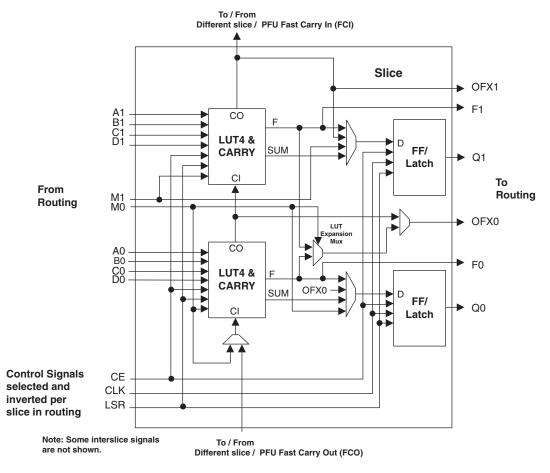

### Slice

Each slice contains two LUT4 lookup tables feeding two registers (programmed to be in FF or Latch mode), and some associated logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/asynchronous), clock select, chip-select and wider RAM/ROM functions. Figure 2-3 shows an overview of the internal logic of the slice. The registers in the slice can be configured for positive/negative and edge/level clocks.

There are 14 input signals: 13 signals from routing and one from the carry-chain (from adjacent slice or PFU). There are 7 outputs: 6 to routing and one to carry-chain (to adjacent PFU). Table 2-1 lists the signals associated with each slice.

### Figure 2-3. Slice Diagram

## Lattice Semiconductor

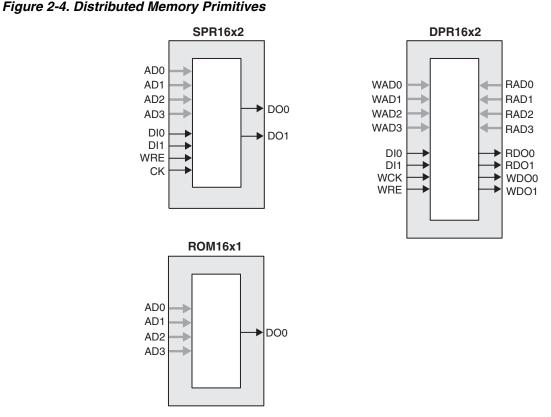

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of Slices required to implement different distributed RAM primitives. Figure 2-4 shows the distributed memory primitive block diagrams. Dual port memories involve the pairing of two Slices, one Slice functions as the read-write port. The other companion Slice supports the read-only port. For more information on RAM mode in LatticeXP devices, please see details of additional technical documentation at the end of this data sheet.

### Table 2-3. Number of Slices Required for Implementing Distributed RAM

|                            | SPR16x2       | DPR16x2  |

|----------------------------|---------------|----------|

| Number of Slices           | 1             | 2        |

| Note: SPR = Single Port RA | M, DPR = Dual | Port RAM |

| <br>District of Manager |  |

|-------------------------|--|

|                         |  |

|                         |  |

**ROM Mode:** The ROM mode uses the same principal as the RAM modes, but without the Write port. Pre-loading is accomplished through the programming interface during configuration.

### **PFU Modes of Operation**

Slices can be combined within a PFU to form larger functions. Table 2-4 tabulates these modes and documents the functionality possible at the PFU level.

### Lattice Semiconductor

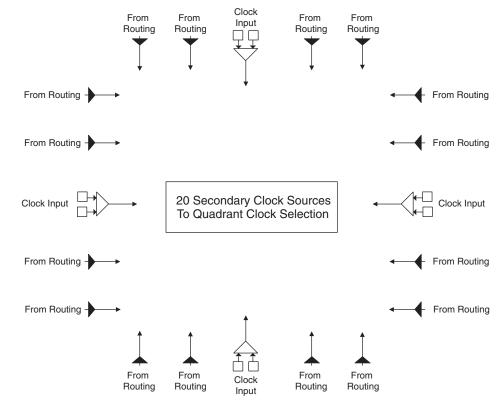

### Figure 2-6. Secondary Clock Sources

### **Clock Routing**

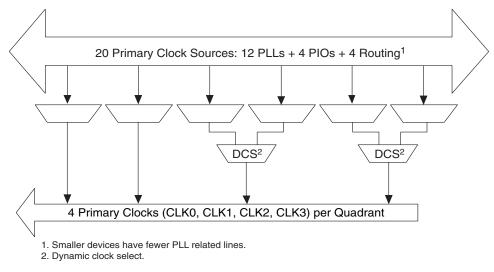

The clock routing structure in LatticeXP devices consists of four Primary Clock lines and a Secondary Clock network per quadrant. The primary clocks are generated from MUXs located in each quadrant. Figure 2-7 shows this clock routing. The four secondary clocks are generated from MUXs located in each quadrant as shown in Figure 2-8. Each slice derives its clock from the primary clock lines, secondary clock lines and routing as shown in Figure 2-9.

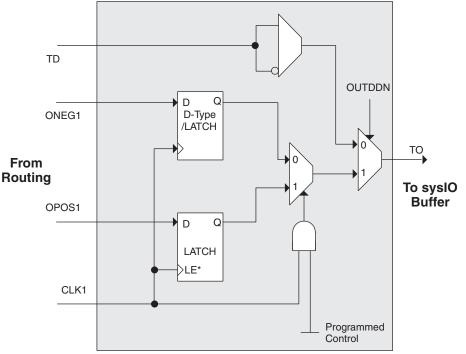

Figure 2-25. Tristate Register Block

\*Latch is transparent when input is low.

### Control Logic Block

The control logic block allows the selection and modification of control signals for use in the PIO block. A clock is selected from one of the clock signals provided from the general purpose routing and a DQS signal provided from the programmable DQS pin. The clock can optionally be inverted.

The clock enable and local reset signals are selected from the routing and optionally inverted. The global tristate signal is passed through this block.

# DDR Memory Support

Implementing high performance DDR memory interfaces requires dedicated DDR register structures in the input (for read operations) and in the output (for write operations). As indicated in the PIO Logic section, the LatticeXP devices provide this capability. In addition to these registers, the LatticeXP devices contain two elements to simplify the design of input structures for read operations: the DQS delay block and polarity control logic.

## DLL Calibrated DQS Delay Block

Source Synchronous interfaces generally require the input clock to be adjusted in order to correctly capture data at the input register. For most interfaces a PLL is used for this adjustment, however in DDR memories the clock (referred to as DQS) is not free running so this approach cannot be used. The DQS Delay block provides the required clock alignment for DDR memory interfaces.

The DQS signal (selected PIOs only) feeds from the PAD through a DQS delay element to a dedicated DQS routing resource. The DQS signal also feeds the polarity control logic which controls the polarity of the clock to the sync registers in the input register blocks. Figures 2-26 and 2-27 show how the polarity control logic are routed to the PIOs.

The temperature, voltage and process variations of the DQS delay block are compensated by a set of calibration (6-bit bus) signals from two DLLs on opposite sides of the device. Each DLL compensates DQS Delays in its half of the device as shown in Figure 2-27. The DLL loop is compensated for temperature, voltage and process variations by the system clock and feedback loop.

| Characteristic                  | Normal         | Off             | Sleep           |

|---------------------------------|----------------|-----------------|-----------------|

| SLEEPN Pin                      | High           | —               | Low             |

| Static Icc                      | Typical <100mA | 0               | Typical <100uA  |

| I/O Leakage                     | <10µA          | <1mA            | <10µA           |

| Power Supplies VCC/VCCIO/VCCAUX | Normal Range   | Off             | Normal Range    |

| Logic Operation                 | User Defined   | Non Operational | Non operational |

| I/O Operation                   | User Defined   | Tri-state       | Tri-state       |

| JTAG and Programming circuitry  | Operational    | Non-operational | Non-operational |

| EBR Contents and Registers      | Maintained     | Non-maintained  | Non-maintained  |

Table 2-9. Characteristics of Normal, Off and Sleep Modes

## **SLEEPN Pin Characteristics**

The SLEEPN pin behaves as an LVCMOS input with the voltage standard appropriate to the VCC supply for the device. This pin also has a weak pull-up typically in the order of  $10\mu$ A along with a Schmidt trigger and glitch filter to prevent false triggering. An external pull-up to V<sub>CC</sub> is recommended when Sleep Mode is not used to ensure the device stays in normal operation mode. Typically the device enters Sleep Mode several hundred ns after SLEEPN is held at a valid low and restarts normal operation as specified in the Sleep Mode Timing table. The AC and DC specifications portion of this data sheet show a detailed timing diagram.

## **Configuration and Testing**

The following section describes the configuration and testing features of the LatticeXP family of devices.

## IEEE 1149.1-Compliant Boundary Scan Testability

All LatticeXP devices have boundary scan cells that are accessed through an IEEE 1149.1 compliant test access port (TAP). This allows functional testing of the circuit board, on which the device is mounted, through a serial scan path that can access all critical logic nodes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test data to be captured and shifted out for verification. The test access port consists of dedicated I/Os: TDI, TDO, TCK and TMS. The test access port has its own supply voltage V<sub>CCJ</sub> and can operate with LVCMOS3.3, 2.5, 1.8, 1.5 and 1.2 standards.

For more details on boundary scan test, please see information regarding additional technical documentation at the end of this data sheet.

## **Device Configuration**

All LatticeXP devices contain two possible ports that can be used for device configuration and programming. The test access port (TAP), which supports serial configuration, and the sysCONFIG port that supports both byte-wide and serial configuration.

The non-volatile memory in the LatticeXP can be configured in three different modes:

- In sysCONFIG mode via the sysCONFIG port. Note this can also be done in background mode.

- In 1532 mode via the 1149.1 port.

- In background mode via the 1149.1 port. This allows the device to be operated while reprogramming takes place.

The SRAM configuration memory can be configured in three different ways:

- At power-up via the on-chip non-volatile memory.

- In 1532 mode via the 1149.1 port SRAM direct configuration.

- In sysCONFIG mode via the sysCONFIG port SRAM direct configuration.

# **DC Electrical Characteristics**

| Symbol                                              | Parameter                                | Condition                                  | Min.                  | Тур. | Max.                  | Units |

|-----------------------------------------------------|------------------------------------------|--------------------------------------------|-----------------------|------|-----------------------|-------|

| I <sub>IL,</sub> I <sub>IH</sub> <sup>1, 2, 4</sup> | Input or I/O Leakage                     | $0 \le V_{IN} \le (V_{CCIO} - 0.2V)$       | —                     | _    | 10                    | μA    |

| 'IL, 'IH                                            | Input of I/O Leakage                     | $(V_{CCIO} - 0.2V) < V_{IN} \le 3.6V$      | —                     | _    | 40                    | μA    |

| I <sub>PU</sub>                                     | I/O Active Pull-up Current               | $0 \le V_{IN} \le 0.7 V_{CCIO}$            | -30                   | _    | -150                  | μA    |

| I <sub>PD</sub>                                     | I/O Active Pull-down Current             | $V_{IL} (MAX) \le V_{IN} \le V_{IH} (MAX)$ | 30                    | _    | 150                   | μA    |

| I <sub>BHLS</sub>                                   | Bus Hold Low sustaining current          | $V_{IN} = V_{IL}$ (MAX)                    | 30                    | _    | —                     | μA    |

| I <sub>BHHS</sub>                                   | Bus Hold High sustaining current         | $V_{IN} = 0.7 V_{CCIO}$                    | -30                   | _    | —                     | μA    |

| I <sub>BHLO</sub>                                   | Bus Hold Low Overdrive current           | $0 \le V_{IN} \le V_{IH}$ (MAX)            |                       | _    | 150                   | μΑ    |

| I <sub>BHHO</sub>                                   | Bus Hold High Overdrive current          | $0 \le V_{IN} \le V_{IH}$ (MAX)            | —                     | _    | -150                  | μA    |

| V <sub>BHT</sub>                                    | Bus Hold trip Points                     | $0 \le V_{IN} \le V_{IH}$ (MAX)            | V <sub>IL</sub> (MAX) | _    | V <sub>IH</sub> (MIN) | V     |

| C1                                                  | I/O Capacitance <sup>3</sup>             |                                            | —                     | 8    | —                     | pf    |

| C2                                                  | Dedicated Input Capacitance <sup>3</sup> |                                            | —                     | 8    | —                     | pf    |

### **Over Recommended Operating Conditions**

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

2. Not applicable to SLEEPN/TOE pin.

3. T<sub>A</sub> 25°C, f = 1.0MHz

4. When V<sub>IH</sub> is higher than V<sub>CCIO</sub>, a transient current typically of 30ns in duration or less with a peak current of 6mA can be expected on the high-to-low transition.

# Supply Current (Sleep Mode)<sup>1, 2, 3</sup>

| Symbol             | Parameter                  | Device               | Typ.⁴ | Max | Units |

|--------------------|----------------------------|----------------------|-------|-----|-------|

|                    |                            | LFXP3C               | 12    | 65  | μA    |

|                    |                            | LFXP6C               | 14    | 75  | μA    |

| I <sub>CC</sub>    | Core Power Supply          | LFXP10C              | 16    | 85  | μΑ    |

|                    |                            | LFXP15C              | 18    | 95  | μΑ    |

|                    |                            | LFXP20C              | 20    | 105 | μA    |

| I <sub>CCP</sub>   | PLL Power Supply (per PLL) | All LFXP 'C' Devices | 1     | 5   | μA    |

|                    |                            | LFXP3C               | 2     | 90  | μA    |

|                    |                            | LFXP6C               | 2     | 100 | μA    |

| I <sub>CCAUX</sub> | Auxiliary Power Supply     | LFXP10C              | 2     | 110 | μA    |

|                    |                            | LFXP15C              | 3     | 120 | μA    |

|                    |                            | LFXP20C              | 4     | 130 | μΑ    |

|                    |                            | LFXP3C               | 2     | 20  | μA    |

|                    |                            | LFXP6C               | 2     | 22  | μA    |

| Iccio              | Bank Power Supply⁵         | LFXP10C              | 2     | 24  | μΑ    |

|                    |                            | LFXP15C              | 3     | 27  | μΑ    |

|                    |                            | LFXP20C              | 4     | 30  | μA    |

| I <sub>CCJ</sub>   | VCCJ Power Supply          | All LFXP 'C' Devices | 1     | 5   | μA    |

1. Assumes all inputs are configured as LVCMOS and held at the VCCIO or GND.

2. Frequency 0MHz.

3. User pattern: blank.

4.  $T_A=25^{\circ}C$ , power supplies at nominal voltage.

5. Per bank.

# Initialization Supply Current<sup>1, 2, 3, 4, 5, 6</sup>

| Symbol             | Parameter                                           | Device    | Typ. <sup>7</sup> | Units |

|--------------------|-----------------------------------------------------|-----------|-------------------|-------|

|                    |                                                     | LFXP3E    | 40                | mA    |

|                    |                                                     | LFXP6E    | 50                | mA    |

|                    |                                                     | LFXP10E   | 110               | mA    |

|                    |                                                     | LFXP15E   | 140               | mA    |

|                    | Core Power Supply                                   | LFXP20E   | 250               | mA    |

| I <sub>CC</sub>    | Core Power Supply                                   | LFXP3C    | 60                | mA    |

|                    |                                                     | LFXP6C    | 70                | mA    |

|                    |                                                     | LFXP10C   | 150               | mA    |

|                    | Γ                                                   | LFXP15C   | 180               | mA    |

|                    |                                                     | LFXP20C   | 290               | mA    |

|                    |                                                     | LFXP3E/C  | 50                | mA    |

|                    |                                                     | LFXP6E/C  | 60                | mA    |

| I <sub>CCAUX</sub> | Auxiliary Power Supply<br>V <sub>CCAUX</sub> = 3.3V | LFXP10E/C | 90                | mA    |

|                    | CCAUX - 0.0V                                        | LFXP15 /C | 110               | mA    |

|                    |                                                     | LFXP20E/C | 130               | mA    |

| ICCJ               | V <sub>CCJ</sub> Power Supply                       | All       | 2                 | mA    |

### Over Recommended Operating Conditions

1. Until DONE signal is active.

2. For further information on supply current, please see details of additional technical documentation at the end of this data sheet.

3. Assumes all outputs are tristated, all inputs are configured as LVCMOS and held at the V<sub>CCIO</sub> or GND.

4. Frequency 0MHz.

5. Typical user pattern.

6. Assume normal bypass capacitor/decoupling capacitor across the supply.

7.  $T_A=25^{\circ}C$ , power supplies at nominal voltage.

# Programming and Erase Flash Supply Current<sup>1, 2, 3, 4, 5</sup>

| Symbol             | Parameter                                           | Device    | Тур.6 | Units |

|--------------------|-----------------------------------------------------|-----------|-------|-------|

|                    |                                                     | LFXP3E    | 30    | mA    |

|                    |                                                     | LFXP6E    | 40    | mA    |

|                    |                                                     | LFXP10E   | 50    | mA    |

|                    |                                                     | LFXP15E   | 60    | mA    |

|                    | Core Dower Supply                                   | LFXP20E   | 70    | mA    |

| Icc                | Core Power Supply                                   | LFXP3C    | 50    | mA    |

|                    |                                                     | LFXP6C    | 60    | mA    |

|                    |                                                     | LFXP10C   | 90    | mA    |

|                    |                                                     | LFXP15C   | 100   | mA    |

|                    |                                                     | LFXP20C   | 110   | mA    |

|                    |                                                     | LFXP3E/C  | 50    | mA    |

|                    |                                                     | LFXP6E/C  | 60    | mA    |

| I <sub>CCAUX</sub> | Auxiliary Power Supply<br>V <sub>CCAUX</sub> = 3.3V | LFXP10E/C | 90    | mA    |

|                    |                                                     | LFXP15E/C | 110   | mA    |

|                    |                                                     | LFXP20E/C | 130   | mA    |

| I <sub>CCJ</sub>   | V <sub>CCJ</sub> Power Supply <sup>7</sup>          | All       | 2     | mA    |

1. For further information on supply current, please see details of additional technical documentation at the end of this data sheet.

2. Assumes all outputs are tristated, all inputs are configured as LVCMOS and held at the  $V_{\mbox{CCIO}}$  or GND.

3. Blank user pattern; typical Flash pattern.

4. Bypass or decoupling capacitor across the supply.

5. JTAG programming is at 1MHz.

6.  $T_A=25^{\circ}C$ , power supplies at nominal voltage.

7. When programming via JTAG.

# sysIO Differential Electrical Characteristics LVDS

| Parameter<br>Symbol                | Parameter Description                          | Test Conditions                               | Min.                | Тур. | Max.  | Units |

|------------------------------------|------------------------------------------------|-----------------------------------------------|---------------------|------|-------|-------|

| V <sub>INP,</sub> V <sub>INM</sub> | Input Voltage                                  |                                               | 0                   | _    | 2.4   | V     |

| V <sub>THD</sub>                   | Differential Input Threshold                   |                                               | +/-100              | _    | _     | mV    |

|                                    |                                                | $100mV \le V_{THD}$                           | V <sub>THD</sub> /2 | 1.2  | 1.8   | V     |

| V <sub>CM</sub>                    | Input Common Mode Voltage                      | $200mV \le V_{THD}$                           | V <sub>THD</sub> /2 | 1.2  | 1.9   | V     |

|                                    |                                                | $350mV \le V_{THD}$                           | V <sub>THD</sub> /2 | 1.2  | 2.0   | V     |

| I <sub>IN</sub>                    | Input current                                  | Power on or power off                         |                     |      | +/-10 | μA    |

| V <sub>OH</sub>                    | Output high voltage for $V_{OP}$ or $V_{OM}$   | R <sub>T</sub> = 100 ohms                     | _                   | 1.38 | 1.60  | V     |

| V <sub>OL</sub>                    | Output low voltage for $V_{OP}$ or $V_{OM}$    | R <sub>T</sub> = 100 ohms                     | 0.9V                | 1.03 | —     | V     |

| V <sub>OD</sub>                    | Output voltage differential                    | $(V_{OP} - V_{OM}), R_T = 100 \text{ ohms}$   | 250                 | 350  | 450   | mV    |

| $\Delta V_{OD}$                    | Change in V <sub>OD</sub> between high and low |                                               | _                   | _    | 50    | mV    |

| V <sub>OS</sub>                    | Output voltage offset                          | $(V_{OP} - V_{OM})/2, R_T = 100 \text{ ohms}$ | 1.125               | 1.25 | 1.375 | V     |

| $\Delta V_{OS}$                    | Change in V <sub>OS</sub> between H and L      |                                               | —                   | _    | 50    | mV    |

| I <sub>OSD</sub>                   | Output short circuit current                   | V <sub>OD</sub> = 0V Driver outputs shorted   | _                   | _    | 6     | mA    |

### **Over Recommended Operating Conditions**

# LatticeXP External Switching Characteristics

|                       |                                                                   |                        | -     | 5    | -     | 4    | -     | 3    |          |

|-----------------------|-------------------------------------------------------------------|------------------------|-------|------|-------|------|-------|------|----------|

| Parameter             | Description                                                       | Device                 | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units    |

| General I/C           | Pin Parameters (Using Primary Clock wit                           | hout PLL) <sup>1</sup> |       |      |       |      |       |      |          |

|                       |                                                                   | LFXP3                  |       | 5.12 |       | 6.12 | _     | 7.43 | ns       |

|                       |                                                                   | LFXP6                  | —     | 5.30 | —     | 6.34 | -     | 7.69 | ns       |

| t <sub>CO</sub>       | Clock to Output - PIO Output Register                             | LFXP10                 | _     | 5.52 |       | 6.60 | —     | 8.00 | ns       |

|                       |                                                                   | LFXP15                 | _     | 5.72 |       | 6.84 | —     | 8.29 | ns       |

|                       |                                                                   | LFXP20                 | —     | 5.97 | —     | 7.14 | -     | 8.65 | ns       |

|                       |                                                                   | LFXP3                  | -0.40 | —    | -0.28 | —    | -0.16 | —    | ns       |

|                       |                                                                   | LFXP6                  | -0.33 | —    | -0.32 | —    | -0.30 | —    | ns       |

| t <sub>SU</sub>       | Clock to Data Setup - PIO Input Register                          | LFXP10                 | -0.61 | —    | -0.71 | —    | -0.81 | —    | ns       |

|                       |                                                                   | LFXP15                 | -0.71 |      | -0.77 | _    | -0.87 | _    | ns       |

|                       |                                                                   | LFXP20                 | -0.95 |      | -1.14 | _    | -1.35 | _    | ns       |

|                       |                                                                   | LFXP3                  | 2.10  |      | 2.50  | _    | 2.98  | _    | ns       |

|                       |                                                                   | LFXP6                  | 2.28  | _    | 2.72  | —    | 3.24  | —    | ns       |

| t <sub>H</sub>        | Clock to Data Hold - PIO Input Register                           | LFXP10                 | 3.02  | _    | 3.51  | —    | 3.71  | —    | ns       |

|                       |                                                                   | LFXP15                 | 2.70  |      | 3.22  | —    | 3.85  | —    | ns       |

|                       |                                                                   | LFXP20                 | 2.95  | _    | 3.52  | —    | 4.21  | _    | ns       |

|                       |                                                                   | LFXP3                  | 2.38  |      | 2.49  | —    | 2.66  | —    | ns       |

|                       |                                                                   | LFXP6                  | 2.92  |      | 3.18  | —    | 3.42  | —    | ns       |

| t <sub>SU_DEL</sub>   | Clock to Data Setup - PIO Input Register<br>with Input Data Delay | LFXP10                 | 2.72  | _    | 2.75  | —    | 2.84  | _    | ns       |

|                       | with input Data Delay                                             | LFXP15                 | 2.99  |      | 3.13  | —    | 3.18  | —    | ns       |

|                       |                                                                   | LFXP20                 | 4.47  | _    | 4.56  | —    | 4.80  | —    | ns       |

|                       |                                                                   | LFXP3                  | -0.70 | _    | -0.80 | —    | -0.92 | _    | ns       |

|                       |                                                                   | LFXP6                  | -0.47 |      | -0.38 | —    | -0.31 | —    | ns       |

| t <sub>H_DEL</sub>    | Clock to Data Hold - PIO Input Register with<br>Input Data Delay  | LFXP10                 | -0.60 |      | -0.47 | —    | -0.32 | —    | ns       |

|                       |                                                                   | LFXP15                 | -1.05 | —    | -0.98 | —    | -1.01 | _    | ns       |

|                       |                                                                   | LFXP20                 | -0.80 | _    | -0.58 | —    | -0.31 | _    | ns       |

| f <sub>MAX_IO</sub>   | Clock Frequency of I/O and PFU Register                           | All                    | —     | 400  | _     | 360  | —     | 320  | MHz      |

|                       | n Parameters <sup>2</sup>                                         |                        | I     | l    | l     | I    |       | l    | L        |

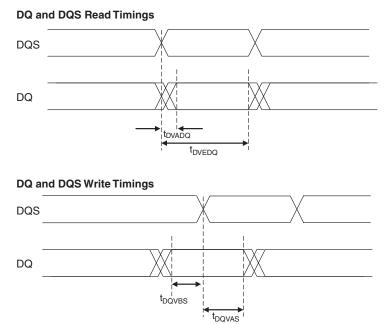

| t <sub>DVADQ</sub>    | Data Valid After DQS (DDR Read)                                   | All                    | _     | 0.19 |       | 0.19 | —     | 0.19 | UI       |

| t <sub>DVEDQ</sub>    | Data Hold After DQS (DDR Read)                                    | All                    | 0.67  |      | 0.67  | —    | 0.67  | —    | UI       |

| t <sub>DQVBS</sub>    | Data Valid Before DQS                                             | All                    | 0.20  | —    | 0.20  | —    | 0.20  | _    | UI       |

| t <sub>DQVAS</sub>    | Data Valid After DQS                                              | All                    | 0.20  |      | 0.20  |      | 0.20  | _    | UI       |

| f <sub>MAX_DDR</sub>  | DDR Clock Frequency                                               | All                    | 95    | 166  | 95    | 133  | 95    | 100  | MHz      |

|                       | nd Secondary Clocks                                               | 1                      | 1     | 1    | 1     | 1    | 1     | 1    | <u> </u> |

| f <sub>MAX_PRI</sub>  | Frequency for Primary Clock Tree                                  | All                    | —     | 450  | —     | 412  | —     | 375  | MHz      |

| t <sub>W_PRI</sub>    | Clock Pulse Width for Primary Clock                               | All                    | 1.19  | —    | 1.19  | —    | 1.19  | —    | ns       |

|                       |                                                                   | LFXP3/6/10/15          |       | 250  |       | 300  | —     | 350  | ps       |

| <sup>t</sup> SKEW_PRI | Primary Clock Skew within an I/O Bank                             | LFXP20                 |       | 300  |       | 350  | —     | 400  | ps       |

|                       |                                                                   | 1                      | 1     |      | 1     | 1    | 1     | 1    | 1        |

### **Over Recommended Operating Conditions**

1. General timing numbers based on LVCMOS 2.5, 12mA.

2. DDR timing numbers based on SSTL I/O.

Timing v.F0.11

### Figure 3-5. DDR Timings

## **Switching Test Conditions**

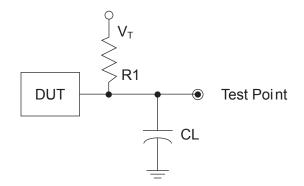

Figure 3-13 shows the output test load that is used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are shown in Figure 3-5.

### Figure 3-13. Output Test Load, LVTTL and LVCMOS Standards

Table 3-5. Test Fixture Required Components, Non-Terminated Interfaces

| Test Condition                                   | R <sub>1</sub> | CL  | Timing Ref.                       | V <sub>T</sub>  |

|--------------------------------------------------|----------------|-----|-----------------------------------|-----------------|

|                                                  |                |     | LVCMOS 3.3 = 1.5V                 | —               |

|                                                  |                |     | LVCMOS 2.5 = $V_{CCIO}/2$         | —               |

| LVTTL and other LVCMOS settings (L -> H, H -> L) | $\infty$       | 0pF | LVCMOS 1.8 = V <sub>CCIO</sub> /2 | —               |

|                                                  |                |     | LVCMOS 1.5 = $V_{CCIO}/2$         | —               |

|                                                  |                |     | LVCMOS 1.2 = $V_{CCIO}/2$         | —               |

| LVCMOS 2.5 I/O (Z -> H)                          |                |     | V <sub>CCIO</sub> /2              | V <sub>OL</sub> |

| LVCMOS 2.5 I/O (Z -> L)                          | 188            | 0pF | V <sub>CCIO</sub> /2              | V <sub>OH</sub> |

| LVCMOS 2.5 I/O (H -> Z)                          | 100            | opi | V <sub>OH</sub> - 0.15            | V <sub>OL</sub> |

| LVCMOS 2.5 I/O (L -> Z)                          |                |     | V <sub>OL</sub> + 0.15            | V <sub>OH</sub> |

Note: Output test conditions for all other interfaces are determined by the respective standards.

# PICs and DDR Data (DQ) Pins Associated with the DDR Strobe (DQS) Pin

| PICs Associated<br>with DQS Strobe | PIO within PIC | Polarity   | DDR Strobe (DQS)<br>and Data (DQ) Pins |

|------------------------------------|----------------|------------|----------------------------------------|

| D[Edge] [p. 4]                     | А              | True       | DQ                                     |

| P[Edge] [n-4]                      | В              | Complement | DQ                                     |

| D[Edgo] [n 2]                      | А              | True       | DQ                                     |

| P[Edge] [n-3]                      | В              | Complement | DQ                                     |

| P[Edge] [n-2]                      | А              | True       | DQ                                     |

|                                    | В              | Complement | DQ                                     |

| P[Edge] [n-1]                      | A              | True       | DQ                                     |

| P[Edge] [n]                        | В              | Complement | DQ                                     |

|                                    | A              | True       | [Edge]DQSn                             |

| P[Edge] [n+1]                      | В              | Complement | DQ                                     |

|                                    | А              | True       | DQ                                     |

| P[Edge] [n+2]                      | В              | Complement | DQ                                     |

| D[Edgo] [n , 2]                    | А              | True       | DQ                                     |

| P[Edge] [n+3]                      | В              | Complement | DQ                                     |

Notes:

1. "n" is a row/column PIC number.

2. The DDR interface is designed for memories that support one DQS strobe per eight bits of data. In some packages, all the potential DDR data (DQ) pins may not be available.

3. The definition of the PIC numbering is provided in the Signal Names column of the Signal Descriptions table in this data sheet.

# Pin Information Summary<sup>1</sup>

|                                         |           |          | XP3      |          | XP6      |          |           |  |

|-----------------------------------------|-----------|----------|----------|----------|----------|----------|-----------|--|

| Pin Type                                |           | 100 TQFP | 144 TQFP | 208 PQFP | 144 TQFP | 208 PQFP | 256 fpBGA |  |

| Single Ended User I/O                   |           | 62       | 100      | 136      | 100      | 142      | 188       |  |

| Differential Pair User I/O <sup>2</sup> |           | 19       | 35       | 56       | 35       | 58       | 80        |  |

| Configuration                           | Dedicated | 11       | 11       | 11       | 11       | 11       | 11        |  |

| Conliguration                           | Muxed     | 14       | 14       | 14       | 14       | 14       | 14        |  |

| ТАР                                     |           | 5        | 5        | 5        | 5        | 5        | 5         |  |

| Dedicated (total without s              | upplies)  | 6        | 6        | 6        | 6        | 6        | 6         |  |

| V <sub>CC</sub>                         |           | 2        | 4        | 8        | 4        | 8        | 8         |  |

| V <sub>CCAUX</sub>                      |           | 2        | 2        | 2        | 2        | 2        | 4         |  |

| V <sub>CCPLL</sub>                      |           | 2        | 2        | 2        | 2        | 2        | 2         |  |

|                                         | Bank0     | 1        | 1        | 2        | 1        | 2        | 2         |  |

|                                         | Bank1     | 1        | 1        | 2        | 1        | 2        | 2         |  |

|                                         | Bank2     | 1        | 1        | 2        | 1        | 2        | 2         |  |

| M                                       | Bank3     | 1        | 1        | 2        | 1        | 2        | 2         |  |

| V <sub>CCIO</sub>                       | Bank4     | 1        | 2        | 2        | 2        | 2        | 2         |  |

|                                         | Bank5     | 1        | 1        | 2        | 1        | 2        | 2         |  |

|                                         | Bank6     | 1        | 1        | 2        | 1        | 2        | 2         |  |

|                                         | Bank7     | 1        | 1        | 2        | 1        | 2        | 2         |  |

| GND                                     |           | 10       | 13       | 24       | 13       | 24       | 24        |  |

| GND <sub>PLL</sub>                      |           | 2        | 2        | 2        | 2        | 2        | 2         |  |

| NC                                      |           | 0        | 0        | 6        | 0        | 0        | 0         |  |

|                                         | Bank0     | 8/2      | 12/3     | 20/8     | 12/3     | 20/8     | 26/11     |  |

|                                         | Bank1     | 9/0      | 12/2     | 18/6     | 12/2     | 18/6     | 26/11     |  |

|                                         | Bank2     | 8/3      | 12/5     | 14/6     | 12/5     | 17/7     | 21/9      |  |

| Single Ended/Differential               | Bank3     | 6/2      | 13/5     | 14/6     | 13/5     | 14/6     | 21/9      |  |

| I/O per Bank <sup>2</sup>               | Bank4     | 5/2      | 14/6     | 21/9     | 14/6     | 21/9     | 26/11     |  |

|                                         | Bank5     | 12/4     | 12/4     | 21/9     | 12/4     | 21/9     | 26/11     |  |

|                                         | Bank6     | 4/2      | 13/5     | 14/6     | 13/5     | 17/7     | 21/9      |  |

|                                         | Bank7     | 10/4     | 12/5     | 14/6     | 12/5     | 14/6     | 21/9      |  |

| V <sub>CCJ</sub>                        | •         | 1        | 1        | 1        | 1        | 1        | 1         |  |

1. During configuration the user-programmable I/Os are tri-stated with an internal pull-up resistor enabled. If any pin is not used (or not bonded to a package pin), it is also tri-stated with an internal pull-up resistor enabled after configuration.

2. The differential I/O per bank includes both dedicated LVDS and emulated LVDS pin pairs. Please see the Logic Signal Connections table for more information.

# LFXP6 & LFXP10 Logic Signal Connections: 256 fpBGA (Cont.)

|                |                            |   | LFXP6        |                  | LFXP10           |      |              |                  |  |  |

|----------------|----------------------------|---|--------------|------------------|------------------|------|--------------|------------------|--|--|

| Ball<br>Number | Ball<br>Function Bank Diff |   | Differential | Dual<br>Function | Ball<br>Function | Bank | Differential | Dual<br>Function |  |  |

| E8             | PT13B                      | 0 | -            | -                | PT17B            | 0    | -            | -                |  |  |

| D8             | PT12A                      | 0 | -            | DOUT             | PT16A            | 0    | -            | DOUT             |  |  |

| A6             | PT11B                      | 0 | С            | -                | PT15B            | 0    | С            | -                |  |  |

| -              | GNDIO0                     | 0 | -            | -                | GNDIO0           | 0    | -            | -                |  |  |

| C6             | PT11A                      | 0 | Т            | WRITEN           | PT15A            | 0    | Т            | WRITEN           |  |  |

| E7             | PT10B                      | 0 | С            | -                | PT14B            | 0    | С            | -                |  |  |

| D7             | PT10A                      | 0 | Т            | VREF1_0          | PT14A            | 0    | Т            | VREF1_0          |  |  |

| A5             | PT9B                       | 0 | С            | -                | PT13B            | 0    | С            | -                |  |  |

| B5             | PT9A                       | 0 | Т            | DI               | PT13A            | 0    | Т            | DI               |  |  |

| A4             | PT8B                       | 0 | С            | -                | PT12B            | 0    | С            | -                |  |  |

| B6             | PT8A                       | 0 | Т            | CSN              | PT12A            | 0    | Т            | CSN              |  |  |

| E6             | PT7B                       | 0 | С            | -                | PT11B            | 0    | С            | -                |  |  |

| -              | GNDIO0                     | 0 | -            | -                | GNDIO0           | 0    | -            | -                |  |  |

| D6             | PT7A                       | 0 | Т            | -                | PT11A            | 0    | Т            | -                |  |  |

| D5             | PT6B                       | 0 | С            | VREF2_0          | PT10B            | 0    | С            | VREF2_0          |  |  |

| A3             | PT6A                       | 0 | Т            | DQS              | PT10A            | 0    | Т            | DQS              |  |  |

| B3             | PT5B                       | 0 | -            | -                | PT9B             | 0    | -            | -                |  |  |

| B2             | PT4A                       | 0 | -            | -                | PT8A             | 0    | -            | -                |  |  |

| A2             | PT3B                       | 0 | С            | -                | PT7B             | 0    | С            | -                |  |  |

| B1             | PT3A                       | 0 | Т            | -                | PT7A             | 0    | Т            | -                |  |  |

| F5             | PT2B                       | 0 | С            | -                | PT6B             | 0    | С            | -                |  |  |

| -              | GNDIO0                     | 0 | -            | -                | GNDIO0           | 0    | -            | -                |  |  |

| C5             | PT2A                       | 0 | Т            | -                | PT6A             | 0    | Т            | -                |  |  |

| C4             | CFG0                       | 0 | -            | -                | CFG0             | 0    | -            | -                |  |  |

| B4             | CFG1                       | 0 | -            | -                | CFG1             | 0    | -            | -                |  |  |

| C3             | DONE                       | 0 | -            | -                | DONE             | 0    | -            | -                |  |  |

| A1             | GND                        | - | -            | -                | GND              | -    | -            | -                |  |  |

| A16            | GND                        | - | -            | -                | GND              | -    | -            | -                |  |  |

| F11            | GND                        | - | -            | -                | GND              | -    | -            | -                |  |  |

| F6             | GND                        | - | -            | -                | GND              | -    | -            | -                |  |  |

| G10            | GND                        | - | -            | -                | GND              | -    | -            | -                |  |  |

| G7             | GND                        | - | -            | -                | GND              | -    | -            | -                |  |  |

| G8             | GND                        | - | -            | -                | GND              | -    | -            | -                |  |  |

| G9             | GND                        | - | -            | -                | GND              | -    | -            | -                |  |  |

| H10            | GND                        | - | -            | -                | GND              | -    | -            | -                |  |  |

| H7             | GND                        | - | -            | -                | GND              | -    | -            | -                |  |  |

| H8             | GND                        | - | -            | -                | GND              | -    | -            | -                |  |  |

| H9             | GND                        | - | -            | -                | GND              | -    | -            | -                |  |  |

| J10            | GND                        | - | -            | -                | GND              | -    | -            | -                |  |  |

| J7             | GND                        | - | -            | -                | GND              | -    | -            | -                |  |  |

| J8             | GND                        | - | -            | -                | GND              | -    | -            | -                |  |  |

| J9             | GND                        | - | -            | -                | GND              | -    | -            | -                |  |  |

# LFXP15 & LFXP20 Logic Signal Connections: 256 fpBGA (Cont.)

|                |                  |      | LFXP15       |                  | LFXP20           |      |              |                  |  |  |

|----------------|------------------|------|--------------|------------------|------------------|------|--------------|------------------|--|--|

| Ball<br>Number | Ball<br>Function | Bank | Differential | Dual<br>Function | Ball<br>Function | Bank | Differential | Dual<br>Function |  |  |

| G10            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| G7             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| G8             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| G9             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| H10            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| H7             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| H8             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| H9             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| J10            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| J7             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| J8             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| J9             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| K10            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| K7             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| K8             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| K9             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| L11            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| L6             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| T1             | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| T16            | GND              | -    | -            | -                | GND              | -    | -            | -                |  |  |

| D13            | VCC              | -    | -            | -                | VCC              | -    | -            | -                |  |  |

| D4             | VCC              | -    | -            | -                | VCC              | -    | -            | -                |  |  |

| E12            | VCC              | -    | -            | -                | VCC              | -    | -            | -                |  |  |

| E5             | VCC              | -    | -            | -                | VCC              | -    | -            | -                |  |  |

| M12            | VCC              | -    | -            | -                | VCC              | -    | -            | -                |  |  |

| M5             | VCC              | -    | -            | -                | VCC              | -    | -            | -                |  |  |

| N13            | VCC              | -    | -            | -                | VCC              | -    | -            | -                |  |  |

| N4             | VCC              | -    | -            | -                | VCC              | -    | -            | -                |  |  |

| E13            | VCCAUX           | -    | -            | -                | VCCAUX           | -    | -            | -                |  |  |

| E4             | VCCAUX           | -    | -            | -                | VCCAUX           | -    | -            | -                |  |  |

| M13            | VCCAUX           | -    | -            | -                | VCCAUX           | -    | -            | -                |  |  |

| M4             | VCCAUX           | -    | -            | -                | VCCAUX           | -    | -            | -                |  |  |

| F7             | VCCIO0           | 0    | -            | -                | VCCIO0           | 0    | -            | -                |  |  |

| F8             | VCCIO0           | 0    | -            | -                | VCCIO0           | 0    | -            | -                |  |  |

| F10            | VCCIO1           | 1    | -            | -                | VCCIO1           | 1    | -            | -                |  |  |

| F9             | VCCIO1           | 1    | -            | -                | VCCIO1           | 1    | -            | -                |  |  |

| G11            | VCCIO2           | 2    | -            | -                | VCCIO2           | 2    | -            | -                |  |  |

| H11            | VCCIO2           | 2    | -            | -                | VCCIO2           | 2    | -            | -                |  |  |

| J11            | VCCIO3           | 3    | -            | -                | VCCIO3           | 3    | -            | -                |  |  |

| K11            | VCCIO3           | 3    | -            | -                | VCCIO3           | 3    | -            | -                |  |  |

| L10            | VCCIO4           | 4    | -            | -                | VCCIO4           | 4    | -            | -                |  |  |

| L9             | VCCIO4           | 4    | -            | -                | VCCIO4           | 4    | - +          | -                |  |  |

# LFXP15 & LFXP20 Logic Signal Connections: 484 fpBGA (Cont.)

|                |                                           |   | LFXP15         |                  | LFXP20                                    |      |                |                  |  |  |

|----------------|-------------------------------------------|---|----------------|------------------|-------------------------------------------|------|----------------|------------------|--|--|

| Ball<br>Number | Ball<br>Function Bank                     |   | Differential   | Dual<br>Function | Ball<br>Function                          | Bank | Differential   | Dual<br>Function |  |  |

| T6             | PL41A                                     | 6 | Т              | -                | PL45A                                     | 6    | Т              | -                |  |  |

| T5             | PL41B                                     | 6 | С              | -                | PL45B                                     | 6    | С              | -                |  |  |

| -              | GNDIO6                                    | 6 | -              | -                | GNDIO6                                    | 6    | -              | -                |  |  |

| U3             | PL42A                                     | 6 | T <sup>3</sup> | -                | PL46A                                     | 6    | T <sup>3</sup> | -                |  |  |

| U4             | PL42B                                     | 6 | C <sup>3</sup> | -                | PL46B                                     | 6    | C <sup>3</sup> | -                |  |  |

| V4             | PL43A                                     | 6 | -              | -                | PL47A                                     | 6    | -              | -                |  |  |

| W4             | SLEEPN <sup>1</sup> /<br>TOE <sup>2</sup> | - | -              | -                | SLEEPN <sup>1</sup> /<br>TOE <sup>2</sup> | -    | -              | -                |  |  |

| W5             | INITN                                     | 5 | -              | -                | INITN                                     | 5    | -              | -                |  |  |

| Y3             | -                                         | - | -              | -                | PB3B                                      | 5    | -              | -                |  |  |

| -              | GNDIO5                                    | 5 | -              | -                | GNDIO5                                    | 5    | -              | -                |  |  |

| U5             | -                                         | - | -              | -                | PB4A                                      | 5    | Т              | -                |  |  |

| V5             | -                                         | - | -              | -                | PB4B                                      | 5    | С              | -                |  |  |

| Y4             | -                                         | - | -              | -                | PB5A                                      | 5    | Т              | -                |  |  |

| Y5             | -                                         | - | -              | -                | PB5B                                      | 5    | С              | -                |  |  |

| V6             | -                                         | - | -              | -                | PB6A                                      | 5    | Т              | -                |  |  |

| -              | GNDIO5                                    | 5 | -              | -                | GNDIO5                                    | 5    | -              | -                |  |  |

| U6             | -                                         | - | -              | -                | PB6B                                      | 5    | С              | -                |  |  |

| W6             | PB3A                                      | 5 | Т              | -                | PB7A                                      | 5    | Т              | -                |  |  |

| Y6             | PB3B                                      | 5 | С              | -                | PB7B                                      | 5    | С              | -                |  |  |

| AA2            | PB4A                                      | 5 | Т              | -                | PB8A                                      | 5    | Т              | -                |  |  |

| AA3            | PB4B                                      | 5 | С              | -                | PB8B                                      | 5    | С              | -                |  |  |

| V7             | PB5A                                      | 5 | -              | -                | PB9A                                      | 5    | -              | -                |  |  |

| U7             | PB6B                                      | 5 | -              | -                | PB10B                                     | 5    | -              | -                |  |  |

| Y7             | PB7A                                      | 5 | Т              | DQS              | PB11A                                     | 5    | Т              | DQS              |  |  |

| W7             | PB7B                                      | 5 | С              | -                | PB11B                                     | 5    | С              | -                |  |  |

| AA4            | PB8A                                      | 5 | Т              | -                | PB12A                                     | 5    | Т              | -                |  |  |

| -              | GNDIO5                                    | 5 | -              | -                | GNDIO5                                    | 5    | -              | -                |  |  |

| AA5            | PB8B                                      | 5 | С              | -                | PB12B                                     | 5    | С              | -                |  |  |

| AB3            | PB9A                                      | 5 | Т              | -                | PB13A                                     | 5    | Т              | -                |  |  |

| AB4            | PB9B                                      | 5 | С              | -                | PB13B                                     | 5    | С              | -                |  |  |

| AA6            | PB10A                                     | 5 | Т              | -                | PB14A                                     | 5    | Т              | -                |  |  |

| AA7            | PB10B                                     | 5 | С              | -                | PB14B                                     | 5    | С              | -                |  |  |

| U8             | PB11A                                     | 5 | Т              | -                | PB15A                                     | 5    | Т              | -                |  |  |

| V8             | PB11B                                     | 5 | С              | -                | PB15B                                     | 5    | С              | -                |  |  |

| Y8             | PB12A                                     | 5 | Т              | VREF1_5          | PB16A                                     | 5    | Т              | VREF1_5          |  |  |

| -              | GNDIO5                                    | 5 | -              | -                | GNDIO5                                    | 5    | -              | -                |  |  |

| W8             | PB12B                                     | 5 | С              | -                | PB16B                                     | 5    | С              | -                |  |  |

| V9             | PB13A                                     | 5 | -              | -                | PB17A                                     | 5    | -              | -                |  |  |

| U9             | PB14B                                     | 5 | -              | -                | PB18B                                     | 5    | -              | -                |  |  |

| Y9             | PB15A                                     | 5 | Т              | DQS              | PB19A                                     | 5    | Т              | DQS              |  |  |

| W9             | PB15B                                     | 5 | С              | -                | PB19B                                     | 5    | С              | -                |  |  |

# LFXP15 & LFXP20 Logic Signal Connections: 484 fpBGA (Cont.)

|                |                  |      | LFXP15                |                  |                  | LFXP20 |                |                  |  |  |  |

|----------------|------------------|------|-----------------------|------------------|------------------|--------|----------------|------------------|--|--|--|

| Ball<br>Number | Ball<br>Function | Bank | Differential          | Dual<br>Function | Ball<br>Function | Bank   | Differential   | Dual<br>Function |  |  |  |

| AB19           | PB37A            | 4    | -                     | -                | PB41A            | 4      | -              | -                |  |  |  |

| AB20           | PB38B            | 4    | -                     | -                | PB42B            | 4      | -              | -                |  |  |  |

| -              | GNDIO4           | 4    | -                     | -                | GNDIO4           | 4      | -              | -                |  |  |  |

| V15            | PB39A            | 4    | Т                     | DQS              | PB43A            | 4      | Т              | DQS              |  |  |  |

| U15            | PB39B            | 4    | С                     | -                | PB43B            | 4      | С              | -                |  |  |  |

| Y15            | PB40A            | 4    | Т                     | -                | PB44A            | 4      | Т              | -                |  |  |  |

| W15            | PB40B            | 4    | С                     | -                | PB44B            | 4      | С              | -                |  |  |  |

| AA16           | PB41A            | 4    | Т                     | -                | PB45A            | 4      | Т              | -                |  |  |  |

| AA17           | PB41B            | 4    | С                     | -                | PB45B            | 4      | С              | -                |  |  |  |

| AA18           | PB42A            | 4    | Т                     | -                | PB46A            | 4      | Т              | -                |  |  |  |

| AA19           | PB42B            | 4    | С                     | -                | PB46B            | 4      | С              | -                |  |  |  |

| Y16            | PB43A            | 4    | Т                     | -                | PB47A            | 4      | Т              | -                |  |  |  |

| W16            | PB43B            | 4    | С                     | -                | PB47B            | 4      | С              | -                |  |  |  |

| -              | GNDIO4           | 4    | -                     | -                | GNDIO4           | 4      | -              | -                |  |  |  |

| AA20           | PB44A            | 4    | Т                     | -                | PB48A            | 4      | Т              | -                |  |  |  |

| AA21           | PB44B            | 4    | С                     | -                | PB48B            | 4      | С              | -                |  |  |  |

| Y17            | PB45A            | 4    | -                     | -                | PB49A            | 4      | -              | -                |  |  |  |

| Y18            | PB46B            | 4    | -                     | -                | PB50B            | 4      | -              | -                |  |  |  |

| Y19            | PB47A            | 4    | Т                     | DQS              | PB51A            | 4      | Т              | DQS              |  |  |  |

| Y20            | PB47B            | 4    | С                     | -                | PB51B            | 4      | С              | -                |  |  |  |

| V16            | PB48A            | 4    | Т                     | -                | PB52A            | 4      | Т              | -                |  |  |  |

| U16            | PB48B            | 4    | С                     | -                | PB52B            | 4      | С              | -                |  |  |  |

| -              | GNDIO4           | 4    | -                     | -                | GNDIO4           | 4      | -              | -                |  |  |  |

| U18            | -                | -    | -                     | -                | PB53A            | 4      | Т              | -                |  |  |  |

| V18            | -                | -    | -                     | -                | PB53B            | 4      | С              | -                |  |  |  |

| W19            | -                | -    | -                     | -                | PB54A            | 4      | Т              | -                |  |  |  |

| W18            | -                | -    | -                     | -                | PB54B            | 4      | С              | -                |  |  |  |

| U17            | -                | -    | -                     | -                | PB55A            | 4      | Т              | -                |  |  |  |

| V17            | -                | -    | -                     | -                | PB55B            | 4      | С              | -                |  |  |  |

| -              | GNDIO4           | 4    | -                     | -                | GNDIO4           | 4      | -              | -                |  |  |  |

| W17            | -                | -    | -                     | -                | PB56A            | 4      | -              | -                |  |  |  |

| -              | GNDIO3           | 3    | -                     | -                | GNDIO3           | 3      | -              | -                |  |  |  |

| V19            | PR43A            | 3    | -                     | -                | PR47A            | 3      | -              | -                |  |  |  |

| U20            | PR42B            | 3    | C <sup>3</sup>        | -                | PR46B            | 3      | C <sup>3</sup> | -                |  |  |  |

| U19            | PR42A            | 3    | T <sup>3</sup>        | -                | PR46A            | 3      | T <sup>3</sup> | -                |  |  |  |

| V20            | PR41B            | 3    | С                     | -                | PR45B            | 3      | С              | -                |  |  |  |

| W20            | PR41A            | 3    | Т                     | -                | PR45A            | 3      | Т              | -                |  |  |  |

| T17            | PR40B            | 3    | C <sup>3</sup>        | -                | PR44B            | 3      | C <sup>3</sup> | -                |  |  |  |

| T18            | PR40A            | 3    | T <sup>3</sup>        | -                | PR44A            | 3      | T <sup>3</sup> | -                |  |  |  |

| T19            | PR39B            | 3    | <b>C</b> <sup>3</sup> | -                | PR43B            | 3      | C <sup>3</sup> | -                |  |  |  |

| T20            | PR39A            | 3    | T <sup>3</sup>        | -                | PR43A            | 3      | T <sup>3</sup> | -                |  |  |  |

| -              | GNDIO3           | 3    | -                     | -                | GNDIO3           | 3      | -              | -                |  |  |  |

## Lead-free Packaging

Commercial I/Os Part Number Voltage Grade Package Pins Temp. LUTs LFXP3C-3QN208C PQFP 136 1.8/2.5/3.3V -3 208 COM 3.1K LFXP3C-4QN208C 136 1.8/2.5/3.3V PQFP 208 COM -4 3.1K LFXP3C-5QN208C 136 -5 PQFP 208 COM 1.8/2.5/3.3V 3.1K LFXP3C-3TN144C COM 100 1.8/2.5/3.3V -3 TQFP 144 3.1K LFXP3C-4TN144C COM 100 1.8/2.5/3.3V -4 TQFP 144 3.1K LFXP3C-5TN144C 100 1.8/2.5/3.3V -5 TQFP 144 COM 3.1K LFXP3C-3TN100C 62 1.8/2.5/3.3V TQFP 100 COM 3.1K -3 LFXP3C-4TN100C TQFP 100 COM 62 1.8/2.5/3.3V -4 3.1K LFXP3C-5TN100C 62 -5 TQFP 100 COM 1.8/2.5/3.3V 3.1K

| Part Number    | l/Os | Voltage      | Grade | Package | Pins | Temp. | LUTs |

|----------------|------|--------------|-------|---------|------|-------|------|

| LFXP6C-3FN256C | 188  | 1.8/2.5/3.3V | -3    | fpBGA   | 256  | COM   | 5.8K |

| LFXP6C-4FN256C | 188  | 1.8/2.5/3.3V | -4    | fpBGA   | 256  | COM   | 5.8K |

| LFXP6C-5FN256C | 188  | 1.8/2.5/3.3V | -5    | fpBGA   | 256  | COM   | 5.8K |

| LFXP6C-3QN208C | 142  | 1.8/2.5/3.3V | -3    | PQFP    | 208  | COM   | 5.8K |

| LFXP6C-4QN208C | 142  | 1.8/2.5/3.3V | -4    | PQFP    | 208  | COM   | 5.8K |

| LFXP6C-5QN208C | 142  | 1.8/2.5/3.3V | -5    | PQFP    | 208  | COM   | 5.8K |

| LFXP6C-3TN144C | 100  | 1.8/2.5/3.3V | -3    | TQFP    | 144  | COM   | 5.8K |

| LFXP6C-4TN144C | 100  | 1.8/2.5/3.3V | -4    | TQFP    | 144  | COM   | 5.8K |

| LFXP6C-5TN144C | 100  | 1.8/2.5/3.3V | -5    | TQFP    | 144  | COM   | 5.8K |

| Part Number     | I/Os | Voltage      | Grade | Package | Pins | Temp. | LUTs |

|-----------------|------|--------------|-------|---------|------|-------|------|

| LFXP10C-3FN388C | 244  | 1.8/2.5/3.3V | -3    | fpBGA   | 388  | COM   | 9.7K |

| LFXP10C-4FN388C | 244  | 1.8/2.5/3.3V | -4    | fpBGA   | 388  | COM   | 9.7K |

| LFXP10C-5FN388C | 244  | 1.8/2.5/3.3V | -5    | fpBGA   | 388  | COM   | 9.7K |

| LFXP10C-3FN256C | 188  | 1.8/2.5/3.3V | -3    | fpBGA   | 256  | COM   | 9.7K |

| LFXP10C-4FN256C | 188  | 1.8/2.5/3.3V | -4    | fpBGA   | 256  | COM   | 9.7K |

| LFXP10C-5FN256C | 188  | 1.8/2.5/3.3V | -5    | fpBGA   | 256  | COM   | 9.7K |

| Part Number     | l/Os | Voltage      | Grade | Package | Pins | Temp. | LUTs  |

|-----------------|------|--------------|-------|---------|------|-------|-------|

| LFXP15C-3FN484C | 300  | 1.8/2.5/3.3V | -3    | fpBGA   | 484  | COM   | 15.5K |

| LFXP15C-4FN484C | 300  | 1.8/2.5/3.3V | -4    | fpBGA   | 484  | COM   | 15.5K |

| LFXP15C-5FN484C | 300  | 1.8/2.5/3.3V | -5    | fpBGA   | 484  | COM   | 15.5K |

| LFXP15C-3FN388C | 268  | 1.8/2.5/3.3V | -3    | fpBGA   | 388  | COM   | 15.5K |

| LFXP15C-4FN388C | 268  | 1.8/2.5/3.3V | -4    | fpBGA   | 388  | COM   | 15.5K |

| LFXP15C-5FN388C | 268  | 1.8/2.5/3.3V | -5    | fpBGA   | 388  | COM   | 15.5K |

| LFXP15C-3FN256C | 188  | 1.8/2.5/3.3V | -3    | fpBGA   | 256  | COM   | 15.5K |

| LFXP15C-4FN256C | 188  | 1.8/2.5/3.3V | -4    | fpBGA   | 256  | COM   | 15.5K |

| LFXP15C-5FN256C | 188  | 1.8/2.5/3.3V | -5    | fpBGA   | 256  | COM   | 15.5K |

# LatticeXP Family Data Sheet Supplemental Information

November 2007

Data Sheet DS1001

## For Further Information

A variety of technical notes for the LatticeXP family are available on the Lattice website at <u>www.latticesemi.com</u>.

- LatticeECP/EC and LatticeXP sysIO Usage Guide (TN1056)

- Lattice ispTRACY Usage Guide (TN1054)

- LatticeECP/EC and LatticeXP sysCLOCK PLL Design and Usage Guide (TN1049)

- Memory Usage Guide for LatticeECP/EC and LatticeXP Devices (TN1051)

- LatticeECP/EC and XP DDR Usage Guide (TN1050)

- Power Estimation and Management for LatticeECP/EC and LatticeXP Devices (TN1052)

- LatticeXP sysCONFIG Usage Guide (TN1082)

For further information on interface standards refer to the following web sites:

- JEDEC Standards (LVTTL, LVCMOS, SSTL, HSTL): www.jedec.org

- PCI: <u>www.pcisig.com</u>

© 2007 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.