Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

|                            |                                                                       |

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART               |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 37                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 11x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f303c8t6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 6.3.5     | Supply current characteristics              |

|------|-----------|---------------------------------------------|

|      | 6.3.6     | Wakeup time from low-power mode64           |

|      | 6.3.7     | External clock source characteristics64     |

|      | 6.3.8     | Internal clock source characteristics       |

|      | 6.3.9     | PLL characteristics                         |

|      | 6.3.10    | Memory characteristics                      |

|      | 6.3.11    | EMC characteristics                         |

|      | 6.3.12    | Electrical sensitivity characteristics      |

|      | 6.3.13    | I/O current injection characteristics74     |

|      | 6.3.14    | I/O port characteristics                    |

|      | 6.3.15    | NRST pin characteristics                    |

|      | 6.3.16    | Timer characteristics                       |

|      | 6.3.17    | Communication interfaces                    |

|      | 6.3.18    | ADC characteristics                         |

|      | 6.3.19    | DAC electrical specifications94             |

|      | 6.3.20    | Comparator characteristics96                |

|      | 6.3.21    | Operational amplifier characteristics97     |

|      | 6.3.22    | Temperature sensor (TS) characteristics     |

|      | 6.3.23    | V <sub>BAT</sub> monitoring characteristics |

| Pacl | kage info | ormation                                    |

| 7.1  | Packag    | ge mechanical data                          |

| 7.2  | LQFP3     | 2 package information                       |

| 7.3  | LQFP4     | 8 package information                       |

| 7.4  | LQFP6     | 4 package information                       |

| 7.5  | Therma    | al characteristics                          |

|      | 7.5.1     | Reference document                          |

|      | 7.5.2     | Selecting the product temperature range     |

7

8

9

# 1 Introduction

This datasheet provides the ordering information and the mechanical device characteristics of the STM32F303x6/8 microcontrollers.

This document should be read in conjunction with the STM32F303xx, STM32F358xx and STM32F328xx advanced ARM<sup>®</sup>-based 32-bit MCUs reference manual (RM00316) available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M4 core with FPU, refer to:

- ARM<sup>®</sup> Cortex<sup>®</sup>-M4 Processor Technical Reference Manual available from the www.arm.com website.

- STM32F3xxx and STM32F4xxx Cortex<sup>®</sup>-M4 programming manual (PM0214) available from the <u>www.st.com</u> website.

| Group | Capacitive sensing group name | Pin name |

|-------|-------------------------------|----------|

|       | TSC_G3_IO1                    | PC5      |

| 3     | TSC_G3_IO2                    | PB0      |

| 5     | TSC_G3_IO3                    | PB1      |

|       | TSC_G3_IO4                    | PB2      |

|       | TSC_G4_IO1                    | PA9      |

| 4     | TSC_G4_IO2                    | PA10     |

| 4     | TSC_G4_IO3                    | PA13     |

|       | TSC_G4_IO4                    | PA14     |

|       | TSC_G5_IO1                    | PB3      |

| 5     | TSC_G5_IO2                    | PB4      |

| 5     | TSC_G5_IO3                    | PB6      |

|       | TSC_G5_IO4                    | PB7      |

|       | TSC_G6_IO1                    | PB11     |

| 6     | TSC_G6_IO2                    | PB12     |

| U     | TSC_G6_IO3                    | PB13     |

|       | TSC_G6_IO4                    | PB14     |

## Table 10. Capacitive sensing GPIOs available on STM32F303x6/8 devices (continued)

### Table 11. Capacitive sensing GPIO available

| Group  | Capacitive sensing group<br>name | Pin name |

|--------|----------------------------------|----------|

|        | TSC_G1_IO1                       | PA0      |

| 1      | TSC_G1_IO2                       | PA1      |

| 1      | TSC_G1_IO3                       | PA2      |

|        | TSC_G1_IO4                       | PA3      |

|        | TSC_G2_IO1                       | PA4      |

| 2      | TSC_G2_IO2                       | PA5      |

| 2      | TSC_G2_IO3                       | PA6      |

|        | TSC_G2_IO4                       | PA7      |

|        | TSC_G3_IO1                       | PC5      |

| 3      | TSC_G3_IO2                       | PB0      |

| ы<br>С | TSC_G3_IO3                       | PB1      |

|        | TSC_G3_IO1                       | PC5      |

| Na                     | me                   | Abbreviation                                                     | Definition                                                                                       |  |

|------------------------|----------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|

| Pin r                  | name                 |                                                                  | specified in brackets below the pin name, the pin function during and ame as the actual pin name |  |

|                        |                      | S                                                                | Supply pin                                                                                       |  |

| Pin                    | type                 | I                                                                | Input only pin                                                                                   |  |

|                        |                      | I/O                                                              | Input / output pin                                                                               |  |

|                        |                      | FT                                                               | 5 V tolerant I/O                                                                                 |  |

|                        |                      | FTf                                                              | 5 V tolerant I/O, FM+ capable                                                                    |  |

|                        |                      | TTa                                                              | 3.3 V tolerant I/O directly connected to ADC                                                     |  |

|                        |                      | TT                                                               | 3.3 V tolerant I/O                                                                               |  |

| I/O str                | ructure              | TC                                                               | Standard 3.3 V I/O                                                                               |  |

|                        |                      | В                                                                | Dedicated BOOT0 pin                                                                              |  |

|                        |                      | RST                                                              | Bi-directional reset pin with embedded weak pull-up resistor                                     |  |

|                        |                      | POR                                                              | External power-on reset pin with embedded weak pull-up resistor, powered from V <sub>DDA</sub> . |  |

| No                     | tes                  | Unless otherwise s<br>reset                                      | specified by a note, all I/Os are set as floating inputs during and after                        |  |

| Alternate<br>functions |                      | Functions selected through GPIOx_AFR registers                   |                                                                                                  |  |

| Pin<br>functions       | Additional functions | Functions directly selected/enabled through peripheral registers |                                                                                                  |  |

## Table 13. Legend/abbreviations used in the pinout table

### Table 14. STM32F303x6/8 pin definitions

| Pi         | n Numb     | er         |                                    |          |               | Pin functions                                |                      |

|------------|------------|------------|------------------------------------|----------|---------------|----------------------------------------------|----------------------|

| LQFP<br>32 | LQFP<br>48 | LQFP<br>64 | Pin name (function<br>after reset) | Pin type | I/O structure | Alternate<br>functions                       | Additional functions |

| -          | 1          | 1          | VBAT                               | S        | -             | Backı                                        | up power supply      |

| -          | 2          | 2          | PC13 <sup>(1)</sup>                | I/O      | тс            | TIM1_CH1N RTC_TAMP1/RTC_TS/<br>RTC_OUT/WKUP2 |                      |

| -          | 3          | 3          | PC14 / OSC32_IN <sup>(1)</sup>     | I/O      | TC            | - OSC32_IN                                   |                      |

| -          | 4          | 4          | PC15 / OSC32_OUT <sup>(1)</sup>    | I/O      | TC            | - OSC32_OUT                                  |                      |

| 2          | 5          | 5          | PF0 / OSC_IN                       | I/O      | FT            | TIM1_CH3N                                    | OSC_IN               |

| Pi         | n Numb     | er         |                                    |          |               | Pin functions                                                                 |                                                     |  |

|------------|------------|------------|------------------------------------|----------|---------------|-------------------------------------------------------------------------------|-----------------------------------------------------|--|

| LQFP<br>32 | LQFP<br>48 | LQFP<br>64 | Pin name (function<br>after reset) | Pin type | I/O structure | Alternate<br>functions                                                        | Additional functions                                |  |

| 12         | 16         | 22         | PA6 <sup>(3)</sup>                 | I/O      | ТТа           | TIM16_CH1, TIM3_CH1,<br>TSC_G2_IO3,<br>SPI1_MISO,<br>TIM1_BKIN, ,<br>EVENTOUT | ADC2_IN3 <sup>(2)</sup> , DAC2_OUT1,<br>OPAMP2_VOUT |  |

| 13         | 17         | 23         | PA7                                | I/O      | ТТа           | TIM17_CH1, TIM3_CH2,<br>TSC_G2_IO4,<br>SPI1_MOSI,<br>TIM1_CH1N,<br>EVENTOUT   | ADC2_IN4 <sup>(2)</sup> , COMP2_INP,<br>OPAMP2_VINP |  |

| -          | -          | 24         | PC4                                | I/O      | TTa           | EVENTOUT, TIM1_ETR,<br>USART1_TX                                              | ADC2_IN5 <sup>(2)</sup>                             |  |

| -          | -          | 25         | PC5                                | I/O      | ТТа           | EVENTOUT,<br>TIM15_BKIN,<br>TSC_G3_IO1,<br>USART1_RX                          | ADC2_IN11, OPAMP2_VINM                              |  |

| 14         | 18         | 26         | PB0                                | I/O      | ТТа           | TIM3_CH3,<br>TSC_G3_IO2,<br>TIM1_CH2N,<br>EVENTOUT                            | ADC1_IN11, COMP4_INP,<br>OPAMP2_VINP                |  |

| 15         | 19         | 27         | PB1                                | I/O      | ТТа           | TIM3_CH4,<br>TSC_G3_IO3,<br>TIM1_CH3N,<br>COMP4_OUT,<br>EVENTOUT              | ADC1_IN12                                           |  |

| -          | 20         | 28         | PB2                                | I/O      | TTa           | TSC_G3_IO4,<br>EVENTOUT                                                       | ADC2_IN12, COMP4_INM                                |  |

| -          | 21         | 29         | PB10                               | I/O      | TT            | TIM2_CH3, TSC_SYNC,<br>USART3_TX,<br>EVENTOUT                                 | -                                                   |  |

| -          | 22         | 30         | PB11                               | I/O      | ТТа           | TIM2_CH4,<br>TSC_G6_IO1,<br>USART3_RX,<br>EVENTOUT                            | COMP6_INP                                           |  |

| 16         | 23         | 31         | VSS                                | S        | -             | Di                                                                            | igital ground                                       |  |

| 17         | 24         | 32         | VDD                                | S        | -             | Digita                                                                        | al power supply                                     |  |

| -          | 25         | 33         | PB12                               | I/O      | TTa           | TSC_G6_IO2,<br>TIM1_BKIN,<br>USART3_CK,<br>EVENTOUT                           | ADC2_IN13                                           |  |

| -          | 26         | 34         | PB13                               | I/O      | ТТа           | TSC_G6_IO3,<br>TIM1_CH1N,<br>USART3_CTS,<br>EVENTOUT                          | ADC1_IN13                                           |  |

| -          | 27         | 35         | PB14                               | I/O      | ТТа           | TIM15_CH1,<br>TSC_G6_IO4,<br>TIM1_CH2N,<br>USART3_RTS_DE,<br>EVENTOUT         | ADC2_IN14, OPAMP2_VINP                              |  |

Table 14. STM32F303x6/8 pin definitions (continued)

Г

| Pi         | n Numb     | er         |                                    |          |               | Pin functions                                                                                           |                      |

|------------|------------|------------|------------------------------------|----------|---------------|---------------------------------------------------------------------------------------------------------|----------------------|

| LQFP<br>32 | LQFP<br>48 | LQFP<br>64 | Pin name (function<br>after reset) | Pin type | I/O structure | Alternate<br>functions                                                                                  | Additional functions |

| 25         | 38         | 50         | PA15                               | I/O      | FTf           | JTDI,<br>TIM2_CH1/TIM2_ETR,<br>TSC_SYNC, I2C1_SCL,<br>SPI1_NSS,<br>USART2_RX,<br>TIM1_BKIN,<br>EVENTOUT | -                    |

| -          | -          | 51         | PC10                               | I/O      | FT            | EVENTOUT,<br>USART3_TX                                                                                  | -                    |

| -          | -          | 52         | PC11                               | I/O      | FT            | EVENTOUT,<br>USART3_RX                                                                                  | -                    |

| -          | -          | 53         | PC12                               | I/O      | FT            | EVENTOUT,<br>USART3_CK                                                                                  | -                    |

| -          | -          | 54         | PD2                                | I/O      | FT            | EVENTOUT, TIM3_ETR                                                                                      | -                    |

| 26         | 39         | 55         | PB3                                | I/O      | FT            | JTDO/TRACE<br>SWO, TIM2_CH2,<br>TSC_G5_IO1,<br>SPI1_SCK,<br>USART2_TX,<br>TIM3_ETR, EVENTOUT            | -                    |

| 27         | 40         | 56         | PB4                                | I/O      | FT            | NJTRST, TIM16_CH1,<br>TIM3_CH1,<br>TSC_G5_IO2,<br>SPI1_MISO,<br>USART2_RX,<br>TIM17_BKIN,<br>EVENTOUT   | -                    |

| 28         | 41         | 57         | PB5                                | I/O      | FT            | TIM16_BKIN,<br>TIM3_CH2,<br>I2C1_SMBA,<br>SPI1_MOSI,<br>USART2_CK,<br>TIM17_CH1,<br>EVENTOUT            | -                    |

| 29         | 42         | 58         | PB6                                | I/O      | FTf           | TIM16_CH1N,<br>TSC_G5_IO3,<br>I2C1_SCL,<br>USART1_TX,<br>EVENTOUT                                       | -                    |

| 30         | 43         | 59         | PB7                                | I/O      | FTf           | TIM17_CH1N,<br>TSC_G5_IO4,<br>I2C1_SDA,<br>USART1_RX,<br>TIM3_CH4, EVENTOUT                             | -                    |

| 31         | 44         | 60         | BOOT0                              | I        | В             | -                                                                                                       | -                    |

| -          | 45         | 61         | PB8                                | I/O      | FTf           | TIM16_CH1,<br>TSC_SYNC, I2C1_SCL,<br>USART3_RX, CAN_RX,<br>TIM1_BKIN,<br>EVENTOUT                       | -                    |

| Table 14. STM32 | F303x6/8 | s pin def | initions (continued) |

|-----------------|----------|-----------|----------------------|

|                 |          |           |                      |

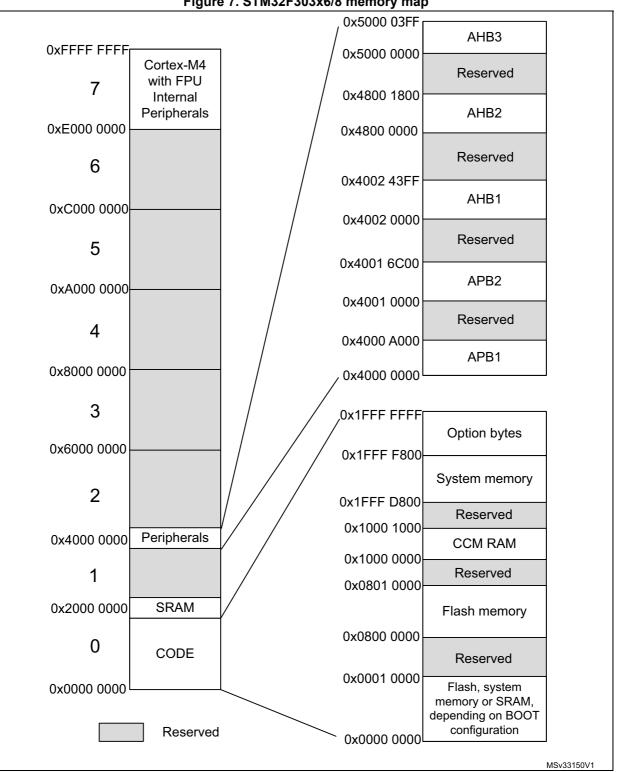

#### 5 Memory mapping

Figure 7. STM32F303x6/8 memory map

DocID025083 Rev 5

# 6.3 Operating conditions

## 6.3.1 General operating conditions

| Table 20 | General | operating | conditions |

|----------|---------|-----------|------------|

|----------|---------|-----------|------------|

| Symbol             | Parameter                                                                                    | Conditions                           | Min. | Max.                  | Unit       |  |

|--------------------|----------------------------------------------------------------------------------------------|--------------------------------------|------|-----------------------|------------|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                                                 | -                                    | 0    | 72                    |            |  |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                                                                | -                                    | 0    | 36                    | MHz        |  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                                                                | -                                    | 0    | 72                    |            |  |

| V <sub>DD</sub>    | Standard operating voltage                                                                   | -                                    | 2    | 3.6                   |            |  |

|                    | Analog operating voltage<br>(OPAMP and DAC not used)                                         | Must have a potential equal to       | 2    | 3.6                   |            |  |

| V <sub>DDA</sub>   | Analog operating voltage<br>(OPAMP and DAC used)                                             | or higher than V <sub>DD</sub>       | 2.4  | 3.6                   | V          |  |

| V <sub>BAT</sub>   | Backup operating voltage                                                                     | -                                    | 1.65 | 3.6                   | V          |  |

|                    |                                                                                              | TC I/O                               | -0.3 | V <sub>DD</sub> +0.3  |            |  |

|                    |                                                                                              | TT I/O                               | -0.3 | 3.6                   |            |  |

| V <sub>IN</sub>    | I/O input voltage                                                                            | TTa I/O                              | -0.3 | V <sub>DDA</sub> +0.3 | V          |  |

|                    |                                                                                              | FT and FTf I/O <sup>(1)</sup>        | -0.3 | 5.5                   |            |  |

|                    |                                                                                              | BOOT0                                | 0    | 5.5                   |            |  |

| PD                 | Power dissipation at $T_A = 85$ °C for<br>suffix 6 or $T_A = 105$ °C for suffix<br>$7^{(2)}$ | LQFP64                               | -    | 444                   | mW         |  |

| PD                 | Power dissipation at $T_A$ = 85 °C for<br>suffix 6 or $T_A$ = 105 °C for suffix<br>$7^{(3)}$ | LQFP48                               | -    | 364                   | mW         |  |

|                    | Ambient temperature for 6 suffix                                                             | Maximum power dissipation            | -40  | 85                    | ° <b>C</b> |  |

| Та                 | version                                                                                      | Low power dissipation <sup>(4)</sup> | -40  | 105                   | °C         |  |

| IA                 | Ambient temperature for 7 suffix                                                             | Maximum power dissipation            | -40  | 105                   | °C         |  |

|                    | version                                                                                      | Low power dissipation <sup>(4)</sup> | -40  | 125                   |            |  |

| TJ                 | Junction temperature range                                                                   | 6 suffix version                     | -40  | 105                   | °C         |  |

| IJ                 |                                                                                              | 7 suffix version                     | -40  | 125                   |            |  |

1. To sustain a voltage higher than  $V_{DD}$ +0.3 V, the internal pull-up/pull-down resistors must be disabled.

2. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$  (see Section 7.5: Thermal characteristics).

3. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$  (see Section 7.5: Thermal characteristics).

4. In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.5: *Thermal characteristics*).

## 6.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 21* are derived from tests performed under the ambient temperature condition summarized in *Table 20*.

| Symbol            | Parameter                       | Conditions | Min. | Max. | Unit  |

|-------------------|---------------------------------|------------|------|------|-------|

| +                 | V <sub>DD</sub> rise time rate  |            | 0    | 8    |       |

| t <sub>VDD</sub>  | V <sub>DD</sub> fall time rate  | -          | 20   | 8    | µs/V  |

| +                 | V <sub>DDA</sub> rise time rate |            | 0    | ∞    | μ5/ ν |

| <sup>t</sup> VDDA | V <sub>DDA</sub> fall time rate | -          | 20   | ∞    |       |

Table 21. Operating conditions at power-up / power-down

## 6.3.3 Characteristics of the embedded reset and power-control block

The parameters given in *Table 22* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 20*.

| Symbol                               | Parameter                           | Conditions   | Min.               | Тур. | Max. | Unit |

|--------------------------------------|-------------------------------------|--------------|--------------------|------|------|------|

| V <sub>POR/PDR</sub> <sup>(1)</sup>  | Power on/power down reset threshold | Falling edge | 1.8 <sup>(2)</sup> | 1.88 | 1.96 | V    |

|                                      |                                     | Rising edge  | 1.84               | 1.92 | 2.0  | V    |

| V <sub>PDRhyst</sub> <sup>(1)</sup>  | PDR hysteresis                      | -            | -                  | 40   | -    | mV   |

| t <sub>RSTTEMPO</sub> <sup>(3)</sup> | POR reset temporization             | -            | 1.5                | 2.5  | 4.5  | ms   |

1. The PDR detector monitors  $V_{DD}$  and also  $V_{DDA}$  (if kept enabled in the option bytes). The POR detector monitors only  $V_{DD}$ .

2. The product behavior is guaranteed by design down to the minimum  $V_{\mbox{POR/PDR}}$  value.

3. Guaranteed by design, not tested in production.

| Calibration value name  | Description                                                              | Memory address            |

|-------------------------|--------------------------------------------------------------------------|---------------------------|

| V <sub>REFINT_CAL</sub> | Raw data acquired at<br>temperature of 30 °C<br>V <sub>DDA</sub> = 3.3 V | 0x1FFF F7BA - 0x1FFF F7BB |

#### Table 25. Internal reference voltage calibration values

## 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 11: Scheme of the current-consumption measurement.*

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

Note: The total current consumption is the sum of IDD and IDDA.

### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states from 48 to 72 MHz)

- Prefetch in ON (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled  $f_{PCLK2} = f_{HCLK}$  and  $f_{PCLK1} = f_{HCLK/2}$

- When f<sub>HCLK</sub> > 8 MHz, the PLL is ON and the PLL input is equal to HSI/2 (4 MHz) or HSE (8 MHz) in bypass mode.

The parameters given in *Table 26* to *Table 30* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 20*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

### I/O dynamic current consumption

In addition to the internal peripheral current consumption (see *Table 35: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the MCU supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DD} \times f_{SW} \times C$$

where:

$I_{SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load  $V_{DD}$  is the MCU supply voltage

f<sub>SW</sub> is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT+CS}$

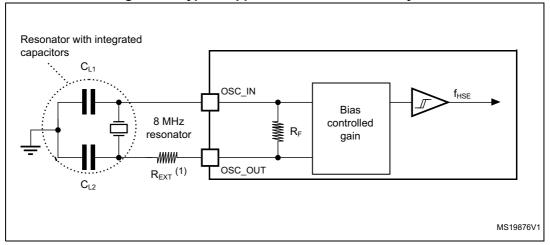

For C<sub>L1</sub> and C<sub>L2</sub>, it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 15*). C<sub>L1</sub> and C<sub>L2</sub> are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of C<sub>L1</sub> and C<sub>L2</sub>. PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing C<sub>L1</sub> and C<sub>L2</sub>.

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 41*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

## 6.3.16 Timer characteristics

The parameters given in *Table 56* are guaranteed by design.

Refer to Section 6.3.14: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Table 56. TIMx <sup>(1)(2)</sup> characteristics |                                                 |                                |        |                         |                          |  |  |

|--------------------------------------------------|-------------------------------------------------|--------------------------------|--------|-------------------------|--------------------------|--|--|

| Symbol                                           | Parameter                                       | Conditions                     | Min.   | Max.                    | Unit                     |  |  |

|                                                  | Timer resolution time                           | -                              | 1      | -                       | t <sub>TIMxCL</sub><br>к |  |  |

| t <sub>res(TIM)</sub>                            |                                                 | f <sub>TIMxCLK</sub> = 72 MHz  | 13.9   | -                       | ns                       |  |  |

|                                                  |                                                 | f <sub>TIM1CLK</sub> = 144 MHz | 6.95   | -                       | ns                       |  |  |

| f                                                | Timer external clock<br>frequency on CH1 to CH4 | -                              | 0      | f <sub>TIMxCLK</sub> /2 | MHz                      |  |  |

| f <sub>EXT</sub>                                 |                                                 | f <sub>TIMxCLK</sub> = 72 MHz  | 0      | 36                      | MHz                      |  |  |

| Pos-u i                                          | Timer resolution                                | TIMx (except TIM2)             | -      | 16                      | bit                      |  |  |

| Res <sub>TIM</sub>                               |                                                 | TIM2                           | -      | 32                      | DIL                      |  |  |

|                                                  | 16-bit counter clock period                     | -                              | 1      | 65536                   | t <sub>TIMxCL</sub><br>к |  |  |

| <sup>t</sup> COUNTER                             |                                                 | f <sub>TIMxCLK</sub> = 72 MHz  | 0.0139 | 910                     | μs                       |  |  |

|                                                  |                                                 | f <sub>TIM1CLK</sub> = 144 MHz | 0.0069 | 455                     | μs                       |  |  |

| t <sub>MAX_COUN</sub>                            | Maximum possible count                          | -                              | -      | 65536 × 65536           | t <sub>TIMxCL</sub><br>к |  |  |

|                                                  | with 32-bit counter                             | f <sub>TIMxCLK</sub> = 72 MHz  | -      | 59.65                   | S                        |  |  |

|                                                  |                                                 | f <sub>TIM1CLK</sub> = 144 MHz | -      | 29.825                  | S                        |  |  |

Table 56. TIMx<sup>(1)(2)</sup> characteristics

1. TIMx is used as a general term to refer to the TIM1, TIM2, TIM3, TIM15, TIM16 and TIM17 timers.

2. Guaranteed by design, not tested in production.

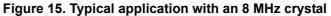

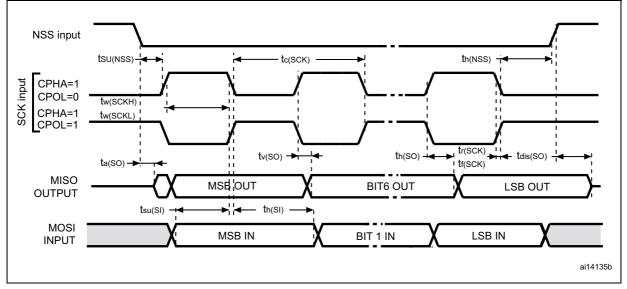

Figure 24. SPI timing diagram - slave mode and CPHA = 0

Figure 25. SPI timing diagram - slave mode and CPHA = 1<sup>(1)</sup>

1. Measurement points are done at 0.5V\_{DD} and with external C\_L = 30 pF.

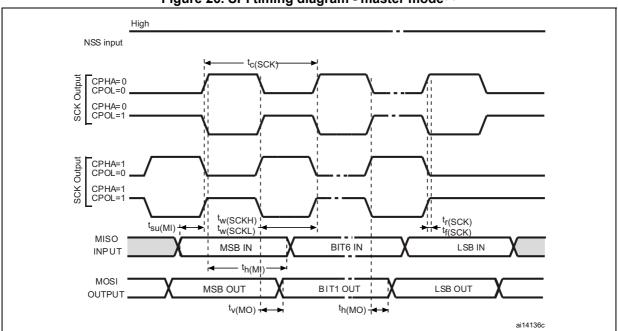

Figure 26. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at  $0.5V_{DD}$  and with external C<sub>L</sub> = 30 pF.

#### CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

## 6.3.18 ADC characteristics

Unless otherwise specified, the parameters given in *Table 61* to *Table 64* are guaranteed by design, with conditions summarized in *Table 20*.

| Symbol           | Parameter                                       | Conditions                     | Min. | Тур.   | Max.   | Unit |

|------------------|-------------------------------------------------|--------------------------------|------|--------|--------|------|

| V <sub>DDA</sub> | Analog supply voltage for ADC                   | -                              | 2    | -      | 3.6    | V    |

|                  |                                                 | Single ended mode, 5<br>MSPS,  | -    | 1011.3 | 1172.0 |      |

|                  |                                                 | Single ended mode, 1<br>MSPS   | -    | 214.7  | 322.3  |      |

|                  | ADC current consumption<br>( <i>Figure 27</i> ) | Single ended mode, 200<br>KSPS | -    | 54.7   | 81.1   |      |

| IDDA             |                                                 | Differential mode,5<br>MSPS,   | -    | 1061.5 | 1243.6 | μA   |

|                  |                                                 | Differential mode, 1<br>MSPS   | -    | 246.6  | 337.6  |      |

|                  |                                                 | Differential mode, 200<br>KSPS | -    | 56.4   | 83.0   |      |

Table 61. ADC characteristics

| Symbol                                        | Parameter                        | (                                                                          | Conditions   | -                   | Min <sup>(4)</sup> | Max <sup>(4)</sup> | Unit |

|-----------------------------------------------|----------------------------------|----------------------------------------------------------------------------|--------------|---------------------|--------------------|--------------------|------|

|                                               |                                  |                                                                            | Single ended | Fast channel 5.1 Ms | -                  | ±3                 |      |

| EL                                            | Integral                         |                                                                            | Single ended | Slow channel 4.8 Ms | -                  | ±3.5               |      |

|                                               | linearity<br>error               |                                                                            | Differential | Fast channel 5.1 Ms | -                  | ±2                 |      |

|                                               |                                  |                                                                            | Differential | Slow channel 4.8 Ms | -                  | ±2.5               |      |

|                                               |                                  |                                                                            | Single ended | Fast channel 5.1 Ms | 10.4               | -                  | bits |

| ENOB<br>(5)<br>Effective<br>number of<br>bits |                                  | ADC clock freq. $\leq$ 72 MHz,<br>Sampling freq. $\leq$ 5 Msps             | Single ended | Slow channel 4.8 Ms | 10.4               | -                  |      |

|                                               |                                  | $2.0 \text{ V} \le \text{V}_{\text{DDA}} \le 3.6 \text{ V}$                | Differential | Fast channel 5.1 Ms | 10.8               | -                  |      |

|                                               |                                  |                                                                            |              | Slow channel 4.8 Ms | 10.8               | -                  |      |

| Signal-t<br>SINAD noise ar                    | Signal-to-                       |                                                                            | Single ended | Fast channel 5.1 Ms | 64                 | -                  | dB   |

|                                               | noise and<br>distortion<br>ratio | oise and<br>istortion                                                      |              | Slow channel 4.8 Ms | 63                 | -                  |      |

| (5)                                           |                                  |                                                                            | Differential | Fast channel 5.1 Ms | 67                 | -                  |      |

|                                               |                                  |                                                                            |              | Slow channel 4.8 Ms | 67                 | -                  |      |

|                                               |                                  |                                                                            | Single ended | Fast channel 5.1 Ms | 64                 | -                  | dB   |

| SNR <sup>(5)</sup>                            | Signal-to-                       |                                                                            | Single ended | Slow channel 4.8 Ms | 64                 | -                  |      |

| SINK                                          | noise ratio                      | ADC clock freq. ≤ 72 MHz, Differentia                                      | Differential | Fast channel 5.1 Ms | 67                 | -                  |      |

|                                               |                                  |                                                                            | Dillerential | Slow channel 4.8 Ms | 67                 | -                  |      |

| THD <sup>(5)</sup>                            |                                  | Sampling freq $\leq$ 5 Msps,<br>2.0 V $\leq$ V <sub>DDA</sub> $\leq$ 3.6 V | Single ended | Fast channel 5.1 Ms | -                  | -75                |      |

|                                               | Total<br>harmonic                |                                                                            | Single ended | Slow channel 4.8 Ms | -                  | -75                |      |

| יייטחו                                        | distortion                       |                                                                            | Differential | Fast channel 5.1 Ms | -                  | -79                |      |

|                                               |                                  |                                                                            | Dinerential  | Slow channel 4.8 Ms | -                  | -78                |      |

## Table 64. ADC accuracy <sup>(1)(2)(3)</sup> (continued)

1. ADC DC accuracy values are measured after internal calibration.

ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.14 does not affect the ADC accuracy.

3. Better performance may be achieved in restricted  $V_{\text{DDA}}$ , frequency and temperature ranges.

4. Data based on characterization results, not tested in production.

5. Value measured with a -0.5 dB full scale 50 kHz sine wave input signal.

| Symbol                   | Parameter                                                                                               | Condition                                                                                                                  | Min.                  | Тур.     | Max.                | Unit |

|--------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|---------------------|------|

| VOH                      | High saturation voltage <sup>(2)</sup>                                                                  | R <sub>load</sub> = min,<br>Input at V <sub>DDA</sub> .                                                                    | V <sub>DDA</sub> -100 | -        |                     |      |

| VOH <sub>SAT</sub>       | ngi oddiadon tolago                                                                                     | R <sub>load</sub> = 20K,<br>Input at V <sub>DDA</sub> .                                                                    | V <sub>DDA</sub> -20  | -        |                     | mV   |

| VOL <sub>SAT</sub>       | Low saturation voltage                                                                                  | R <sub>load</sub> = min,<br>input at 0 V                                                                                   | -                     | -        | 100                 | IIIV |

| VOLSAT                   |                                                                                                         | R <sub>load</sub> = 20K,<br>input at 0 V.                                                                                  | -                     | -        | 20                  |      |

| φm                       | Phase margin                                                                                            | -                                                                                                                          | -                     | 62       | -                   | 0    |

| t <sub>offtrim</sub>     | Offset trim time: during calibration,<br>minimum time needed between two<br>steps to have 1 mV accuracy | -                                                                                                                          | -                     | -        | 2                   | ms   |

| twakeup                  | Wake up time from OFF state.                                                                            | $\begin{array}{l} C_{LOAD} \leq \!\! 50 \mbox{ pf}, \\ R_{LOAD} \geq 4  k\Omega, \\ Follower \\ configuration \end{array}$ | -                     | 2.8      | 5                   | μs   |

| t <sub>S_OPAM_VOUT</sub> | ADC sampling time when reading the 0                                                                    | DPAMP output                                                                                                               | 400                   | -        | -                   | ns   |

|                          | Non inverting gain value                                                                                | -                                                                                                                          | -                     | 2        | -                   | -    |

| PGA gain                 |                                                                                                         |                                                                                                                            | -                     | 4        | -                   | -    |

| FGA yain                 |                                                                                                         |                                                                                                                            | -                     | 8        | -                   | -    |

|                          |                                                                                                         |                                                                                                                            | -                     | 16       | -                   | -    |

|                          | R2/R1 internal resistance values in PGA mode <sup>(3)</sup>                                             | Gain=2                                                                                                                     | -                     | 5.4/5.4  | -                   |      |

| D                        |                                                                                                         | Gain=4                                                                                                                     | -                     | 16.2/5.4 | -                   | kΩ   |

| R <sub>network</sub>     |                                                                                                         | Gain=8                                                                                                                     | -                     | 37.8/5.4 | -                   |      |

|                          |                                                                                                         | Gain=16                                                                                                                    | -                     | 40.5/2.7 | -                   |      |

| PGA gain error           | PGA gain error                                                                                          | -                                                                                                                          | -1%                   | -        | 1%                  | -    |

| I <sub>bias</sub>        | OPAMP input bias current                                                                                | -                                                                                                                          | -                     | -        | ±0.2 <sup>(4)</sup> | μA   |

|                          |                                                                                                         | PGA Gain = 2,<br>$C_{load}$ = 50pF,<br>$R_{load}$ = 4 K $\Omega$                                                           | -                     | 4        | -                   |      |

| PGA BW                   | PGA bandwidth for different non                                                                         | PGA Gain = 4,<br>$C_{load}$ = 50pF,<br>$R_{load}$ = 4 K $\Omega$                                                           | -                     | 2        | -                   | MHz  |

|                          | inverting gain                                                                                          | PGA Gain = 8,<br>$C_{load}$ = 50pF,<br>$R_{load}$ = 4 K $\Omega$                                                           | -                     | 1        | -                   |      |

|                          |                                                                                                         | PGA Gain = 16,<br>$C_{load}$ = 50pF,<br>$R_{load}$ = 4 K $\Omega$                                                          | -                     | 0.5      | -                   |      |

| Table 68. Operational amplifier ch | naracteristics <sup>(1)</sup> (continued) |

|------------------------------------|-------------------------------------------|

|------------------------------------|-------------------------------------------|

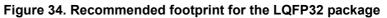

| Table 72. EQT F 52 mechanical data (continued) |       |             |       |        |                       |        |  |  |

|------------------------------------------------|-------|-------------|-------|--------|-----------------------|--------|--|--|

| Symbol                                         |       | Millimeters |       |        | Inches <sup>(1)</sup> |        |  |  |

| Symbol                                         | Min.  | Тур.        | Max.  | Min.   | Тур.                  | Max.   |  |  |

| b                                              | 0.300 | 0.370       | 0.450 | 0.0118 | 0.0146                | 0.0177 |  |  |

| С                                              | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |  |  |

| D                                              | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543                | 0.3622 |  |  |

| D1                                             | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756                | 0.2835 |  |  |

| D3                                             | -     | 5.600       | -     | -      | 0.2205                | -      |  |  |

| E                                              | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543                | 0.3622 |  |  |

| E1                                             | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756                | 0.2835 |  |  |

| E3                                             | -     | 5.600       | -     | -      | 0.2205                | -      |  |  |

| е                                              | -     | 0.800       | -     | -      | 0.0315                | -      |  |  |

| L                                              | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |  |  |

| L1                                             | -     | 1.000       | -     | -      | 0.0394                | -      |  |  |

| k                                              | 0.0°  | 3.5°        | 7.0°  | 0.0°   | 3.5°                  | 7.0°   |  |  |

| CCC                                            | -     | -           | 0.100 | -      | -                     | 0.0039 |  |  |

Table 72. LQFP32 mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Drawing is not to scale.

2. Dimensions are expressed in millimeters.

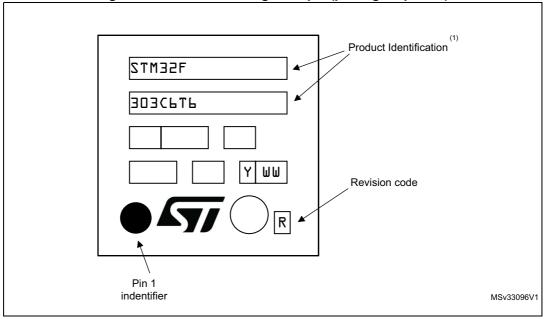

### **Device marking for LQFP48**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 38. LQFP48 marking example (package top view)

Parts marked as "ES","E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

## 7.5 Thermal characteristics

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max x \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub> max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I/O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Sy | ymbol         | Parameter                                                                      | Value  | Unit |

|----|---------------|--------------------------------------------------------------------------------|--------|------|

|    | $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch      | 45°C/W | °C/W |

|    | $\Theta_{JA}$ | <b>Thermal resistance junction-ambient</b><br>LQFP32 - 7 × 7 mm / 0.8 mm pitch | 60°C/W | °C/W |

Table 75. Package thermal characteristics

## 7.5.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

## 7.5.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Table 76: Ordering information scheme*.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

As applications do not commonly use the STM32F303x6/8 at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

#### Example: high-performance application

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$  = 82 °C (measured according to JESD51-2), I<sub>DDmax</sub> = 50 mA, V<sub>DD</sub> = 3.5 V, maximum 20 I/Os used at the same time in output at low