#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

|                            |                                                                       |

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART               |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K × 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 9x12b; D/A 3x12b                                                  |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f303k8t6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## • 96-bit unique ID

• All packages ECOPACK<sup>®</sup>2

| Reference   | Part number       |

|-------------|-------------------|

| STM32F303x6 | STM32F303K6/C6/R6 |

| STM32F303x8 | STM32F303K8/C8/R8 |

|      | 6.3.5     | Supply current characteristics              |

|------|-----------|---------------------------------------------|

|      | 6.3.6     | Wakeup time from low-power mode64           |

|      | 6.3.7     | External clock source characteristics64     |

|      | 6.3.8     | Internal clock source characteristics       |

|      | 6.3.9     | PLL characteristics                         |

|      | 6.3.10    | Memory characteristics                      |

|      | 6.3.11    | EMC characteristics                         |

|      | 6.3.12    | Electrical sensitivity characteristics      |

|      | 6.3.13    | I/O current injection characteristics74     |

|      | 6.3.14    | I/O port characteristics                    |

|      | 6.3.15    | NRST pin characteristics                    |

|      | 6.3.16    | Timer characteristics                       |

|      | 6.3.17    | Communication interfaces                    |

|      | 6.3.18    | ADC characteristics                         |

|      | 6.3.19    | DAC electrical specifications94             |

|      | 6.3.20    | Comparator characteristics96                |

|      | 6.3.21    | Operational amplifier characteristics97     |

|      | 6.3.22    | Temperature sensor (TS) characteristics     |

|      | 6.3.23    | V <sub>BAT</sub> monitoring characteristics |

| Pacl | kage info | ormation                                    |

| 7.1  | Packag    | ge mechanical data                          |

| 7.2  | LQFP3     | 2 package information                       |

| 7.3  | LQFP4     | 8 package information                       |

| 7.4  | LQFP6     | 4 package information                       |

| 7.5  | Therma    | al characteristics                          |

|      | 7.5.1     | Reference document                          |

|      | 7.5.2     | Selecting the product temperature range     |

7

8

9

## 1 Introduction

This datasheet provides the ordering information and the mechanical device characteristics of the STM32F303x6/8 microcontrollers.

This document should be read in conjunction with the STM32F303xx, STM32F358xx and STM32F328xx advanced ARM<sup>®</sup>-based 32-bit MCUs reference manual (RM00316) available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M4 core with FPU, refer to:

- ARM<sup>®</sup> Cortex<sup>®</sup>-M4 Processor Technical Reference Manual available from the www.arm.com website.

- STM32F3xxx and STM32F4xxx Cortex<sup>®</sup>-M4 programming manual (PM0214) available from the <u>www.st.com</u> website.

## 2 Description

The STM32F303x6/8 family incorporates the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at up to 72 MHz frequency embedding a floating point unit (FPU), high-speed embedded memories (up to 64 Kbytes of Flash memory, 12 Kbytes of SRAM), and an extensive range of enhanced I/Os and peripherals connected to two APB buses.

The STM32F303x6/8 microcontrollers offer up to two fast 12-bit ADCs (5 Msps), up to three ultra-fast comparators, an operational amplifier, three DAC channels, a low-power RTC, one general-purpose, 32-bit timer, one timer dedicated to motor control, and four general-purpose, 16-bit timers. They also feature standard and advanced communication interfaces: one I<sup>2</sup>C, one SPI, up to three USARTs and one CAN.

The STM32F303x6/8 family operates in the -40 to +85 °C and -40 to +105 °C temperature ranges from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving modes allows the design of low-power applications.

The STM32F303x6/8 family offers devices in 32, and 64-pin packages.

Depending on the device chosen, different sets of peripherals are included.

remains in reset mode when the monitored supply voltage is below a specified threshold, VPOR/PDR, without the need for an external reset circuit.

- The POR monitors only the V<sub>DD</sub> supply voltage. During the startup phase it is required that V<sub>DDA</sub> should arrive first and be greater than or equal to V<sub>DD</sub>.

- The PDR monitors both the V<sub>DD</sub> and V<sub>DDA</sub> supply voltages, however the V<sub>DDA</sub> power supply supervisor can be disabled (by programming a dedicated Option bit) to reduce the power consumption if the application design ensures that V<sub>DDA</sub> is higher than or equal to V<sub>DD</sub>.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}$  power supply and compares it to the VPVD threshold. An interrupt can be generated when  $V_{DD}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

### 3.4.3 Voltage regulator

The regulator has three operation modes: main (MR), low-power (LPR), and power-down.

- The MR mode is used in the nominal regulation mode (Run)

- The LPR mode is used in Stop mode.

- The power-down mode is used in Standby mode: the regulator output is in high impedance, and the kernel circuitry is powered down thus inducing zero consumption.

The voltage regulator is always enabled after reset. It is disabled in Standby mode.

#### 3.4.4 Low-power modes

The STM32F303x6/8 supports three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

#### • Stop mode

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm, COMPx,  $I^2C$  or USARTx.

#### Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

DocID025083 Rev 5

high-speed APB domains is 72 MHz, while the maximum allowed frequency of the low-speed APB domain is 36 MHz.

TIM1 maximum frequency is 144 MHz.

## 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high current capable except for analog inputs.

The I/Os alternate function configuration can be locked if needed, following a specific sequence to avoid spurious writing to the I/Os registers.

Fast I/O handling allows I/O toggling up to 36 MHz.

## 3.8 Direct memory access (DMA)

The flexible general-purpose DMA is able to manage memory-to-memory, peripheral-tomemory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each of the 7 DMA channels is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, general-purpose timers, DAC and ADC.

## 3.9 Interrupts and events

### 3.9.1 Nested vectored interrupt controller (NVIC)

The STM32F303x6/8 devices embed a nested vectored interrupt controller (NVIC) able to handle up to 60 interrupt channels, that can be masked and 16 priority levels.

The NVIC benefits are the following:

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

The NVIC hardware block provides flexible interrupt management features with minimal interrupt latency.

### 3.9.2 Extended interrupt/event controller (EXTI)

The external interrupt/event controller consists of 27 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked

DocID025083 Rev 5

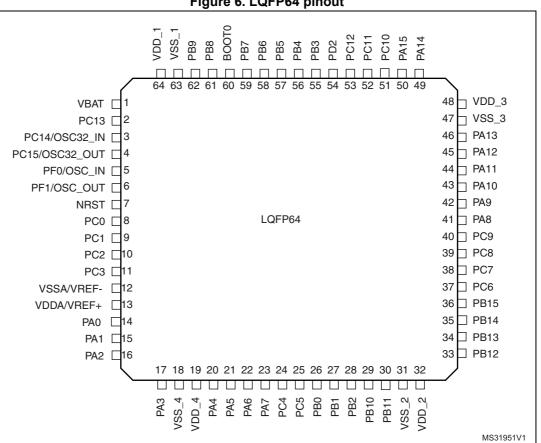

Figure 6. LQFP64 pinout

## 6.3 Operating conditions

## 6.3.1 General operating conditions

| Table 20 | General | operating | conditions |

|----------|---------|-----------|------------|

|----------|---------|-----------|------------|

| Symbol             | Parameter                                                                                    | Conditions                           | Min. | Max.                  | Unit       |  |  |

|--------------------|----------------------------------------------------------------------------------------------|--------------------------------------|------|-----------------------|------------|--|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                                                 | -                                    | 0    | 72                    |            |  |  |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                                                                | -                                    | 0    | 36                    | MHz        |  |  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                                                                | -                                    | 0    | 72                    |            |  |  |

| V <sub>DD</sub>    | Standard operating voltage                                                                   | -                                    | 2    | 3.6                   |            |  |  |

|                    | Analog operating voltage<br>(OPAMP and DAC not used)                                         | Must have a potential equal to       | 2    | 3.6                   |            |  |  |

| V <sub>DDA</sub>   | Analog operating voltage<br>(OPAMP and DAC used)                                             | or higher than V <sub>DD</sub>       | 2.4  | 3.6                   | V          |  |  |

| V <sub>BAT</sub>   | Backup operating voltage                                                                     | -                                    | 1.65 | 3.6                   | V          |  |  |

|                    |                                                                                              | TC I/O                               | -0.3 | V <sub>DD</sub> +0.3  |            |  |  |

|                    |                                                                                              | TT I/O                               | -0.3 | 3.6                   |            |  |  |

| V <sub>IN</sub>    | I/O input voltage                                                                            | TTa I/O                              | -0.3 | V <sub>DDA</sub> +0.3 | v          |  |  |

|                    |                                                                                              | FT and FTf I/O <sup>(1)</sup>        | -0.3 | 5.5                   | 5          |  |  |

|                    |                                                                                              | BOOT0                                | 0    | 5.5                   |            |  |  |

| PD                 | Power dissipation at $T_A = 85$ °C for<br>suffix 6 or $T_A = 105$ °C for suffix<br>$7^{(2)}$ | LQFP64                               | -    | 444                   | mW         |  |  |

| PD                 | Power dissipation at $T_A$ = 85 °C for<br>suffix 6 or $T_A$ = 105 °C for suffix<br>$7^{(3)}$ | LQFP48                               | -    | 364                   | mW         |  |  |

|                    | Ambient temperature for 6 suffix                                                             | Maximum power dissipation            | -40  | 85                    | ° <b>C</b> |  |  |

| Ve                 | version                                                                                      | Low power dissipation <sup>(4)</sup> | -40  | 105                   | °C         |  |  |

| ΤΑ                 | Ambient temperature for 7 suffix                                                             | Maximum power dissipation            | -40  | 105                   | °C         |  |  |

|                    | version                                                                                      | Low power dissipation <sup>(4)</sup> | -40  | 125                   |            |  |  |

| TJ                 | Junction temperature range                                                                   | 6 suffix version                     | -40  | 105                   | °C         |  |  |

| IJ                 |                                                                                              | 7 suffix version                     | -40  | 125                   | - °C       |  |  |

1. To sustain a voltage higher than  $V_{DD}$ +0.3 V, the internal pull-up/pull-down resistors must be disabled.

2. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$  (see Section 7.5: Thermal characteristics).

3. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$  (see Section 7.5: Thermal characteristics).

4. In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.5: *Thermal characteristics*).

|                  |                         |                   |                   | V <sub>DDA</sub> = 2.4 V |                    |                                      |                    |      | V <sub>DDA</sub> = 3.6 V |         |                    |                |  |  |

|------------------|-------------------------|-------------------|-------------------|--------------------------|--------------------|--------------------------------------|--------------------|------|--------------------------|---------|--------------------|----------------|--|--|

| Symbol           | Parameter               | Conditions<br>(1) | f <sub>HCLK</sub> | Тур.                     | Ma                 | Max. @ T <sub>A</sub> <sup>(2)</sup> |                    |      | М                        | ax. @ T | 4 <sup>(2)</sup>   | Unit           |  |  |

|                  |                         |                   |                   | тур.                     | 25 °C              | 85 °C                                | 105 °C             | Тур. | 25 °C                    | 85 °C   | 105 °C             |                |  |  |

|                  |                         |                   | 72 MHz            | 224                      | 252 <sup>(3)</sup> | 265                                  | 269 <sup>(3)</sup> | 245  | 272 <sup>(3)</sup>       | 288     | 295 <sup>(3)</sup> |                |  |  |

|                  |                         |                   | 64 MHz            | 196                      | 225                | 237                                  | 241                | 214  | 243                      | 257     | 263                |                |  |  |

|                  |                         | D                 | 48 MHz            | 147                      | 174                | 183                                  | 186                | 159  | 186                      | 196     | 201                | -<br>-<br>- μΑ |  |  |

|                  | Supply                  |                   | 32 MHz            | 100                      | 126                | 133                                  | 135                | 109  | 133                      | 142     | 145                |                |  |  |

|                  | current in<br>Run/Sleep |                   | 24 MHz            | 79                       | 102                | 107                                  | 108                | 85   | 108                      | 113     | 116                |                |  |  |

| 1                | mode,                   |                   | 8 MHz             | 3                        | 5                  | 5                                    | 6                  | 4    | 6                        | 6       | 7                  |                |  |  |

| I <sub>DDA</sub> | code                    |                   | 1 MHz             | 3                        | 5                  | 5                                    | 6                  | 3    | 5                        | 6       | 6                  |                |  |  |

|                  | from Flash              |                   | 64 MHz            | 259                      | 288                | 304                                  | 309                | 285  | 315                      | 332     | 338                |                |  |  |

| or RAM           |                         |                   | 48 MHz            | 208                      | 239                | 251                                  | 254                | 230  | 258                      | 271     | 277                |                |  |  |

|                  |                         |                   | 32 MHz            | 162                      | 190                | 198                                  | 202                | 179  | 206                      | 216     | 219                |                |  |  |

|                  |                         |                   | 24 MHz            | 140                      | 168                | 175                                  | 178                | 155  | 181                      | 188     | 191                |                |  |  |

|                  |                         |                   | 8 MHz             | 62                       | 85                 | 88                                   | 89                 | 71   | 94                       | 96      | 98                 |                |  |  |

Table 27. Typical and maximum current consumption from the V<sub>DDA</sub> supply

Current consumption from the V<sub>DDA</sub> supply is independent of whether the peripherals are on or off. Furthermore when the PLL is off, I<sub>DDA</sub> is independent from the frequency.

2. Data based on characterization results, not tested in production.

3. Data based characterization results and tested in production with code executing from RAM.

|                               |                                                        |                                            |           | Typ. @V <sub>DD</sub> (V <sub>DD</sub> =V <sub>DDA</sub> ) |           |           |           |           | Max. <sup>(1)</sup>       |                           |                                |      |

|-------------------------------|--------------------------------------------------------|--------------------------------------------|-----------|------------------------------------------------------------|-----------|-----------|-----------|-----------|---------------------------|---------------------------|--------------------------------|------|

| Symbol                        | Parameter                                              | Conditions                                 | 2.0<br>V  | 2.4<br>V                                                   | 2.7<br>V  | 3.0<br>V  | 3.3<br>V  | 3.6<br>V  | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °<br>C | Unit |

|                               | Supply                                                 | Regulator in run mode, all oscillators OFF | 17.5<br>1 | 17.6<br>8                                                  | 17.8<br>4 | 18.1<br>7 | 18.5<br>7 | 19.3<br>9 | 30.6                      | 232.5                     | 612.2                          |      |

| current in<br>Stop mode       | Regulator in low-power<br>mode, all oscillators<br>OFF | 6.44                                       | 6.51      | 6.60                                                       | 6.73      | 6.96      | 7.20      | 20.0      | 246.4                     | 585.0                     | μA                             |      |

| Supply                        | LSI ON and IWDG ON                                     | 0.73                                       | 0.89      | 1.02                                                       | 1.14      | 1.28      | 1.44      | -         | -                         | -                         |                                |      |

| current in<br>Standby<br>mode | LSI OFF and IWDG<br>OFF                                | 0.55                                       | 0.66      | 0.75                                                       | 0.85      | 0.93      | 1.01      | 4.9       | 7.0                       | 7.9                       |                                |      |

### Table 28. Typical and maximum $V_{\text{DD}}$ consumption in Stop and Standby modes

1. Data based on characterization results, not tested in production unless otherwise specified.

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

| Symbol          | Parameter                  | Conditions <sup>(1)</sup>                                          | l/O toggling<br>frequency (f <sub>SW</sub> ) | Тур. | Unit |

|-----------------|----------------------------|--------------------------------------------------------------------|----------------------------------------------|------|------|

|                 |                            |                                                                    | 2 MHz                                        | 0.90 |      |

|                 |                            | V <sub>DD</sub> =3.3 V                                             | 4 MHz                                        | 0.93 |      |

|                 |                            | C <sub>ext</sub> = 0 pF                                            | 8 MHz                                        | 1.16 |      |

|                 |                            | $C = C_{INT} + C_{EXT} + C_{S}$                                    | $C = C_{INT} + C_{EXT} + C_S$ 18 MHz         | 1.60 |      |

|                 |                            |                                                                    | 36 MHz                                       | 2.51 |      |

|                 |                            |                                                                    | 2 MHz                                        | 0.93 |      |

|                 |                            | V <sub>DD</sub> = 3.3 V                                            | 4 MHz                                        | 1.06 |      |

|                 |                            | C <sub>ext</sub> = 10 pF                                           | 8 MHz                                        | 1.47 |      |

|                 |                            | $C = C_{INT} + C_{EXT} + C_S$                                      | 18 MHz                                       | 2.26 |      |

|                 |                            |                                                                    | 36 MHz                                       | 3.39 |      |

|                 |                            | $V_{DD} = 3.3 V$ $C_{ext} = 22 pF$ $C = C_{INT} + C_{EXT} + C_{S}$ | 2 MHz                                        | 1.03 |      |

|                 |                            |                                                                    | 4 MHz                                        | 1.30 |      |

| I <sub>SW</sub> | I/O current<br>consumption |                                                                    | 8 MHz                                        | 1.79 | mA   |

|                 |                            |                                                                    | 18 MHz                                       | 3.01 |      |

|                 |                            |                                                                    | 36 MHz                                       | 5.99 |      |

|                 |                            |                                                                    | 2 MHz                                        | 1.10 |      |

|                 |                            | V <sub>DD</sub> = 3.3 V                                            | 4 MHz                                        | 1.31 |      |

|                 |                            | C <sub>ext</sub> = 33 pF                                           | 8 MHz                                        | 2.06 |      |

|                 |                            | $C = C_{INT} + C_{EXT} + C_S$                                      | 18 MHz                                       | 3.47 |      |

|                 |                            |                                                                    | 36 MHz                                       | 8.35 |      |

|                 |                            |                                                                    | 2 MHz                                        | 1.20 |      |

|                 |                            | V <sub>DD</sub> = 3.3 V                                            | 4 MHz                                        | 1.54 |      |

|                 |                            | C <sub>ext</sub> = 47 pF                                           | 8 MHz                                        | 2.46 |      |

|                 |                            | $C = C_{INT} + C_{EXT} + C_S$                                      | 18 MHz                                       | 4.51 |      |

|                 |                            |                                                                    | 36 MHz                                       | 9.98 |      |

Table 34. Switching output I/O current consumption

1. CS = 5 pF (estimated value).

| Paripharal | Typical consumption <sup>(1)</sup> | Unit |  |  |  |  |  |

|------------|------------------------------------|------|--|--|--|--|--|

| Peripheral | I <sub>DD</sub>                    | Onit |  |  |  |  |  |

| CAN        | 31.3                               | -    |  |  |  |  |  |

| PWR        | 4.7                                | -    |  |  |  |  |  |

| DAC        | 15.4                               | -    |  |  |  |  |  |

| DAC2       | 8.6                                | -    |  |  |  |  |  |

| SPI1       | 8.2                                | -    |  |  |  |  |  |

#### Table 35. Peripheral current consumption (continued)

1. The power consumption of the analog part (I<sub>DDA</sub>) of peripherals such as ADC, DAC, Comparators, OpAmp etc. is not included. Refer to the tables of characteristics in the subsequent sections.

2. BusMatrix is automatically active when at least one master is ON (CPU or DMA1).

3. The APBx bridge is automatically active when at least one peripheral is ON on the same bus.

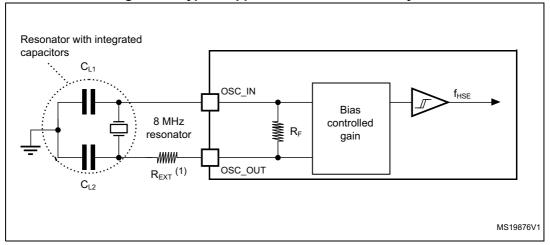

For C<sub>L1</sub> and C<sub>L2</sub>, it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 15*). C<sub>L1</sub> and C<sub>L2</sub> are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of C<sub>L1</sub> and C<sub>L2</sub>. PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing C<sub>L1</sub> and C<sub>L2</sub>.

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 41*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Table 41. LOL OSCINATOR CHARACTERISTICS ( $I_{SE} = 52.700$ KHz) |                                |                                                     |             |      |                         |      |  |  |  |  |

|------------------------------------------------------------------|--------------------------------|-----------------------------------------------------|-------------|------|-------------------------|------|--|--|--|--|

| Symbol                                                           | Parameter                      | Conditions <sup>(1)</sup>                           | Min.<br>(2) | Тур. | Max. <sup>(</sup><br>2) | Unit |  |  |  |  |

|                                                                  |                                | LSEDRV[1:0]=00<br>lower driving capability          | -           | 0.5  | 0.9                     |      |  |  |  |  |

|                                                                  |                                | LSEDRV[1:0]=10<br>medium low driving<br>capability  |             |      |                         |      |  |  |  |  |

| I <sub>DD</sub>                                                  | LSE current consumption        | LSEDRV[1:0]=01<br>medium high-driving<br>capability | -           | -    | 1.3                     | μA   |  |  |  |  |

|                                                                  |                                | LSEDRV[1:0]=11<br>higher-driving capability         | -           | -    | 1.6                     |      |  |  |  |  |

|                                                                  |                                | LSEDRV[1:0]=00<br>lower-driving capability          | 5           | -    | -                       |      |  |  |  |  |

| <i>.</i>                                                         | Oscillator<br>transconductance | LSEDRV[1:0]=10<br>medium low-driving<br>capability  | 8           | -    | -                       |      |  |  |  |  |

| 9m                                                               |                                | LSEDRV[1:0]=01<br>medium high-driving<br>capability | 15          | -    | -                       | µA/V |  |  |  |  |

|                                                                  |                                | LSEDRV[1:0]=11<br>higher-driving capability         | 25          | -    | -                       |      |  |  |  |  |

| t <sub>SU(LSE)</sub> <sup>(3)</sup>                              | Startup time                   | V <sub>DD</sub> is stabilized                       | -           | 2    | -                       | S    |  |  |  |  |

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer.

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

## 6.3.10 Memory characteristics

### Flash memory

The characteristics are given at  $T_A = -40$  to 105 °C unless otherwise specified.

| Symbol             | Parameter               | Conditions                      | Min. | Тур. | Max. <sup>(1)</sup> | Unit |

|--------------------|-------------------------|---------------------------------|------|------|---------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = -40 to +105 °C | 40   | 53.5 | 60                  | μs   |

| t <sub>ERASE</sub> | Page (2 KB) erase time  | $T_A = -40$ to +105 °C          | 20   | -    | 40                  | ms   |

| t <sub>ME</sub>    | Mass erase time         | $T_A = -40$ to +105 °C          | 20   | -    | 40                  | ms   |

| I <sub>DD</sub>    | Supply current          | Write mode                      | -    | -    | 10                  | mA   |

|                    |                         | Erase mode                      | -    | -    | 12                  | mA   |

Table 45. Flash memory characteristics

1. Guaranteed by design, not tested in production.

| Quantast         | Demonster      | <b>2</b>                                                                          |                     | 11      |  |

|------------------|----------------|-----------------------------------------------------------------------------------|---------------------|---------|--|

| Symbol           | Parameter      | Conditions                                                                        | Min. <sup>(1)</sup> | Unit    |  |

| N <sub>END</sub> | Endurance      | TA = –40 to +85 °C (6 suffix versions)<br>TA = –40 to +105 °C (7 suffix versions) | 10                  | kcycles |  |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                 | 30                  |         |  |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                | 10                  | Years   |  |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                               | 20                  |         |  |

1. Data based on characterization results, not tested in production.

2. Cycling performed over the whole temperature range.

## 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 47*. They are based on the EMS levels and classes defined in *"EMC design guide for ST microcontrollers"* application note (AN1709).

| Symbol Parameter |                                                                                         | Min. | Max.               | Unit |

|------------------|-----------------------------------------------------------------------------------------|------|--------------------|------|

| t <sub>AF</sub>  | t <sub>AF</sub> Maximum pulse width of spikes that are suppressed by the analog filter. |      | 260 <sup>(3)</sup> | ns   |

### Table 59. I<sup>2</sup>C analog filter characteristics<sup>(1)</sup>

1. Guaranteed by design, not tested in production.

2. Spikes with width below  $t_{AF}(min.)$  are filtered.

3. Spikes with width above  $t_{AF}(max.)$  are not filtered.

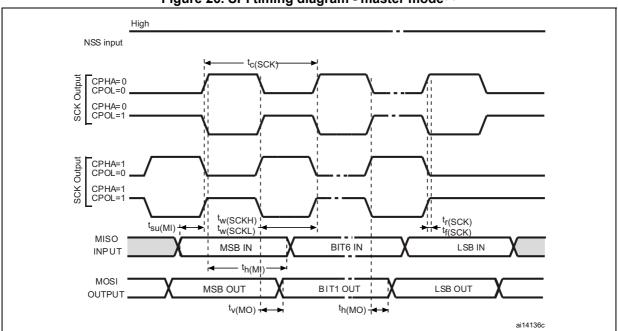

### **SPI characteristics**

Unless otherwise specified, the parameters given in *Table 55* for SPI are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 20: General operating conditions*.

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

| Symbol                | Parameter                                         | Conditions                               | Min     | Тур     | Max               | Unit |

|-----------------------|---------------------------------------------------|------------------------------------------|---------|---------|-------------------|------|

|                       |                                                   | Master mode 2.7 <v<sub>DD&lt;3.6</v<sub> |         |         | 24                |      |

|                       |                                                   | Master mode 2 <v<sub>DD&lt;3.6</v<sub>   |         |         | 18                |      |

| f <sub>SCK</sub>      | SPI clock frequency                               | Slave mode 2 <v<sub>DD&lt;3.6</v<sub>    | _       | _       | 24                | MHz  |

| 1/t <sub>c(SCK)</sub> |                                                   | Slave mode transmitter/full duplex       |         |         | 18 <sup>(2)</sup> |      |

|                       |                                                   | 2 <v<sub>DD&lt;3.6</v<sub>               |         |         |                   |      |

| DuCy(scк)             | Duty cycle of SPI clock<br>frequency Slave mode 3 |                                          | 30      | 50      | 70                | %    |

| t <sub>su(NSS)</sub>  | NSS setup time                                    | Slave mode, SPI presc = 2                | 4*Tpclk | -       | -                 |      |

| t <sub>h(NSS)</sub>   | NSS hold time                                     | Slave mode, SPI presc = 2                | 2*Tpclk | -       | -                 |      |

| t <sub>w(SCKH)</sub>  | SCK high and low time                             | Master mode                              | Tpclk-2 | Tpclk   | Tpclk+2           |      |

| t <sub>w(SCKL)</sub>  |                                                   |                                          |         | 1 point |                   |      |

| t <sub>su(MI)</sub>   | Data input setup time                             | Master mode                              | 0       | -       | -                 |      |

| t <sub>su(SI)</sub>   |                                                   | Slave mode                               | 3       | -       | -                 |      |

| t <sub>h(MI)</sub>    | Data input hold time                              | Master mode                              | 5       | -       | -                 |      |

| t <sub>h(SI)</sub>    |                                                   | Slave mode                               | 1       | -       | -                 | ns   |

| t <sub>a(SO)</sub>    | Data output access time                           | Slave mode                               | 10      | -       | 40                |      |

| t <sub>dis(SO)</sub>  | Data output disable time                          | Slave mode                               | 10      | -       | 17                |      |

| t <sub>v(SO)</sub>    |                                                   | Slave mode 2.7 <v<sub>DD&lt;3.6V</v<sub> | -       | 12      | 20                |      |

|                       | Data output valid time                            | Slave mode 2 <v<sub>DD&lt;3.6V</v<sub>   | -       | 12      | 27.5              | 1    |

| t <sub>v(MO)</sub>    |                                                   | Master mode                              | -       | 1.5     | 5                 |      |

| t <sub>h(SO)</sub>    | Data output hold time                             | Slave mode                               | 7.5     | -       | -                 | 1    |

| t <sub>h(MO)</sub>    |                                                   | Master mode                              | 0       | -       | -                 | 1    |

#### Table 60. SPI characteristics<sup>(1)</sup>

1. Data based on characterization results, not tested in production.

Maximum frequency in Slave transmitter mode is determined by the sum of tv(SO) and tsu(MI) which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having tsu(MI) = 0 while Duty(SCK) = 50%.

Figure 26. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at  $0.5V_{DD}$  and with external C<sub>L</sub> = 30 pF.

#### CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

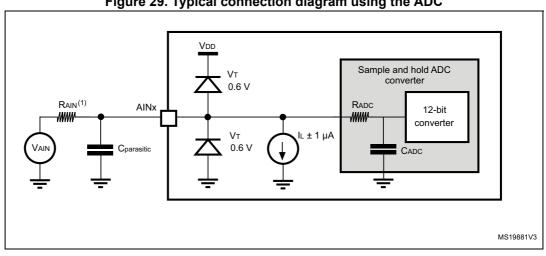

### 6.3.18 ADC characteristics

Unless otherwise specified, the parameters given in *Table 61* to *Table 64* are guaranteed by design, with conditions summarized in *Table 20*.

| Symbol           | Parameter                     | Conditions                     | Min. | Тур.   | Max.   | Unit |

|------------------|-------------------------------|--------------------------------|------|--------|--------|------|

| V <sub>DDA</sub> | Analog supply voltage for ADC | -                              | 2    | -      | 3.6    | V    |

|                  |                               | Single ended mode, 5<br>MSPS,  | -    | 1011.3 | 1172.0 |      |

|                  |                               | Single ended mode, 1<br>MSPS   | -    | 214.7  | 322.3  |      |

|                  | ADC current consumption       | Single ended mode, 200<br>KSPS | -    | 54.7   | 81.1   |      |

| IDDA             | (Figure 27)                   | Differential mode,5<br>MSPS,   | -    | 1061.5 | 1243.6 | μA   |

|                  |                               | Differential mode, 1<br>MSPS   | -    | 246.6  | 337.6  |      |

|                  |                               | Differential mode, 200<br>KSPS | -    | 56.4   | 83.0   |      |

Table 61. ADC characteristics

Figure 29. Typical connection diagram using the ADC

1. Refer to Table 61 for the values of RAIN.

$C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high  $C_{parasitic}$  value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced. 2.

### **General PCB design guidelines**

Power supply decoupling should be performed as shown in *Figure 10: Power-supply* scheme. The 10 nF capacitor should be ceramic (good quality) and it should be placed as close as possible to the chip.

#### 6.3.19 **DAC electrical specifications**

| Symbol                           | Parameter                                  | Conditions                                                                                                            |     | Тур. | Max.                    | Unit |

|----------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|------|-------------------------|------|

| V <sub>DDA</sub>                 | Analog supply voltage                      | -                                                                                                                     |     | -    | 3.6                     | V    |

| R <sub>LOAD</sub> <sup>(1)</sup> | Resistive load                             | DAC output buffer ON (to $V_{SSA}$ )                                                                                  | 5   | -    | -                       | kΩ   |

| R <sub>LOAD</sub> <sup>(1)</sup> | Resistive load                             | DAC output buffer ON (to V <sub>DDA</sub> )                                                                           | 25  | -    | -                       | kΩ   |

| R <sub>O</sub> <sup>(1)</sup>    | Output impedance                           | DAC output buffer OFF                                                                                                 | -   | -    | 15                      | kΩ   |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                            | DAC output buffer ON                                                                                                  |     | -    | 50                      | pF   |

| V <sub>DAC,OUT</sub> (           | Voltage on DAC_OUT                         | Corresponds to 12-bit input code (0x0E0) to (0xF1C) at $V_{DDA}$ = 3.6 V and (0x155) and (0xEAB) at $V_{DDA}$ = 2.4 V | 0.2 | -    | V <sub>DDA</sub> – 0.2  | v    |

|                                  |                                            | DAC output buffer OFF                                                                                                 | -   | 0.5  | V <sub>DDA</sub> - 0.2  | mV   |

|                                  |                                            |                                                                                                                       | -   | -    | V <sub>DDA</sub> - 1LSB | V    |

| I <sub>DDA</sub> <sup>(3)</sup>  | DAC DC current<br>consumption in quiescent | With no load, middle code (0x800) on the input                                                                        | -   | -    | 380                     | μA   |

|                                  | mode <sup>(2)</sup>                        | With no load, worst code (0xF1C) on the input.                                                                        | -   | -    | 480                     | μA   |

#### Table 66. DAC characteristics

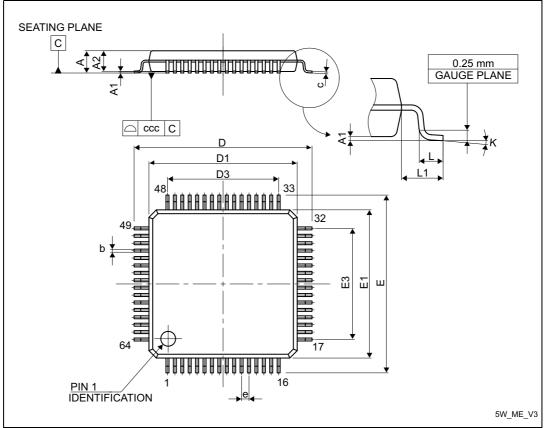

## 7.4 LQFP64 package information

LQFP64 is a 64-pin, 10 x 10 mm low-profile quad flat package.

Figure 39. LQFP64 package outline

1. Drawing is not to scale.

| Sympol | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур    | Мах   | Min                   | Тур    | Мах    |

| А      | -           | -      | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |

| D      | 11.800      | 12.000 | -     | -                     | 0.4724 | -      |

| D1     | 9.800       | 10.000 | -     | -                     | 0.3937 | -      |

| E      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| E1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

| е      | -           | 0.500  | -     | -                     | 0.0197 | -      |

# 9 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11-Apr-2014 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9-Dec-2014  | 2        | Updated:<br>Table 73: Package thermal characteristics: remove Note 1.<br>Table 17: Voltage characteristics: added line in VIN<br>Table 35: Low-power mode wakeup timings: updated Max<br>values<br>Table 40: HSI oscillator characteristics (Accuracy of the<br>oscillator)<br>Table 40: HSI oscillator characteristics (Accuracy of the<br>oscillator)<br>Table 54: TIMx characteristics<br>Table 54: TIMx characteristics<br>Table 59: ADC characteristics<br>Table 54: Peripheral current consumption<br>Table 2: STM32F303x6/8 family device features and<br>peripherals count<br>Figure 17: HSI oscillator accuracy characterization results for<br>soldered parts<br>Updated notes of Table 31: Typical current consumption in<br>Run mode, code with data processing running from Flash and<br>Table 32: Typical current consumption in Sleep mode, code<br>running from Flash or RAM. |

| 09-May-2015 | 4        | Updated Section Table 14.: STM32F303x6/8 pin definitions<br>and Section Table 15.: Alternate functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2-Feb-2015  | 3        | Updated:<br>Figure 1: STM32F303x6/8 block diagram<br>Table 40: HSE oscillator characteristics<br>Table 45: Flash memory characteristics<br>Added Figure 13: High-speed external clock source AC timing<br>diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 05-Oct-2016 | 5        | Updated:<br>Section Table 66.: DAC characteristics, Section Table 61.:<br>ADC characteristics, Table 55: NRST pin characteristics,<br>Figure 2: Clock tree, Table 14: STM32F303x6/8 pin<br>definitions, Table 68: Operational amplifier characteristics,<br>Figure 20: 5V- tolerant (FT and FTf) I/O input characteristics -<br>CMOS port, Table 24: Embedded internal reference voltage,<br>Table 41: LSE oscillator characteristics (fLSE = 32.768 kHz).<br>Added:<br>Table 37: Wakeup time using USART.                                                                                                                                                                                                                                                                                                                                                                                    |