Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

#### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application charific microcontrollars are angineered to

#### Details

⊡XFI

| Detalls                 |                                                                                 |

|-------------------------|---------------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                        |

| Applications            | Automotive                                                                      |

| Core Processor          | External                                                                        |

| Program Memory Type     | External Program Memory                                                         |

| Controller Series       | -                                                                               |

| RAM Size                | 8K x 8                                                                          |

| Interface               | Parallel Host, SPI                                                              |

| Number of I/O           | -                                                                               |

| Voltage - Supply        | 3V ~ 5.5V                                                                       |

| Operating Temperature   | -40°C ~ 125°C (TA)                                                              |

| Mounting Type           | Surface Mount                                                                   |

| Package / Case          | 64-LQFP                                                                         |

| Supplier Device Package | 64-LQFP (10x10)                                                                 |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/mb88121cpmc1-gs-n2e2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# FlexRay ASSP

# MB88121

| Pin No. | Pin name    | Circuit type | Function                                                                                                                                                                            |

|---------|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | ALE         |              | Input pin for the address latch enable input (high active).<br>This function is enabled in the multiplexed parallel modes for<br>16FX and for other devices to be defined later.    |

| 22      | AS          | с            | Input pin for the address strobe input (low active).<br>This function is enabled in the multiplexed parallel modes. Timing<br>meets FR core devices (460 series) and other devices. |

|         | INT2        |              | Output pin for the Interrupt 2 output.<br>This function is enabled in 16-bit non-multiplexed parallel mode.                                                                         |

|         | -           |              | This pin is Hi-Z in in SPI mode.                                                                                                                                                    |

| 23      | MT/NC       | В/-          | MB88121B/C: Debug pin; Macrotick start output, when function is<br>disabled, this pin outputs 'L'-Level<br>MB88121(A): Do not connect!                                              |

| 24      | RXDB        | A            | Input pin for the data receiver input channel B.                                                                                                                                    |

| 25      | TXENB       | В            | Output pin for the transmission enable output channel B.                                                                                                                            |

| 26      | TXDB        | В            | Output pin for the data transmitter output channel B.                                                                                                                               |

| 27      | RDY         | В            | Output pin for the ready output.<br>This function is enabled in all parallel modes.                                                                                                 |

|         | -           |              | This pin is Hi-Z in SPI mode.                                                                                                                                                       |

| 28-30   | MDE2 - MDE0 | А            | Input pins for the extended mode selection.                                                                                                                                         |

| 31      | DMA_REQ     | В            | Output pin for the DMA request output (MB88121A/B/C only).<br>On MB88121, this pin outputs "L" level.<br>This function is enabled in all parallel modes                             |

|         | -           | В            | This pin is Hi-Z in SPI mode.                                                                                                                                                       |

| 34      | INT1        | В            | Output pin for the Interrupt 1 output.                                                                                                                                              |

|         | A10         |              | Input pin for the address bus.<br>This function is enabled in 16-bit non-multiplexed parallel mode.                                                                                 |

| 35      | 35 INT2     |              | Output pin for the Interrupt 2 output.<br>This function is enabled in 16-bit multiplexed parallel mode.                                                                             |

|         | -           |              | This pin is Hi-Z in SPI mode.                                                                                                                                                       |

|         | A9          |              | Input pin for the address bus.<br>This function is enabled in 16-bit non-multiplexed parallel mode.                                                                                 |

| 36      | INT3        | С            | Output pin for the Interrupt 3 output.<br>This function is enabled in 16-bit multiplexed parallel mode.                                                                             |

|         | -           |              | This pin is Hi-Z in SPI mode.                                                                                                                                                       |

| 07      | A8          |              | Input pin for the address bus.<br>This function is enabled in 16-bit non-multiplexed multiplexed<br>parallel mode.                                                                  |

| 37      | INT4        | С            | Output pin for the Interrupt 4 output<br>This function is enabled in 16-bit multiplexed parallel mode                                                                               |

|         | -           |              | This pin is Hi-Z inSPI mode.                                                                                                                                                        |

| Pin No. | Pin name | Circuit type | Function                                                                                                                                                                                    |  |  |  |  |

|---------|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|         | A7       |              | Input pins for the address bus.<br>This function is enabled in 16-bit non-multiplexed parallel mode.                                                                                        |  |  |  |  |

| 38      | MBSU_TX1 | с            | MB88121B/C: Debug pin, when function is disabled, this pin out-<br>puts 'L'-Level<br>MB88121(A): Not supported.<br>This function is enabled in 16-bit multiplexed parallel and SPI<br>mode. |  |  |  |  |

|         | A6       |              | Input pins for the address bus.<br>This function is enabled in 16-bit non-multiplexed parallel mode.                                                                                        |  |  |  |  |

| 39      | MBSU_RX1 | с            | MB88121B/C: Debug pin, when function is disabled, this pin out-<br>puts 'L'-Level<br>MB88121(A): Not supported.<br>This function is enabled in 16-bit multiplexed parallel and SPI<br>mode. |  |  |  |  |

|         | A5       |              | Input pin for the address bus.<br>This function is enabled 16-bit non-multiplexed parallel modes.                                                                                           |  |  |  |  |

| 40      | SCK      | A            | Input pin for the serial clock input.<br>This function is enabled in SPI mode.                                                                                                              |  |  |  |  |

|         | -        | _            | This pin is unused in 16-bit multiplexed parallel modes.                                                                                                                                    |  |  |  |  |

|         | A4       | A            | Input pin for the address bus.<br>This function is enabled in 16-bit non-multiplexed parallel modes.                                                                                        |  |  |  |  |

| 41      | SDI      |              | Input pin for the serial data input.<br>This function is enabled in SPI mode.                                                                                                               |  |  |  |  |

|         | -        |              | This pin is unused in 16-bit multiplexed parallel modes.                                                                                                                                    |  |  |  |  |

|         | A3       |              | Input pin for the address bus.<br>This function is enabled in 16-bit non-multiplexed parallel modes.                                                                                        |  |  |  |  |

| 42      | SDO      | с            | Output pin for the serial data output.<br>When CS is "H" SDO is High-Z.<br>This function is enabled in SPI mode.                                                                            |  |  |  |  |

|         | -        |              | This pin is Hi-Z in 16-bit multiplexed parallel modes.                                                                                                                                      |  |  |  |  |

| 13      | A2       | - A          | Input pin for the address bus.<br>This function is enabled in 16-bit non-multiplexed parallel modes.                                                                                        |  |  |  |  |

| 45      | 43 -     |              | This pin is unused in 16-bit multiplexed parallel mode and in SPI mode.                                                                                                                     |  |  |  |  |

|         | A1       |              | Input pin for the address bus.<br>This function is enabled in 16-bit non-multiplexed parallel modes.                                                                                        |  |  |  |  |

| 44      | MBSU_TX2 | с            | MB88121B/C: Debug pin, when function is disabled, this pin out-<br>puts 'L'-Level<br>MB88121(A): Not supported.<br>This function is enabled in 16-bit multiplexed parallel and SPI<br>mode. |  |  |  |  |

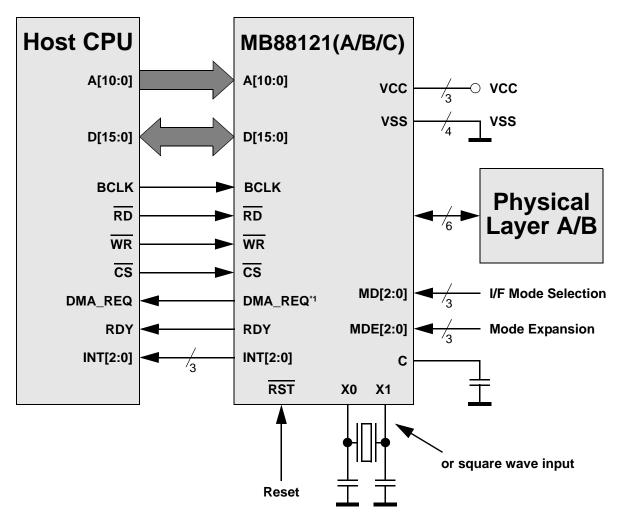

## Connection to Host CPU in 16-bit non-multiplexed Mode

\*1: MB88121A/B/C only

(Continued)

| Address            | Symbol | Name                          | Reset                                         | Access |

|--------------------|--------|-------------------------------|-----------------------------------------------|--------|

|                    |        | CC Control Registers          |                                               |        |

| 0x0080             | SUCC   | SUC Configuration Register 1  | MB88121: 0C40 0000<br>MB88121A/B/C: 0C40 1000 | r/w    |

| 0x0084             | SUCC2  | SUC Configuration Register 2  | MB88121: 0100 05A4<br>MB88121A/B/C: 0100 0504 | r/w    |

| 0x0088             | SUCC3  | SUC Configuration Register 3  | 0000 0011                                     | r/w    |

| 0x008C             | NEMC   | NEM Configuration Register    | 0000 0000                                     | r/w    |

| 0x0090             | PRTC1  | PRT Configuration Register 1  | MB88121: 084C 0005<br>MB88121A/B/C: 084C 0633 | r/w    |

| 0x0094             | PRTC2  | PRT Configuration Register 2  | MB88121: 0F2D 0E0E<br>MB88121A/B/C:0F2D 0A0E  | r/w    |

| 0x0098             | MHDC   | MHD Configuration Register    | MB88121: 0001 0000<br>MB88121A/B/C: 0000 0000 | r/w    |

| 0x009C             | -      | reserved (1)                  | 0000 0000                                     | r      |

| 0x00A0             | GTUC1  | GTU Configuration Register 1  | MB88121: 0000 02D0<br>MB88121A/B/C: 0000 0280 | r/w    |

| 0x00A4             | GTUC2  | GTU Configuration Register 2  | MB88121: 0002 000C<br>MB88121A/B/C: 0002 000A | r/w    |

| 0x00A8             | GTUC3  | GTU Configuration Register 3  | MB88121: 0001 0000<br>MB88121A/B/C: 0202 0000 | r/w    |

| 0x00AC             | GTUC4  | GTU Configuration Register 4  | MB88121: 000A 0009<br>MB88121A/B/C: 0008 0007 | r/w    |

| 0x00B0             | GTUC5  | GTU Configuration Register 5  | MB88121: 0A01 0000<br>MB88121A/B/C: 0E00 0000 | r/w    |

| 0x00B4             | GTUC6  | GTU Configuration Register 6  | 0002 0000                                     | r/w    |

| 0x00B8             | GTUC7  | GTU Configuration Register 7  | MB88121: 0002 0005<br>MB88121A/B/C: 0002 0004 | r/w    |

| 0x00BC             | GTUC8  | GTU Configuration Register 8  | 0000 0002                                     | r/w    |

| 0x00C0             | GTUC9  | GTU Configuration Register 9  | MB88121: 0001 0101<br>MB88121A/B/C: 0000 0101 | r/w    |

| 0x00C4             | GTUC10 | GTU Configuration Register 10 | MB88121: 0002 0001<br>MB88121A/B/C: 0002 0005 | r/w    |

| 0x00C8             | GTUC11 | GTU Configuration Register 11 | 0000 0000                                     | r/w    |

| 0x00CC -<br>0x00FC | -      | reserved (13)                 | 0000 0000                                     | r      |

# FlexRay ASSP

# MB88121

| Bit                   | Name                                        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                             |   |   |                             |  |  |  |

|-----------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---|---|-----------------------------|--|--|--|

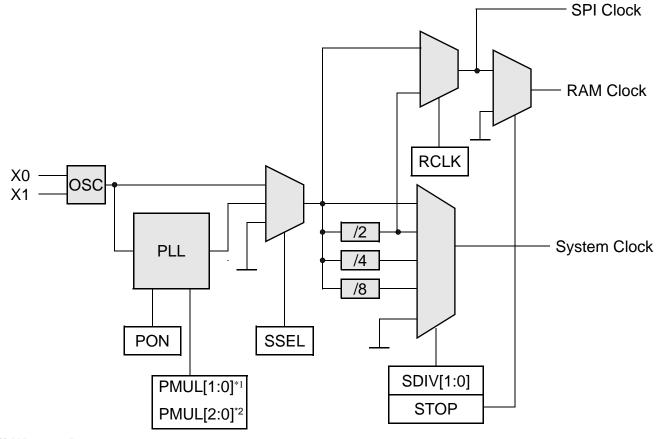

| bit 11<br>bit3 – bit2 | PMUL[2:0]:<br>PLL Multiplier Selec-<br>tion | These bits control the PLL multiplier. These bits must set up so that the PLL clock is set to 80MHz.<br>In MB88121 and MB88121A, the functionality of the PLL is not guaranteed.                                                                                                                                                                                                                                                                                                                                                                                                                                          |                             |   |   |                             |  |  |  |

|                       |                                             | For MB88121B/C, the evaluation of the PLL performance is pending. For thi reason, do not use other settings than PMUL[1:0] = "11".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             |   |   |                             |  |  |  |

|                       |                                             | PMUL[2] PMUL[1] PMUL[0] Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                             |   |   |                             |  |  |  |

|                       |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                           | 0 | 0 | X0/X1 (4MHz) x 20 (80MHz)   |  |  |  |

|                       |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                           | 0 | 1 | X0/X1 (5MHz) x 16 (80MHz)   |  |  |  |

|                       |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                           | 1 | 0 | X0/X1 (8MHz) x 10 (80MHz)   |  |  |  |

|                       |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                           | 1 | 1 | X0/X1 (10MHz) x 8 (80MHz)   |  |  |  |

|                       |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                           | 0 | 0 | X0/X1 (16MHz) x 5 (80MHz)*1 |  |  |  |

|                       |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | X0/X1 (20MHz) x 4 (80MHz)*1 |   |   |                             |  |  |  |

|                       |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | reserved                    |   |   |                             |  |  |  |

|                       |                                             | 1 1 1 1 reserve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                             |   |   |                             |  |  |  |

|                       |                                             | These bits must be changed before PON bit is set to "1".<br>When 16 bit parallel bus and external clock are used(MD2="1", M<br>MD0="1"), the clock for X0/X1 pins can be used from 4MHz to 20<br>When 16 bit parallel bus and oscillator are used(MD2="1", MD1="<br>), the clock for X0/X1 pins can be used from 4MHz to 8MHz.<br>When serial bus is used(MD="1", MD1="1", MD0="0") on externa<br>clock for X0/X1 pins can't be used at 16MHz and 20MHz, and on o<br>clock for X0/X1 pins can be used from 4MHz to 8MHz. And PMU<br>shouldn't be set to "100" and "101".                                                  |                             |   |   |                             |  |  |  |

| bit1                  | SSEL:<br>System Clock<br>Selection          | <ul> <li>Setting to be resered is prohibition.</li> <li>This bit selects the system clock.<br/>"0": Select the clock of X0/X1<br/>"1": Select the clock of PLL</li> <li>In MB88121 and MB88121A, the functionality of the PLL is not guaranteed.</li> <li>&lt;<note>&gt;</note></li> <li>Must be changed into "1" from "0" after "1" is set as a PON bit and PLL<br/>lock-up time (600us) passes.</li> <li>If the oscillater of PLL is stopped, PON bit is set to "0" after this bit is<br/>changed to "0".</li> <li>When FlexRay controller can receive or transmit data, these bits must not<br/>be changed.</li> </ul> |                             |   |   |                             |  |  |  |

Clock supply circuit of MB88121B/C for SPI mode (MD[2:0] = 1 1 0)

<sup>\*1</sup> MB88121B <sup>\*2</sup> MB88121C

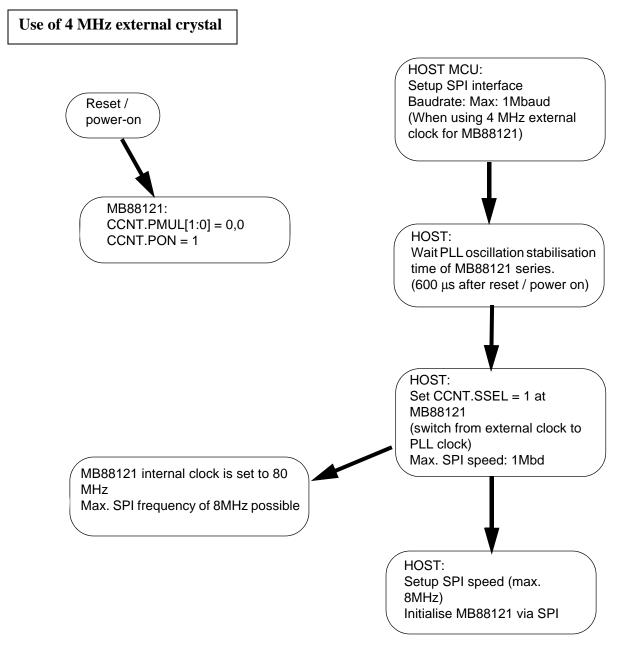

### Clock Settings after power-on / reset in SPI mode

| Bit          | Name                                  | Function                                                                                                                                                                                                                                                                                                                           |  |  |  |

|--------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| bit15 - bit4 | RSV: Reserved                         | These bits are reserved. "0" is read. Write "0".                                                                                                                                                                                                                                                                                   |  |  |  |

| bit3         | SWAP: Byte Swap Enable Bit            | This bit selects whether to exchange the data handled with input/<br>output buffer by each byte.In the case of MB88121A and<br>MB88121B, this bit is dealt with for "0".                                                                                                                                                           |  |  |  |

|              |                                       | When this bit set to "0":                                                                                                                                                                                                                                                                                                          |  |  |  |

|              |                                       | In this case, writing and reading are done as it is.                                                                                                                                                                                                                                                                               |  |  |  |

|              |                                       | When this bit set to "1":                                                                                                                                                                                                                                                                                                          |  |  |  |

|              |                                       | <460, 360 mode>                                                                                                                                                                                                                                                                                                                    |  |  |  |

|              |                                       | When writing it in the input buffer, the data of bit 7-0 is written in bit31-24 in the input buffer. The data of bit 15-8 is written in bit23-16 in the input buffer. The data of bit 23-16 is written in bit15-8 in the input buffer. The data of bit 31-24 is written in bit7-0 in the input buffer.                             |  |  |  |

|              |                                       | When it is read from the input/output buffer, the data of bit 7-0 of the input/output buffer is read as bit 31-24. The data of bit 15-8 of the input/output buffer is read as bit 23-16. The data of bit 23-16 of the input/output buffer is read as bit 15-8. The data of bit 31-24 of the input/output buffer is read as bit 7-0 |  |  |  |

|              |                                       | <16FX mode>                                                                                                                                                                                                                                                                                                                        |  |  |  |

|              |                                       | When writing it in the input buffer, the data of bit 7-0 is written in bit15-8 in the input buffer. The data of bit 15-8 is written in bit7-0 in the input buffer. The data of bit 23-16 is written in bit31-24 in the input buffer. The data of bit 31-24 is written in bit23-16 in the input buffer.                             |  |  |  |

|              |                                       | When it is read from the input/output buffer, the data of bit 7-0 of the input/output buffer is read as bit 15-8. The data of bit 15-8 of the input/output buffer is read as bit 7-0. The data of bit 23-16 of the input/output buffer is read as bit 31-24. The data of bit 31-24 of the input/output buffer is read as bit 23-16 |  |  |  |

|              |                                       | < <note>&gt;<br/>This bit is invalid serial bus mode.<br/>This bit is valid for the 16-bit parallel (non-multiplex and multi-<br/>plex).</note>                                                                                                                                                                                    |  |  |  |

| bit2         | DMAINV: DMA Request Level<br>Inverted | This bit controls the DMA request level.<br>"0": Active level for DMA request is "H"<br>"1": Active level for DMA request is "L"                                                                                                                                                                                                   |  |  |  |

|              |                                       | < <note>&gt;<br/>It is valid when DMAOE bit is "1".</note>                                                                                                                                                                                                                                                                         |  |  |  |

| bit1         | DMARE: DMA Request enable             | This bit controls the DMA request.<br>"0": Disabled<br>"1": Enabled                                                                                                                                                                                                                                                                |  |  |  |

|              |                                       | < <note>&gt;<br/>It is valid when DMAOE bit is "1".</note>                                                                                                                                                                                                                                                                         |  |  |  |

| Bit      | Name                                         | Function                                                                                                                                                                                                  |

|----------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 31-8 | reserved                                     | These bits are reserved. "0" is read. Write "0".                                                                                                                                                          |

|          |                                              | This bit clears the LVD18 bit by writing "1"                                                                                                                                                              |

| Bit 7    | LVD18CL: LVD18 clear bit                     | "0": LVD18 Flag not changed<br>"1": LVD18 Flag cleared to "0"<br>< <note>&gt;:</note>                                                                                                                     |

|          |                                              | This Bit is always read as "0"                                                                                                                                                                            |

|          |                                              | This bit clears the LVD5 bit by writing "1"                                                                                                                                                               |

| Bit 6    | LVD5CL: LVD5 clear bit                       | "0": LVD5 Flag not changed<br>"1": LVD5 Flag cleared to "0"<br>< <note>&gt;:</note>                                                                                                                       |

|          |                                              | This Bit is always read as "0"                                                                                                                                                                            |

| Bit 5    | TINTE1: TINT1 enable bit                     | This bit enables the Timer interrupt 1 (TINT1) signal output via the corresponding INT pin.                                                                                                               |

| Bit 5    |                                              | "0": Interrupt disabled<br>"1": Interrupt enabled                                                                                                                                                         |

| Bit 4    | TINTE0: TINT0 enable bit                     | This bit enables the Timer interrupt 0 (TINT0) signal output via the corresponding INT pin.                                                                                                               |

| Bit 4    |                                              | "0": Interrupt disabled<br>"1": Interrupt enabled                                                                                                                                                         |

| Bit 3    | LVD18E: Interrupt enable bit for             | This bit enables the LVD18 flag signal output via the corresponding INT pin:                                                                                                                              |

| Dit 5    | LVD18                                        | "0": Interrupt disabled<br>"1": Interrupt enabled                                                                                                                                                         |

| Dit 2    | LVD5E: Interrupt enable bit for              | This bit enables the LVD5 flag signal output via the corresponding INT pin:                                                                                                                               |

| Bit 2    | LVD5                                         | "0": Interrupt disabled<br>"1": Interrupt enabled                                                                                                                                                         |

| Bit 1    | LVD18: Low voltage detector Flag<br>for 1.8V | This bit indicates a lov voltage detection of internal 1.8V:<br>"0": No undervoltage occured<br>"1": undervoltage occured<br>< <note>&gt;<br/>This Flag is cleared by writing "1" to Bit 7 LVD18CL</note> |

|          | LVD5: Low voltage detector Flag              | This bit indicates a lov voltage detection of Vcc input volt-<br>age:<br>"0": No undervoltage occured                                                                                                     |

| Bit 0    | for 5V                                       | "1": undervoltage occured                                                                                                                                                                                 |

|          |                                              | < <note>&gt;</note>                                                                                                                                                                                       |

|          |                                              | This Flag is cleared by writing "1" to Bit 6 LVD5CL                                                                                                                                                       |

Note: In 16/bit none-multiplexed mode the LVD5, LVD18, TINT0 and TINT1 are assigned to INT2 pin. In 16 bit multiplexed or SPI mode the assignment is: TINT0 to INT2; TINT1 to INT3, LVD5 and LVD18 to INT4 pin. See also chapter "Handling Devices" topic 10 Interrupt pin assignment

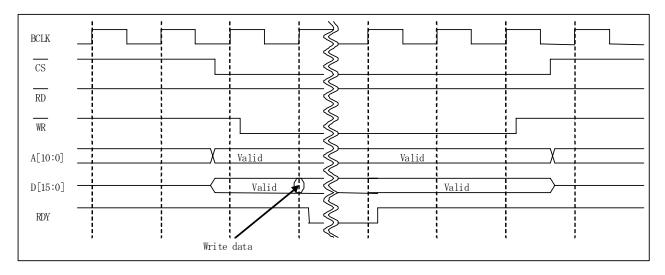

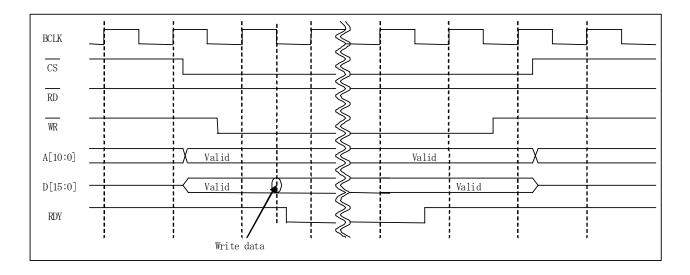

### Write timing in FR460 mode

When the CS pin and the WR pin become "L", the data on the D[15:0] pins is written to a temporary register at the next rising edge of the BCLK pin, and the RDY pin becomes "L", causing the CPU to wait. When the data of the temporary register is written to the register addressed by the A[10:0] pins, the RDY pin becomes "H".

Write timing in FR360 mode

When the CS pin and the WR pin become "L", the data on the D[15:0] pins is written to a temporary register at the next falling edge of the BCLK pin, and the RDY pin becomes "L", causing the CPU to wait. When the data of the temporary register is written to the register addressed by the A[10:0] pins, the RDY pin becomes "H".

### 4. The write timing for the register

The FlexRay Controller registers have a width of 32bit. A 32bit temporary read register is available to save write data. In the case of writing in 16bit multiplexted parallel bus mode, the temporary register is written as follows.

FR460 mode: Data of the D[15:11] pins and AD[10:0] pins is written to the 16bit upper temporary register in case of the first write access, and it is written to the 16 bit lower temporary register in case of the second write access. Then the data of the temporary register is written to the 16bit lower temporary register in case of the first write access, and it is written to the 16 bit lower temporary register of FlexRay controller.

16FX mode: Data of the D[15:11] pins and AD[10:0] pins is written to the 16bit lower temporary register in case of the first write access, and it is written to the 16 bit upper temporary register in case of the second write access. Then the data of the temporary register is written to the 16bit lower temporary register in case of the first write access, and it is written to the 16 bit upper temporary register in case of the second write access. Then the data of the temporary register is written to the register of FlexRay controller.

Write operation in FR460 mode

Write operation in 16FX mode

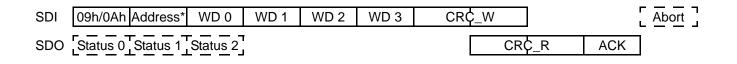

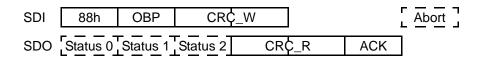

### WR: Write one Word, Command Byte = 09h/0Ah

\*: A[10] = bit 0 of command byte, A[9:2] = Address byte, A[1:0] = 00.

After successful check of CRC\_W, ACK=FFh is sent. Otherwise, ACK=00h is sent. If ACK=FFh was sent, 32bit of data WD[3:0] is written to the address A[10:0] if CS has a rising edge immediately after ACK. If there is no rising CS edge immediately after ACK, data is not written. The SPI master can transmit an extra byte (Abort) after it has received the ACK. MB88121 will detect clock edges when it expects a rising CS edge and will not write the data.

Payload:4 bytesCommand length:10 bytesOverhead:150%Efficiency:40%

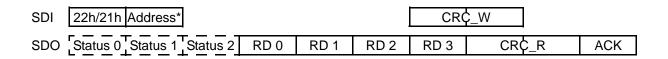

### RD: Read one Word, Command Byte = 22h/21h

\*: A[10] = bit 0 of command byte, A[9:2] = Address byte, A[1:0] = 00.

Data RD[3:0] is read from address A[10:0]. After successful check of CRC\_W, ACK=FFh is sent. Otherwise, ACK=00h is sent.

| 4 bytes  |

|----------|

| 10 bytes |

| 150%     |

| 40%      |

|          |

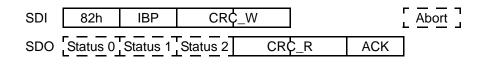

### WIP: Write Input Buffer Pointer, Command Byte = 82h

After successful check of CRC\_W, ACK=FFh is sent. Otherwise, ACK=00h is sent. If ACK=FFh was sent, IBP is written if CS has a rising edge immediately after ACK. If there is no rising CS edge immediately after ACK, IBP is not written. The SPI master can transmit an extra byte (Abort) after it has received the ACK. MB88121 will detect clock edges when it expects a rising CS edge and will not write IBP. IBP is used by commands WBC, RBIWBC and RBCWBC.

| Payload:        | 0 bytes |

|-----------------|---------|

| Command length: | 6 bytes |

| Overhead:       | 6 bytes |

| Efficiency:     | 0%      |

### WOP: Write Output Buffer Pointer, Command Byte = 88h

After successful check of CRC\_W, ACK=FFh is sent. Otherwise, ACK=00h is sent. If ACK=FFh was sent, OBP is written if CS has a rising edge immediately after ACK. If there is no rising CS edge immediately after ACK, OBP is not written. The SPI master can transmit an extra byte (Abort) after it has received the ACK. MB88121 will detect clock edges when it expects a rising CS edge and will not write OBP. OBP is used by commands RBC, RBCWBI and RBCWBC.

| Payload:        | 0 bytes |

|-----------------|---------|

| Command length: | 6 bytes |

| Overhead:       | 6 bytes |

| Efficiency:     | 0%      |

### 4. Default Status Read Out

With this protocol MB88121 transmits 24 bits of status information at the beginning of each command frame. **Status Byte Overview:**

#### STATUS 0

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| ST07 | ST06 | ST05 | ST04 | ST03 | ST02 | ST01 | ST00 |

STATUS 1

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| ST17 | ST16 | ST15 | ST14 | ST13 | ST12 | ST11 | ST10 |

STATUS 2

7 6 5 4 3 2 1 0 ST27 ST26 ST25 ST24 ST23 ST22 ST21 ST20

#### STATUS 0 Definition

| Bit | Name | Function                                                                                                                                                                                                                                                                                                          |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ST07 | reserved                                                                                                                                                                                                                                                                                                          |

| 6   | ST06 | reserved                                                                                                                                                                                                                                                                                                          |

| 5   | ST05 | reserved                                                                                                                                                                                                                                                                                                          |

| 4   | ST04 | reserved                                                                                                                                                                                                                                                                                                          |

| 3   | ST03 | reserved                                                                                                                                                                                                                                                                                                          |

| 2   | ST02 | reserved                                                                                                                                                                                                                                                                                                          |

| 1   | ST01 | <ul> <li>eray_obusy</li> <li>'1': Output buffer busy flag. If it is set, the output buffer is busy (0x600-0x6fc).Write access to OBCR register should not be performed. After confirming this bit is '0' by NOP command, write it in the OBCM and OBCR registers.</li> <li>'0': Output buffer not busy</li> </ul> |

| 0   | ST00 | <ul> <li>eray_ibusy</li> <li>'1': Input buffer busy flag. If it is when input buffer is busy. (0x400-0x4fc). Write access to the input buffer shoud not be performed. After confirming this bit is '0' by NOP command, write it in the IBCM and IBCR registers.</li> <li>'0': Input buffer not busy</li> </ul>    |

**Note:** STATUS 0 register shows status of e-ray core(bit2-bit7=0). The status value is changed at falling edge of CSX.

STATUS 1 Definition

| Bit | Name | Function                                                                                    |

|-----|------|---------------------------------------------------------------------------------------------|

| 7   |      | Parity error<br>'1': Parity error occured during last tranmission.<br>'0': No parity error. |

| Bit | Name | Function                                                                                                                                                                                                 |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | ST16 | Command format error<br>'1': Command format error occured at last transmission. (ie. bit2/bit0 of command<br>first byte) is 1 (exception : command that has A[10] bit))<br>'0': No command format error. |

| 5   | ST15 | reserved                                                                                                                                                                                                 |

| 4   | ST14 | Undefined error<br>'1': Undifiened Command used at last transmission.<br>'0': no undefiened error.                                                                                                       |

| 3   | ST13 | Busy error<br>'1': E-Ray Communication Controller was busy and command is not executed.<br>'0': No tbusy error.                                                                                          |

| 2   | ST12 | Long message error<br>'1': Message was too long at last transmission.<br>'0': No long message error occured                                                                                              |

| 1   | ST11 | Short message error<br>'1': Message was too short at last transmission.<br>'0': No short message error.                                                                                                  |

| 0   | ST10 | Crc error<br>'1': CRC error at last transmission<br>'0': No CRC error.                                                                                                                                   |

Note: STATUS 1 register shows the status of previous SPI session. This status is cleared by eray\_reset.

#### STATUS 2 Definition

| Bit | Name | Function                                                                                                                                                                                                                                     |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ST27 | reserved                                                                                                                                                                                                                                     |

| 6   | ST26 | reserved                                                                                                                                                                                                                                     |

| 5   | ST25 | E-Ray timer 1 interrupt flag (tint1)<br>'1': E-Ray timer 1 interrupt flag is set<br>'0': No E-Ray timer 1 flag is set                                                                                                                        |

| 4   | ST24 | E-Ray timer 0 interrupt flag (tint0)<br>'1': E-Ray timer 0 interrupt flag is set<br>'0': No E-Ray timer 0 flag is set                                                                                                                        |

| 3   | ST23 | <ul> <li>E-Ray interrupt lin1 (int1) flag</li> <li>'1': E-Ray interrupt line 1 flag is set. At least one of the E-Ray line 1 assigned interrupt (EILS, SILS, EIES, SIES,ILE) flag is set.</li> <li>'0': No E-Ray line1 interrupt.</li> </ul> |

| 2   | ST22 | <ul> <li>E-Ray interrupt line0 (int0) flag</li> <li>'1': E-Ray interupt line 0 flag is set. At least one of the E-Ray line 0 assigned interrupt (EILS, SILS, EIES, SIES,ILE) flag is set.</li> <li>'0': No E-Ray line0 interrupt.</li> </ul> |

| 1   | ST21 | Status Interrupt register (SIR) flag<br>'1': At least one flag int the E-Ray Satuts interrupt register (SIR) is set to "1".<br>'0': No SIR interrupt flag is set.                                                                            |

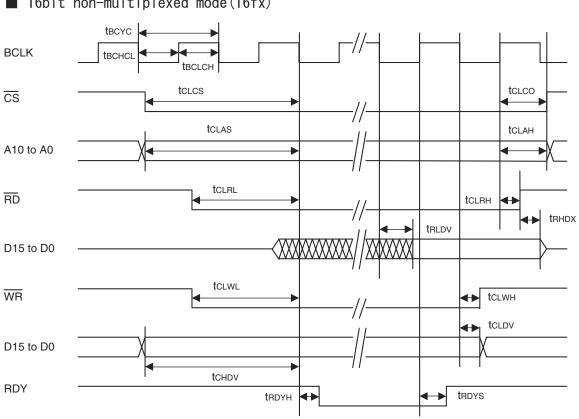

### (2) 16 bit non-multiplexed mode

|                    |                   | $0^{\circ}$ C to +85 °C, V <sub>CC</sub> = 5.0 V ±0.5V, V <sub>CC</sub><br>(MB88121B: T <sub>A</sub> = -40 °C to +105 °C, V<br>(MB88121C: T <sub>A</sub> = -40 °C to +125 °C, V | $Vcc = 5.0 V \pm$ | 0.5V / Vcc = | 3.3 V ±0.3V |

|--------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------|-------------|

| Demonster          | Symbol            | Condition                                                                                                                                                                       | Timing            |              | l lucit     |

| Parameter          |                   |                                                                                                                                                                                 | Min               | Max          | Unit        |

| Bus Clock Cycle    | <b>t</b> BCYC     |                                                                                                                                                                                 | 31.25             |              | ns          |

| High width of BCLK | tbclch            |                                                                                                                                                                                 | 5.0               | —            | ns          |

| Low width of BCLK  | <b>t</b> BCHCL    |                                                                                                                                                                                 | 5.0               | —            | ns          |

|                    |                   | MB88121, MB88121A                                                                                                                                                               | 12.5              | 100          | ns          |

| System Cleak Cycle | 4                 | MB88121B                                                                                                                                                                        | 100               | 250          | ns          |

| System Clock Cycle | tscyc             | MB88121C(Oscillator)                                                                                                                                                            | 125               | 250          | ns          |

|                    |                   | MB88121C(External Clock Input)                                                                                                                                                  | 12.5              | 250          | ns          |

|                    |                   | MB88121, MB88121A                                                                                                                                                               | 4.8               |              | ns          |

| Link width of COLK |                   | MB88121B                                                                                                                                                                        | 10                |              | ns          |

| High width of SCLK | tsclch            | MB88121C(Oscillator)                                                                                                                                                            | 10                |              | ns          |

|                    |                   | MB88121C(External Clock Input)                                                                                                                                                  | 4.8               |              | ns          |

|                    |                   | MB88121, MB88121A                                                                                                                                                               | 4.8               |              | ns          |

|                    | 1                 | MB88121B                                                                                                                                                                        | 10                |              | ns          |

| Low width of SCLK  | tschc∟            | MB88121C(Oscillator)                                                                                                                                                            | 10                |              | ns          |

|                    |                   | MB88121C(External Clock Input)                                                                                                                                                  | 4.8               |              | ns          |

| CS setup           | tclcs             |                                                                                                                                                                                 | 18.0              |              | ns          |

| CS hold            | tclco             |                                                                                                                                                                                 | 0                 |              | ns          |

| Address setup      | <b>t</b> CLAS     | _                                                                                                                                                                               | 13.0              |              | ns          |

| Address hold       | <b>t</b> clah     | _                                                                                                                                                                               | 0                 |              | ns          |

| RD setup time      | <b>t</b> clrl     | _                                                                                                                                                                               | 14.0              |              | ns          |

| RD hold time       | <b>t</b> clrh     | _                                                                                                                                                                               | 0                 |              | ns          |

| Data Valid dalay   | <b>t</b> =1 = 1 + | $C_f = 20pF$ (VCC = 5V)                                                                                                                                                         | 3.0               | 19.0         | ns          |

| Data Valid delay   | <b>t</b> rldv     | $C_f = 20pF$ (VCC = 3V)                                                                                                                                                         | 3.0               | 30.0         | ns          |

| Data Valid hold    | <b>t</b> RHDX     | $C_f = 20 pF$                                                                                                                                                                   | 3.0               | 18.5         | ns          |

| WR setup time      | <b>t</b> CLWL     |                                                                                                                                                                                 | 14.0              |              | ns          |

| WR hold time       | <b>t</b> clwh     |                                                                                                                                                                                 | 0                 |              | ns          |

| Data setup         | <b>t</b> CHDV     |                                                                                                                                                                                 | 18.0              | I —          | ns          |

| Data hold          | <b>t</b> CLDV     |                                                                                                                                                                                 | 0                 |              | ns          |

|                    | <b>t</b> RDYS     | $C_f = 20pF$ (VCC = 5V)                                                                                                                                                         |                   | 15.4         | ns          |

| RDY output delay   | <b>t</b> RDYS     | $C_f = 20pF$ (VCC = 3V)                                                                                                                                                         |                   | 25.4         | ns          |

| RDY output hold    | <b>t</b> rdyh     | $C_f = 20 pF$                                                                                                                                                                   | 3.0               |              | ns          |

| RST input time     | <b>t</b> RSTL     |                                                                                                                                                                                 | 200.0             |              | ns          |

(MB88121/MB88121A:  $T_A = -40 \degree C$  to +85 °C,  $V_{CC} = 5.0 V \pm 0.5V$ ,  $V_{CC33} = 3.3 V \pm 0.3V$ ,  $V_{CC18} = 1.8 V \pm 0.15V$ )

■ 16bit non-multiplexed mode(16fx)

MDS1 = 0, MDS0 = 1

(MB88121B:  $T_A = -40 \ ^{\circ}C$  to  $+105 \ ^{\circ}C$ ,  $V_{CC} = 5.0 \ V \pm 0.5V / V_{CC} = 3.3 \ V \pm 0.3V$ ) (MB88121C:  $T_A = -40 \ ^{\circ}C$  to  $+125 \ ^{\circ}C$ ,  $V_{CC} = 5.0 \ V \pm 0.5V / V_{CC} = 3.3 \ V \pm 0.3V$ )

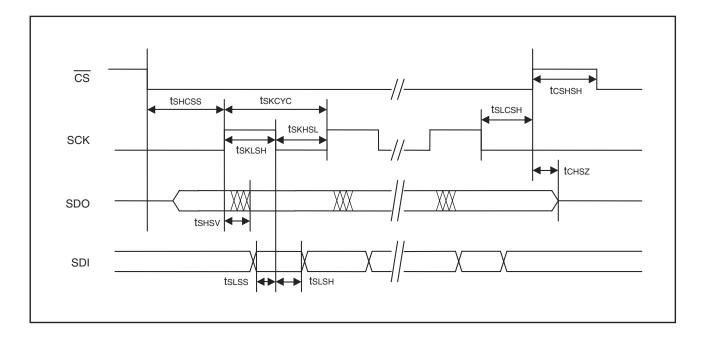

| Parameter               | Symbol         | Condition       | Timing |     | Unit |

|-------------------------|----------------|-----------------|--------|-----|------|

| Farameter               |                |                 | Min    | Max | Unit |

| Cycle of SCK            | tsксүс         | —               | 6trp   | —   | ns   |

|                         |                |                 | 100    | —   | ns   |

| Low width of SCK        | <b>t</b> skhsl |                 | 30     | —   | ns   |

| High width of SCK       | <b>t</b> sklsh |                 | 30     |     | ns   |

| SDO valid delay for SCK | <b>t</b> shsv  | $C_{f} = 20 pF$ |        | 20  | ns   |

| SDI setup time          | <b>t</b> s∟ss  |                 | 20     | —   | ns   |

| SDI hold time           | <b>t</b> slsh  |                 | 20     |     | ns   |

| CS setup                | <b>t</b> shcss |                 | 30     |     |      |

| CS hold time            | <b>t</b> slcsh |                 | 30     |     |      |

| SDO Hi-impedance delay  | <b>t</b> chsz  |                 |        | 30  | ns   |

| CS recovery time        | <b>t</b> csнsн |                 | 50     |     | ns   |

\*1: trp shows the RAM cycle for FlexRay

MDS1 = 1, MDS0 = 0

(MB88121B:  $T_A = -40 \degree C$  to +105 °C,  $V_{CC} = 5.0 \lor \pm 0.5 \lor / \lor_{CC} = 3.3 \lor \pm 0.3 \lor$ ) (MB88121C:  $T_A = -40 \degree C$  to +125 °C,  $\lor_{CC} = 5.0 \lor \pm 0.5 \lor / \lor_{CC} = 3.3 \lor \pm 0.3 \lor$ )

| Parameter               | Symbol         | Condition             | Timing |     | Unit |

|-------------------------|----------------|-----------------------|--------|-----|------|

| Faidilietei             |                |                       | Min    | Max | Unit |

| Cycle of SCK            | <b>t</b> ѕксүс | _                     | 6trp   | —   | ns   |

|                         |                |                       | 100    | —   | ns   |

| Low width of SCK        | <b>t</b> skhsl | _                     | 30     | —   | ns   |

| High width of SCK       | <b>t</b> sklsh |                       | 30     | —   | ns   |

| SDO valid delay for CS  | <b>t</b> cLsv  | C <sub>f</sub> = 20pF | —      | 25  | ns   |

| SDO valid delay for SCK | <b>t</b> shsv  | Cf = 20pi             |        | 20  | ns   |

| SDI setup time          | ts∟ss          |                       | 20     | —   | ns   |

| SDI hold time           | ts∟sн          | _                     | 20     | —   | ns   |

| CS setup time           | <b>t</b> s∟css | _                     | 30     | —   |      |

| CS hold time            | <b>t</b> shcsh |                       | 30     | —   |      |

| SDO Hi-impedance delay  | <b>t</b> chsz  | _                     |        | 30  | ns   |

| CS recovery time        | <b>t</b> csнsн |                       | 50     |     | ns   |

\*1: trp shows the RAM cycle for FlexRay

All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of Fujitsu semiconductor device; Fujitsu does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. Fujitsu assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of Fujitsu or any third party or does Fujitsu warrant non-infringement of any third-party's intellectual property right or other right by using such information. Fujitsu assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

For further information please contact: FUJITSU SEMICONDUCTOR EUROPE GmbH Pittlerstrasse 47, D-63225 Langen, Germany Tel: +49-6103-690-0 Fax: +49-6103-690-122

http://www.fujitsu.com/emea/services/microelectronics/

mail: flexray\_info@fme.fujitsu.com

F0610

© FUJITSU SEMICONDUCTOR EUROPE GmbH Printed in Germany