Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                        |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 16MHz                                                                          |

| Connectivity               | I²C, SCI                                                                       |

| Peripherals                | PWM, WDT                                                                       |

| Number of I/O              | 29                                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                      |

| Data Converters            | A/D 8x10b                                                                      |

| Oscillator Type            | External                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 48-LQFP                                                                        |

| Supplier Device Package    | 48-LFQFP (7x7)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd64f3664fyiv |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| Secti | ion 1 C | Dverview                                     | 1  |

|-------|---------|----------------------------------------------|----|

| 1.1   | Feature | 25                                           | 1  |

| 1.2   | Interna | l Block Diagram                              |    |

| 1.3   | Pin Arı | rangement                                    | 5  |

| 1.4   | Pin Fu  | nctions                                      | 9  |

| Secti | ion 2 C | CPU                                          | 13 |

| 2.1   | Addres  | s Space and Memory Map                       |    |

| 2.2   | Registe | er Configuration                             |    |

|       | 2.2.1   | General Registers                            |    |

|       | 2.2.2   | Program Counter (PC)                         |    |

|       | 2.2.3   | Condition-Code Register (CCR)                |    |

| 2.3   | Data Fe | ormats                                       |    |

|       | 2.3.1   | General Register Data Formats                |    |

|       | 2.3.2   | Memory Data Formats                          |    |

| 2.4   | Instruc | tion Set                                     |    |

|       | 2.4.1   | Table of Instructions Classified by Function |    |

|       | 2.4.2   | Basic Instruction Formats                    |    |

| 2.5   | Addres  | sing Modes and Effective Address Calculation |    |

|       | 2.5.1   | Addressing Modes                             |    |

|       | 2.5.2   | Effective Address Calculation                |    |

| 2.6   | Basic E | Bus Cycle                                    |    |

|       | 2.6.1   | Access to On-Chip Memory (RAM, ROM)          |    |

|       | 2.6.2   | On-Chip Peripheral Modules                   |    |

| 2.7   | CPU S   | tates                                        |    |

| 2.8   | Usage 1 | Notes                                        |    |

|       | 2.8.1   | Notes on Data Access to Empty Areas          |    |

|       | 2.8.2   | EEPMOV Instruction                           |    |

|       | 2.8.3   | Bit Manipulation Instruction                 |    |

| Secti | ion 3 E | Exception Handling                           | 51 |

| 3.1   |         | ion Sources and Vector Address               |    |

| 3.2   | Registe | er Descriptions                              |    |

|       | 3.2.1   | Interrupt Edge Select Register 1 (IEGR1)     |    |

|       | 3.2.2   | Interrupt Edge Select Register 2 (IEGR2)     |    |

|       | 3.2.3   | Interrupt Enable Register 1 (IENR1)          |    |

# 2.1 Address Space and Memory Map

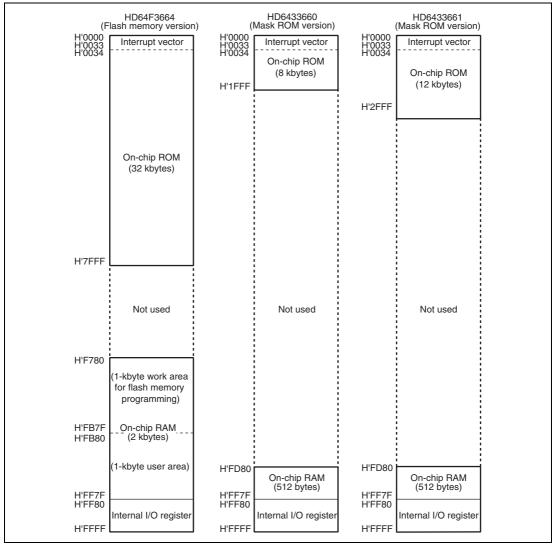

The address space of this LSI is 64 kbytes, which includes the program area and the data area. Figures 2.1 show the memory map.

Figure 2.1 Memory Map (1)

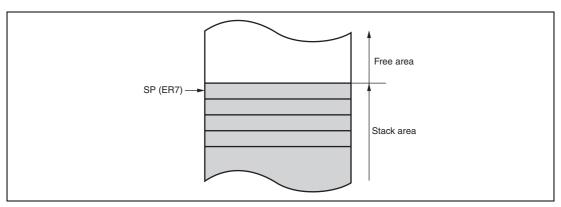

Figure 2.4 Relationship between Stack Pointer and Stack Area

## 2.2.2 Program Counter (PC)

This 24-bit counter indicates the address of the next instruction the CPU will execute. The length of all CPU instructions is 2 bytes (one word), so the least significant PC bit is ignored. (When an instruction is fetched, the least significant PC bit is regarded as 0). The PC is initialized when the start address is loaded by the vector address generated during reset exception-handling sequence.

## 2.2.3 Condition-Code Register (CCR)

This 8-bit register contains internal CPU status information, including an interrupt mask bit (I) and half-carry (H), negative (N), zero (Z), overflow (V), and carry (C) flags. The I bit is initialized to 1 by reset exception-handling sequence, but other bits are not initialized.

Some instructions leave flag bits unchanged. Operations can be performed on the CCR bits by the LDC, STC, ANDC, ORC, and XORC instructions. The N, Z, V, and C flags are used as branching conditions for conditional branch (Bcc) instructions.

For the action of each instruction on the flag bits, see appendix A.1, Instruction List.

## 2.3.2 Memory Data Formats

Figure 2.6 shows the data formats in memory. The H8/300H CPU can access word data and longword data in memory, however word or longword data must begin at an even address. If an attempt is made to access word or longword data at an odd address, an address error does not occur, however the least significant bit of the address is regarded as 0, so access begins the preceding address. This also applies to instruction fetches.

When ER7 (SP) is used as an address register to access the stack, the operand size should be word or longword.

| Data Type     | Address                        | Data Format     |

|---------------|--------------------------------|-----------------|

|               | 7                              | 0               |

| 1-bit data    | Address L 7                    | 7 6 5 4 3 2 1 0 |

| Byte data     | Address L MSB                  | SB: LSB         |

| Word data     | Address 2M MSB<br>Address 2M+1 | SB' LSB         |

| Longword data | Address 2N MSE<br>Address 2N+1 | SB              |

|               | Address 2N+2<br>Address 2N+3   | LSB             |

|               |                                |                 |

Figure 2.6 Memory Data Formats

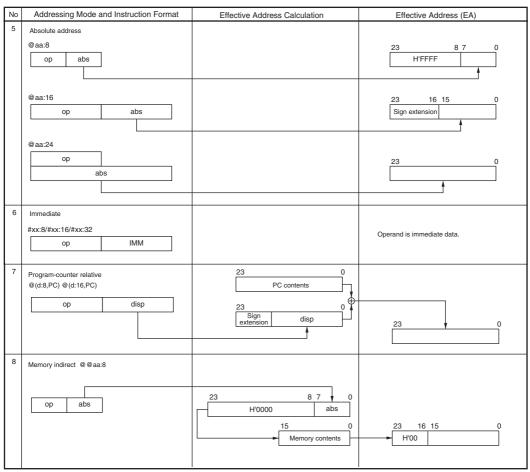

## Table 2.12 Effective Address Calculation (2)

[Legend]

r, rm,rn : Register field

op : Operation field

disp : Displacement

IMM : Immediate data

abs : Absolute address

Example 2: The BSET instruction is executed for port 5.

P57 and P56 are input pins, with a low-level signal input at P57 and a high-level signal input at P56. P55 to P50 are output pins and output low-level signals. An example to output a high-level signal at P50 with a BSET instruction is shown below.

|              | P57          | P56           | P55          | P54          | P53          | P52          | P51          | P50          |

|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Input/output | Input        | Input         | Output       | Output       | Output       | Output       | Output       | Output       |

| Pin state    | Low<br>level | High<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level |

| PCR5         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 1            |

| PDR5         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 0            |

Prior to executing BSET

BSET instruction executed

| BSET | #O,         | @PDR5 |

|------|-------------|-------|

| DOLI | <b>π</b> υ, | GEDRO |

The BSET instruction is executed for port 5.

After executing BSET

|              | P57          | P56           | P55          | P54          | P53          | P52          | P51          | P50           |

|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Input/output | Input        | Input         | Output       | Output       | Output       | Output       | Output       | Output        |

| Pin state    | Low<br>level | High<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | High<br>level |

| PCR5         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 1             |

| PDR5         | 0            | 1             | 0            | 0            | 0            | 0            | 0            | 1             |

Description on operation

When the BSET instruction is executed, first the CPU reads port 5.

Since P57 and P56 are input pins, the CPU reads the pin states (low-level and high-level input). P55 to P50 are output pins, so the CPU reads the value in PDR5. In this example PDR5 has a value of H'80, but the value read by the CPU is H'40.

Next, the CPU sets bit 0 of the read data to 1, changing the PDR5 data to H'41.

Finally, the CPU writes H'41 to PDR5, completing execution of BSET.

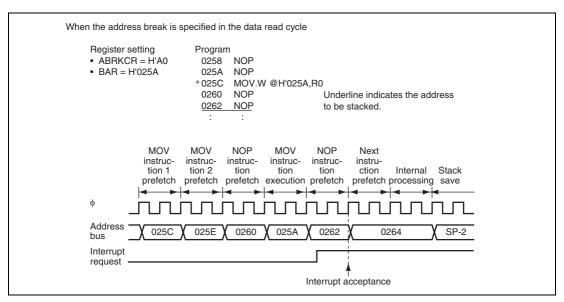

Figure 4.2 Address Break Interrupt Operation Example (2)

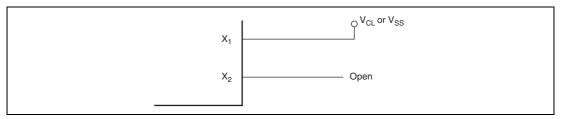

## 5.2.2 Pin Connection when Not Using Subclock

When the subclock is not used, connect pin  $X_1$  to  $V_{cL}$  or  $V_{ss}$  and leave pin  $X_2$  open, as shown in figure 5.10.

Figure 5.10 Pin Connection when not Using Subclock

## 5.3 Prescalers

## 5.3.1 Prescaler S

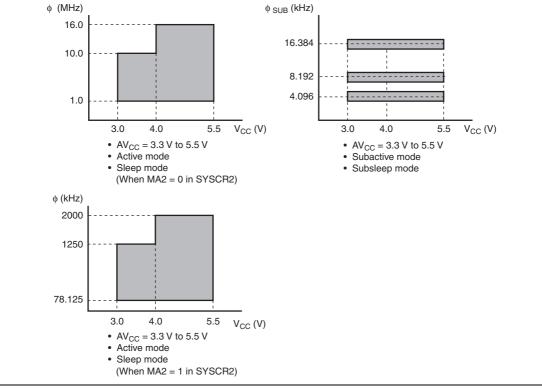

Prescaler S is a 13-bit counter using the system clock ( $\phi$ ) as its input clock. It is incremented once per clock period. Prescaler S is initialized to H'0000 by a reset, and starts counting on exit from the reset state. In standby mode, subactive mode, and subsleep mode, the system clock pulse generator stops. Prescaler S also stops and is initialized to H'0000. The CPU cannot read or write prescaler S. The output from prescaler S is shared by the on-chip peripheral modules. The divider ratio can be set separately for each on-chip peripheral function. In active mode and sleep mode, the clock input to prescaler S is determined by the division factor designated by MA2 to MA0 in SYSCR2.

### 5.3.2 Prescaler W

Prescaler W is a 5-bit counter using a 32.768 kHz signal divided by 4 ( $\phi_w/4$ ) as its input clock. The divided output is used for clock time base operation of timer A. Prescaler W is initialized to H'00 by a reset, and starts counting on exit from the reset state. Even in standby mode, subactive mode, or subsleep mode, prescaler W continues functioning so long as clock signals are supplied to pins  $X_1$  and  $X_2$ . Prescaler W can be reset by setting 1s in bits TMA3 and TMA2 of timer mode register A (TMA).

## 9.1.5 Pin Functions

The correspondence between the register specification and the port functions is shown below.

• P17/IRQ3/TRGV Pin

| Register      | PMR1 | PCR1  |                           |

|---------------|------|-------|---------------------------|

| Bit Name      | IRQ3 | PCR17 | Pin Function              |

| Setting value | 9 0  | 0     | P17 input pin             |

|               |      | 1     | P17 output pin            |

|               | 1    | Х     | IRQ3 input/TRGV input pin |

[Legend]

X: Don't care.

•  $P16/\overline{IRQ2}$  Pin

| Register      | PMR1 | PCR1  |                |

|---------------|------|-------|----------------|

| Bit Name      | IRQ2 | PCR16 | Pin Function   |

| Setting value | 9 0  | 0     | P16 input pin  |

|               |      | 1     | P16 output pin |

|               | 1    | Х     | IRQ2 input pin |

[Legend]

X: Don't care.

# • P15/IRQ1 Pin

| Register      | PMR1 | PCR1  |                |

|---------------|------|-------|----------------|

| Bit Name      | IRQ1 | PCR15 | Pin Function   |

| Setting value | 9 0  | 0     | P15 input pin  |

|               |      | 1     | P15 output pin |

|               | 1    | Х     | IRQ1 input pin |

[Legend]

X: Don't care.

Port 7 has the following registers.

- Port control register 7 (PCR7) •

- Port data register 7 (PDR7) •

#### 9.4.1 Port Control Register 7 (PCR7)

PCR7 selects inputs/outputs in bit units for pins to be used as general I/O ports of port 7.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                  |

|-----|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------|

| 7   | _        | _                | _   | Reserved                                                                                                                     |

| 6   | PCR76    | 0                | W   | Setting a PCR7 bit to 1 makes the corresponding pin an                                                                       |

| 5   | PCR75    | 0                | W   | output port, while clearing the bit to 0 makes the pin an                                                                    |

| 4   | PCR74    | 0                | W   | input port. Note that the TCSRV setting of the timer V has priority for deciding input/output direction of the P76/TMOV pin. |

| 3   | _        | —                | —   | Reserved                                                                                                                     |

| 2   | —        | —                | —   |                                                                                                                              |

| 1   | —        | —                |     |                                                                                                                              |

| 0   |          |                  | _   |                                                                                                                              |

#### 9.4.2 Port Data Register 7 (PDR7)

PDR7 is a general I/O port data register of port 7.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                               |

|-----|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| 7   |          | 1                |     | Reserved                                                                                                                                  |

|     |          |                  |     | This bit is always read as 1.                                                                                                             |

| 6   | P76      | 0                | R/W | PDR7 stores output data for port 7 pins.                                                                                                  |

| 5   | P75      | 0                | R/W | PDR7 is read while PCR7 bits are set to 1, the value                                                                                      |

| 4   | P74      | 0                | R/W | stored in PDR7 is read. If PDR7 is read while PCR7 bits are cleared to 0, the pin states are read regardless of the value stored in PDR7. |

| 3   | _        | 1                |     | Reserved                                                                                                                                  |

| 2   | _        | 1                |     | These bits are always read as 1.                                                                                                          |

| 1   | _        | 1                | _   |                                                                                                                                           |

| 0   |          | 1                |     |                                                                                                                                           |

# Section 10 Timer A

Timer A is an 8-bit timer with interval timing and real-time clock time-base functions. The clock time-base function is available when a 32.768kHz crystal oscillator is connected. Figure 10.1 shows a block diagram of timer A.

# 10.1 Features

- Timer A can be used as an interval timer or a clock time base.

- An interrupt is requested when the counter overflows.

- Any of eight clock signals can be output from pin TMOW: 32.768 kHz divided by 32, 16, 8, or 4 (1 kHz, 2 kHz, 4 kHz, 8 kHz), or the system clock divided by 32, 16, 8, or 4.

# **Interval Timer:**

Choice of eight internal clock sources (φ/8192, φ/4096, φ/2048, φ/512, φ/256, φ/128, φ/32, φ8)

# **Clock Time Base:**

• Choice of four overflow periods (1 s, 0.5 s, 0.25 s, 31.25 ms) when timer A is used as a clock time base (using a 32.768 kHz crystal oscillator).

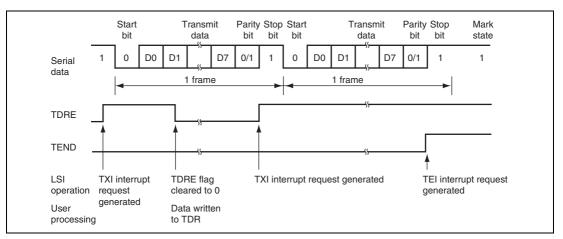

## 14.4.3 Data Transmission

Figure 14.5 shows an example of operation for transmission in asynchronous mode. In transmission, the SCI3 operates as described below.

- 1. The SCI3 monitors the TDRE flag in SSR. If the flag is cleared to 0, the SCI3 recognizes that data has been written to TDR, and transfers the data from TDR to TSR.

- 2. After transferring data from TDR to TSR, the SCI3 sets the TDRE flag to 1 and starts transmission. If the TIE bit is set to 1 at this time, a TXI interrupt request is generated. Continuous transmission is possible because the TXI interrupt routine writes next transmit data to TDR before transmission of the current transmit data has been completed.

- 3. The SCI3 checks the TDRE flag at the timing for sending the stop bit.

- 4. If the TDRE flag is 0, the data is transferred from TDR to TSR, the stop bit is sent, and then serial transmission of the next frame is started.

- 5. If the TDRE flag is 1, the TEND flag in SSR is set to 1, the stop bit is sent, and then the "mark state" is entered, in which 1 is output. If the TEIE bit in SCR3 is set to 1 at this time, a TEI interrupt request is generated.

6. Figure 14.6 shows a sample flowchart for transmission in asynchronous mode.

Figure 14.5 Example SCI3 Operation in Transmission in Asynchronous Mode (8-Bit Data, Parity, One Stop Bit)

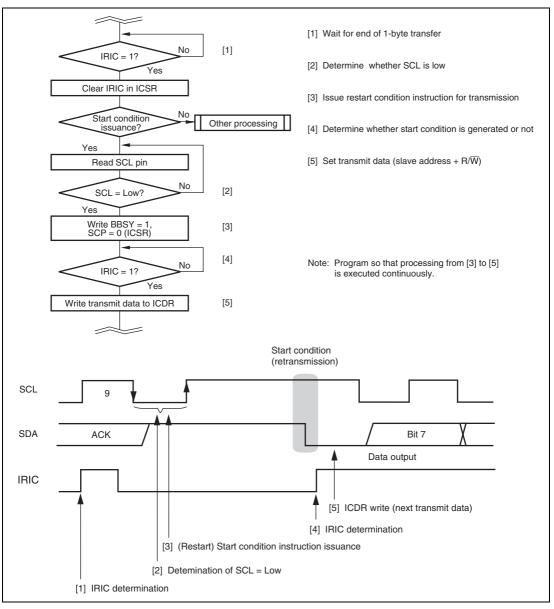

Figure 15.17 Flowchart and Timing of Start Condition Instruction Issuance for Retransmission

# 17.4 Operation

## 17.4.1 EEPROM Interface

This LSI has a multi-chip structure with two internal chips of F-ZTAT<sup>™</sup> HD64F3664 and 512byte EEPROM.

The EEPROM interface is the  $I^2C$  bus interface. This  $I^2C$  bus is open to the outside, so the communication with the external devices connected to the  $I^2C$  bus can be made.

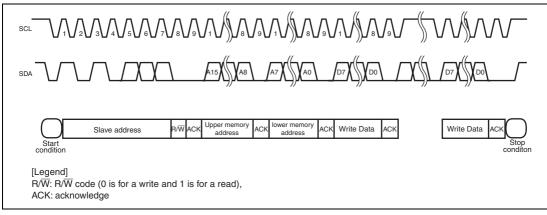

## 17.4.2 Bus Format and Timing

The I<sup>2</sup>C bus format and the I<sup>2</sup>C bus timing follow section 15.4.1, I<sup>2</sup>C Bus Data Format. The bus formats specific for the EEPROM are the following two.

- 1. The EEPROM address is configured of two bytes, the write data is transferred in the order of upper address and lower address from each MSB side.

- 2. The write data is transmitted from the MSB side.

The bus format and bus timing of the EEPROM are shown in figure 17.2.

| Start<br>condition<br>Slave addres                      | s R/W AG            | CK Upper memory A  | CK lower memory address | ACK Data A                         | CK Data A | Stop<br>conditon |

|---------------------------------------------------------|---------------------|--------------------|-------------------------|------------------------------------|-----------|------------------|

| SCL 1/2/3/4/5                                           | 5 6 7 8             | ₽\_1\ <u>}</u> _8\ | ¶√1√∬√®↓                | ∫ <sub>9</sub> √1√∫ <sub>8</sub> √ | ¶√1√}\s   |                  |

| SDA                                                     |                     | A15                | A7 X XA0                |                                    |           |                  |

| [Legend]<br>R/W: R/W code (0 is for<br>ACK: acknowledge | a write and 1 is fo | or a read),        |                         |                                    |           |                  |

Figure 17.2 EEPROM Bus Format and Bus Timing

Addresses in the page are incremented at each receipt of the write data and the write data can be input up to 8 bytes. If the LSB 3 bits (A2 to A0) in the EEPROM address reach the last address of the page, the address will roll over to the first address of the same page. When the address is rolled over, write data is received twice or more to the same address, however, the last received data is valid. At the receipt of the stop condition, write data reception is terminated and the write operation is entered.

The page write operation is shown in figure 17.4.

Figure 17.4 Page Write Operation

## 17.4.8 Acknowledge Polling

Acknowledge polling feature is used to show if the EEPROM is in an internally-timed write cycle or not. This feature is initiated by the input of the 8-bit slave address +  $R/\overline{W}$  code following the start condition during an internally-timed write cycle. Acknowledge polling will operate R/W code = "0". The ninth acknowledgement judges if the EEPROM is an internally-timed write cycle or not. Acknowledgement "1" shows the EEPROM is in a internally-timed write cycle and acknowledgement "0" shows the internally-timed write cycle has been completed. The acknowledge polling starts to function after a write data is input, i.e., when the stop condition is input.

### Power Supply Voltage and Operating Frequency Range

|                           |                 |                                                                                        |                               | Values                |     |     |       |       |

|---------------------------|-----------------|----------------------------------------------------------------------------------------|-------------------------------|-----------------------|-----|-----|-------|-------|

| ltem                      | Symbol          | Applicable Pins                                                                        | Test Condition                | Min                   | Тур | Max | Unit  | Notes |

| Output<br>high<br>voltage | V <sub>oH</sub> | P10 to P12,<br>P14 to P17,<br>P20 to P22,<br>P50 to P55,<br>P74 to P76,<br>P80 to P87, | $V_{cc}$ = 4.0 V to 5.5 V     | V <sub>cc</sub> - 1.0 | —   | —   | V     |       |

|                           |                 |                                                                                        | –I <sub>он</sub> = 1.5 mA     |                       |     |     |       |       |

|                           |                 |                                                                                        | -I <sub>OH</sub> = 0.1 mA     | $V_{cc} - 0.5$        | —   | —   |       |       |

|                           |                 |                                                                                        |                               |                       |     |     |       |       |

|                           |                 | P56, P57*                                                                              | $V_{cc}$ = 4.0 V to 5.5 V     | $V_{cc} - 2.5$        | _   | _   | V     |       |

|                           |                 |                                                                                        | –I <sub>OH</sub> = 0.1 mA     |                       |     |     |       |       |

|                           |                 |                                                                                        | $V_{\rm cc}$ = 3.0 V to 4.0 V | $V_{\rm cc}-2.0$      | _   | _   |       |       |

|                           |                 |                                                                                        | -I <sub>OH</sub> = 0.1 mA     |                       |     |     |       |       |

| Output                    | V <sub>oL</sub> | P10 to P12,<br>P14 to P17,<br>P20 to P22,<br>P50 to P57*,<br>P74 to P76,               | $V_{cc}$ = 4.0 V to 5.5 V     | _                     | _   | 0.6 | V     | _     |

| low<br>voltage            |                 |                                                                                        | I <sub>oL</sub> = 1.6 mA      |                       |     |     |       |       |

|                           |                 |                                                                                        | $I_{_{OL}} = 0.4 \text{ mA}$  | _                     | —   | 0.4 | _     |       |

|                           |                 | P80 to P87                                                                             | $V_{\rm cc}$ = 4.0 V to 5.5 V | _                     | —   | 1.5 | V     | _     |

|                           |                 |                                                                                        | I <sub>oL</sub> = 20.0 mA     |                       |     |     |       |       |

|                           |                 |                                                                                        | $V_{cc}$ = 4.0 V to 5.5 V     | _                     | _   | 1.0 |       |       |

|                           |                 |                                                                                        | I <sub>oL</sub> = 10.0 mA     |                       |     |     |       |       |

|                           |                 |                                                                                        | $V_{\rm cc}$ = 4.0 V to 5.5 V | _                     | —   | 0.4 |       |       |

|                           |                 |                                                                                        | I <sub>oL</sub> = 1.6 mA      |                       |     |     | <br>V |       |

|                           |                 |                                                                                        | I <sub>oL</sub> = 0.4 mA      | _                     | _   | 0.4 |       |       |

|                           |                 | SCL, SDA                                                                               | $V_{cc}$ = 4.0 V to 5.5 V     | _                     | _   | 0.6 |       |       |

|                           |                 |                                                                                        | I <sub>oL</sub> = 6.0 mA      |                       |     |     |       |       |

|                           |                 |                                                                                        | I <sub>oL</sub> = 3.0 mA      | —                     | _   | 0.4 |       |       |

Note: \* P50 to P55 for H8/3664N

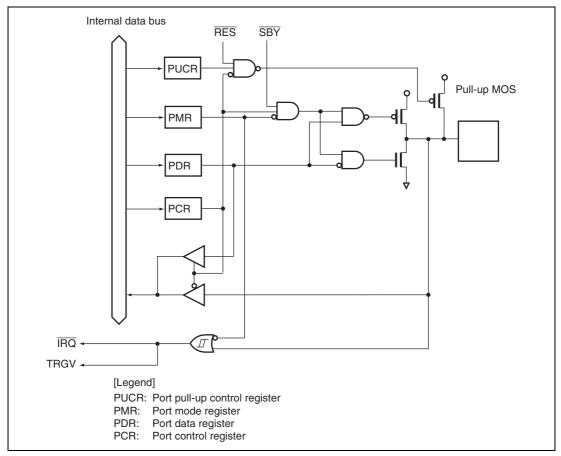

# Appendix B I/O Port Block Diagrams

# B.1 I/O Port Block

$\overline{\text{RES}}$  goes low in a reset, and  $\overline{\text{SBY}}$  goes low in a reset and in standby mode.

Figure B.1 Port 1 Block Diagram (P17)

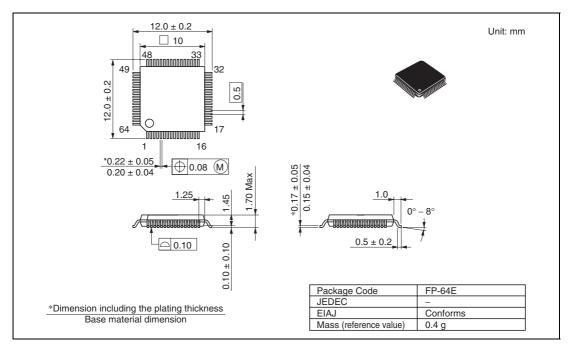

# Appendix D Package Dimensions

The package dimensions that are shows in the Renesas Semiconductor Packages Data Book have priority.

Figure D.1 FP-64E Package Dimensions

# Renesas 16-Bit Single-Chip Microcomputer Hardware Manual H8/3664 Group

| Publication Date: | 1st Edition, Mar, 2000              |

|-------------------|-------------------------------------|

|                   | Rev.6.00, Mar. 24, 2006             |

| Published by:     | Sales Strategic Planning Div.       |

|                   | Renesas Technology Corp.            |

| Edited by:        | Customer Support Department         |

|                   | Global Strategic Communication Div. |

|                   | Renesas Solutions Corp.             |

© 2006. Renesas Technology Corp., All rights reserved. Printed in Japan.