Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I²C), SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 16                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 768 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                    |

| Data Converters            | A/D 15x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-WFQFN Exposed Pad                                           |

| Supplier Device Package    | 24-QFN (4x4)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f901-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C8051F91x-C8051F90x

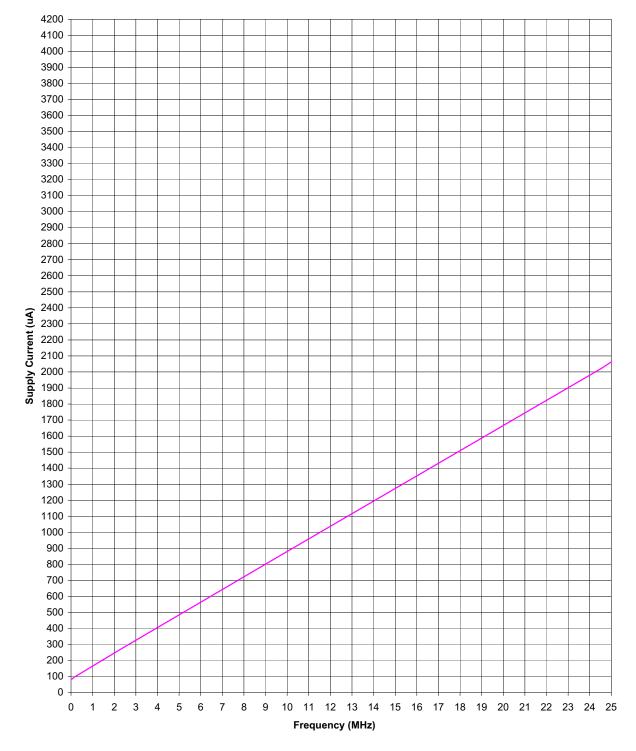

Figure 4.2. Idle Mode Current (External CMOS Clock)

## 7.2. Comparator Outputs

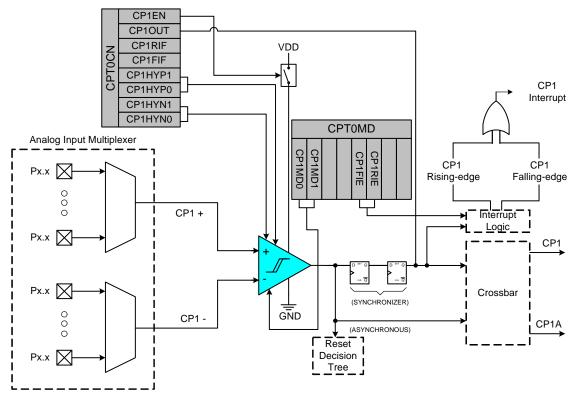

When a comparator is enabled, its output is a logic 1 if the voltage at the positive input is higher than the voltage at the negative input. When disabled, the comparator output is a logic 0. The comparator output is synchronized with the system clock as shown in Figure 7.2. The synchronous "latched" output (CP0, CP1) can be polled in software (CPnOUT bit), used as an interrupt source, or routed to a Port pin (configured for digital I/O) through the Crossbar.

The asynchronous "raw" comparator output (CP0A, CP1A) is used by the low power mode wake-up logic and reset decision logic. See the Power Options chapter and the Reset Sources chapter for more details on how the asynchronous comparator outputs are used to make wake-up and reset decisions. The asynchronous comparator output can also be routed directly to a Port pin through the Crossbar, and is available for use outside the device even if the system clock is stopped.

When using a Comparator as an interrupt source, Comparator interrupts can be generated on rising-edge and/or falling-edge comparator output transitions. Two independent interrupt flags (CPnRIF and CPnFIF) allow software to determine which edge caused the Comparator interrupt. The comparator rising-edge and falling-edge interrupt flags are set by hardware when a corresponding edge is detected regardless of the interrupt enable state. Once set, these bits remain set until cleared by software.

The rising-edge and falling-edge interrupts can be individually enabled using the CPnRIE and CPnFIE interrupt enable bits in the CPTnMD register. In order for the CPnRIF and/or CPnFIF interrupt flags to generate an interrupt request to the CPU, the Comparator must be enabled as an interrupt source and global interrupts must be enabled. See the Interrupt Handler chapter for additional information.

Figure 7.2. Comparator 1 Functional Block Diagram

# C8051F91x-C8051F90x

## SFR Definition 7.5. CPT0MX: Comparator0 Input Channel Select

| Bit   | 7   | 6    | 5      | 4   | 3          | 2   | 1   | 0   |  |

|-------|-----|------|--------|-----|------------|-----|-----|-----|--|

| Name  |     | CMX0 | N[3:0] |     | CMX0P[3:0] |     |     |     |  |

| Туре  | R/W | R/W  | R/W    | R/W | R/W        | R/W | R/W | R/W |  |

| Reset | 1   | 1    | 1      | 1   | 1          | 1   | 1   | 1   |  |

SFR Page = 0x0; SFR Address = 0x9F

| Bit | Name  |                                                     |                            | Function         |                                   |  |  |  |

|-----|-------|-----------------------------------------------------|----------------------------|------------------|-----------------------------------|--|--|--|

| 7:4 | CMX0N | Comparator0 Negative Input Selection.               |                            |                  |                                   |  |  |  |

|     |       | Selects the negative input channel for Comparator0. |                            |                  |                                   |  |  |  |

|     |       | 0000:                                               | P0.1                       | 1000:            | Reserved                          |  |  |  |

|     |       | 0001:                                               | P0.3                       | 1001:            | Reserved                          |  |  |  |

|     |       | 0010:                                               | P0.5                       | 1010:            | Reserved                          |  |  |  |

|     |       | 0011:                                               | P0.7                       | 1011:            | Reserved                          |  |  |  |

|     |       | 0100:                                               | P1.1                       | 1100:            | Capacitive Touch Sense<br>Compare |  |  |  |

|     |       | 0101:                                               | P1.3                       | 1101:            | VDD/DC+ divided by 2              |  |  |  |

|     |       | 0110:                                               | P1.5                       | 1110:            | Digital Supply Voltage            |  |  |  |

|     |       | 0111:                                               | Reserved                   | 1111:            | Ground                            |  |  |  |

| 3:0 | CMX0P | Comparat                                            | or0 Positive Input Sele    | ction.           |                                   |  |  |  |

|     |       | Selects the                                         | e positive input channel f | for Comparator0. |                                   |  |  |  |

|     |       | 0000:                                               | P0.0                       | 1000:            | Reserved                          |  |  |  |

|     |       | 0001:                                               | P0.2                       | 1001:            | Reserved                          |  |  |  |

|     |       | 0010:                                               | P0.4                       | 1010:            | Reserved                          |  |  |  |

|     |       | 0011:                                               | P0.6                       | 1011:            | Reserved                          |  |  |  |

|     |       | 0100:                                               | P1.0                       | 1100:            | Capacitive Touch Sense<br>Compare |  |  |  |

|     |       | 0101:                                               | P1.2                       | 1101:            | VDD/DC+ divided by 2              |  |  |  |

|     |       | 0110:                                               | P1.4                       | 1110:            | VBAT Supply Voltage               |  |  |  |

|     |       | 0111:                                               | P1.6                       | 1111:            | VDD/DC+ Supply Voltage            |  |  |  |

## SFR Definition 7.6. CPT1MX: Comparator1 Input Channel Select

| Bit   | 7          | 6   | 5   | 4   | 3          | 2   | 1   | 0   |  |

|-------|------------|-----|-----|-----|------------|-----|-----|-----|--|

| Name  | CMX1N[3:0] |     |     |     | CMX1P[3:0] |     |     |     |  |

| Туре  | R/W        | R/W | R/W | R/W | R/W        | R/W | R/W | R/W |  |

| Reset | 1          | 1   | 1   | 1   | 1          | 1   | 1   | 1   |  |

SFR Page = 0x0; SFR Address = 0x9E

| Bit | Name  |                                                     |                         | Function            |                                   |  |  |  |

|-----|-------|-----------------------------------------------------|-------------------------|---------------------|-----------------------------------|--|--|--|

| 7:4 | CMX1N | Comparator1 Negative Input Selection.               |                         |                     |                                   |  |  |  |

|     |       | Selects the negative input channel for Comparator1. |                         |                     |                                   |  |  |  |

|     |       | 0000:                                               | P0.1                    | 1000:               | Reserved                          |  |  |  |

|     |       | 0001:                                               | P0.3                    | 1001:               | Reserved                          |  |  |  |

|     |       | 0010:                                               | P0.5                    | 1010:               | Reserved                          |  |  |  |

|     |       | 0011:                                               | P0.7                    | 1011:               | Reserved                          |  |  |  |

|     |       | 0100:                                               | P1.1                    | 1100:               | Capacitive Touch Sense<br>Compare |  |  |  |

|     |       | 0101:                                               | P1.3                    | 1101:               | VDD/DC+ divided by 2              |  |  |  |

|     |       | 0110:                                               | P1.5                    | 1110:               | Digital Supply Voltage            |  |  |  |

|     |       | 0111:                                               | Reserved                | 1111:               | Ground                            |  |  |  |

| 3:0 | CMX1P | Comparat                                            | tor1 Positive Input Se  | election.           |                                   |  |  |  |

|     |       | Selects the                                         | e positive input channe | el for Comparator1. |                                   |  |  |  |

|     |       | 0000:                                               | P0.0                    | 1000:               | Reserved                          |  |  |  |

|     |       | 0001:                                               | P0.2                    | 1001:               | Reserved                          |  |  |  |

|     |       | 0010:                                               | P0.4                    | 1010:               | Reserved                          |  |  |  |

|     |       | 0011:                                               | P0.6                    | 1011:               | Reserved                          |  |  |  |

|     |       | 0100:                                               | P1.0                    | 1100:               | Capacitive Touch Sense<br>Compare |  |  |  |

|     |       | 0101:                                               | P1.2                    | 1101:               | VDD/DC+ divided by 2              |  |  |  |

|     |       | 0110:                                               | P1.4                    | 1110:               | VBAT Supply Voltage               |  |  |  |

|     |       | 0111:                                               | P1.6                    | 1111:               | VDD/DC+ Supply Voltage            |  |  |  |

whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory. Figure 9.1 illustrates the data memory organization of the C8051F91x-C8051F90x.

#### 9.2.1.1. General Purpose Registers

The lower 32 bytes of data memory, locations 0x00 through 0x1F, may be addressed as four banks of general-purpose registers. Each bank consists of eight byte-wide registers designated R0 through R7. Only one of these banks may be enabled at a time. Two bits in the program status word, RS0 (PSW.3) and RS1 (PSW.4), select the active register bank (see description of the PSW in SFR Definition 8.6). This allows fast context switching when entering subroutines and interrupt service routines. Indirect addressing modes use registers R0 and R1 as index registers.

#### 9.2.1.2. Bit Addressable Locations

In addition to direct access to data memory organized as bytes, the sixteen data memory locations at 0x20 through 0x2F are also accessible as 128 individually addressable bits. Each bit has a bit address from 0x00 to 0x7F. Bit 0 of the byte at 0x20 has bit address 0x00 while bit7 of the byte at 0x20 has bit address 0x07. Bit 7 of the byte at 0x2F has bit address 0x7F. A bit access is distinguished from a full byte access by the type of instruction used (bit source or destination operands as opposed to a byte source or destination).

The MCS-51<sup>™</sup> assembly language allows an alternate notation for bit addressing of the form XX.B where XX is the byte address and B is the bit position within the byte. For example, the instruction:

MOV C, 22.3h

moves the Boolean value at 0x13 (bit 3 of the byte at location 0x22) into the Carry flag.

# C8051F91x-C8051F90x

## SFR Definition 14.2. PMU0MD: Power Management Unit Mode

| Bit   | 7     | 6      | 5      | 4   | 3   | 2   | 1   | 0   |

|-------|-------|--------|--------|-----|-----|-----|-----|-----|

| Name  | RTCOE | WAKEOE | MONDIS |     |     |     |     |     |

| Туре  | R/W   | R/W    | R/W    | R/W | R/W | R/W | R/W | R/W |

| Reset | 0     | 0      | 0      | 0   | 0   | 0   | 0   | 0   |

### SFR Page = 0xF; SFR Address = 0xB5

| Bit | Name   | Function                                                                                                                                                                                             |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RTCOE  | Buffered SmaRTClock Output Enable.                                                                                                                                                                   |

|     |        | Enables the buffered SmaRTClock oscillator output on P0.2. Only available on<br>'F912 and 'F902 devices.                                                                                             |

|     |        | 0: Buffered SmaRTClock output is not enabled.                                                                                                                                                        |

|     |        | 1: Buffered SmaRTClock output is enabled.                                                                                                                                                            |

| 6   | WAKEOE | Wakeup Request Output Enable.                                                                                                                                                                        |

|     |        | Enables the Sleep Mode wake-up request signal on P0.3. Only available on 'F912 and 'F902 devices.                                                                                                    |

|     |        | 0: Wake-up request signal is not enabled.                                                                                                                                                            |

|     |        | 1: Wake-up request signal is enabled.                                                                                                                                                                |

| 5   | MONDIS | VBAT Supply Monitor Disable.                                                                                                                                                                         |

|     |        | Writing a 1 to this bit disables the VBAT supply monitor. Writing a 0 to this bit when the VBAT supply monitor is disabled will trigger a power-on reset. Only available on 'F912 and 'F902 devices. |

| 4:0 | Unused | Unused.                                                                                                                                                                                              |

|     |        | Read = 00000b. Write = Don't Care.                                                                                                                                                                   |

outputs during sleep mode, then the VDD/DC+ output can be made to float during Sleep mode by setting the VDDSLP bit in the DC0CF register to 1.

Setting this bit can provide power savings in two ways. First, if the sleep interval is relatively short and the VDD/DC+ load current (include leakage currents) is negligible, then the capacitor on VDD/DC+ will maintain the output voltage near the programmed value, which means that the VDD/DC+ capacitor will not need to be recharged upon every wake up event. The second power advantage is that internal or external low-power circuits that require more than 1.8 V can continue to function during Sleep mode without operating the dc-dc converter, powered by the energy stored in the 1  $\mu$ F output decoupling capacitor. For example, the C8051F91x-C8051F90x comparators require about 0.4  $\mu$ A when operating in their lowest power mode. If the dc-dc converter output were increased to 3.3 V just before putting the device into Sleep mode, then the comparator could be powered for more than 3 seconds before the output voltage dropped to 1.8 V. In this example, the overall energy consumption would be much lower than if the dc-dc converter were kept running to power the comparator.

If the load current on VDD/DC+ is high enough to discharge the VDD/DC+ capacitance to a voltage lower than VBAT during the sleep interval, an internal diode will prevent VDD/DC+ from dropping more than a few hundred millivolts below VBAT. There may be some additional leakage current from VBAT to ground when the VDD/DC+ level falls below VBAT, but this leakage current should be small compared to the current from VDD/DC+.

The amount of time that it takes for a device configured in one-cell mode to wake up from Sleep mode depends on a number of factors, including the dc-dc converter clock speed, the settings of the SWSEL, ILIMIT, and LPEN bits, the battery internal resistance, the load current, and the difference between the VBAT voltage level and the programmed output voltage. The wake up time can be as short as 2  $\mu$ s, though it is more commonly in the range of 5 to 10  $\mu$ s, and it can exceed 50  $\mu$ s under extreme conditions.

See Section "14. Power Management" on page 143 for more information about sleep mode.

## 16.9. Bypass Mode (C8051F912/02 only)

During normal operation, if the dc-dc converter input voltage exceeds the programmed output voltage, the converter will stop switching and the Diode Bypass switch will remain in the "on" state. The output voltage will be equal to the input voltage minus any resistive loss in the switch and all of the converter's analog circuits will remain biased. The bypass feature automatically shuts off the dc-dc converter when the input voltage is greater than the programmed output voltage by 150 mV. In bypass, the Diode Bypass switch and dc-dc converter bias currents are disabled except for the voltage comparison circuitry (~ 3  $\mu$ A, depending on the configuration settings in the DC0MD register). If the input voltage drops within 50 mV of the programmed output value, then the dc-dc converter automatically starts operating in the normal state. There is 100 mV voltage hysteresis built in the bypass comparator to enhance stability.

The bypass mode increases system operating time in systems which have a minimum operating voltage higher than the battery end of life voltage. For instance, if an external chip requires a minimum supply voltage of 2.7 V and a lithium coin cell battery is used as power source (end-of-life voltage is approximately 2 V), then the C8051F912/902's dc-dc converter could be configured for an output voltage of 2.7 V with bypass mode enabled. The dc-dc converter would be bypassed when the battery was fresh, but as soon as the battery voltage dropped below 2.75 V, the dc-dc converter would turn on to ensure that the external chip was provided with a minimum of 2.7 V for the remainder of the battery life.

## 16.10. Low Power Mode (C8051F912/02 only)

Setting the LPEN bit in the DC0CF register will enable a Low Power Mode for the dc-dc converter. In Low Power Mode, the bias currents are substantially reduced, which can lead to an efficiency improvement with light load currents (generally less than a few mA). The drawback to this mode is that the response time of the converter's analog blocks is increased; larger delay in the circuits controlling the Diode Bypass switch can lead to loss of efficiency at medium and high load currents due to reverse leakage in the switch. The Low power mode also reduces the peak inductor current limit as shown in Table 16.1.

## **16.12. DC-DC Converter Register Descriptions**

The SFRs used to configure the dc-dc converter are described in the following register descriptions. The reset values for these registers can be used as-is in most systems; therefore, no software intervention or initialization is required.

## SFR Definition 16.1. DC0CN: DC-DC Converter Control

| Bit   | 7     | 6 | 5     | 4        | 3    | 2    | 1 | 0 |

|-------|-------|---|-------|----------|------|------|---|---|

| Name  | MINPW |   | SWSEL | Reserved | SYNC | VSEL |   |   |

| Туре  | R/W   |   | R/W   | R/W      | R/W  | R/W  |   |   |

| Reset | 0     | 0 | 1     | 0        | 0    | 0    | 0 | 1 |

SFR Page = 0x0; SFR Address = 0x97

| Bit | Name       | Function                                                                                                                                |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | MINPW[1:0] | DC-DC Converter Minimum Pulse Width.                                                                                                    |

|     |            | Specifies the minimum pulse width.                                                                                                      |

|     |            | 00: No minimum duty cycle.                                                                                                              |

|     |            | 01: Minimum pulse width is 20 ns.                                                                                                       |

|     |            | 10: Minimum pulse width is 40 ns.                                                                                                       |

|     |            | 11: Minimum pulse width is 80 ns.                                                                                                       |

| 5   | SWSEL      | DC-DC Converter Switch Select.                                                                                                          |

|     |            | Selects one of two possible converter switch sizes to maximize efficiency.                                                              |

|     |            | 0: The large switches are selected (best efficiency for high output currents).                                                          |

|     |            | 1: The small switches are selected (best efficiency for low output currents).                                                           |

| 4   | Reserved   | Reserved. Always Write to 0.                                                                                                            |

| 3   | SYNC       | ADC0 Synchronization Enable.                                                                                                            |

|     |            | When synchronization is enabled, the ADC0SC[4:0] bits in the ADC0CF register                                                            |

|     |            | must be set to 00000b.                                                                                                                  |

|     |            | 0: The ADC is not synchronized to the dc-dc converter.<br>1: The ADC is synchronized to the dc-dc converter. ADC0 tracking is performed |

|     |            | during the longest quiet time of the dc-dc converter switching cycle and ADC0 SAR                                                       |

|     |            | clock is also synchronized to the dc-dc converter switching cycle.                                                                      |

| 2:0 | VSEL[2:0]  | DC-DC Converter Output Voltage Select.                                                                                                  |

|     |            | Specifies the target output voltage.                                                                                                    |

|     |            | 000: Target output voltage is 1.8 V.                                                                                                    |

|     |            | 001: Target output voltage is 1.9 V.                                                                                                    |

|     |            | 010: Target output voltage is 2.0 V.                                                                                                    |

|     |            | 011: Target output voltage is 2.1 V.                                                                                                    |

|     |            | 100: Target output voltage is 2.4 V.<br>101: Target output voltage is 2.7 V.                                                            |

|     |            | 110: Target output voltage is 3.0 V.                                                                                                    |

|     |            | 111: Target output voltage is 3.3 V.                                                                                                    |

|     |            |                                                                                                                                         |

## 19.3.4. External CMOS Clock Mode

If an external CMOS clock is used as the external oscillator, the clock should be directly routed into XTAL2. The XTAL2 pin should be configured as a digital input. XTAL1 is not used in external CMOS clock mode. The external oscillator valid detector will always return zero when the external oscillator is configured to External CMOS Clock mode.

## **19.4.** Special Function Registers for Selecting and Configuring the System Clock

The clocking sources on C8051F91x-C8051F90x devices are enabled and configured using the OSCICN, OSCICL, OSCXCN and the SmaRTClock internal registers. See Section "20. SmaRTClock (Real Time Clock)" on page 188 for SmaRTClock register descriptions. The system clock source for the MCU can be selected using the CLKSEL register. To minimize active mode current, the oneshot timer which sets Flash read time should by bypassed when the system clock is greater than 10 MHz. See the FLSCL register description for details.

The clock selected as the system clock can be divided by 1, 2, 4, 8, 16, 32, 64, or 128. When switching between two clock divide values, the transition may take up to 128 cycles of the undivided clock source. The CLKRDY flag can be polled to determine when the new clock divide value has been applied. The clock divider must be set to "divide by 1" when entering Suspend or Sleep Mode.

The system clock source may also be switched on-the-fly. The switchover takes effect after one clock period of the slower oscillator.

| Bit   | 7      | 6           | 5   | 4   | 3   | 2           | 1   | 0   |

|-------|--------|-------------|-----|-----|-----|-------------|-----|-----|

| Name  | CLKRDY | CLKDIV[2:0] |     |     |     | CLKSEL[2:0] |     |     |

| Туре  | R      | R/W         | R/W | R/W | R/W | R/W         | R/W | R/W |

| Reset | 0      | 0           | 1   | 1   | 0   | 1           | 0   | 0   |

SFR Page = All Pages; SFR Address = 0xA9

| Bit | Name        | Function                                                                       |

|-----|-------------|--------------------------------------------------------------------------------|

| 7   | CLKRDY      | System Clock Divider Clock Ready Flag.                                         |

|     |             | 0: The selected clock divide setting has not been applied to the system clock. |

|     |             | 1: The selected clock divide setting has been applied to the system clock.     |

| 6:4 | CLKDIV[2:0] | System Clock Divider Bits.                                                     |

|     |             | Selects the clock division to be applied to the undivided system clock source. |

|     |             | 000: System clock is divided by 1.                                             |

|     |             | 001: System clock is divided by 2.                                             |

|     |             | 010: System clock is divided by 4.                                             |

|     |             | 011: System clock is divided by 8.                                             |

|     |             | 100: System clock is divided by 16.                                            |

|     |             | 101: System clock is divided by 32.                                            |

|     |             | 110: System clock is divided by 64.                                            |

|     |             | 111: System clock is divided by 128.                                           |

| 3   | Unused      | Unused.                                                                        |

|     |             | Read = 0b. Must Write 0b.                                                      |

| 2:0 | CLKSEL[2:0] | System Clock Select.                                                           |

|     |             | Selects the oscillator to be used as the undivided system clock source.        |

|     |             | 000: Precision Internal Oscillator.                                            |

|     |             | 001: External Oscillator.                                                      |

|     |             | 011: SmaRTClock Oscillator.                                                    |

|     |             | 100: Low Power Oscillator.                                                     |

|     |             | All other values reserved.                                                     |

### 20.3.2. Setting a SmaRTClock Alarm

The SmaRTClock alarm function compares the 32-bit value of SmaRTClock Timer to the value of the ALARMn registers. An alarm event is triggered if the SmaRTClock timer is **equal to** the ALARMn registers. If Auto Reset is enabled, the 32-bit timer will be cleared to zero one SmaRTClock cycle after the alarm event.

The SmaRTClock alarm event can be configured to reset the MCU, wake it up from a low power mode, or generate an interrupt. See Section "12. Interrupt Handler" on page 120, Section "14. Power Management" on page 143, and Section "18. Reset Sources" on page 171 for more information.

The following steps can be used to set up a SmaRTClock Alarm:

- 1. Disable SmaRTClock Alarm Events (RTC0AEN = 0).

- 2. Set the ALARMn registers to the desired value.

- 3. Enable SmaRTClock Alarm Events (RTC0AEN = 1).

#### Notes:

- The ALRM bit, which is used as the SmaRTClock Alarm Event flag, is cleared by disabling SmaRTClock Alarm Events (RTC0AEN = 0).

- If AutoReset is disabled, disabling (RTC0AEN = 0) then Re-enabling Alarm Events (RTC0AEN = 1) after a SmaRTClock Alarm without modifying ALARMn registers will automatically schedule the next alarm after 2^32 SmaRTClock cycles (approximately 36 hours using a 32.768 kHz crystal).

- The SmaRTClock Alarm Event flag will remain asserted for a maximum of one SmaRTClock cycle. See Section "14. Power Management" on page 143 for information on how to capture a SmaRTClock Alarm event using a flag which is not automatically cleared by hardware.

#### 20.3.3. Software Considerations for using the SmaRTClock Timer and Alarm

The SmaRTClock timer and alarm have two operating modes to suit varying applications. The two modes are described below:

#### Mode 1:

The first mode uses the SmaRTClock timer as a perpetual timebase which is never reset to zero. Every 36 hours, the timer is allowed to overflow without being stopped or disrupted. The alarm interval is software managed and is added to the ALRMn registers by software after each alarm. This allows the alarm match value to always stay ahead of the timer by one software managed interval. If software uses 32-bit unsigned addition to increment the alarm match value, then it does not need to handle overflows since both the timer and the alarm match value will overflow in the same manner.

This mode is ideal for applications which have a long alarm interval (e.g., 24 or 36 hours) and/or have a need for a perpetual timebase. An example of an application that needs a perpetual timebase is one whose wake-up interval is constantly changing. For these applications, software can keep track of the number of timer overflows in a 16-bit variable, extending the 32-bit (36 hour) timer to a 48-bit (272 year) perpetual timebase.

#### Mode 2:

The second mode uses the SmaRTClock timer as a general purpose up counter which is auto reset to zero by hardware after each alarm. The alarm interval is managed by hardware and stored in the ALRMn registers. Software only needs to set the alarm interval once during device initialization. After each alarm, software should keep a count of the number of alarms that have occurred in order to keep track of time.

This mode is ideal for applications that require minimal software intervention and/or have a fixed alarm interval. This mode is the most power efficient since it requires less CPU time per alarm.

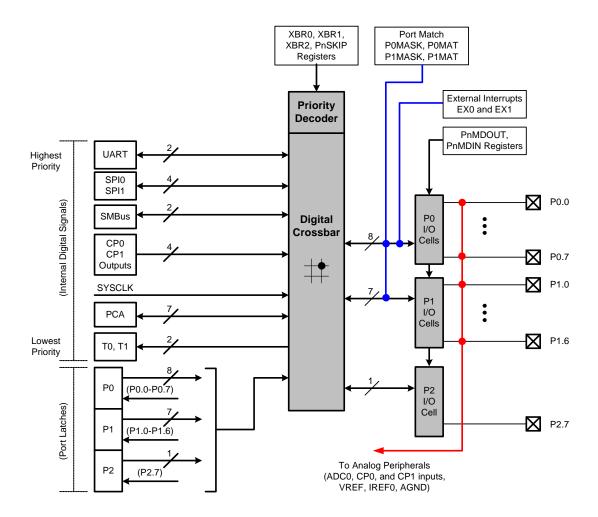

## 21. Port Input/Output

Digital and analog resources are available through 16 I/O pins. Port pins are organized as three byte-wide ports. Port pins P0.0–P1.6 can be defined as digital or analog I/O. Digital I/O pins can be assigned to one of the internal digital resources or used as general purpose I/O (GPIO). Analog I/O pins are used by the internal analog resources. P2.7 can be used as GPIO and is shared with the C2 Interface Data signal (C2D). See Section "27. C2 Interface" on page 312 for more details.

The designer has complete control over which digital and analog functions are assigned to individual Port pins, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. See Section 21.3 for more information on the Crossbar.

All Port I/Os are 5 V tolerant when used as digital inputs or open-drain outputs. For Port I/Os configured as push-pull outputs, current is sourced from the VDD/DC+ supply. Port I/Os used for analog functions can operate up to the VDD/DC+ supply voltage. See Section 21.1 for more information on Port I/O operating modes and the electrical specifications chapter for detailed electrical specifications.

Figure 21.1. Port I/O Functional Block Diagram

# C8051F91x-C8051F90x

## SFR Definition 21.6. P1MASK: Port1 Mask Register

| Bit   | 7           | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|-----|---|---|---|---|---|---|

| Name  | P1MASK[7:0] |     |   |   |   |   |   |   |

| Туре  |             | R/W |   |   |   |   |   |   |

| Reset | 0           | 0   | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page= 0x0; SFR Address = 0xBF

| Bit | Name        | Function                                                                                                                                                                                            |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MASK[7:0] | Port 1 Mask Value.                                                                                                                                                                                  |

|     |             | Selects P1 pins to be compared to the corresponding bits in P1MAT.<br>0: P1.n pin logic value is ignored and cannot cause a Port Mismatch event.<br>1: P1.n pin logic value is compared to P1MAT.n. |

## SFR Definition 21.7. P1MAT: Port1 Match Register

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | P1MAT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 1          | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Page = 0x0; SFR Address = 0xCF

| Bit | Name       | Function                                                                                                                                                                                    |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MAT[7:0] | Port 1 Match Value.                                                                                                                                                                         |

|     |            | Match comparison value used on Port 1 for bits in P1MASK which are set to 1.<br>0: P1.n pin logic value is compared with logic LOW.<br>1: P1.n pin logic value is compared with logic HIGH. |

## 21.5. Special Function Registers for Accessing and Configuring Port I/O

All Port I/O are accessed through corresponding special function registers (SFRs) that are both byte addressable and bit addressable. When writing to a Port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the Port's input pins are returned regardless of the XBRn settings (i.e., even when the pin is assigned to another signal by the Crossbar, the Port register can always read its corresponding Port I/O pin). The exception to this is the execution of the read-modify-write instructions that target a Port Latch register as the destination. The read-modify-write instructions when operating on a Port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SETB, when the destination is an individual bit in a Port SFR. For these instructions, the value of the latch register (not the pin) is read, modified, and written back to the SFR.

Each Port has a corresponding PnSKIP register which allows its individual Port pins to be assigned to digital functions or skipped by the Crossbar. All Port pins used for analog functions, GPIO, or dedicated digital functions such as the EMIF should have their PnSKIP bit set to 1.

The Port input mode of the I/O pins is defined using the Port Input Mode registers (PnMDIN). Each Port cell can be configured for analog or digital I/O. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is P2.7, which can only be used for digital I/O.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings.

The drive strength of the output drivers are controlled by the Port Drive Strength (PnDRV) registers. The default is low drive strength. See Section "4. Electrical Characteristics" on page 36 for the difference in output drive strength between the two modes.

## SFR Definition 21.17. P1DRV: Port1 Drive Strength

| Bit   | 7 | 6 | 5          | 4 | 3 | 2 | 1 | 0 |

|-------|---|---|------------|---|---|---|---|---|

| Name  |   |   | P1DRV[6:0] |   |   |   |   |   |

| Туре  |   |   | R/W        |   |   |   |   |   |

| Reset | 0 | 0 | 0          | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0xF; SFR Address = 0xA5

| Bit | Name       | Function                                                                                                                                                                                               |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused     | Unused.                                                                                                                                                                                                |

|     |            | Read =0b; Write = Don't Care.                                                                                                                                                                          |

| 6:0 | P1DRV[6:0] | Drive Strength Configuration Bits for P1.6–P1.0 (respectively).                                                                                                                                        |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P1.n Output has low output drive strength.<br>1: Corresponding P1.n Output has high output drive strength. |

## SFR Definition 21.18. P2: Port2

| Bit   | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|---|---|---|---|---|---|---|

| Name  | P2  |   |   |   |   |   |   |   |

| Туре  | R/W |   |   |   |   |   |   |   |

| Reset | 1   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = All Pages; SFR Address = 0xA0; Bit-Addressable

| Bit | Name   | Description                                                                                                                                   | Read                                                                          | Write |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------|

| 7   | P2     | <b>Port 2 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | LOW.  |

| 6:0 | Unused | <b>Unused.</b><br>Read = 0000000b; Write = D                                                                                                  | on't Care.                                                                    |       |

### 23.2.2. 9-Bit UART

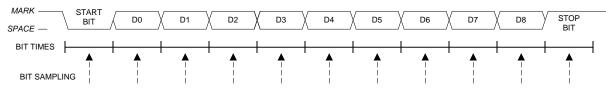

9-bit UART mode uses a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The state of the ninth transmit data bit is determined by the value in TB80 (SCON0.3), which is assigned by user software. It can be assigned the value of the parity flag (bit P in register PSW) for error detection, or used in multiprocessor communications. On receive, the ninth data bit goes into RB80 (SCON0.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: (1) RI0 must be logic 0, and (2) if MCE0 is logic 1, the 9th bit must be logic 1 (when MCE0 is logic 0, the state of the ninth data bit is unimportant). If these conditions are met, the eight bits of data are stored in SBUF0, the ninth bit is stored in RB80, and the RI0 flag is set to 1. If the above conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set to 1. A UART0 interrupt will occur if enabled when either TI0 or RI0 is set to 1.

## 23.3. Multiprocessor Communications

9-Bit UART mode supports multiprocessor communication between a master processor and one or more slave processors by special use of the ninth data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its ninth bit is logic 1; in a data byte, the ninth bit is always set to logic 0.

Setting the MCE0 bit (SCON0.5) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the ninth bit is logic 1 (RB80 = 1) signifying an address byte has been received. In the UART interrupt handler, software will compare the received address with the slave's own assigned 8-bit address. If the addresses match, the slave will clear its MCE0 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE0 bits set and do not generate interrupts on the reception of the following the addressed slave resets its MCE0 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

## SFR Definition 24.3. SPInCKR: SPI Clock Rate

| Bit   | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------|---|---|---|---|---|---|---|

| Name  | SCRn[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W       |   |   |   |   |   |   |   |

| Reset | 0         | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Addresses: SPI0CKR = 0xA2, SPI1CKR = 0x85 SFR Pages: SPI0CKR = 0x0, SPI1CKR = 0x0

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SCRn | SPI Clock Rate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |      | These bits determine the frequency of the SCK output when the SPI module is<br>configured for master mode operation. The SCK clock frequency is a divided<br>version of the system clock, and is given in the following equation, where SYSCLK<br>is the system clock frequency and SPInCKR is the 8-bit value held in the SPInCKR<br>register.<br>$f_{SCK} = \frac{SYSCLK}{2 \times (SPInCKR[7:0] + 1)}$ for 0 <= SPI0CKR <= 255<br>Example: If SYSCLK = 2 MHz and SPInCKR = 0x04,<br>$f_{SCK} = \frac{2000000}{2 \times (4 + 1)}$ $f_{SCK} = 200kHz$ |

|     |      | $I_{SCK} = 200 \kappa H Z$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

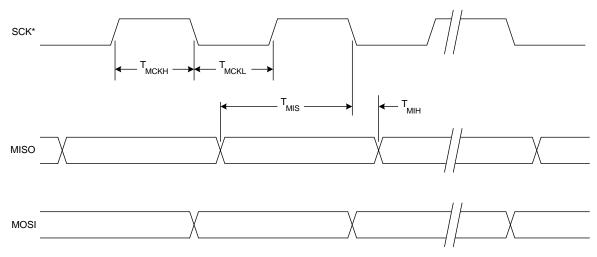

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

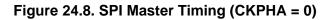

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

## Figure 24.9. SPI Master Timing (CKPHA = 1)

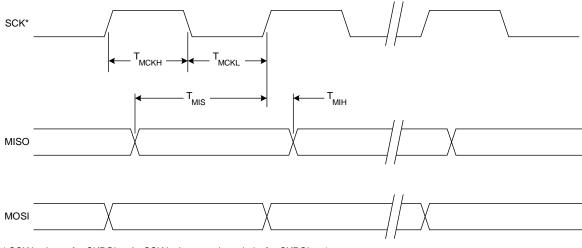

## 25.2.2. 8-bit Timers with Auto-Reload

When T2SPLIT is set, Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 25.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control for TMR2H. TMR2L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, SmaRTClock divided by 8 or Comparator 0 output. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bits (T2XCLK[1:0] in TMR2CN), as follows:

| T2MH | T2XCLK[1:0] | TMR2H Clock<br>Source |

|------|-------------|-----------------------|

| 0    | 00          | SYSCLK / 12           |

| 0    | 01          | SmaRTClock / 8        |

| 0    | 10          | Reserved              |

| 0    | 11          | Comparator 0          |

| 1    | Х           | SYSCLK                |

| T2ML | T2XCLK[1:0] | TMR2L Clock<br>Source |

|------|-------------|-----------------------|

| 0    | 00          | SYSCLK / 12           |

| 0    | 01          | SmaRTClock / 8        |

| 0    | 10          | Reserved              |

| 0    | 11          | Comparator 0          |

| 1    | Х           | SYSCLK                |

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled (IE.5), an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 25.5. Timer 2 8-Bit Mode Block Diagram

## 27. C2 Interface

C8051F91x-C8051F90x devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow Flash programming and in-system debugging with the production part installed in the end application. The C2 interface uses a clock signal (C2CK) and a bi-directional C2 data signal (C2D) to transfer information between the device and a host system. See the C2 Interface Specification for details on the C2 protocol.

## 27.1. C2 Interface Registers

The following describes the C2 registers necessary to perform Flash programming through the C2 interface. All C2 registers are accessed through the C2 interface as described in the C2 Interface Specification.

## C2 Register Definition 27.1. C2ADD: C2 Address

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | C2ADD[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | Name       | Function                                                                                                                                               |                                                                                       |  |  |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|

| 7:0 | C2ADD[7:0] | <b>C2 Address.</b><br>The C2ADD register is accessed via the C2 interface to select the target Data register for C2 Data Read and Data Write commands. |                                                                                       |  |  |

|     |            |                                                                                                                                                        |                                                                                       |  |  |

|     |            | Address                                                                                                                                                | Description                                                                           |  |  |

|     |            | 0x00                                                                                                                                                   | Selects the Device ID register for Data Read instructions                             |  |  |

|     |            | 0x01                                                                                                                                                   | Selects the Revision ID register for Data Read instructions                           |  |  |

|     |            | 0x02                                                                                                                                                   | Selects the C2 Flash Programming Control register for Data<br>Read/Write instructions |  |  |

|     |            | 0xB4                                                                                                                                                   | Selects the C2 Flash Programming Data register for Data Read/Write instructions       |  |  |