# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 16                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 768 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                    |

| Data Converters            | A/D 15x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                 |

| Supplier Device Package    | 24-QSOP                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f901-gu |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

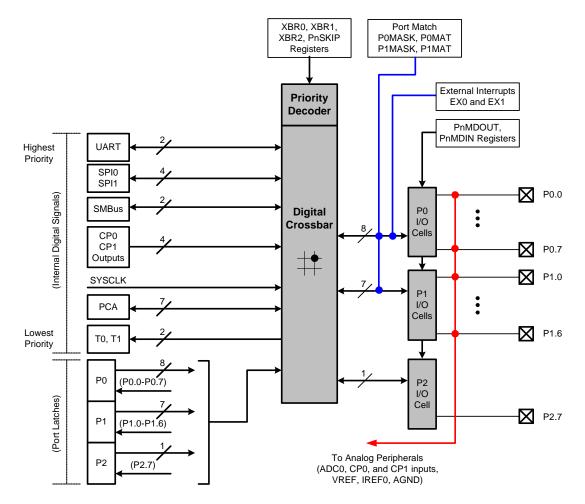

#### 1.2. Port Input/Output

Digital and analog resources are available through 16 I/O pins. Port pins are organized as three byte-wide ports. Port pins P0.0–P1.6 can be defined as digital or analog I/O. Digital I/O pins can be assigned to one of the internal digital resources or used as general purpose I/O (GPIO). Analog I/O pins are used by the internal analog resources. P2.7 can be used as GPIO and is shared with the C2 Interface Data signal (C2D). See Section "27. C2 Interface" on page 312 for more details.

The designer has complete control over which digital and analog functions are assigned to individual Port pins, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. See Section "21.3. Priority Crossbar Decoder" on page 209 for more information on the Crossbar.

All Port I/Os are 5 V tolerant when used as digital inputs or open-drain outputs. For Port I/Os configured as push-pull outputs, current is sourced from the VDD/DC+ supply. Port I/Os used for analog functions can operate up to the VDD/DC+ supply voltage. See Section "21.1. Port I/O Modes of Operation" on page 206 for more information on Port I/O operating modes and the electrical specifications chapter for detailed electrical specifications.

Figure 1.5. Port I/O Functional Block Diagram

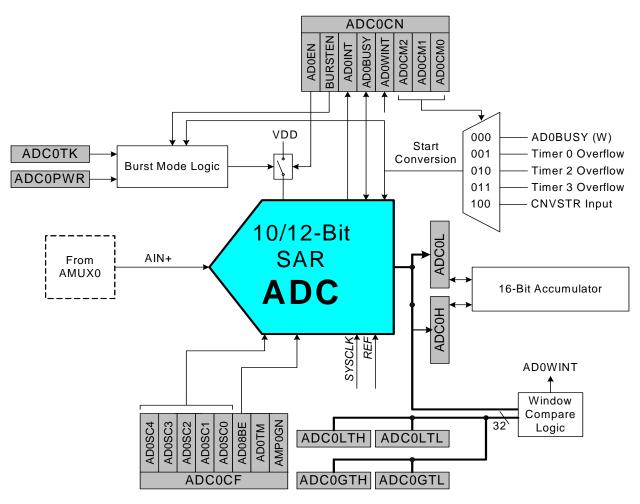

# 1.5. SAR ADC with 16-bit Auto-Averaging Accumulator and Autonomous Low Power Burst Mode

C8051F91x-C8051F90x devices have a 300 ksps, 10-bit or 75 ksps 12-bit successive-approximationregister (SAR) ADC with integrated track-and-hold and programmable window detector. ADC0 also has an autonomous low power Burst Mode which can automatically enable ADC0, capture and accumulate samples, then place ADC0 in a low power shutdown mode without CPU intervention. It also has a 16-bit accumulator that can automatically average the ADC results, providing an effective 11, 12, or 13 bit ADC result without any additional CPU intervention.

The ADC can sample the voltage at any of the GPIO pins (with the exception of P2.7) and has an on-chip attenuator that allows it to measure voltages up to twice the voltage reference. Additional ADC inputs include an on-chip temperature sensor, the VDD/DC+ supply voltage, the VBAT supply voltage, and the internal digital supply voltage.

Figure 1.7. ADC0 Functional Block Diagram

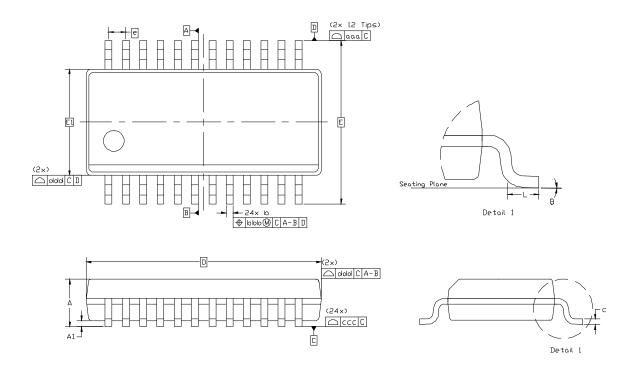

Figure 3.5. QSOP-24 Package Diagram

| Dimension | Min      | Nom      | Max      | ] | Dimension | Min Nom   |      | Ma  |

|-----------|----------|----------|----------|---|-----------|-----------|------|-----|

| А         |          | —        | 1.75     |   | е         | 0.635 BSC |      |     |

| A1        | 0.10     | —        | 0.25     |   | L         | 0.40 —    |      | 1.2 |

| b         | 0.20     | —        | 0.30     | l | θ         | 0°        | _    | 80  |

| С         | 0.10     |          | 0.25     | l | aaa       |           | 0.20 |     |

| D         |          | 8.65 BSC | <u>.</u> | Ī | bbb       |           | 0.18 |     |

| E         | 6.00 BSC |          |          | 1 | ссс       |           | 0.10 |     |

| E1        |          | 3.90 BSC |          | l | ddd       |           | 0.10 |     |

Table 3.4. QSOP-24 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MO-137, variation AE.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### 5.6. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to userprogrammed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

#### SFR Definition 5.8. ADC0GTH: ADC0 Greater-Than High Byte

| Bit   | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|-----------------|---|---|---|---|---|---|---|--|--|--|

| Name  | AD0GT[15:8]     |   |   |   |   |   |   |   |  |  |  |

| Туре  | R/W             |   |   |   |   |   |   |   |  |  |  |

| Reset | 1 1 1 1 1 1 1 1 |   |   |   |   |   |   |   |  |  |  |

#### SFR Page = 0x0; SFR Address = 0xC4

| Bit | Name        | Function                                                                  |

|-----|-------------|---------------------------------------------------------------------------|

| 7:0 | AD0GT[15:8] | ADC0 Greater-Than High Byte.                                              |

|     |             | Most Significant Byte of the 16-bit Greater-Than window compare register. |

#### SFR Definition 5.9. ADC0GTL: ADC0 Greater-Than Low Byte

| Bit   | 7 | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|---------------|---|---|---|---|---|---|--|--|--|

| Name  |   | AD0GT[7:0]    |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W           |   |   |   |   |   |   |  |  |  |

| Reset | 1 | 1 1 1 1 1 1 1 |   |   |   |   |   |   |  |  |  |

SFR Page = 0x0; SFR Address = 0xC3

| Bit   | Name           | Function                                                                   |

|-------|----------------|----------------------------------------------------------------------------|

| 7:0   | AD0GT[7:0]     | ADC0 Greater-Than Low Byte.                                                |

|       |                | Least Significant Byte of the 16-bit Greater-Than window compare register. |

| Note: | In 8-bit mode, | this register should be set to 0x00.                                       |

## SFR Definition 5.12. ADC0MX: ADC0 Input Channel Select

| Bit   | 7 | 6 | 5 | 4               | 3 | 2 | 1 | 0 |  |

|-------|---|---|---|-----------------|---|---|---|---|--|

| Name  |   |   |   | ADOMX           |   |   |   |   |  |

| Туре  | R | R | R | R/W R/W R/W R/W |   |   |   |   |  |

| Reset | 0 | 0 | 0 | 1               | 1 | 1 | 1 | 1 |  |

SFR Page = 0x0; SFR Address = 0xBB

| Bit | Name   |                              |                                                                                                                                                                                                              | Function                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                       |

|-----|--------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Unused | <b>Unused.</b><br>Read = 000 | 0b; Write = Don't Ca                                                                                                                                                                                         | re.                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                       |

| 4:0 | ADOMX  | AMUX0 Pc                     | Db; Write = Don't Ca<br>positive Input Select<br>positive input channel<br>P0.0<br>P0.1<br>P0.2<br>P0.3<br>P0.4<br>P0.5<br>P0.6<br>P0.7<br>P1.0<br>P1.1<br>P1.2<br>P1.3<br>P1.4<br>P1.5<br>P1.6<br>Reserved, | ion.<br>nel for ADC0.<br>10000:<br>10001:<br>10010:<br>10011:<br>10100:<br>10101:<br>10110:<br>11001:<br>11001:<br>11011:<br>11100:<br>11101:<br>11101: | Reserved.<br>Reserved.<br>Reserved.<br>Reserved.<br>Reserved.<br>Reserved.<br>Reserved.<br>Reserved.<br>Reserved.<br>Reserved.<br>Reserved.<br>Reserved.<br>Reserved.<br>Reserved.<br>Reserved.<br>Temperature Sensor<br>VBAT Supply Voltage<br>(0.9–1.8 V) or (1.8–3.6 V)<br>Digital Supply Voltage<br>(VREG0 Output, 1.7 V Typical) |

|     |        |                              |                                                                                                                                                                                                              | 11110:<br>111111:                                                                                                                                       | VDD/DC+ Supply Voltage<br>(1.8–3.6 V)<br>Ground                                                                                                                                                                                                                                                                                       |

#### 7.5. Comparator Register Descriptions

The SFRs used to enable and configure the comparators are described in the following register descriptions. A Comparator must be enabled by setting the CPnEN bit to logic 1 before it can be used. From an enabled state, a comparator can be disabled and placed in a low power state by clearing the CPnEN bit to logic 0.

**Important Note About Comparator Settings:** False rising and falling edges can be detected by the Comparator while powering on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed. The Comparator Power Up Time is specified in Section "Table 4.14. Comparator Electrical Characteristics" on page 58.

#### SFR Definition 7.1. CPT0CN: Comparator 0 Control

| Bit   | 7     | 6      | 5      | 4      | 3           | 2 | 1           | 0 |

|-------|-------|--------|--------|--------|-------------|---|-------------|---|

| Name  | CP0EN | CP0OUT | CP0RIF | CP0FIF | CP0HYP[1:0] |   | CP0HYN[1:0] |   |

| Туре  | R/W   | R      | R/W    | R/W    | R/W         |   | R/          | W |

| Reset | 0     | 0      | 0      | 0      | 0           | 0 | 0           | 0 |

SFR Page= 0x0; SFR Address = 0x9B

| Bit | Name        | Function                                                                                                                                          |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                                                                                           |

|     |             | 0: Comparator0 Disabled.<br>1: Comparator0 Enabled.                                                                                               |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                                                                                    |

|     |             | 0: Voltage on CP0+ < CP0<br>1: Voltage on CP0+ > CP0                                                                                              |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                                                                                        |

|     |             | <ul><li>0: No Comparator0 Rising Edge has occurred since this flag was last cleared.</li><li>1: Comparator0 Rising Edge has occurred.</li></ul>   |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                                                                                       |

|     |             | <ul><li>0: No Comparator0 Falling-Edge has occurred since this flag was last cleared.</li><li>1: Comparator0 Falling-Edge has occurred.</li></ul> |

| 3-2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                                                                                     |

|     |             | 00: Positive Hysteresis Disabled.                                                                                                                 |

|     |             | 01: Positive Hysteresis = Hysteresis 1.                                                                                                           |

|     |             | <ul><li>10: Positive Hysteresis = Hysteresis 2.</li><li>11: Positive Hysteresis = Hysteresis 3 (Maximum).</li></ul>                               |

| 1:0 | CP0HYN[1:0] | Comparator0 Negative Hysteresis Control Bits.                                                                                                     |

|     |             | 00: Negative Hysteresis Disabled.                                                                                                                 |

|     |             | 01: Negative Hysteresis = Hysteresis 1.                                                                                                           |

|     |             | 10: Negative Hysteresis = Hysteresis 2.                                                                                                           |

|     |             | 11: Negative Hysteresis = Hysteresis 3 (Maximum).                                                                                                 |

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

#### 8.2. Programming and Debugging Support

In-system programming of the Flash program memory and communication with on-chip debug support logic is accomplished via the Silicon Labs 2-Wire Development Interface (C2).

The on-chip debug support logic facilitates full speed in-circuit debugging, allowing the setting of hardware breakpoints, starting, stopping and single stepping through program execution (including interrupt service routines), examination of the program's call stack, and reading/writing the contents of registers and memory. This method of on-chip debugging is completely non-intrusive, requiring no RAM, Stack, timers, or other on-chip resources. C2 details can be found in Section "27. C2 Interface" on page 312.

The CIP-51 is supported by development tools from Silicon Labs and third party vendors. Silicon Labs provides an integrated development environment (IDE) including editor, debugger and programmer. The IDE's debugger and programmer interface to the CIP-51 via the C2 interface to provide fast and efficient in-system device programming and debugging. Third party macro assemblers and C compilers are also available.

#### 8.3. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 8.3.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 8.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

## SFR Definition 8.3. SP: Stack Pointer

| Bit     | 7            | 6               | 5            | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|--------------|-----------------|--------------|---|---|---|---|---|--|--|--|

| Name    | SP[7:0]      |                 |              |   |   |   |   |   |  |  |  |

| Туре    | R/W          |                 |              |   |   |   |   |   |  |  |  |

| Reset   | 0            | 0 0 0 0 0 1 1 1 |              |   |   |   |   |   |  |  |  |

| SFR Pag | ge = All Pag | es; SFR Add     | dress = 0x81 |   |   |   |   |   |  |  |  |

| Bit | Name    | Function                                                                                                                                                                       |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SP[7:0] | Stack Pointer.                                                                                                                                                                 |

|     |         | The Stack Pointer holds the location of the top of the stack. The stack pointer is incre-<br>mented before every PUSH operation. The SP register defaults to 0x07 after reset. |

#### SFR Definition 8.4. ACC: Accumulator

| Bit    | 7                                                         | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|--------|-----------------------------------------------------------|-----|---|---|---|---|---|---|--|--|--|

| Name   | ACC[7:0]                                                  |     |   |   |   |   |   |   |  |  |  |

| Туре   |                                                           | R/W |   |   |   |   |   |   |  |  |  |

| Reset  | 0                                                         | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

| SER Pa | SFR Page = All Pages: SFR Address = 0xE0: Bit-Addressable |     |   |   |   |   |   |   |  |  |  |

SFK Page = All Pages; SFK Address = 0xE0; Bit-Addressable

Bit

Name

Function

| Bit | Name     | Function                                                    |

|-----|----------|-------------------------------------------------------------|

| 7:0 | ACC[7:0] | Accumulator.                                                |

|     |          | This register is the accumulator for arithmetic operations. |

#### SFR Definition 8.5. B: B Register

| Bit   | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|--------|---|---|---|---|---|---|---|--|--|

| Name  | B[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R/W    |   |   |   |   |   |   |   |  |  |

| Reset | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Page = All Pages; SFR Address = 0xF0; Bit-Addressable

| ſ | Bit | Name   | Function                                                                        |

|---|-----|--------|---------------------------------------------------------------------------------|

|   | 7:0 | B[7:0] | B Register.                                                                     |

|   |     |        | This register serves as a second accumulator for certain arithmetic operations. |

#### Table 11.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved. SFRs highlighted in **blue** are only available on 'F912 and 'F902 devices.

| Register | Address | SFR Page | Description                          | Page |

|----------|---------|----------|--------------------------------------|------|

| CPT1MD   | 0x9C    | 0x0      | Comparator1 Mode Selection           | 94   |

| CPT1MX   | 0x9E    | 0x0      | Comparator1 Mux Selection            | 97   |

| CRC0AUTO | 0x96    | 0xF      | CRC0 Automatic Control               | 157  |

| CRC0CN   | 0x92    | 0xF      | CRC0 Control                         | 155  |

| CRC0CNT  | 0x97    | 0xF      | CRC0 Automatic Flash Sector Count    | 158  |

| CRC0DAT  | 0x91    | 0xF      | CRC0 Data                            | 156  |

| CRC0FLIP | 0x95    | 0xF      | CRC0 Flip                            | 159  |

| CRC0IN   | 0x93    | 0xF      | CRC0 Input                           | 156  |

| DC0CF    | 0x96    | 0x0      | DC0 (DC-DC Converter) Configuration  | 168  |

| DC0CN    | 0x97    | 0x0      | DC0 (DC-DC Converter) Control        | 167  |

| DC0MD    | 0x94    | 0xF      | DC0 (DC-DC Converter) Mode           | 169  |

| DPH      | 0x83    | All      | Data Pointer High                    | 104  |

| DPL      | 0x82    | All      | Data Pointer Low                     | 104  |

| EIE1     | 0xE6    | All      | Extended Interrupt Enable 1          | 126  |

| EIE2     | 0xE7    | All      | Extended Interrupt Enable 2          | 128  |

| EIP1     | 0xF6    | 0x0      | Extended Interrupt Priority 1        | 127  |

| EIP2     | 0xF7    | 0x0      | Extended Interrupt Priority 2        | 129  |

| EMI0CN   | 0xAA    | 0x0      | EMIF Control                         | 112  |

| FLKEY    | 0xB7    | 0x0      | Flash Lock And Key                   | 141  |

| FLSCL    | 0xB6    | 0x0      | Flash Scale                          | 141  |

| IE       | 0xA8    | All      | Interrupt Enable                     | 124  |

| IP       | 0xB8    | 0x0      | Interrupt Priority                   | 125  |

| IREF0CN  | 0xB9    | 0x0      | Current Reference IREF Control       | 86   |

| IREF0CF  | 0xB9    | 0xF      | Current Reference IREF Configuration | 87   |

| IT01CF   | 0xE4    | 0x0      | INT0/INT1 Configuration              | 131  |

| OSCICL   | 0xB3    | 0x0      | Internal Oscillator Calibration      | 186  |

| OSCICN   | 0xB2    | 0x0      | Internal Oscillator Control          | 186  |

| OSCXCN   | 0xB1    | 0x0      | External Oscillator Control          | 187  |

| P0       | 0x80    | All      | Port 0 Latch                         | 218  |

| P0DRV    | 0xA4    | 0xF      | Port 0 Drive Strength                | 220  |

| P0MASK   | 0xC7    | 0x0      | Port 0 Mask                          | 215  |

| POMAT    | 0xD7    | 0x0      | Port 0 Match                         | 215  |

| POMDIN   | 0xF1    | 0x0      | Port 0 Input Mode Configuration      | 219  |

## 13. Flash Memory

On-chip, re-programmable Flash memory is included for program code and non-volatile data storage. The Flash memory can be programmed in-system through the C2 interface or by software using the MOVX write instruction. Once cleared to logic 0, a Flash bit must be erased to set it back to logic 1. Flash bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution; data polling to determine the end of the write/erase operations is not required. Code execution is stalled during Flash write/erase operations. Refer to Table 4.6 for complete Flash memory electrical characteristics.

#### 13.1. Programming The Flash Memory

The simplest means of programming the Flash memory is through the C2 interface using programming tools provided by Silicon Laboratories or a third party vendor. This is the only means for programming a non-initialized device. For details on the C2 commands to program Flash memory, see Section "27. C2 Interface" on page 312.

The Flash memory can be programmed by software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before programming Flash memory using MOVX, Flash programming operations must be enabled by: (1) setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 (this directs the MOVX writes to target Flash memory); and (2) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY). The PSWE bit remains set until cleared by software. For detailed guidelines on programming Flash from firmware, please see Section "13.5. Flash Write and Erase Guidelines" on page 137.

To ensure the integrity of the Flash contents, the on-chip VDD Monitor must be enabled and enabled as a reset source in any system that includes code that writes and/or erases Flash memory from software. Furthermore, there should be no delay between enabling the  $V_{DD}$  Monitor and enabling the  $V_{DD}$  Monitor as a reset source. Any attempt to write or erase Flash memory while the  $V_{DD}$  Monitor is disabled, or not enabled as a reset source, will cause a Flash Error device reset.

#### 13.1.1. Flash Lock and Key Functions

Flash writes and erases by user software are protected with a lock and key function. The Flash Lock and Key Register (FLKEY) must be written with the correct key codes, in sequence, before Flash operations may be performed. The key codes are: 0xA5, 0xF1. The timing does not matter, but the codes must be written in order. If the key codes are written out of order, or the wrong codes are written, Flash writes and erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 13.2.

#### 14.2. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

# Note: To ensure the MCU enters a low power state upon entry into Idle Mode, the one-shot circuit should be enabled by clearing the BYPASS bit (FLSCL.6).

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to Section "18.6. PCA Watchdog Timer Reset" on page 176 for more information on the use and configuration of the WDT.

#### 14.3. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter stop mode as soon as the instruction that sets the bit completes execution. In stop mode the precision internal oscillator and CPU are stopped; the state of the low power oscillator and the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering stop mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout.

Stop mode is a legacy 8051 power mode; it will not result in optimal power savings. Sleep or suspend mode will provide more power savings if the MCU needs to be inactive for a long period of time.

# Note: To ensure the MCU enters a low power state upon entry into Stop Mode, the one-shot circuit should be enabled by clearing the BYPASS bit (FLSCL.6).

# 17. Voltage Regulator (VREG0)

C8051F91x-C8051F90x devices include an internal voltage regulator (VREG0) to regulate the internal core supply to 1.8 V from a VDD/DC+ supply of 1.8 to 3.6 V. Electrical characteristics for the on-chip regulator are specified in the Electrical Specifications chapter.

The REGOCN register allows the Precision Oscillator Bias to be disabled, reducing supply current in all non-Sleep power modes. This bias should only be disabled when the precision oscillator is not being used.

The internal regulator (VREG0) is disabled when the device enters Sleep Mode and remains enabled when the device enters Suspend Mode. See Section "14. Power Management" on page 143 for complete details about low power modes.

#### SFR Definition 17.1. REG0CN: Voltage Regulator Control

| Bit   | 7 | 6        | 5        | 4       | 3 | 2 | 1 | 0        |

|-------|---|----------|----------|---------|---|---|---|----------|

| Name  |   | Reserved | Reserved | OSCBIAS |   |   |   | Reserved |

| Туре  | R | R/W      | R/W      | R/W     | R | R | R | R/W      |

| Reset | 0 | 0        | 0        | 1       | 0 | 0 | 0 | 0        |

#### SFR Page = 0x0; SFR Address = 0xC9

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                            |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused   | Unused.                                                                                                                                                                                                                                                                                                                             |

|     |          | Read = 0b. Write = Don't care.                                                                                                                                                                                                                                                                                                      |

| 6   | Reserved | Reserved.                                                                                                                                                                                                                                                                                                                           |

|     |          | Read = 0b. Must Write 0b.                                                                                                                                                                                                                                                                                                           |

| 5   | Reserved | Reserved.                                                                                                                                                                                                                                                                                                                           |

|     |          | Read = 0b. Must Write 0b.                                                                                                                                                                                                                                                                                                           |

| 4   | OSCBIAS  | Precision Oscillator Bias.                                                                                                                                                                                                                                                                                                          |

|     |          | When set to 1, the bias used by the precision oscillator is forced on. If the precision oscillator is not being used, this bit may be cleared to 0 to save approximately 80 $\mu$ A of supply current in all non-Sleep power modes. If disabled then re-enabled, the precision oscillator bias requires 4 $\mu$ s of settling time. |

| 3:1 | Unused   | Unused.                                                                                                                                                                                                                                                                                                                             |

|     |          | Read = 000b. Write = Don't care.                                                                                                                                                                                                                                                                                                    |

| 0   | Reserved | Reserved.                                                                                                                                                                                                                                                                                                                           |

|     |          | Read = 0b. Must Write 0b.                                                                                                                                                                                                                                                                                                           |

#### 17.1. Voltage Regulator Electrical Specifications

See Table 4.15 on page 59 for detailed Voltage Regulator Electrical Specifications.

#### **19.4.** Special Function Registers for Selecting and Configuring the System Clock

The clocking sources on C8051F91x-C8051F90x devices are enabled and configured using the OSCICN, OSCICL, OSCXCN and the SmaRTClock internal registers. See Section "20. SmaRTClock (Real Time Clock)" on page 188 for SmaRTClock register descriptions. The system clock source for the MCU can be selected using the CLKSEL register. To minimize active mode current, the oneshot timer which sets Flash read time should by bypassed when the system clock is greater than 10 MHz. See the FLSCL register description for details.

The clock selected as the system clock can be divided by 1, 2, 4, 8, 16, 32, 64, or 128. When switching between two clock divide values, the transition may take up to 128 cycles of the undivided clock source. The CLKRDY flag can be polled to determine when the new clock divide value has been applied. The clock divider must be set to "divide by 1" when entering Suspend or Sleep Mode.

The system clock source may also be switched on-the-fly. The switchover takes effect after one clock period of the slower oscillator.

| SFR Definition 19.1 | . CLKSEL: Clock Select |

|---------------------|------------------------|

|---------------------|------------------------|

| Bit   | 7      | 6   | 5           | 4   | 3   | 2           | 1   | 0   |  |

|-------|--------|-----|-------------|-----|-----|-------------|-----|-----|--|

| Name  | CLKRDY |     | CLKDIV[2:0] |     |     | CLKSEL[2:0] |     |     |  |

| Туре  | R      | R/W | R/W         | R/W | R/W | R/W         | R/W | R/W |  |

| Reset | 0      | 0   | 1           | 1   | 0   | 1           | 0   | 0   |  |

SFR Page = All Pages; SFR Address = 0xA9

| Bit | Name        | Function                                                                       |

|-----|-------------|--------------------------------------------------------------------------------|

| 7   | CLKRDY      | System Clock Divider Clock Ready Flag.                                         |

|     |             | 0: The selected clock divide setting has not been applied to the system clock. |

|     |             | 1: The selected clock divide setting has been applied to the system clock.     |

| 6:4 | CLKDIV[2:0] | System Clock Divider Bits.                                                     |

|     |             | Selects the clock division to be applied to the undivided system clock source. |

|     |             | 000: System clock is divided by 1.                                             |

|     |             | 001: System clock is divided by 2.                                             |

|     |             | 010: System clock is divided by 4.                                             |

|     |             | 011: System clock is divided by 8.                                             |

|     |             | 100: System clock is divided by 16.                                            |

|     |             | 101: System clock is divided by 32.                                            |

|     |             | 110: System clock is divided by 64.                                            |

|     |             | 111: System clock is divided by 128.                                           |

| 3   | Unused      | Unused.                                                                        |

|     |             | Read = 0b. Must Write 0b.                                                      |

| 2:0 | CLKSEL[2:0] | System Clock Select.                                                           |

|     |             | Selects the oscillator to be used as the undivided system clock source.        |

|     |             | 000: Precision Internal Oscillator.                                            |

|     |             | 001: External Oscillator.                                                      |

|     |             | 011: SmaRTClock Oscillator.                                                    |

|     |             | 100: Low Power Oscillator.                                                     |

|     |             | All other values reserved.                                                     |

# C8051F91x-C8051F90x

## SFR Definition 21.3. XBR2: Port I/O Crossbar Register 2

| Bit   | 7       | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---------|-------|-----|-----|-----|-----|-----|-----|

| Name  | WEAKPUD | XBARE |     |     |     |     |     |     |

| Туре  | R/W     | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0       | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Page = 0x0; SFR Address = 0xE3

| Bit     | Name                                                                                           | Function                                                                                                               |  |  |  |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 7       | WEAKPUD                                                                                        | <b>Port I/O Weak Pullup Disable.</b><br>0: Weak Pullups enabled (except for Port I/O pins configured for analog mode). |  |  |  |  |  |  |  |  |

| 6       | XBARE                                                                                          | Crossbar Enable.                                                                                                       |  |  |  |  |  |  |  |  |

|         |                                                                                                | 0: Crossbar disabled.<br>1: Crossbar enabled.                                                                          |  |  |  |  |  |  |  |  |

| 5:0     | Unused                                                                                         | Unused.                                                                                                                |  |  |  |  |  |  |  |  |

|         |                                                                                                | Read = 000000b; Write = Don't Care.                                                                                    |  |  |  |  |  |  |  |  |

| Note: T | <b>Note:</b> The Crossbar must be enabled (XBARE = 1) to use any Port pin as a digital output. |                                                                                                                        |  |  |  |  |  |  |  |  |

### SFR Definition 22.3. SMB0ADR: SMBus Slave Address

| Bit   | 7        | 6 | 5 | 4 | 3 | 2 | 2 1 |  |  |  |  |

|-------|----------|---|---|---|---|---|-----|--|--|--|--|

| Name  | SLV[6:0] |   |   |   |   |   |     |  |  |  |  |

| Туре  | R/W      |   |   |   |   |   |     |  |  |  |  |

| Reset | 0        | 0 | 0 | 0 | 0 | 0 | 0   |  |  |  |  |

SFR Page = 0x0; SFR Address = 0xF4

| Bit | Name     | Function                                                                                                                                                                                                                                                                   |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLV[6:0] | SMBus Hardware Slave Address.                                                                                                                                                                                                                                              |

|     |          | Defines the SMBus Slave Address(es) for automatic hardware acknowledgement.<br>Only address bits which have a 1 in the corresponding bit position in SLVM[6:0]<br>are checked against the incoming address. This allows multiple addresses to be<br>recognized.            |

| 0   | GC       | General Call Address Enable.                                                                                                                                                                                                                                               |

|     |          | <ul> <li>When hardware address recognition is enabled (EHACK = 1), this bit will determine whether the General Call Address (0x00) is also recognized by hardware.</li> <li>0: General Call Address is ignored.</li> <li>1: General Call Address is recognized.</li> </ul> |

#### SFR Definition 22.4. SMB0ADM: SMBus Slave Address Mask

| Bit   | 7         | 7 6 5 4 3 2 1 |  |  |  |  |  |  |  |  |  |  |

|-------|-----------|---------------|--|--|--|--|--|--|--|--|--|--|

| Name  | SLVM[6:0] |               |  |  |  |  |  |  |  |  |  |  |

| Туре  | R/W       |               |  |  |  |  |  |  |  |  |  |  |

| Reset |           |               |  |  |  |  |  |  |  |  |  |  |

#### SFR Page = 0x0; SFR Address = 0xF5

| Bit | Name      | Function                                                                                                                                                                                                                                                                           |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLVM[6:0] | SMBus Slave Address Mask.                                                                                                                                                                                                                                                          |

|     |           | Defines which bits of register SMB0ADR are compared with an incoming address byte, and which bits are ignored. Any bit set to 1 in SLVM[6:0] enables comparisons with the corresponding bit in SLV[6:0]. Bits set to 0 are ignored (can be either 0 or 1 in the incoming address). |

| 0   | EHACK     | Hardware Acknowledge Enable.                                                                                                                                                                                                                                                       |

|     |           | Enables hardware acknowledgement of slave address and received data bytes.<br>0: Firmware must manually acknowledge all incoming address and data bytes.<br>1: Automatic Slave Address Recognition and Hardware Acknowledge is Enabled.                                            |

# C8051F91x-C8051F90x

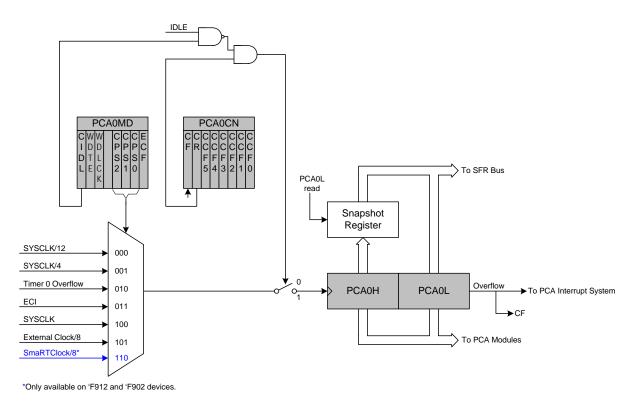

#### 26.2. PCA0 Interrupt Sources

Figure 26.3 shows a diagram of the PCA interrupt tree. There are eight independent event flags that can be used to generate a PCA0 interrupt. They are: the main PCA counter overflow flag (CF), which is set upon a 16-bit overflow of the PCA0 counter, an intermediate overflow flag (COVF), which can be set on an overflow from the 8th, 9th, 10th, or 11th bit of the PCA0 counter, and the individual flags for each PCA channel (CCF0, CCF1, CCF2, CCF3, CCF4, and CCF5), which are set according to the operation mode of that module. These event flags are always set when the trigger condition occurs. Each of these flags can be individually selected to generate a PCA0 interrupt, using the corresponding interrupt enable flag (ECF for CF, ECOV for COVF, and ECCFn for each CCFn). PCA0 interrupts must be globally enabled before any individual interrupt sources are recognized by the processor. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1.

#### 26.3. Capture/Compare Modules

Each module can be configured to operate independently in one of six operation modes: edge-triggered capture, software timer, high speed output, frequency output, 8 to 11-bit pulse width modulator, or 16-bit pulse width modulator. Each module has special function registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation. Table 26.2 summarizes the bit settings in the PCA0CPMn and PCA0PWM registers used to select the PCA capture/compare module's operating mode. Note that all modules set to use 8, 9, 10, or 11-bit PWM mode must use the same cycle length (8-11 bits). Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt.

| Operational Mode                                                                                                                                                                                                                                                                                                         |   |   | PC | A0 | СР | Mn |   |   |   | Ρ | CA | 0PWN |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|----|----|----|----|---|---|---|---|----|------|-----|

| Bit Number                                                                                                                                                                                                                                                                                                               | 7 | 6 | 5  | 4  | 3  | 2  | 1 | 0 | 7 | 6 | 5  | 4-2  | 1–0 |

| Capture triggered by positive edge on CEXn                                                                                                                                                                                                                                                                               | Х | Х | 1  | 0  | 0  | 0  | 0 | Α | 0 | Х | В  | XXX  | XX  |

| Capture triggered by negative edge on CEXn                                                                                                                                                                                                                                                                               | Х | Х | 0  | 1  | 0  | 0  | 0 | А | 0 | Х | В  | XXX  | XX  |

| Capture triggered by any transition on CEXn                                                                                                                                                                                                                                                                              | Х | Х | 1  | 1  | 0  | 0  | 0 | А | 0 | Х | В  | XXX  | XX  |

| Software Timer                                                                                                                                                                                                                                                                                                           | Х | С | 0  | 0  | 1  | 0  | 0 | Α | 0 | Х | В  | XXX  | XX  |

| High-Speed Output                                                                                                                                                                                                                                                                                                        | Х | С | 0  | 0  | 1  | 1  | 0 | Α | 0 | Х | В  | XXX  | XX  |

| Frequency Output                                                                                                                                                                                                                                                                                                         | Х | С | 0  | 0  | 0  | 1  | 1 | Α | 0 | Х | В  | XXX  | XX  |

| 8-Bit Pulse Width Modulator (Note 7)                                                                                                                                                                                                                                                                                     | 0 | С | 0  | 0  | Е  | 0  | 1 | Α | 0 | Х | В  | XXX  | 00  |

| 9-Bit Pulse Width Modulator (Note 7)                                                                                                                                                                                                                                                                                     | 0 | С | 0  | 0  | Е  | 0  | 1 | А | D | Х | В  | XXX  | 01  |

| 10-Bit Pulse Width Modulator (Note 7)                                                                                                                                                                                                                                                                                    | 0 | С | 0  | 0  | Е  | 0  | 1 | А | D | Х | В  | XXX  | 10  |

| 11-Bit Pulse Width Modulator (Note 7)                                                                                                                                                                                                                                                                                    | 0 | С | 0  | 0  | Е  | 0  | 1 | А | D | Х | В  | XXX  | 11  |

| 16-Bit Pulse Width Modulator                                                                                                                                                                                                                                                                                             | 1 | С | 0  | 0  | Е  | 0  | 1 | А | 0 | Х | В  | XXX  | XX  |

| <ul> <li>Notes:</li> <li>1. X = Don't Care (no functional difference for individual module if 1 or 0).</li> <li>2. A = Enable interrupts for this module (PCA interrupt triggered on CCFn set to 1).</li> <li>3. B = Enable 8th, 9th, 10th or 11th bit overflow interrupt (Depends on setting of CLSEL[1:0]).</li> </ul> |   |   |    |    |    |    |   |   |   |   |    |      |     |

#### Table 26.2. PCA0CPM and PCA0PWM Bit Settings for PCA Capture/Compare Modules

C = When set to 0, the digital comparator is off. For high speed and frequency output modes, the associated pin will not toggle. In any of the PWM modes, this generates a 0% duty cycle (output = 0).

5. D = Selects whether the Capture/Compare register (0) or the Auto-Reload register (1) for the associated channel is accessed via addresses PCA0CPHn and PCA0CPLn.

6. E = When set, a match event will cause the CCFn flag for the associated channel to be set.

7. All modules set to 8, 9, 10 or 11-bit PWM mode use the same cycle length setting.

### SFR Definition 26.2. PCA0MD: PCA Mode

| Bit   | 7                                                                                                                                                                                  | 6                                                                                                                                                                                                                                                                                        | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4    | 3    | 2    | 1    | 0   |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-----|--|--|--|--|--|

| Nam   | e CIDL                                                                                                                                                                             | WDTE                                                                                                                                                                                                                                                                                     | WDLCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | CPS2 | CPS1 | CPS0 | ECF |  |  |  |  |  |

| Туре  | R/W                                                                                                                                                                                | R/W                                                                                                                                                                                                                                                                                      | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R    | R/W  | R/W  | R/W  | R/W |  |  |  |  |  |

| Rese  | t O                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0    | 0    | 0    | 0    | 0   |  |  |  |  |  |

| SFR F | age = 0x0;                                                                                                                                                                         | SFR Address = 0xD9                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |      |      |      |     |  |  |  |  |  |

| Bit   | Name                                                                                                                                                                               | Function                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |      |      |      |     |  |  |  |  |  |

| 7     | CIDL                                                                                                                                                                               | Specifies PCA<br>0: PCA contin                                                                                                                                                                                                                                                           | <ul> <li>PCA Counter/Timer Idle Control.</li> <li>Specifies PCA behavior when CPU is in Idle Mode.</li> <li>0: PCA continues to function normally while the system controller is in Idle Mode.</li> <li>1: PCA operation is suspended while the system controller is in Idle Mode.</li> </ul>                                                                                                                                                                                                                                                                                   |      |      |      |      |     |  |  |  |  |  |

| 6     | WDTE                                                                                                                                                                               | If this bit is se<br>0: Watchdog                                                                                                                                                                                                                                                         | Watchdog Timer Enable.         If this bit is set, PCA Module 2 is used as the watchdog timer.         0: Watchdog Timer disabled.         1: PCA Module 2 enabled as Watchdog Timer.                                                                                                                                                                                                                                                                                                                                                                                           |      |      |      |      |     |  |  |  |  |  |

| 5     | WDLCK                                                                                                                                                                              | This bit locks/<br>Timer may no<br>0: Watchdog 1<br>1: Watchdog 1                                                                                                                                                                                                                        | Watchdog Timer Lock.<br>This bit locks/unlocks the Watchdog Timer Enable. When WDLCK is set, the Watchdog<br>Timer may not be disabled until the next system reset.<br>0: Watchdog Timer Enable unlocked.<br>1: Watchdog Timer Enable locked.                                                                                                                                                                                                                                                                                                                                   |      |      |      |      |     |  |  |  |  |  |

| 4     | Unused                                                                                                                                                                             | Read = 0b, W                                                                                                                                                                                                                                                                             | rite = don't c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | are. |      |      |      |     |  |  |  |  |  |

| 3:1   | CPS[2:0]                                                                                                                                                                           | These bits sel<br>000: System of<br>001: System of<br>010: Timer 0 of<br>011: High-to-lo<br>100: System of<br>101: External<br>110: SmaRTC                                                                                                                                               | PCA Counter/Timer Pulse Select.         These bits select the timebase source for the PCA counter         000: System clock divided by 12         001: System clock divided by 4         010: Timer 0 overflow         011: High-to-low transitions on ECI (max rate = system clock divided by 4)         100: System clock         101: External clock divided by 8 (synchronized with the system clock)         110: SmaRTClock divided by 8 (synchronized with the system clock and only available on 'F912 and 'F902 devices this setting is reserved on all other devices) |      |      |      |      |     |  |  |  |  |  |

| 0     | ECF                                                                                                                                                                                | <ul> <li>PCA Counter/Timer Overflow Interrupt Enable.</li> <li>This bit sets the masking of the PCA Counter/Timer Overflow (CF) interrupt.</li> <li>0: Disable the CF interrupt.</li> <li>1: Enable a PCA Counter/Timer Overflow interrupt request when CF (PCA0CN.7) is set.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |      |      |      |     |  |  |  |  |  |

| Note: | When the WDTE bit is set to 1, the other bits in the PCA0MD register cannot be modified. To change the contents of the PCA0MD register, the Watchdog Timer must first be disabled. |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |      |      |      |     |  |  |  |  |  |

# DOCUMENT CHANGE LIST

#### **Revision 0.2 to Revision 1.0**

- Updated specification tables to remove TBDs.

- Updated power management section to indicate that the low power or precision oscillator must be selected when entering sleep or suspend mode.

- Updated Port I/O chapter with additional clarification on 5 V and 3.3 V tolerance.

- Updated QFN-42 landing diagram and stencil recommendations.

- Updated description of ADC0 12-bit mode.

#### **Revision 1.0 to Revision 1.1**

Removed references to AN338.

NOTES: