# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                     |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 16                                                                |

| Program Memory Size        | 8KB (8K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 768 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                       |

| Data Converters            | A/D 15x10/12b                                                     |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                    |

| Supplier Device Package    | 24-QSOP                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f902-d-gur |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 4.2. Global Electrical Characteristics (Continued)-40 to +85 °C, 25 MHz system clock unless otherwise specified. See "AN358: Optimizing Low Power Operation of the 'F9xx" for details on how to achieve the supply current specifications listed in this table.

| Parameter                                                                                          | Conditions                                                                      | Min | Тур  | Max | Units |

|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----|------|-----|-------|

| Digital Supply Current—Suspe                                                                       | end and Sleep Mode                                                              |     |      |     |       |

| Digital Supply Current <sup>6</sup><br>(Suspend Mode)                                              | V <sub>DD</sub> = 1.8–3.6 V, two-cell mode                                      | —   | 77   | —   | μA    |

| Digital Supply Current                                                                             | 1.8 V, T = 25 °C                                                                |     | 0.60 | _   | μA    |

| (Sleep Mode, SmaRTClock run-                                                                       | 3.0 V, T = 25 °C                                                                | —   | 0.75 | —   |       |

| ning, 32.768 kHz crystal)                                                                          | 3.6 V, T = 25 °C                                                                |     | 0.85 |     |       |

|                                                                                                    | 1.8 V, T = 85 °C                                                                | —   | 1.30 | —   |       |

|                                                                                                    | 3.0 V, T = 85 °C                                                                |     | 1.60 |     |       |

|                                                                                                    | 3.6 V, T = 85 °C                                                                |     | 1.90 |     |       |

|                                                                                                    | (includes SmaRTClock oscillator and VBAT Supply Monitor)                        |     |      |     |       |

| Digital Supply Current <sup>8</sup><br>(Sleep Mode, SmaRTClock run-<br>ning, <b>internal LFO</b> ) | 1.8 V, T = 25 °C<br>(includes SmaRTClock oscillator and VBAT<br>Supply Monitor) | —   | 0.3  | —   | μΑ    |

| Digital Supply Current                                                                             | 1.8 V, T = 25 °C                                                                |     | 0.05 |     | μA    |

| (Sleep Mode)                                                                                       | 3.0 V, T = 25 °C                                                                |     | 0.08 | —   |       |

|                                                                                                    | 3.6 V, T = 25 °C                                                                |     | 0.12 | —   |       |

|                                                                                                    | 1.8 V, T = 85 °C                                                                | —   | 0.75 | —   |       |

|                                                                                                    | 3.0 V, T = 85 °C                                                                |     | 0.90 |     |       |

|                                                                                                    | 3.6 V, T = 85 °C                                                                | —   | 1.20 | —   |       |

|                                                                                                    | (includes VBAT supply monitor)                                                  |     |      |     |       |

| Digital Supply Current (Sleep<br>Mode, VBAT Supply Monitor<br>Disabled) <sup>9</sup>               | 1.8 V, T = 25 °C                                                                | —   | 0.01 | _   | μA    |

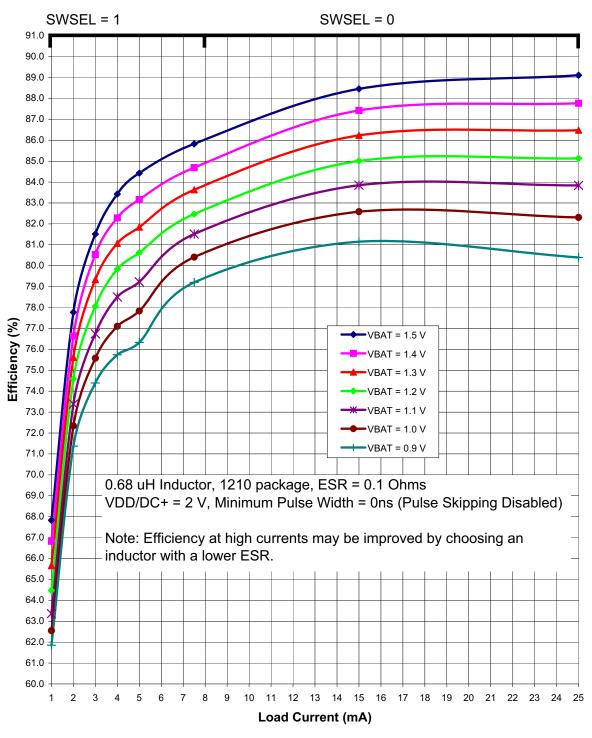

Figure 4.3. Typical DC-DC Converter Efficiency (High Current, VDD/DC+ = 2 V)

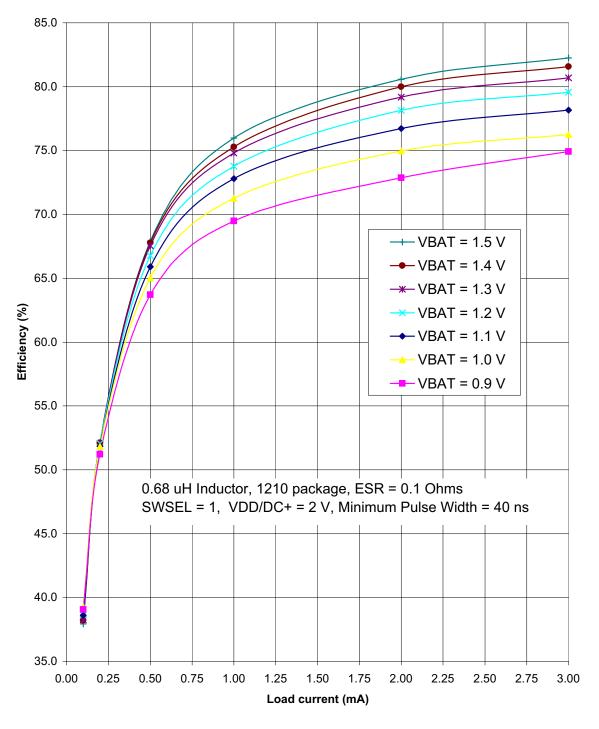

Figure 4.5. Typical DC-DC Converter Efficiency (Low Current, VDD/DC+ = 2 V)

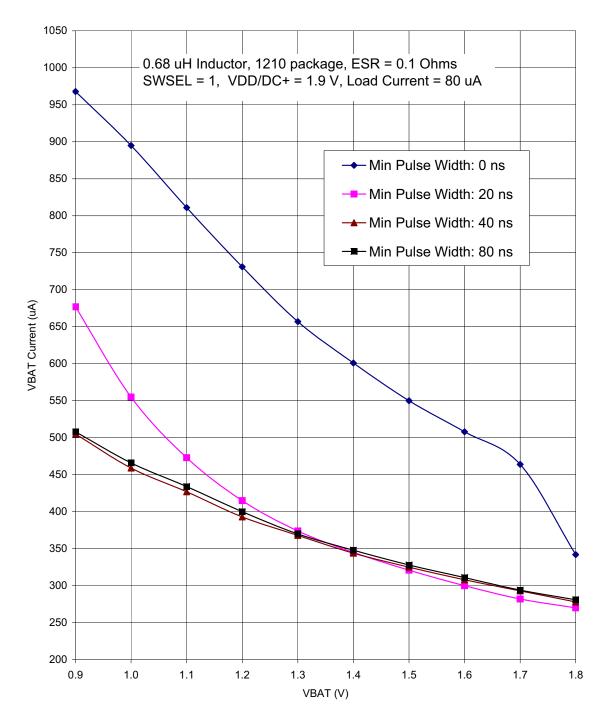

Figure 4.6. Typical One-Cell Suspend Mode Current

# SFR Definition 5.1. ADC0CN: ADC0 Control

| Bit   | 7     | 6       | 5      | 4       | 3       | 2      | 1 | 0 |

|-------|-------|---------|--------|---------|---------|--------|---|---|

| Name  | AD0EN | BURSTEN | AD0INT | AD0BUSY | AD0WINT | ADC0CM |   |   |

| Туре  | R/W   | R/W     | R/W    | W       | R/W     | R/W    |   |   |

| Reset | 0     | 0       | 0      | 0       | 0       | 0      | 0 | 0 |

SFR Page = 0x0; SFR Address = 0xE8; bit-addressable

| Bit   | Name        | Function                                                                                                                                                                                 |

|-------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | AD0EN       | ADC0 Enable.                                                                                                                                                                             |

|       |             | 0: ADC0 Disabled (low-power shutdown).                                                                                                                                                   |

|       |             | 1: ADC0 Enabled (active and ready for data conversions).                                                                                                                                 |

| 6     | BURSTEN     | ADC0 Burst Mode Enable.                                                                                                                                                                  |

|       |             | 0: ADC0 Burst Mode Disabled.                                                                                                                                                             |

|       |             | 1: ADC0 Burst Mode Enabled.                                                                                                                                                              |

| 5     | AD0INT      | ADC0 Conversion Complete Interrupt Flag.                                                                                                                                                 |

|       |             | Set by hardware upon completion of a data conversion (BURSTEN=0), or a burst of conversions (BURSTEN=1). Can trigger an interrupt. Must be cleared by software.                          |

| 4     | AD0BUSY     | ADC0 Busy.                                                                                                                                                                               |

|       |             | Writing 1 to this bit initiates an ADC conversion when ADC0CM[2:0] = 000.                                                                                                                |

| 3     | ADOWINT     | ADC0 Window Compare Interrupt Flag.                                                                                                                                                      |

|       |             | Set by hardware when the contents of ADC0H:ADC0L fall within the window speci-<br>fied by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL. Can trigger an interrupt.<br>Must be cleared by software. |

| 2:0   | ADC0CM[2:0] | ADC0 Start of Conversion Mode Select.                                                                                                                                                    |

|       |             | Specifies the ADC0 start of conversion source.                                                                                                                                           |

|       |             | 000: ADC0 conversion initiated on write of 1 to AD0BUSY.                                                                                                                                 |

|       |             | 001: ADC0 conversion initiated on overflow of Timer 0.                                                                                                                                   |

|       |             | 010: ADC0 conversion initiated on overflow of Timer 2.                                                                                                                                   |

|       |             | 011: ADC0 conversion initiated on overflow of Timer 3.                                                                                                                                   |

|       |             | 1xx: ADC0 conversion initiated on rising edge of CNVSTR.                                                                                                                                 |

| Note: |             |                                                                                                                                                                                          |

# SFR Definition 5.13. TOFFH: ADC0 Data Word High Byte

| Bit   | 7      | 6         | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------|-----------|--------|--------|--------|--------|--------|--------|

| Name  |        | TOFF[9:2] |        |        |        |        |        |        |

| Туре  | R      | R         | R      | R      | R      | R      | R      | R      |

| Reset | Varies | Varies    | Varies | Varies | Varies | Varies | Varies | Varies |

SFR Page = 0xF; SFR Address = 0x86

| Bit | Name      | Function                                                                   |

|-----|-----------|----------------------------------------------------------------------------|

| 7:0 | TOFF[9:2] | Temperature Sensor Offset High Bits.                                       |

|     |           | Most Significant Bits of the 10-bit temperature sensor offset measurement. |

# SFR Definition 5.14. TOFFL: ADC0 Data Word Low Byte

| Bit   | 7         | 6      | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------|--------|---|---|---|---|---|---|

| Name  | TOFF[1:0] |        |   |   |   |   |   |   |

| Туре  | R         | R      |   |   |   |   |   |   |

| Reset | Varies    | Varies | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0xF; SFR Address = 0x85

| Bit | Name      | Function                                                                    |

|-----|-----------|-----------------------------------------------------------------------------|

| 7:6 | TOFF[1:0] | Temperature Sensor Offset Low Bits.                                         |

|     |           | Least Significant Bits of the 10-bit temperature sensor offset measurement. |

| 5:0 | Unused    | Unused.                                                                     |

|     |           | Read = 0; Write = Don't Care.                                               |

### 10.2. Special Function Registers

The special function register used for configuring XRAM access is EMI0CN.

# SFR Definition 10.1. EMI0CN: External Memory Interface Control

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0     |

|-------|-----|-----|-----|-----|-----|-----|-----|-------|

| Name  |     |     |     |     |     |     |     | PGSEL |

| Туре  | R/W   |

| Reset | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0     |

SFR Page = 0x0; SFR Address = 0xAA

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | Unused | Unused.                                                                                                                                                                                                                                                                                                                                                                                                |

|     |        | Read = 0000000b; Write = Don't Care                                                                                                                                                                                                                                                                                                                                                                    |

| 0   | PGSEL  | XRAM Page Select.The EMIOCN register provides the high byte of the 16-bit external data memory<br>address when using an 8-bit MOVX command, effectively selecting a 256-byte page<br>of RAM. Since the upper (unused) bits of the register are always zero, the PGSEL<br>determines which page of XRAM is accessed.For Example:<br>If EMIOCN = 0x01, addresses 0x0100 through 0x01FF will be accessed. |

|     |        | If EMIOCN = 0x00, addresses 0x0000 through 0x00FF will be accessed.                                                                                                                                                                                                                                                                                                                                    |

# SFR Definition 11.1. SFR Page: SFR Page

| Bit   | 7 | 6   | 5 | 4     | 3       | 2 | 1 | 0 |

|-------|---|-----|---|-------|---------|---|---|---|

| Name  |   |     |   | SFRPA | GE[7:0] |   |   |   |

| Туре  |   | R/W |   |       |         |   |   |   |

| Reset | 0 | 0   | 0 | 0     | 0       | 0 | 0 | 0 |

SFR Page = All Pages; SFR Address = 0xA7

| Bit | Name         | Function                                                                                    |

|-----|--------------|---------------------------------------------------------------------------------------------|

| 7:0 | SFRPAGE[7:0] | SFR Page.                                                                                   |

|     |              | Specifies the SFR Page used when reading, writing, or modifying special function registers. |

### Table 11.3. Special Function Registers

SFRs are listed in alphabetical order. All undefined SFR locations are reserved. SFRs highlighted in **blue** are only available on 'F912 and 'F902 devices.

| Register | Address | SFR Page | Description                      | Page |

|----------|---------|----------|----------------------------------|------|

| ACC      | 0xE0    | All      | Accumulator                      | 105  |

| ADC0AC   | 0xBA    | 0x0      | ADC0 Accumulator Configuration   | 71   |

| ADC0CF   | 0xBC    | 0x0      | ADC0 Configuration               | 70   |

| ADC0CN   | 0xE8    | 0x0      | ADC0 Control                     | 69   |

| ADC0GTH  | 0xC4    | 0x0      | ADC0 Greater-Than Compare High   | 75   |

| ADC0GTL  | 0xC3    | 0x0      | ADC0 Greater-Than Compare Low    | 75   |

| ADC0H    | 0xBE    | 0x0      | ADC0 High                        | 74   |

| ADC0L    | 0xBD    | 0x0      | ADC0 Low                         | 74   |

| ADC0LTH  | 0xC6    | 0x0      | ADC0 Less-Than Compare Word High | 76   |

| ADC0LTL  | 0xC5    | 0x0      | ADC0 Less-Than Compare Word Low  | 76   |

| ADC0MX   | 0xBB    | 0x0      | AMUX0 Channel Select             | 79   |

| ADC0PWR  | 0xBA    | 0xF      | ADC0 Burst Mode Power-Up Time    | 72   |

| ADC0TK   | 0xBD    | 0xF      | ADC0 Tracking Control            | 73   |

| В        | 0xF0    | All      | B Register                       | 105  |

| CKCON    | 0x8E    | 0x0      | Clock Control                    | 271  |

| CLKSEL   | 0xA9    | All      | Clock Select                     | 185  |

| CPT0CN   | 0x9B    | 0x0      | Comparator0 Control              | 92   |

| CPT0MD   | 0x9D    | 0x0      | Comparator0 Mode Selection       | 92   |

| CPT0MX   | 0x9F    | 0x0      | Comparator0 Mux Selection        |      |

| CPT1CN   | 0x9A    | 0x0      | Comparator1 Control              | 93   |

# 13. Flash Memory

On-chip, re-programmable Flash memory is included for program code and non-volatile data storage. The Flash memory can be programmed in-system through the C2 interface or by software using the MOVX write instruction. Once cleared to logic 0, a Flash bit must be erased to set it back to logic 1. Flash bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution; data polling to determine the end of the write/erase operations is not required. Code execution is stalled during Flash write/erase operations. Refer to Table 4.6 for complete Flash memory electrical characteristics.

# 13.1. Programming The Flash Memory

The simplest means of programming the Flash memory is through the C2 interface using programming tools provided by Silicon Laboratories or a third party vendor. This is the only means for programming a non-initialized device. For details on the C2 commands to program Flash memory, see Section "27. C2 Interface" on page 312.

The Flash memory can be programmed by software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before programming Flash memory using MOVX, Flash programming operations must be enabled by: (1) setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 (this directs the MOVX writes to target Flash memory); and (2) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY). The PSWE bit remains set until cleared by software. For detailed guidelines on programming Flash from firmware, please see Section "13.5. Flash Write and Erase Guidelines" on page 137.

To ensure the integrity of the Flash contents, the on-chip VDD Monitor must be enabled and enabled as a reset source in any system that includes code that writes and/or erases Flash memory from software. Furthermore, there should be no delay between enabling the  $V_{DD}$  Monitor and enabling the  $V_{DD}$  Monitor as a reset source. Any attempt to write or erase Flash memory while the  $V_{DD}$  Monitor is disabled, or not enabled as a reset source, will cause a Flash Error device reset.

#### 13.1.1. Flash Lock and Key Functions

Flash writes and erases by user software are protected with a lock and key function. The Flash Lock and Key Register (FLKEY) must be written with the correct key codes, in sequence, before Flash operations may be performed. The key codes are: 0xA5, 0xF1. The timing does not matter, but the codes must be written in order. If the key codes are written out of order, or the wrong codes are written, Flash writes and erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 13.2.

# 16. On-Chip DC-DC Converter (DC0)

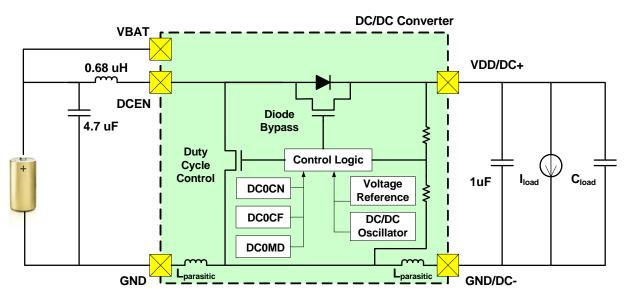

C8051F91x-C8051F90x devices include an on-chip dc-dc converter to allow operation from a single cell battery with a supply voltage as low as 0.9 V. The dc-dc converter is a switching boost converter with an input voltage range of 0.9 to 1.8 V (C8051F911/01) or 3.6 V (C8051F912/11) and a programmable output voltage range of 1.8 to 3.3 V. The default output voltage is 1.9 V when the input is less than 1.9 V. Since the dc-dc converter uses a boost architecture, the output voltage will always be greater than or equal to the input voltage. The dc-dc converter can supply the system with up to 65 mW of regulated power (or up to 100 mW in some applications) and can be used for powering other devices in the system. This allows the most flexibility when interfacing to sensors and other analog signals which typically require a higher supply voltage than a single-cell battery can provide.

Figure 16.1 shows a block diagram of the dc-dc converter. During normal operation in the first half of the switching cycle, the Duty Cycle Control switch is closed and the Diode Bypass switch is open. Since the output voltage is higher than the voltage at the DCEN pin, no current flows through the diode and the load is powered from the output capacitor. During this stage, the DCEN pin is connected to ground through the Duty Cycle Control switch, generating a positive voltage across the inductor and forcing its current to ramp up.

In the second half of the switching cycle, the Duty Cycle control switch is opened and the Diode Bypass switch is closed. This connects DCEN directly to VDD/DC+ and forces the inductor current to charge the output capacitor. Once the inductor transfers its stored energy to the output capacitor, the Duty Cycle Control switch is closed, the Diode Bypass switch is opened, and the cycle repeats.

The dc-dc converter has a built in voltage reference and oscillator, and will automatically limit or turn off the switching activity in case the peak inductor current rises beyond a safe limit or the output voltage rises above the programmed target value. This allows the dc-dc converter output to be safely overdriven by a secondary power source (when available) in order to preserve battery life. The dc-dc converter's settings can be modified using SFR registers which provide the ability to change the target output voltage, oscillator frequency or source, Diode Bypass switch resistance, peak inductor current, and minimum duty cycle.

Figure 16.1. DC-DC Converter Block Diagram

When the RC oscillator is first enabled, the external oscillator valid detector allows software to determine when oscillation has stabilized. The recommended procedure for starting the RC oscillator is as follows:

- 1. Configure XTAL2 for analog I/O and disable the digital output drivers.

- 2. Configure and enable the external oscillator.

- 3. Poll for XTLVLD  $\Rightarrow$  1.

- 4. Switch the system clock to the external oscillator.

#### **19.3.3. External Capacitor Mode**

If a capacitor is used as the external oscillator, the circuit should be configured as shown in Figure 19.1, Option 3. The capacitor should be added to XTAL2, and XTAL2 should be configured for analog I/O with the digital output drivers disabled. XTAL1 is not affected in RC mode.

The capacitor should be no greater than 100 pF; however, for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. The oscillation frequency and the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register can be determined by the following equation:

$$f = \frac{\mathrm{KF}}{\mathrm{C} \times \mathrm{V}_{\mathrm{DD}}}$$

where

f = frequency of clock in MHzR = pull-up resistor value in  $k\Omega$ V<sub>DD</sub> = power supply voltage in VoltsC = capacitor value on the XTAL2 pin in pF

Below is an example of selecting the capacitor and finding the frequency of oscillation Assume  $V_{DD} = 3.0 \text{ V}$  and f = 150 kHz:

$$f = \frac{\mathrm{KF}}{\mathrm{C} \times \mathrm{V}_{\mathrm{DD}}}$$

$0.150 \text{ MHz} = \frac{\text{KF}}{\text{C} \times 3.0}$

Since a frequency of roughly 150 kHz is desired, select the K Factor from Table 19.2 as KF = 22:

0.150 MHz =

$$\frac{22}{C \times 3.0 V}$$

$$C = \frac{22}{0.150 \text{ MHz} \times 3.0 \text{ V}}$$

C = 48.8 pF

Therefore, the XFCN value to use in this example is 011 and C is approximately 50 pF. The recommended startup procedure for C mode is the same as RC mode.

### 20.1. SmaRTClock Interface

The SmaRTClock Interface consists of three registers: RTC0KEY, RTC0ADR, and RTC0DAT. These interface registers are located on the CIP-51's SFR map and provide access to the SmaRTClock internal registers listed in Table 20.1. The SmaRTClock internal registers can only be accessed indirectly through the SmaRTClock Interface.

| SmaRTClock<br>Address | SmaRTClock<br>Register | Register Name                                   | Description                                                                                                                                   |

|-----------------------|------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00–0x03             | CAPTUREn               | SmaRTClock Capture<br>Registers                 | Four Registers used for setting the 32-bit<br>SmaRTClock timer or reading its current value.                                                  |

| 0x04                  | RTC0CN                 | SmaRTClock Control<br>Register                  | Controls the operation of the SmaRTClock State Machine.                                                                                       |

| 0x05                  | RTC0XCN                | SmaRTClock Oscillator<br>Control Register       | Controls the operation of the SmaRTClock<br>Oscillator.<br>Note: Some bits in this register are only available on<br>'F912 and 'F902 devices. |

| 0x06                  | RTC0XCF                | SmaRTClock Oscillator<br>Configuration Register | Controls the value of the progammable oscillator load capacitance and enables/disables AutoStep.                                              |

| 0x07                  | RTC0PIN                | SmaRTClock Pin<br>Configuration Register        | Forces XTAL3 and XTAL4 to be internally<br>shorted.<br>Note: This register also contains other reserved bits<br>which should not be modified. |

| 0x08–0x0B             | ALARMn                 | SmaRTClock Alarm<br>Registers                   | Four registers used for setting or reading the 32-bit SmaRTClock alarm value.                                                                 |

Table 20.1. SmaRTClock Internal Registers

### 20.1.1. SmaRTClock Lock and Key Functions

The SmaRTClock Interface is protected with a lock and key function. The SmaRTClock Lock and Key Register (RTC0KEY) must be written with the correct key codes, in sequence, before writes and reads to RTC0ADR and RTC0DAT may be performed. The key codes are: 0xA5, 0xF1. There are no timing restrictions, but the key codes must be written in order. If the key codes are written out of order, the wrong codes are written, or an indirect register read or write is attempted while the interface is locked, the SmaRTClock interface will be disabled, and the RTC0ADR and RTC0DAT registers will become inaccessible until the next system reset. Once the SmaRTClock interface is unlocked, software may perform any number of accesses to the SmaRTClock registers until the interface is re-locked or the device is reset. Any write to RTC0KEY while the SmaRTClock interface is unlocked will re-lock the interface.

Reading the RTC0KEY register at any time will provide the SmaRTClock Interface status and will not interfere with the sequence that is being written. The RTC0KEY register description in SFR Definition 20.1 lists the definition of each status code.

#### 20.2.4. Programmable Load Capacitance

The programmable load capacitance has 16 values to support crystal oscillators with a wide range of recommended load capacitance. If Automatic Load Capacitance Stepping is enabled, the crystal load capacitors start at the smallest setting to allow a fast startup time, then slowly increase the capacitance until the final programmed value is reached. The final programmed loading capacitor value is specified using the LOADCAP bits in the RTC0XCF register. The LOADCAP setting specifies the amount of on-chip load capacitance and does not include any stray PCB capacitance. Once the final programmed loading capacitor value is reached, the LOADRDY flag will be set by hardware to logic 1.

When using the SmaRTClock oscillator in Self-Oscillate mode, the programmable load capacitance can be used to fine tune the oscillation frequency. In most cases, increasing the load capacitor value will result in a decrease in oscillation frequency. Table 20.2 shows the crystal load capacitance for various settings of LOADCAP.

| LOADCAP | Crystal Load Capacitance | Equivalent Capacitance seen on<br>XTAL3 and XTAL4 |

|---------|--------------------------|---------------------------------------------------|

| 0000    | 4.0 pF                   | 8.0 pF                                            |

| 0001    | 4.5 pF                   | 9.0 pF                                            |

| 0010    | 5.0 pF                   | 10.0 pF                                           |

| 0011    | 5.5 pF                   | 11.0 pF                                           |

| 0100    | 6.0 pF                   | 12.0 pF                                           |

| 0101    | 6.5 pF                   | 13.0 pF                                           |

| 0110    | 7.0 pF                   | 14.0 pF                                           |

| 0111    | 7.5 pF                   | 15.0 pF                                           |

| 1000    | 8.0 pF                   | 16.0 pF                                           |

| 1001    | 8.5 pF                   | 17.0 pF                                           |

| 1010    | 9.0 pF                   | 18.0 pF                                           |

| 1011    | 9.5 pF                   | 19.0 pF                                           |

| 1100    | 10.5 pF                  | 21.0 pF                                           |

| 1101    | 11.5 pF                  | 23.0 pF                                           |

| 1110    | 12.5 pF                  | 25.0 pF                                           |

| 1111    | 13.5 pF                  | 27.0 pF                                           |

#### Table 20.2. SmaRTClock Load Capacitance Settings

| Mode           | Setting                  | Power<br>Consumption |

|----------------|--------------------------|----------------------|

| Crystal        | Bias Double Off, AGC On  | Lowest<br>600 nA     |

|                | Bias Double Off, AGC Off | Low<br>800 nA        |

|                | Bias Double On, AGC On   | High                 |

|                | Bias Double On, AGC Off  | Highest              |

| Self-Oscillate | Bias Double Off          | Low                  |

|                | Bias Double On           | High                 |

# Table 20.3. SmaRTClock Bias Settings

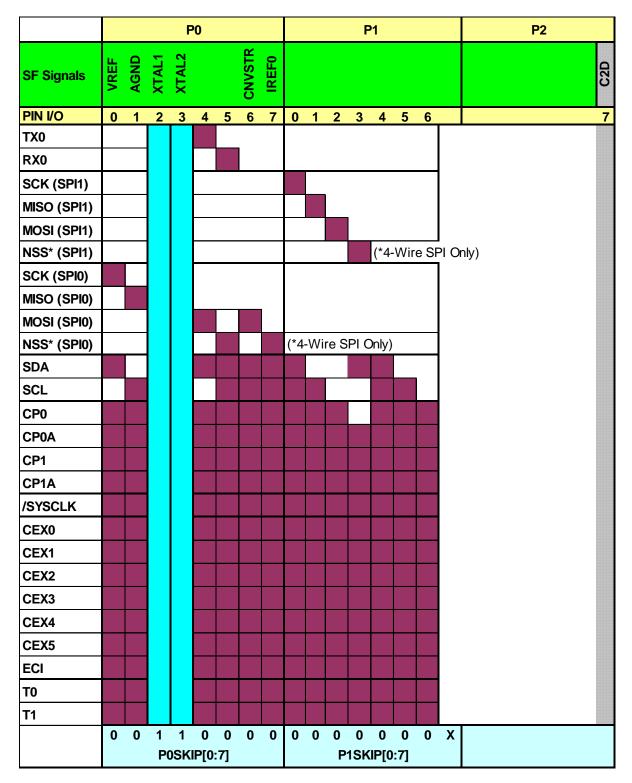

Figure 21.4. Crossbar Priority Decoder with Crystal Pins Skipped

# SFR Definition 21.2. XBR1: Port I/O Crossbar Register 1

| Bit   | 7   | 6     | 5   | 4   | 3    | 2   | 1          | 0   |

|-------|-----|-------|-----|-----|------|-----|------------|-----|

| Name  |     | SPI1E | T1E | T0E | ECIE | F   | PCA0ME[2:0 | ]   |

| Туре  | R/W | R/W   | R/W | R/W | R/W  | R/W | R/W        | R/W |

| Reset | 0   | 0     | 0   | 0   | 0    | 0   | 0          | 0   |

#### SFR Page = 0x0; SFR Address = 0xE2

| Bit     | Name          | Function                                                                                      |

|---------|---------------|-----------------------------------------------------------------------------------------------|

| 7       | Unused        | Unused.                                                                                       |

|         |               | Read = 0b; Write = Don't Care.                                                                |

| 6       | SPI1E         | SPI1 I/O Enable.                                                                              |

|         |               | 0: SPI0 I/O unavailable at Port pin.<br>1: SCK (for SPI1) routed to P1.0.                     |

|         |               | MISO (for SPI1) routed to P1.1.                                                               |

|         |               | MOSI (for SPI1) routed to P1.2.                                                               |

|         |               | NSS (for SPI1) routed to P1.3 only if SPI1 is configured to 4-wire mode.                      |

| 5       | T1E           | Timer1 Input Enable.                                                                          |

|         |               | 0: T1 input unavailable at Port pin.                                                          |

|         |               | 1: T1 input routed to Port pin.                                                               |

| 4       | T0E           | Timer0 Input Enable.                                                                          |

|         |               | 0: T0 input unavailable at Port pin.                                                          |

|         |               | 1: T0 input routed to Port pin.                                                               |

| 3       | ECIE          | PCA0 External Counter Input (ECI) Enable.                                                     |

|         |               | 0: PCA0 external counter input unavailable at Port pin.                                       |

|         |               | 1: PCA0 external counter input routed to Port pin.                                            |

| 2:0     | PCA0ME        | PCA0 Module I/O Enable.                                                                       |

|         |               | 000: All PCA0 I/O unavailable at Port pin.                                                    |

|         |               | 001: CEX0 routed to Port pin.                                                                 |

|         |               | 010: CEX0, CEX1 routed to Port pins.                                                          |

|         |               | 011: CEX0, CEX1, CEX2 routed to Port pins.<br>100: CEX0, CEX1, CEX2 CEX3 routed to Port pins. |

|         |               | 101: CEX0, CEX1, CEX2, CEX3, CEX4 routed to Port pins.                                        |

|         |               | 110: CEX0, CEX1, CEX2, CEX3, CEX4, CEX5 routed to Port pins.                                  |

|         |               | 111: Reserved.                                                                                |

| Note: S | SPI1 can be a | ssigned either 3 or 4 Port I/O pins.                                                          |

# SFR Definition 21.8. P0: Port0

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|---|---|---|---|---|---|---|

| Name  | P0[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W     |   |   |   |   |   |   |   |

| Reset | 1       | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Page = All Pages; SFR Address = 0x80; Bit-Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|

| 7:0 | P0[7:0] | <b>Port 0 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | LOW. |

# SFR Definition 21.9. P0SKIP: Port0 Skip

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | P0SKIP[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page= 0x0; SFR Address = 0xD4

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                           |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0SKIP[7:0] | Port 0 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                  |

|     |             | <ul> <li>These bits select Port 0 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li> <li>0: Corresponding P0.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P0.n pin is skipped by the Crossbar.</li> </ul> |

# 25.3. Timer 3

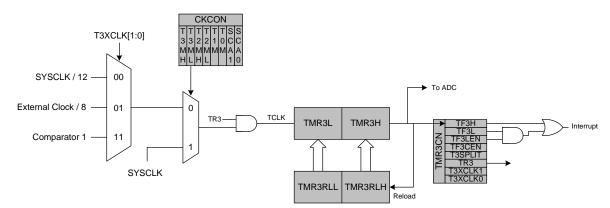

Timer 3 is a 16-bit timer formed by two 8-bit SFRs: TMR3L (low byte) and TMR3H (high byte). Timer 3 may operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T3SPLIT bit (TMR2CN.3) defines the Timer 3 operation mode. Timer 3 can also be used in Capture Mode to measure the external oscillator source or the Comparator 1 period with respect to another oscillator. The ability to measure the Comparator 1 period with respect to the system clock is makes using Touch Sense Switches very easy.

Timer 3 may be clocked by the system clock, the system clock divided by 12, external oscillator source divided by 8, or Comparator 1 output. The external oscillator source divided by 8 and Comparator 1 output is synchronized with the system clock.

#### 25.3.1. 16-bit Timer with Auto-Reload

When T3SPLIT (TMR3CN.3) is zero, Timer 3 operates as a 16-bit timer with auto-reload. Timer 3 can be clocked by SYSCLK, SYSCLK divided by 12, external oscillator clock source divided by 8, or Comparator 1 output. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 3 reload registers (TMR3RLH and TMR3RLL) is loaded into the Timer 3 register as shown in Figure 25.7, and the Timer 3 High Byte Overflow Flag (TMR3CN.7) is set. If Timer 3 interrupts are enabled (if EIE1.7 is set), an interrupt will be generated on each Timer 3 overflow. Additionally, if Timer 3 interrupts are enabled and the TF3LEN bit is set (TMR3CN.5), an interrupt will be generated each time the lower 8 bits (TMR3L) overflow from 0xFF to 0x00.

Figure 25.7. Timer 3 16-Bit Mode Block Diagram

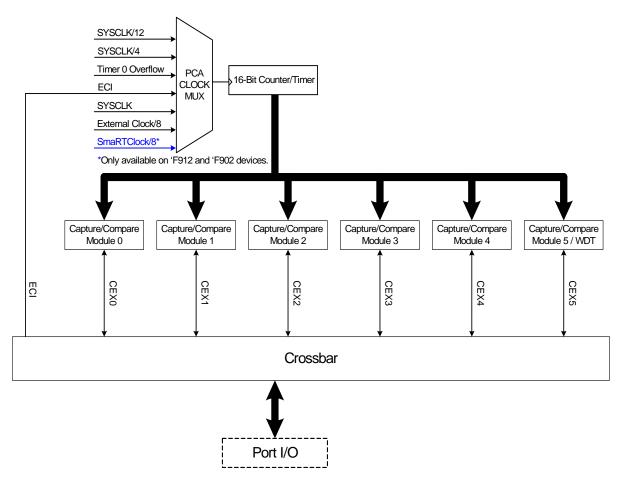

# 26. Programmable Counter Array

The Programmable Counter Array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and six 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled. The counter/timer is driven by a programmable timebase that can select between seven sources: system clock, system clock divided by four, system clock divided by twelve, the external oscillator clock source divided by 8, SmaRTClock divided by 8 ('F912 and 'F902 devices only), Timer 0 overflows, or an external clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of six modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8 to 11-Bit PWM, or 16-Bit PWM (each mode is described in Section "26.3. Capture/Compare Modules" on page 296). The external oscillator clock option is ideal for real-time clock (RTC) functionality, allowing the PCA to be clocked by a precision external oscillator while the internal oscillator drives the system clock. The PCA is configured and controlled through the system controller's Special Function Registers. The PCA block diagram is shown in Figure 26.1.

**Important Note:** The PCA Module 5 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. Access to certain PCA registers is restricted while WDT mode is enabled. See Section 26.4 for details.

Figure 26.1. PCA Block Diagram

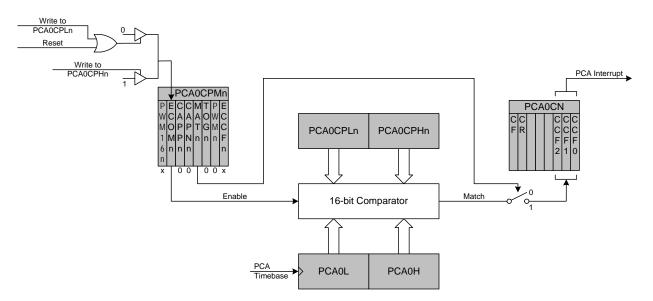

#### 26.3.2. Software Timer (Compare) Mode

In Software Timer mode, the PCA counter/timer value is compared to the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the ECOMn and MATn bits in the PCA0CPMn register enables Software Timer mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Figure 26.5. PCA Software Timer Mode Diagram