Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 16                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 768 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                    |

| Data Converters            | A/D 15x10/12b                                                  |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-WFQFN Exposed Pad                                           |

| Supplier Device Package    | 24-QFN (4x4)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f902-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 6.2. IREF0 Specifications                            | 87         |

|----|------------------------------------------------------|------------|

| 7. | •                                                    |            |

|    | 7.1. Comparator Inputs                               |            |

|    | 7.2. Comparator Outputs                              |            |

|    | 7.3. Comparator Response Time                        |            |

|    | 7.4. Comparator Hysteresis                           |            |

|    | 7.5. Comparator Register Descriptions                | . 00<br>91 |

|    | 7.6. Comparator0 and Comparator1 Analog Multiplexers |            |

| 8  | CIP-51 Microcontroller                               |            |

| 0. | 8.1. Performance                                     |            |

|    | 8.2. Programming and Debugging Support               |            |

|    | 8.3. Instruction Set                                 |            |

|    | 8.3.1. Instruction and CPU Timing                    | 99         |

|    | 8.4. CIP-51 Register Descriptions                    |            |

| 9  | Memory Organization                                  |            |

| 0. | 9.1. Program Memory                                  |            |

|    | 9.1.1. MOVX Instruction and Program Memory           |            |

|    | 9.2. Data Memory                                     |            |

|    | 9.2.1. Internal RAM                                  |            |

|    | 9.2.2. External RAM                                  |            |

| 10 | .On-Chip XRAM                                        |            |

|    | 10.1.Accessing XRAM                                  | 111        |

|    | 10.1.1.16-Bit MOVX Example                           |            |

|    | 10.1.2.8-Bit MOVX Example                            |            |

|    | 10.2.Special Function Registers                      |            |

| 11 | Special Function Registers                           |            |

|    | 11.1.SFR Paging                                      |            |

| 12 | Interrupt Handler                                    |            |

|    | 12.1.Enabling Interrupt Sources                      |            |

|    | 12.2.MCU Interrupt Sources and Vectors               |            |

|    | 12.3.Interrupt Priorities                            |            |

|    | 12.4.Interrupt Latency                               | 121        |

|    | 12.5.Interrupt Register Descriptions                 | 123        |

|    | 12.6.External Interrupts INTO and INT1               | 130        |

| 13 | Flash Memory                                         |            |

|    | 13.1.Programming The Flash Memory                    | 132        |

|    | 13.1.1.Flash Lock and Key Functions                  | 132        |

|    | 13.1.2.Flash Erase Procedure                         | 133        |

|    | 13.1.3.Flash Write Procedure                         | 133        |

|    | 13.2.Non-volatile Data Storage                       | 133        |

|    | 13.3.Security Options                                |            |

|    | 13.4.Determining the Device Part Number at Run Time  |            |

|    | 13.5.Flash Write and Erase Guidelines                |            |

|    | 13.5.1.VDD Maintenance and the VDD Monitor           |            |

|    | 13.5.2.PSWE Maintenance                              | 138        |

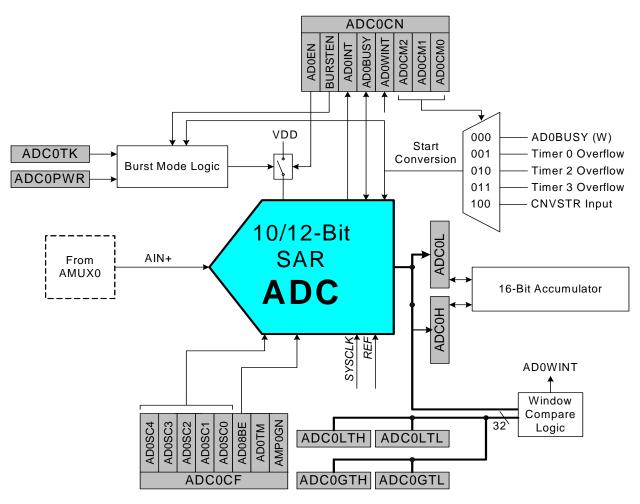

# 1.5. SAR ADC with 16-bit Auto-Averaging Accumulator and Autonomous Low Power Burst Mode

C8051F91x-C8051F90x devices have a 300 ksps, 10-bit or 75 ksps 12-bit successive-approximationregister (SAR) ADC with integrated track-and-hold and programmable window detector. ADC0 also has an autonomous low power Burst Mode which can automatically enable ADC0, capture and accumulate samples, then place ADC0 in a low power shutdown mode without CPU intervention. It also has a 16-bit accumulator that can automatically average the ADC results, providing an effective 11, 12, or 13 bit ADC result without any additional CPU intervention.

The ADC can sample the voltage at any of the GPIO pins (with the exception of P2.7) and has an on-chip attenuator that allows it to measure voltages up to twice the voltage reference. Additional ADC inputs include an on-chip temperature sensor, the VDD/DC+ supply voltage, the VBAT supply voltage, and the internal digital supply voltage.

Figure 1.7. ADC0 Functional Block Diagram

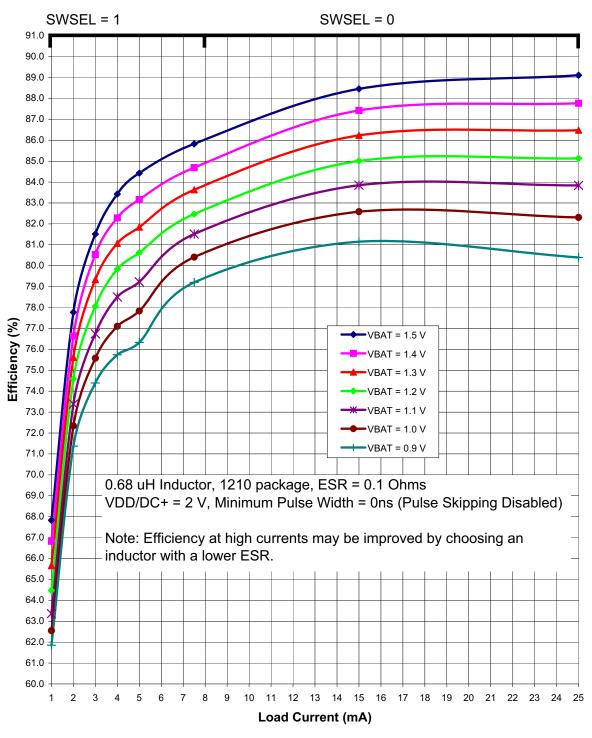

Figure 4.3. Typical DC-DC Converter Efficiency (High Current, VDD/DC+ = 2 V)

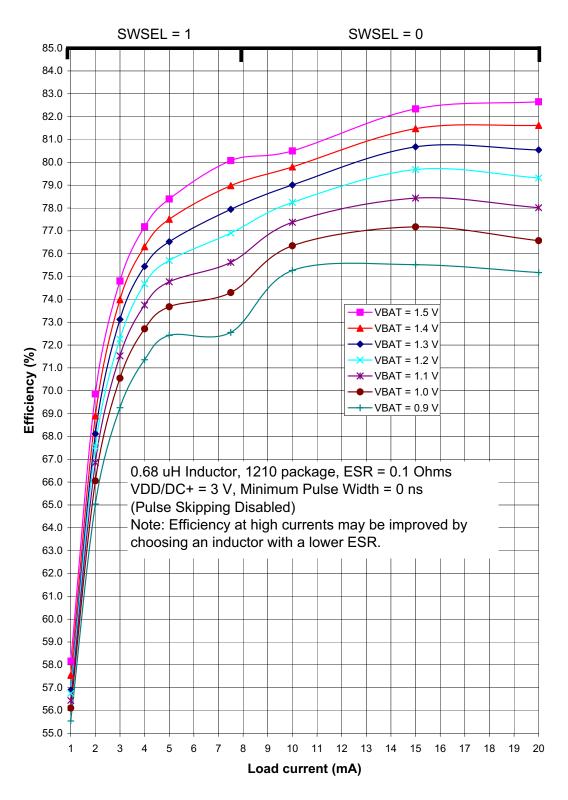

Figure 4.4. Typical DC-DC Converter Efficiency (High Current, VDD/DC+ = 3 V)

## SFR Definition 5.6. ADC0H: ADC0 Data Word High Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | ADC0[15:8] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0; SFR Address = 0xBE

| Bit   | Name                                                                                                                                                                           | Description                  | Read                                                                                                               | Write                                                                                       |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0   | ADC0[15:8]                                                                                                                                                                     | ADC0 Data Word High<br>Byte. | Most Significant Byte of the<br>16-bit ADC0 Accumulator<br>formatted according to the<br>settings in AD0SJST[2:0]. | Set the most significant<br>byte of the 16-bit ADC0<br>Accumulator to the value<br>written. |  |  |  |  |  |

| Note: | <b>bite:</b> If Accumulator shifting is enabled, the most significant bits of the value read will be zeros. This register should not be written when the SYNC bit is set to 1. |                              |                                                                                                                    |                                                                                             |  |  |  |  |  |

### SFR Definition 5.7. ADC0L: ADC0 Data Word Low Byte

| Bit   | 7   | 6         | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|-----------|---|---|---|---|---|---|

| Name  |     | ADC0[7:0] |   |   |   |   |   |   |

| Туре  | R/W |           |   |   |   |   |   |   |

| Reset | 0   | 0         | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0; SFR Address = 0xBD;

| Bit   | Name                                                                                                                                                                                                                             | Description                 | Read                                                                                                                | Write                                                                                        |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|

| 7:0   | ADC0[7:0]                                                                                                                                                                                                                        | ADC0 Data Word Low<br>Byte. | Least Significant Byte of the<br>16-bit ADC0 Accumulator<br>formatted according to the<br>settings in AD0SJST[2:0]. | Set the least significant<br>byte of the 16-bit ADC0<br>Accumulator to the value<br>written. |  |  |  |  |

| Note: | <b>Note:</b> If Accumulator shifting is enabled, the most significant bits of the value read will be the least significant bits of the accumulator high byte. This register should not be written when the SYNC bit is set to 1. |                             |                                                                                                                     |                                                                                              |  |  |  |  |

| Mnemonic          | Description                              | Bytes | Clock<br>Cycles |

|-------------------|------------------------------------------|-------|-----------------|

|                   | Arithmetic Operations                    |       | 1               |

| ADD A, Rn         | Add register to A                        | 1     | 1               |

| ADD A, direct     | Add direct byte to A                     | 2     | 2               |

| ADD A, @Ri        | Add indirect RAM to A                    | 1     | 2               |

| ADD A, #data      | Add immediate to A                       | 2     | 2               |

| ADDC A, Rn        | Add register to A with carry             | 1     | 1               |

| ADDC A, direct    | Add direct byte to A with carry          | 2     | 2               |

| ADDC A, @Ri       | Add indirect RAM to A with carry         | 1     | 2               |

| ADDC A, #data     | Add immediate to A with carry            | 2     | 2               |

| SUBB A, Rn        | Subtract register from A with borrow     | 1     | 1               |

| SUBB A, direct    | Subtract direct byte from A with borrow  | 2     | 2               |

| SUBB A, @Ri       | Subtract indirect RAM from A with borrow | 1     | 2               |

| SUBB A, #data     | Subtract immediate from A with borrow    | 2     | 2               |

| INC A             | Increment A                              | 1     | 1               |

| INC Rn            | Increment register                       | 1     | 1               |

| INC direct        | Increment direct byte                    | 2     | 2               |

| INC @Ri           | Increment indirect RAM                   | 1     | 2               |

| DEC A             | Decrement A                              | 1     | 1               |

| DEC Rn            | Decrement register                       | 1     | 1               |

| DEC direct        | Decrement direct byte                    | 2     | 2               |

| DEC @Ri           | Decrement indirect RAM                   | 1     | 2               |

| INC DPTR          | Increment Data Pointer                   | 1     | 1               |

| MUL AB            | Multiply A and B                         | 1     | 4               |

| DIV AB            | Divide A by B                            | 1     | 8               |

| DA A              | Decimal adjust A                         | 1     | 1               |

|                   | Logical Operations                       |       |                 |

| ANL A, Rn         | AND Register to A                        | 1     | 1               |

| ANL A, direct     | AND direct byte to A                     | 2     | 2               |

| ANL A, @Ri        | AND indirect RAM to A                    | 1     | 2               |

| ANL A, #data      | AND immediate to A                       | 2     | 2               |

| ANL direct, A     | AND A to direct byte                     | 2     | 2               |

| ANL direct, #data | AND immediate to direct byte             | 3     | 3               |

| ORL A, Rn         | OR Register to A                         | 1     | 1               |

| ORL A, direct     | OR direct byte to A                      | 2     | 2               |

| ORL A, @Ri        | OR indirect RAM to A                     | 1     | 2               |

| ORL A, #data      | OR immediate to A                        | 2     | 2               |

| ORL direct, A     | OR A to direct byte                      | 2     | 2               |

| ORL direct, #data | OR immediate to direct byte              | 3     | 3               |

| XRL A, Rn         | Exclusive-OR Register to A               | 1     | 1               |

| XRL A, direct     | Exclusive-OR direct byte to A            | 2     | 2               |

| XRL A, @Ri        | Exclusive-OR indirect RAM to A           | 1     | 2               |

| XRL A, #data      | Exclusive-OR immediate to A              | 2     | 2               |

| XRL direct, A     | Exclusive-OR A to direct byte            | 2     | 2               |

| XRL direct, #data | Exclusive-OR immediate to direct byte    | 3     | 3               |

### Table 8.1. CIP-51 Instruction Set Summary

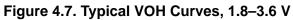

### 9.1. Program Memory

The CIP-51 core has a 64 kB program memory space. The C8051F91x-C8051F90x devices implement 16 kB (C8051F912/1) or 8 kB (C8051F902/1) of this program memory space as in-system, reprogrammable Flash memory, organized in a contiguous block from addresses 0x0000 to 0x3BFF (C8051F912/1) or 0x1FFF (C8051F902/1). The last byte of this contiguous block of addresses serves as the security lock byte for the device. Any addresses above the lock byte are reserved.

#### 9.1.1. MOVX Instruction and Program Memory

The MOVX instruction in an 8051 device is typically used to access external data memory. On the C8051F91x-C8051F90x devices, the MOVX instruction is normally used to read and write on-chip XRAM, but can be re-configured to write and erase on-chip Flash memory space. MOVC instructions are always used to read Flash memory, while MOVX write instructions are used to erase and write Flash. This Flash access feature provides a mechanism for the C8051F91x-C8051F90x to update program code and use the program memory space for non-volatile data storage. Refer to Section "13. Flash Memory" on page 132 for further details.

#### 9.2. Data Memory

The C8051F91x-C8051F90x device family include 768 bytes of RAM data memory. 256 bytes of this memory is mapped into the internal RAM space of the 8051. The remainder of this memory is on-chip "external" memory. The data memory map is shown in Figure 9.1 for reference.

#### 9.2.1. Internal RAM

There are 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or as 128 bit locations accessible with the direct addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFR) but is physically separate from the SFR space. The addressing mode used by an instruction when accessing locations above 0x7F determines

## 13. Flash Memory

On-chip, re-programmable Flash memory is included for program code and non-volatile data storage. The Flash memory can be programmed in-system through the C2 interface or by software using the MOVX write instruction. Once cleared to logic 0, a Flash bit must be erased to set it back to logic 1. Flash bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution; data polling to determine the end of the write/erase operations is not required. Code execution is stalled during Flash write/erase operations. Refer to Table 4.6 for complete Flash memory electrical characteristics.

### 13.1. Programming The Flash Memory

The simplest means of programming the Flash memory is through the C2 interface using programming tools provided by Silicon Laboratories or a third party vendor. This is the only means for programming a non-initialized device. For details on the C2 commands to program Flash memory, see Section "27. C2 Interface" on page 312.

The Flash memory can be programmed by software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before programming Flash memory using MOVX, Flash programming operations must be enabled by: (1) setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 (this directs the MOVX writes to target Flash memory); and (2) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY). The PSWE bit remains set until cleared by software. For detailed guidelines on programming Flash from firmware, please see Section "13.5. Flash Write and Erase Guidelines" on page 137.

To ensure the integrity of the Flash contents, the on-chip VDD Monitor must be enabled and enabled as a reset source in any system that includes code that writes and/or erases Flash memory from software. Furthermore, there should be no delay between enabling the  $V_{DD}$  Monitor and enabling the  $V_{DD}$  Monitor as a reset source. Any attempt to write or erase Flash memory while the  $V_{DD}$  Monitor is disabled, or not enabled as a reset source, will cause a Flash Error device reset.

#### 13.1.1. Flash Lock and Key Functions

Flash writes and erases by user software are protected with a lock and key function. The Flash Lock and Key Register (FLKEY) must be written with the correct key codes, in sequence, before Flash operations may be performed. The key codes are: 0xA5, 0xF1. The timing does not matter, but the codes must be written in order. If the key codes are written out of order, or the wrong codes are written, Flash writes and erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 13.2.

| Action                                                                        | C2 Debug      | User Firmware executing from: |               |  |

|-------------------------------------------------------------------------------|---------------|-------------------------------|---------------|--|

|                                                                               | Interface     | an unlocked page              | a locked page |  |

| Read, Write or Erase unlocked pages<br>(except page with Lock Byte)           | Permitted     | Permitted                     | Permitted     |  |

| Read, Write or Erase locked pages<br>(except page with Lock Byte)             | Not Permitted | FEDR                          | Permitted     |  |

| Read or Write page containing Lock Byte<br>(if no pages are locked)           | Permitted     | Permitted                     | Permitted     |  |

| Read or Write page containing Lock Byte<br>(if any page is locked)            | Not Permitted | FEDR                          | Permitted     |  |

| Read contents of Lock Byte<br>(if no pages are locked)                        | Permitted     | Permitted                     | Permitted     |  |

| Read contents of Lock Byte<br>(if any page is locked)                         | Not Permitted | FEDR                          | Permitted     |  |

| Erase page containing Lock Byte<br>(if no pages are locked)                   | Permitted     | FEDR                          | FEDR          |  |

| Erase page containing Lock Byte - Unlock all pages<br>(if any page is locked) | Only by C2DE  | FEDR                          | FEDR          |  |

| Lock additional pages<br>(change 1s to 0s in the Lock Byte)                   | Not Permitted | FEDR                          | FEDR          |  |

| Unlock individual pages<br>(change 0s to 1s in the Lock Byte)                 | Not Permitted | FEDR                          | FEDR          |  |

| Read, Write or Erase Reserved Area                                            | Not Permitted | FEDR                          | FEDR          |  |

#### Table 13.1. Flash Security Summary

C2DE—C2 Device Erase (Erases all Flash pages including the page containing the Lock Byte) FEDR—Not permitted; Causes Flash Error Device Reset (FERROR bit in RSTSRC is 1 after reset)

- All prohibited operations that are performed via the C2 interface are ignored (do not cause device reset).

- Locking any Flash page also locks the page containing the Lock Byte.

- Once written to, the Lock Byte cannot be modified except by performing a C2 Device Erase.

- If user code writes to the Lock Byte, the Lock does not take effect until the next device reset.

- The scratchpad is locked when all other Flash pages are locked.

- The scratchpad is erased when a Flash Device Erase command is performed.

## 16.11. Passive Diode Mode (C8051F912/02 only)

Setting the EXTDEN bit in DCOMD enables the Passive Diode Mode. In this mode, the control circuits for the Diode Bypass switch are disabled, which reduces the converter's quiescent operating current. An external Schottky diode may be connected between the DCEN (anode) and VDD/DC+ (cathode) pins. Under light load conditions, an external diode is typically not required. There are two situations in which this mode can prove beneficial. First is with very light load currents, where the efficiency is dominated by the converter's quiescent current. The converter will use an internal p-n junction diode to transfer current from the inductor to the output capacitor; although there is a larger voltage drop (and power loss) across a passive diode, the overall efficiency may be improved due to the reduction in quiescent current. The second situation is when output power is very high. In that case, efficiency can suffer because some reverse current can flow in the Diode Bypass switch before the control circuitry turns the switch off. Putting the device in Passive Diode Mode and optionally connecting an external Schottky diode between the DCEN and VDD/DC+ pins (parallel to the internal diode) may provide higher efficiency in some applications than using the internal Diode Bypass switch.

## SFR Definition 16.2. DC0CF: DC-DC Converter Configuration

| Bit   | 7    | 6    | 5       | 4        | 3      | 2      | 1      | 0      |

|-------|------|------|---------|----------|--------|--------|--------|--------|

| Name  | LPEN | CLKD | IV[1:0] | AD0CKINV | CLKINV | ILIMIT | VDDSLP | CLKSEL |

| Туре  | R/W  | R/W  | R/W     | R/W      | R/W    | R/W    | R/W    | R/W    |

| Reset | 0    | 0    | 0       | 0        | 0      | 0      | 0      | 0      |

SFR Page = 0x0; SFR Address = 0x96

| Bit | Name        | Function                                                                                                                                                                                           |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | LPEN        | Low Power Mode Enable.                                                                                                                                                                             |

|     |             | Enables the dc-dc low power mode which reduces bias currents, reduces peak inductor current, and increases efficiency for low load currents. Only available on 'F912 and 'F902 devices.            |

|     |             | 0: Low Power Mode Disabled.<br>1: Low Power Mode Enabled.                                                                                                                                          |

| 6:5 | CLKDIV[1:0] | DC-DC Clock Divider.                                                                                                                                                                               |

|     |             | Divides the dc-dc converter clock when the system clock is selected as the clock source for dc-dc converter. These bits are ignored when the dc-dc converter is clocked from its local oscillator. |

|     |             | 00: The dc-dc converter clock is system clock divided by 1.                                                                                                                                        |

|     |             | 01: The dc-dc converter clock is system clock divided by 2.                                                                                                                                        |

|     |             | <ol> <li>The dc-dc converter clock is system clock divided by 4.</li> <li>The dc-dc converter clock is system clock divided by 8.</li> </ol>                                                       |

| 4   | AD0CKINV    | ADC0 Clock Inversion (Clock Invert During Sync).                                                                                                                                                   |

| -   | ADUCKINV    | Inverts the ADC0 SAR clock derived from the dc-dc converter clock when the SYNC                                                                                                                    |

|     |             | bit (DC0CN.3) is enabled. This bit is ignored when the SYNC bit is set to zero.                                                                                                                    |

|     |             | 0: ADC0 SAR clock is inverted.                                                                                                                                                                     |

|     |             | 1: ADC0 SAR clock is not inverted.                                                                                                                                                                 |

| 3   | CLKINV      | DC-DC Converter Clock Invert.                                                                                                                                                                      |

|     |             | Inverts the system clock used as the input to the dc-dc clock divider.                                                                                                                             |

|     |             | 0: The dc-dc converter clock is not inverted.                                                                                                                                                      |

|     |             | 1: The dc-dc converter clock is inverted.                                                                                                                                                          |

| 2   | ILIMIT      | Peak Current Limit Threshold.                                                                                                                                                                      |

|     |             | Sets the threshold for the maximum allowed peak inductor current according to Table 16.1.                                                                                                          |

| 1   | VDDSLP      | VDD-DC+ Sleep Mode Connection.                                                                                                                                                                     |

|     |             | Specifies the power source for VDD/DC+ in Sleep Mode when the dc-dc converter is enabled.                                                                                                          |

|     |             | <ul><li>0: VDD-DC+ connected to VBAT in Sleep Mode.</li><li>1: VDD-DC+ is floating in Sleep Mode.</li></ul>                                                                                        |

| 0   | CLKSEL      | DC-DC Converter Clock Source Select.                                                                                                                                                               |

|     |             | Specifies the dc-dc converter clock source.                                                                                                                                                        |

|     |             | 0: The dc-dc converter is clocked from its local oscillator.                                                                                                                                       |

|     |             | 1: The dc-dc converter is clocked from the system clock.                                                                                                                                           |

#### 20.1.5. RTC0ADR Autoincrement Feature

For ease of reading and writing the 32-bit CAPTURE and ALARM values, RTC0ADR automatically increments after each read or write to a CAPTUREn or ALARMn register. This speeds up the process of setting an alarm or reading the current SmaRTClock timer value. Autoincrement is always enabled.

Recommended Instruction Timing for a multi-byte register read with short strobe and auto read enabled:

mov RTCOADR, #0d0h

nop

nop

mov A, RTCODAT

nop

mov A, RTCODAT

nop

nop

mov A, RTCODAT

nop

nop

mov A, RTCODAT

nop

nop

mov A, RTCODAT

Recommended Instruction Timing for a multi-byte register write with short strobe enabled:

mov RTCOADR, #010h

mov RTCODAT, #05h

nop

mov RTCODAT, #06h

nop

mov RTCODAT, #07h

nop

mov RTCODAT, #08h

nop

## SFR Definition 21.19. P2MDOUT: Port2 Output Mode

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|---|---|---|---|---|---|---|

| Name  | P2MDOUT |   |   |   |   |   |   |   |

| Туре  | R/W     |   |   |   |   |   |   |   |

| Reset | 0       | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Page = 0x0; SFR Address = 0xA6

| Bit | Name    | Function                                                                                                |  |  |  |

|-----|---------|---------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | P2MDOUT | Output Configuration Bits for P2.7.                                                                     |  |  |  |

|     |         | These bits control the digital driver.<br>0: P2.7 Output is open-drain.<br>1: P2.7 Output is push-pull. |  |  |  |

| 6:0 | Unused  | <b>Unused.</b><br>Read = 0000000b; Write = Don't Care.                                                  |  |  |  |

## SFR Definition 21.20. P2DRV: Port2 Drive Strength

| Bit   | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------|---|---|---|---|---|---|---|

| Name  | P2DRV |   |   |   |   |   |   |   |

| Туре  | R/W   |   |   |   |   |   |   |   |

| Reset | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0F; SFR Address = 0xA6

| Bit | Name   | Function                                                                                                                                                                   |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | P2DRV  | Drive Strength Configuration Bits for P2.7.                                                                                                                                |

|     |        | Configures digital I/O Port cells to high or low output drive strength.<br>0: P2.7 Output has low output drive strength.<br>1: P2.7 Output has high output drive strength. |

| 6:0 | Unused | Unused.<br>Read = 000000b; Write = Don't Care.                                                                                                                             |

### 24.3. SPI Slave Mode Operation

When SPIn is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPIn logic counts SCK edges. When 8 bits have been shifted through the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPInDAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPInDAT. Writes to SPInDAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will load the shift register with the transmit buffer's contents after the last SCK edge of the next (or current) SPI transfer.

When configured as a slave, SPIn can be configured for 4-wire or 3-wire operation. The default, 4-wire slave mode, is active when NSSnMD1 (SPInCN.3) = 0 and NSSnMD0 (SPInCN.2) = 1. In 4-wire mode, the NSS signal is routed to a port pin and configured as a digital input. SPIn is enabled when NSS is logic 0, and disabled when NSS is logic 1. The bit counter is reset on a falling edge of NSS. Note that the NSS signal must be driven low at least 2 system clocks before the first active edge of SCK for each byte transfer. Figure 24.4 shows a connection diagram between two slave devices in 4-wire slave mode and a master device.

3-wire slave mode is active when NSSnMD1 (SPInCN.3) = 0 and NSSnMD0 (SPInCN.2) = 0. NSS is not used in this mode, and is not mapped to an external port pin through the crossbar. Since there is no way of uniquely addressing the device in 3-wire slave mode, SPIn must be the only slave device present on the bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter that determines when a full byte has been received. The bit counter can only be reset by disabling and re-enabling SPIn with the SPIEN bit. Figure 24.3 shows a connection diagram between a slave device in 3-wire slave mode and a master device.

#### 24.4. SPI Interrupt Sources

When SPIn interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

All of the following bits must be cleared by software.

- 1. The SPI Interrupt Flag, SPIFn (SPInCN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPIn modes.

- 2. The Write Collision Flag, WCOLn (SPInCN.6) is set to logic 1 if a write to SPInDAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPInDAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPIn modes.

- 3. The Mode Fault Flag MODFn (SPInCN.5) is set to logic 1 when SPIn is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTENn and SPIENn bits in SPI0CN are set to logic 0 to disable SPIn and allow another master device to access the bus.

- 4. The Receive Overrun Flag RXOVRNn (SPInCN.4) is set to logic 1 when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

## SFR Definition 25.11. TMR2L: Timer 2 Low Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | TMR2L[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0; SFR Address = 0xCC

| Bit | Name       | Function                                                                                                                                          |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2L[7:0] | Timer 2 Low Byte.                                                                                                                                 |

|     |            | In 16-bit mode, the TMR2L register contains the low byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2L contains the 8-bit low byte timer value. |

## SFR Definition 25.12. TMR2H Timer 2 High Byte

| Bit   | 7          | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|-----------------|---|---|---|---|---|---|

| Name  | TMR2H[7:0] |                 |   |   |   |   |   |   |

| Туре  | R/W        |                 |   |   |   |   |   |   |

| Reset | 0          | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |

SFR Page = 0x0; SFR Address = 0xCD

| Bit | Name       | Function                                                                                                                                            |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2H[7:0] | Timer 2 Low Byte.                                                                                                                                   |

|     |            | In 16-bit mode, the TMR2H register contains the high byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2H contains the 8-bit high byte timer value. |

## SFR Definition 25.13. TMR3CN: Timer 3 Control

| Bit   | 7    | 6    | 5      | 4      | 3       | 2   | 1     | 0       |

|-------|------|------|--------|--------|---------|-----|-------|---------|

| Name  | TF3H | TF3L | TF3LEN | TF3CEN | T3SPLIT | TR3 | T3XCI | _K[1:0] |

| Туре  | R/W  | R/W  | R/W    | R/W    | R/W     | R/W | R/    | W       |

| Reset | 0    | 0    | 0      | 0      | 0       | 0   | 0     | 0       |

#### SFR Page = 0x0; SFR Address = 0x91

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF3H        | <b>Timer 3 High Byte Overflow Flag.</b><br>Set by hardware when the Timer 3 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 3 overflows from 0xFFFF to 0x0000. When the Timer 3 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 3 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                                                       |

| 6   | TF3L        | <b>Timer 3 Low Byte Overflow Flag.</b><br>Set by hardware when the Timer 3 low byte overflows from 0xFF to 0x00. TF3L will be set when the low byte overflows regardless of the Timer 3 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5   | TF3LEN      | <b>Timer 3 Low Byte Interrupt Enable.</b><br>When set to 1, this bit enables Timer 3 Low Byte interrupts. If Timer 3 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 3 overflows.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4   | TF3CEN      | Timer 3 Comparator 1/External Oscillator Capture Enable.<br>When set to 1, this bit enables Timer 3 Capture Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3   | T3SPLIT     | Timer 3 Split Mode Enable.When this bit is set, Timer 3 operates as two 8-bit timers with auto-reload.0: Timer 3 operates in 16-bit auto-reload mode.1: Timer 3 operates as two 8-bit auto-reload timers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2   | TR3         | <b>Timer 3 Run Control.</b><br>Timer 3 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables<br>TMR3H only; TMR3L is always enabled in split mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1:0 | T3XCLK[1:0] | Timer 3 External Clock Select.<br>This bit selects the "external" and "capture trigger" clock sources for Timer 3. If<br>Timer 3 is in 8-bit mode, this bit selects the "external" clock source for both timer<br>bytes. Timer 3 Clock Select bits (T3MH and T3ML in register CKCON) may still be<br>used to select between the "external" clock and the system clock for either timer.<br>Note: External clock sources are synchronized with the system clock.<br>00: External Clock is SYSCLK /12. Capture trigger is Comparator 1.<br>01: External Clock is SYSCLK/12. Capture trigger is External Oscillator/8.<br>11: External Clock is Comparator 1. Capture trigger is External Oscillator/8. |

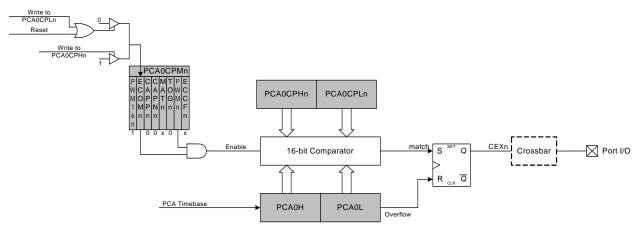

#### 26.3.6. 16-Bit Pulse Width Modulator Mode

A PCA module may also be operated in 16-Bit PWM mode. 16-bit PWM mode is independent of the other (8/9/10/11-bit) PWM modes. In this mode, the 16-bit capture/compare module defines the number of PCA clocks for the low time of the PWM signal. When the PCA counter matches the module contents, the output on CEXn is asserted high; when the 16-bit counter overflows, CEXn is asserted low. To output a varying duty cycle, new value writes should be synchronized with PCA CCFn match interrupts. 16-Bit PWM Mode is enabled by setting the ECOMn, PWMn, and PWM16n bits in the PCA0CPMn register. For a varying duty cycle, match interrupts should be enabled (ECCFn = 1 AND MATn = 1) to help synchronize the capture/compare register writes. If the MATn bit is set to 1, the CCFn flag for the module will be set each time a 16-bit comparator match (rising edge) occurs. The CF flag in PCA0CN can be used to detect the overflow (falling edge). The duty cycle for 16-Bit PWM Mode is given by Equation 26.4.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

$$Duty Cycle = \frac{(65536 - PCA0CPn)}{65536}$$

Equation 26.4. 16-Bit PWM Duty Cycle

Using Equation 26.4, the largest duty cycle is 100% (PCA0CPn = 0), and the smallest duty cycle is 0.0015% (PCA0CPn = 0xFFFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 26.10. PCA 16-Bit PWM Mode

The 8-bit offset held in PCA0CPH5 is compared to the upper byte of the 16-bit PCA counter. This offset value is the number of PCA0L overflows before a reset. Up to 256 PCA clocks may pass before the first PCA0L overflow occurs, depending on the value of the PCA0L when the update is performed. The total offset is then given (in PCA clocks) by Equation 26.5, where PCA0L is the value of the PCA0L register at the time of the update.

#### $Offset = (256 \times PCA0CPL5) + (256 - PCA0L)$

#### Equation 26.5. Watchdog Timer Offset in PCA Clocks

The WDT reset is generated when PCA0L overflows while there is a match between PCA0CPH5 and PCA0H. Software may force a WDT reset by writing a 1 to the CCF5 flag (PCA0CN.5) while the WDT is enabled.

#### 26.4.2. Watchdog Timer Usage

To configure the WDT, perform the following tasks:

- Disable the WDT by writing a 0 to the WDTE bit.

- Select the desired PCA clock source (with the CPS2–CPS0 bits).

- Load PCA0CPL5 with the desired WDT update offset value.

- Configure the PCA Idle mode (set CIDL if the WDT should be suspended while the CPU is in Idle mode).

- Enable the WDT by setting the WDTE bit to 1.

- Reset the WDT timer by writing to PCA0CPH5.

The PCA clock source and Idle mode select cannot be changed while the WDT is enabled. The watchdog timer is enabled by setting the WDTE or WDLCK bits in the PCA0MD register. When WDLCK is set, the WDT cannot be disabled until the next system reset. If WDLCK is not set, the WDT is disabled by clearing the WDTE bit.

The WDT is enabled following any reset. The PCA0 counter clock defaults to the system clock divided by 12, PCA0L defaults to 0x00, and PCA0CPL5 defaults to 0x00. Using Equation 26.5, this results in a WDT timeout interval of 256 PCA clock cycles, or 3072 system clock cycles. Table 26.3 lists some example timeout intervals for typical system clocks.

| System Clock (Hz)        | PCA0CPL5              | Timeout Interval (ms)          |

|--------------------------|-----------------------|--------------------------------|

| 24,500,000               | 255                   | 32.1                           |

| 24,500,000               | 128                   | 16.2                           |

| 24,500,000               | 32                    | 4.1                            |

| 3,062,500*               | 255                   | 257                            |

| 3,062,500*               | 128                   | 129.5                          |

| 3,062,500*               | 32                    | 33.1                           |

| 32,000                   | 255                   | 24576                          |

| 32,000                   | 128                   | 12384                          |

| 32,000                   | 32                    | 3168                           |

| Note: Internal SYSCLK re | eset frequency = Inte | ernal Oscillator divided by 8. |

#### Table 26.3. Watchdog Timer Timeout Intervals

## SFR Definition 26.3. PCA0PWM: PCA PWM Configuration

| Bit   | 7     | 6    | 5    | 4 | 3 | 2 | 1    | 0      |

|-------|-------|------|------|---|---|---|------|--------|

| Name  | ARSEL | ECOV | COVF |   |   |   | CLSE | L[1:0] |

| Туре  | R/W   | R/W  | R/W  | R | R | R | R/W  |        |

| Reset | 0     | 0    | 0    | 0 | 0 | 0 | 0    | 0      |

#### SFR Page = 0x0; SFR Address = 0xDF

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ARSEL      | Auto-Reload Register Select.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |            | This bit selects whether to read and write the normal PCA capture/compare registers (PCA0CPn), or the Auto-Reload registers at the same SFR addresses. This function is used to define the reload value for 9, 10, and 11-bit PWM modes. In all other modes, the Auto-Reload registers have no function.<br>0: Read/Write Capture/Compare Registers at PCA0CPHn and PCA0CPLn.<br>1: Read/Write Auto-Reload Registers at PCA0CPHn and PCA0CPLn. |

| 6   | ECOV       | Cycle Overflow Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |            | This bit sets the masking of the Cycle Overflow Flag (COVF) interrupt.                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | 0: COVF will not generate PCA interrupts.                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 001/5      | 1: A PCA interrupt will be generated when COVF is set.                                                                                                                                                                                                                                                                                                                                                                                         |

| 5   | COVF       | Cycle Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |            | This bit indicates an overflow of the 8th, 9th, 10th, or 11th bit of the main PCA counter (PCA0). The specific bit used for this flag depends on the setting of the Cycle Length Select bits. The bit can be set by hardware or software, but must be cleared by software.                                                                                                                                                                     |

|     |            | 0: No overflow has occurred since the last time this bit was cleared.                                                                                                                                                                                                                                                                                                                                                                          |

|     |            | 1: An overflow has occurred since the last time this bit was cleared.                                                                                                                                                                                                                                                                                                                                                                          |

| 4:2 | Unused     | Unused.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |            | Read = 000b; Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1:0 | CLSEL[1:0] | Cycle Length Select.                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |            | When 16-bit PWM mode is not selected, these bits select the length of the PWM cycle, between 8, 9, 10, or 11 bits. This affects all channels configured for PWM which are not using 16-bit PWM mode. These bits are ignored for individual channels configured to16-bit PWM mode. 00: 8 bits.                                                                                                                                                  |

|     |            | 01: 9 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |            | 10: 10 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |            | 11: 11 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                   |