# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 16                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 768 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                    |

| Data Converters            | A/D 15x10/12b                                                  |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                 |

| Supplier Device Package    | 24-QSOP                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f902-gu |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 13.5.3.System Clock                                    | 138 |

|--------------------------------------------------------|-----|

| 13.6.Minimizing Flash Read Current                     |     |

| 14. Power Management                                   |     |

| 14.1.Normal Mode                                       |     |

| 14.2.Idle Mode                                         |     |

| 14.3.Stop Mode                                         |     |

| 14.4.Suspend Mode                                      |     |

| 14.5.Sleep Mode                                        |     |

| 14.6.Configuring Wakeup Sources                        |     |

| 14.7.Determining the Event that Caused the Last Wakeup |     |

| 14.8.Power Management Specifications                   |     |

| 15. Cyclic Redundancy Check Unit (CRC0)                |     |

| 15.1.CRC Algorithm                                     |     |

| 15.2.Preparing for a CRC Calculation                   | 154 |

| 15.3.Performing a CRC Calculation                      |     |

| 15.4.Accessing the CRC0 Result                         |     |

| 15.5.CRC0 Bit Reverse Feature                          |     |

| 16. On-Chip DC-DC Converter (DC0)                      |     |

| 16.1.Startup Behavior                                  |     |

| 16.2.High Power Applications                           |     |

| 16.3.Pulse Skipping Mode                               |     |

| 16.4.Enabling the DC-DC Converter                      |     |

| 16.5.Minimizing Power Supply Noise                     |     |

| 16.6.Selecting the Optimum Switch Size                 | 164 |

| 16.7.DC-DC Converter Clocking Options                  |     |

| 16.8.DC-DC Converter Behavior in Sleep Mode            |     |

| 16.9.Bypass Mode (C8051F912/02 only)                   |     |

| 16.10.Low Power Mode (C8051F912/02 only)               |     |

| 16.11.Passive Diode Mode (C8051F912/02 only)           |     |

| 16.12.DC-DC Converter Register Descriptions            |     |

| 16.13.DC-DC Converter Specifications                   |     |

| 17. Voltage Regulator (VREG0)                          |     |

| 17.1.Voltage Regulator Electrical Specifications       |     |

| 18. Reset Sources                                      |     |

| 18.1.Power-On (VBAT Supply Monitor) Reset              |     |

| 18.2.Power-Fail (VDD/DC+ Supply Monitor) Reset         | 173 |

| 18.3.External Reset                                    |     |

| 18.4.Missing Clock Detector Reset                      |     |

| 18.5.Comparator0 Reset                                 |     |

| 18.6.PCA Watchdog Timer Reset                          | 176 |

| 18.7.Flash Error Reset                                 |     |

| 18.8.SmaRTClock (Real Time Clock) Reset                |     |

| 18.9.Software Reset                                    |     |

| 19. Clocking Sources                                   |     |

| 19.1.Programmable Precision Internal Oscillator        |     |

|                                                        |     |

### Table 4.12. Voltage Reference Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameter                         | Conditions                                                     | Min   | Тур   | Max      | Units |

|-----------------------------------|----------------------------------------------------------------|-------|-------|----------|-------|

| Internal High Speed Referer       | ice (REFSL[1:0] = 11)                                          |       |       |          |       |

| Output Voltage                    | −40 to +85 °C,                                                 | 1.60  | 1.65  | 1.70     | V     |

| Oulput vollage                    | V <sub>DD</sub> = 1.8–3.6 V                                    |       |       |          |       |

| VREF Turn-on Time                 |                                                                | —     | _     | 1.5      | μs    |

| Supply Current                    | Normal Power Mode                                              | —     | 260   | —        | μA    |

| Supply Current                    | Low Power Mode                                                 | —     | 140   | —        |       |

| Internal Precision Reference      | e (REFSL[1:0] = 00, REFOE = 1)                                 |       |       |          |       |

| Output Voltage                    | −40 to +85 °C,                                                 | 1.645 | 1.680 | 1.715    | V     |

| Culput Voltage                    | V <sub>DD</sub> = 1.8–3.6 V                                    |       |       |          |       |

| VREF Short-Circuit Current        |                                                                | —     | 10    | _        | mA    |

| Load Regulation                   | Load = 0 to 200 µA to AGND                                     | —     | 400   |          | μV/μΑ |

| VREF Turn-on Time 1               | 4.7 μF tantalum, 0.1 μF ceramic<br>bypass, settling to 0.5 LSB | —     | 15    | —        | ms    |

| VREF Turn-on Time 2               | 0.1 µF ceramic bypass, settling to 0.5 LSB                     | _     | 300   | _        | μs    |

| VREF Turn-on Time 3               | no bypass cap, settling to 0.5 LSB                             | —     | 25    | _        | μs    |

| Supply Current                    |                                                                | —     | 15    |          | μA    |

| External Reference (REFSL)        | 1:0] = 00, REFOE = 0)                                          |       |       |          |       |

| Input Voltage Range               |                                                                | 0     | _     | $V_{DD}$ | V     |

| Input Current                     | Sample Rate = 300 ksps; VREF = 3.0 V                           | _     | 5.25  | _        | μA    |

| Note: Blue indicates a feature of | only available on 'F912 and 'F902 devices                      |       |       | •        |       |

## SFR Definition 5.3. ADC0AC: ADC0 Accumulator Configuration

| Bit   | 7       | 6     | 5 | 4       | 3 | 2 | 1      | 0 |

|-------|---------|-------|---|---------|---|---|--------|---|

| Name  | AD012BE | AD0AE |   | AD0SJST |   |   | AD0RPT |   |

| Туре  | R/W     | W     |   | R/W     |   |   | R/W    |   |

| Reset | 0       | 0     | 0 | 0       | 0 | 0 | 0      | 0 |

#### SFR Page = 0x0; SFR Address = 0xBA

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AD012BE      | ADC0 12-Bit Mode Enable.<br>Enables 12-bit Mode. Only available on 'F912 and 'F902 devices.<br>0: 12-bit Mode Disabled.<br>1: 12-bit Mode Enabled.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6   | AD0AE        | <ul> <li>ADC0 Accumulate Enable.</li> <li>Enables multiple conversions to be accumulated when burst mode is disabled.</li> <li>0: ADC0H:ADC0L contain the result of the latest conversion when Burst Mode is disabled.</li> <li>1: ADC0H:ADC0L contain the accumulated conversion results when Burst Mode is disabled. Software must write 0x0000 to ADC0H:ADC0L to clear the accumulated result.</li> <li>This bit is write-only. Always reads 0b.</li> </ul>                                                                                                                   |

| 5:3 | AD0SJST[2:0] | ADC0 Accumulator Shift and Justify.<br>Specifies the format of data read from ADC0H:ADC0L.<br>000: Right justified. No shifting applied.<br>001: Right justified. Shifted right by 1 bit.<br>010: Right justified. Shifted right by 2 bits.<br>011: Right justified. Shifted right by 3 bits.<br>100: Left justified. No shifting applied.<br>All remaining bit combinations are reserved.                                                                                                                                                                                       |

| 2:0 | AD0RPT[2:0]  | <ul> <li>ADC0 Repeat Count.</li> <li>Selects the number of conversions to perform and accumulate in Burst Mode.</li> <li>This bit field must be set to 000 if Burst Mode is disabled.</li> <li>000: Perform and Accumulate 1 conversion.</li> <li>001: Perform and Accumulate 4 conversions.</li> <li>010: Perform and Accumulate 8 conversions.</li> <li>011: Perform and Accumulate 16 conversions.</li> <li>100: Perform and Accumulate 32 conversions.</li> <li>101: Perform and Accumulate 64 conversions.</li> <li>All remaining bit combinations are reserved.</li> </ul> |

#### Table 11.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved. SFRs highlighted in **blue** are only available on 'F912 and 'F902 devices.

| Register | Address | SFR Page | Description                          | Page |

|----------|---------|----------|--------------------------------------|------|

| CPT1MD   | 0x9C    | 0x0      | Comparator1 Mode Selection           | 94   |

| CPT1MX   | 0x9E    | 0x0      | Comparator1 Mux Selection            | 97   |

| CRC0AUTO | 0x96    | 0xF      | CRC0 Automatic Control               | 157  |

| CRC0CN   | 0x92    | 0xF      | CRC0 Control                         | 155  |

| CRC0CNT  | 0x97    | 0xF      | CRC0 Automatic Flash Sector Count    | 158  |

| CRC0DAT  | 0x91    | 0xF      | CRC0 Data                            | 156  |

| CRC0FLIP | 0x95    | 0xF      | CRC0 Flip                            | 159  |

| CRC0IN   | 0x93    | 0xF      | CRC0 Input                           | 156  |

| DC0CF    | 0x96    | 0x0      | DC0 (DC-DC Converter) Configuration  | 168  |

| DC0CN    | 0x97    | 0x0      | DC0 (DC-DC Converter) Control        | 167  |

| DC0MD    | 0x94    | 0xF      | DC0 (DC-DC Converter) Mode           | 169  |

| DPH      | 0x83    | All      | Data Pointer High                    | 104  |

| DPL      | 0x82    | All      | Data Pointer Low                     | 104  |

| EIE1     | 0xE6    | All      | Extended Interrupt Enable 1          | 126  |

| EIE2     | 0xE7    | All      | Extended Interrupt Enable 2          | 128  |

| EIP1     | 0xF6    | 0x0      | Extended Interrupt Priority 1        | 127  |

| EIP2     | 0xF7    | 0x0      | Extended Interrupt Priority 2        | 129  |

| EMI0CN   | 0xAA    | 0x0      | EMIF Control                         | 112  |

| FLKEY    | 0xB7    | 0x0      | Flash Lock And Key                   | 141  |

| FLSCL    | 0xB6    | 0x0      | Flash Scale                          | 141  |

| IE       | 0xA8    | All      | Interrupt Enable                     | 124  |

| IP       | 0xB8    | 0x0      | Interrupt Priority                   | 125  |

| IREF0CN  | 0xB9    | 0x0      | Current Reference IREF Control       | 86   |

| IREF0CF  | 0xB9    | 0xF      | Current Reference IREF Configuration | 87   |

| IT01CF   | 0xE4    | 0x0      | INT0/INT1 Configuration              | 131  |

| OSCICL   | 0xB3    | 0x0      | Internal Oscillator Calibration      | 186  |

| OSCICN   | 0xB2    | 0x0      | Internal Oscillator Control          | 186  |

| OSCXCN   | 0xB1    | 0x0      | External Oscillator Control          | 187  |

| P0       | 0x80    | All      | Port 0 Latch                         | 218  |

| P0DRV    | 0xA4    | 0xF      | Port 0 Drive Strength                | 220  |

| P0MASK   | 0xC7    | 0x0      | Port 0 Mask                          | 215  |

| POMAT    | 0xD7    | 0x0      | Port 0 Match                         | 215  |

| POMDIN   | 0xF1    | 0x0      | Port 0 Input Mode Configuration      | 219  |

## SFR Definition 12.2. IP: Interrupt Priority

| Bit   | 7 | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---|-------|-----|-----|-----|-----|-----|-----|

| Name  |   | PSPI0 | PT2 | PS0 | PT1 | PX1 | PT0 | PX0 |

| Туре  | R | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 1 | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Page = 0x0; SFR Address = 0xB8; Bit-Addressable

| Bit | Name   | Function                                                                                                                                                                                                                                                       |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused | Unused.<br>Read = 1b, Write = don't care.                                                                                                                                                                                                                      |

| 6   | PSPI0  | <ul> <li>Serial Peripheral Interface (SPI0) Interrupt Priority Control.</li> <li>This bit sets the priority of the SPI0 interrupt.</li> <li>0: SPI0 interrupt set to low priority level.</li> <li>1: SPI0 interrupt set to high priority level.</li> </ul>     |

| 5   | PT2    | Timer 2 Interrupt Priority Control.This bit sets the priority of the Timer 2 interrupt.0: Timer 2 interrupt set to low priority level.1: Timer 2 interrupt set to high priority level.                                                                         |

| 4   | PS0    | UART0 Interrupt Priority Control.<br>This bit sets the priority of the UART0 interrupt.<br>0: UART0 interrupt set to low priority level.<br>1: UART0 interrupt set to high priority level.                                                                     |

| 3   | PT1    | Timer 1 Interrupt Priority Control.This bit sets the priority of the Timer 1 interrupt.0: Timer 1 interrupt set to low priority level.1: Timer 1 interrupt set to high priority level.                                                                         |

| 2   | PX1    | <ul> <li>External Interrupt 1 Priority Control.</li> <li>This bit sets the priority of the External Interrupt 1 interrupt.</li> <li>0: External Interrupt 1 set to low priority level.</li> <li>1: External Interrupt 1 set to high priority level.</li> </ul> |

| 1   | PT0    | Timer 0 Interrupt Priority Control.This bit sets the priority of the Timer 0 interrupt.0: Timer 0 interrupt set to low priority level.1: Timer 0 interrupt set to high priority level.                                                                         |

| 0   | PX0    | External Interrupt 0 Priority Control.<br>This bit sets the priority of the External Interrupt 0 interrupt.<br>0: External Interrupt 0 set to low priority level.<br>1: External Interrupt 0 set to high priority level.                                       |

## SFR Definition 12.3. EIE1: Extended Interrupt Enable 1

| Bit   | 7   | 6    | 5    | 4     | 3     | 2      | 1      | 0     |

|-------|-----|------|------|-------|-------|--------|--------|-------|

| Name  | ET3 | ECP1 | ECP0 | EPCA0 | EADC0 | EWADC0 | ERTC0A | ESMB0 |

| Туре  | R/W | R/W  | R/W  | R/W   | R/W   | R/W    | R/W    | R/W   |

| Reset | 0   | 0    | 0    | 0     | 0     | 0      | 0      | 0     |

#### SFR Page = All Pages; SFR Address = 0xE6

| Bit | Name   | Function                                                                                                                                                                                                                                                                          |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ET3    | Enable Timer 3 Interrupt.<br>This bit sets the masking of the Timer 3 interrupt.<br>0: Disable Timer 3 interrupts.<br>1: Enable interrupt requests generated by the TF3L or TF3H flags.                                                                                           |

| 6   | ECP1   | Enable Comparator1 (CP1) Interrupt.<br>This bit sets the masking of the CP1 interrupt.<br>0: Disable CP1 interrupts.<br>1: Enable interrupt requests generated by the CP1RIF or CP1FIF flags.                                                                                     |

| 5   | ECP0   | Enable Comparator0 (CP0) Interrupt.<br>This bit sets the masking of the CP0 interrupt.<br>0: Disable CP0 interrupts.<br>1: Enable interrupt requests generated by the CP0RIF or CP0FIF flags.                                                                                     |

| 4   | EPCA0  | <ul> <li>Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> </ul>                                              |

| 3   | EADC0  | Enable ADC0 Conversion Complete Interrupt.<br>This bit sets the masking of the ADC0 Conversion Complete interrupt.<br>0: Disable ADC0 Conversion Complete interrupt.<br>1: Enable interrupt requests generated by the AD0INT flag.                                                |

| 2   | EWADC0 | <ul> <li>Enable Window Comparison ADC0 Interrupt.</li> <li>This bit sets the masking of ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>1: Enable interrupt requests generated by ADC0 Window Compare flag (AD0WINT).</li> </ul> |

| 1   | ERTC0A | Enable SmaRTClock Alarm Interrupts.<br>This bit sets the masking of the SmaRTClock Alarm interrupt.<br>0: Disable SmaRTClock Alarm interrupts.<br>1: Enable interrupt requests generated by a SmaRTClock Alarm.                                                                   |

| 0   | ESMB0  | Enable SMBus (SMB0) Interrupt.<br>This bit sets the masking of the SMB0 interrupt.<br>0: Disable all SMB0 interrupts.<br>1: Enable interrupt requests generated by SMB0.                                                                                                          |

#### 13.1.2. Flash Erase Procedure

The Flash memory is organized in 512-byte pages. The erase operation applies to an entire page (setting all bytes in the page to 0xFF). To erase an entire Flash page, perform the following steps:

- 1. Save current interrupt state and disable interrupts.

- 2. Set the PSEE bit (register PSCTL).

- 3. Set the PSWE bit (register PSCTL).

- 4. Write the first key code to FLKEY: 0xA5.

- 5. Write the second key code to FLKEY: 0xF1.

- 6. Using the MOVX instruction, write a data byte to any location within the page to be erased.

- 7. Clear the PSWE and PSEE bits.

- 8. Restore previous interrupt state.

Steps 4–6 must be repeated for each 512-byte page to be erased.

#### Notes:

- 1. To maintain code compatibility with the 'F93x-'F92x product family, the erase procedure should be performed on two consecutive 512-byte sections of memory at a time. This allows the same software to run on devices with 1024-byte or 512-byte Flash pages. Using this technique, devices with 1024-byte Flash pages will have each Flash page erased twice.

- 2. Flash security settings may prevent erasure of some Flash pages, such as the reserved area and the page containing the lock bytes. For a summary of Flash security settings and restrictions affecting Flash erase operations, please see Section "13.3. Security Options" on page 134.

- 3. 8-bit MOVX instructions cannot be used to erase or write to Flash memory at addresses higher than 0x00FF.

#### 13.1.3. Flash Write Procedure

A write to Flash memory can clear bits to logic 0 but cannot set them; only an erase operation can set bits to logic 1 in Flash. A byte location to be programmed should be erased before a new value is written.

The recommended procedure for writing a single byte in Flash is as follows:

- 1. Save current interrupt state and disable interrupts.

- 2. Ensure that the Flash byte has been erased (has a value of 0xFF).

- 3. Set the PSWE bit (register PSCTL).

- 4. Clear the PSEE bit (register PSCTL).

- 5. Write the first key code to FLKEY: 0xA5.

- 6. Write the second key code to FLKEY: 0xF1.

- 7. Using the MOVX instruction, write a single data byte to the desired location within the 1024byte sector.

- 8. Clear the PSWE bit.

- 9. Restore previous interrupt state.

Steps 5–7 must be repeated for each byte to be written.

#### Notes:

- 1. Flash security settings may prevent writes to some areas of Flash, such as the reserved area. For a summary of Flash security settings and restrictions affecting Flash write operations, please see Section "13.3. Security Options" on page 134.

- 2. 8-bit MOVX instructions cannot be used to erase or write to Flash memory at addresses higher than 0x00FF.

#### 13.2. Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction and read using the MOVC instruction. MOVX read instructions always target XRAM.

An additional 512-byte scratchpad is available for non-volatile data storage. It is accessible at addresses 0x0000 to 0x01FF when SFLE is set to 1. The scratchpad area cannot be used for code execution.

## 16.5. Minimizing Power Supply Noise

To minimize noise on the power supply lines, the GND and GND/DC- pins should be kept separate, as shown in Figure 16.2; one or the other should be connected to the pc board ground plane. For applications in which the dc-dc converter is used only to power internal circuits, the GND pin is normally connected to the board ground.

The large decoupling capacitors in the input and output circuits ensure that each supply is relatively quiet with respect to its own ground. However, connecting a circuit element "diagonally" (e.g. connecting an external chip between VDD/DC+ and GND, or between VBAT and GND/DC-) can result in high supply noise across that circuit element. For applications in which the dc-dc converter is used to power external analog circuitry, it is recommended to connect the GND/DC– pin to the board ground and connect the battery's negative terminal to the GND pin only, which is not connected to board ground.

To accommodate situations in which ADC0 is sampling a signal that is referenced to one of the external grounds, we recommend using the Analog Ground Reference (P0.1/AGND) option described in Section 5.12. This option prevents any voltage differences between the internal chip ground and the external grounds from modulating the ADC input signal. If this option is enabled, the P0.1 pin should be tied to the ground reference of the external analog input signal. When using the ADC with the dc-dc converter, we also recommend enabling the SYNC bit in the DC0CN register to minimize interference.

These general guidelines provide the best performance in most applications, though some situations may benefit from experimentation to eliminate any residual noise issues. Examples might include tying the grounds together, using additional low-inductance decoupling caps in parallel with the recommended ones, investigating the effects of different dc-dc converter settings, etc.

#### 16.6. Selecting the Optimum Switch Size

The dc-dc converter has two built-in switches (the diode bypass switch and duty cycle control switch). To maximize efficiency, one of two switch sizes may be selected. The large switches are ideal for carrying high currents and the small switches are ideal for low current applications. The ideal switchover point to switch from the small switches to the large switches varies with the programmed output voltage. At an output voltage of 2 V, the ideal switchover point is at approximately 4 mA total output current. At an output voltage of 3 V, the ideal switchover point is at approximately 8 mA total output current.

## 16.7. DC-DC Converter Clocking Options

The dc-dc converter may be clocked from its internal oscillator, or from any system clock source, selectable by the CLKSEL bit (DC0CF.0). The dc-dc converter internal oscillator frequency is approximately 2.4 MHz. For a more accurate clock source, the system clock, or a divided version of the system clock may be used as the dc-dc clock source. The dc-dc converter has a built in clock divider (configured using DC0CF[6:5]) which allows any system clock frequency over 1.6 MHz to generate a valid clock in the range of 1.6 to 3.2 MHz.

When the precision internal oscillator is selected as the system clock source, the OSCICL register may be used to fine tune the oscillator frequency and the dc-dc converter clock. The oscillator frequency should only be decreased since it is factory calibrated at its maximum frequency. The minimum frequency which can be reached by the oscillator after taking into account process variations is approximately 16 MHz. The system clock routed to the dc-dc converter clock divider also may be inverted by setting the CLKINV bit (DC0CF.3) to logic 1. These options can be used to minimize interference in noise sensitive applications.

#### 16.8. DC-DC Converter Behavior in Sleep Mode

When the C8051F91x-C8051F90x devices are placed in Sleep mode, the dc-dc converter is disabled, and the VDD/DC+ output is internally connected to VBAT by default. This behavior ensures that the GPIO pins are powered from a low-impedance source during sleep mode. If the GPIO pins are not used as inputs or

### 20.2. SmaRTClock Clocking Sources

The SmaRTClock peripheral is clocked from its own timebase, independent of the system clock. The SmaRTClock timebase can be derived from an external CMOS clock, the internal LFO ('F912 and 'F902 devices only), or the SmaRTClock oscillator circuit, which has two modes of operation: Crystal Mode, and Self-Oscillate Mode. The oscillation frequency is 32.768 kHz in Crystal Mode and can be programmed in the range of 10 kHz to 40 kHz in Self-Oscillate Mode. The internal LFO frequency is 16.4 kHz ±20%. The frequency of the SmaRTClock oscillator can be measured with respect to another oscillator using an on-chip timer. See Section "25. Timers" on page 270 for more information on how this can be accomplished.

**Note:** The SmaRTClock timebase can be selected as the system clock and routed to a port pin. See Section "19. Clocking Sources" on page 179 for information on selecting the system clock source and Section "21. Port Input/Output" on page 205 for information on how to route the system clock to a port pin. On 'F912 and 'F902 devices, the SmaRTClock timebase can be routed to a port pin while the device is in its ultra low power sleep mode. See the PMU0MD register description for details.

#### 20.2.1. Using the SmaRTClock Oscillator with a Crystal or External CMOS Clock

When using Crystal Mode, a 32.768 kHz crystal should be connected between XTAL3 and XTAL4. No other external components are required. The following steps show how to start the SmaRTClock crystal oscillator in software:

- 1. Set SmaRTClock to Crystal Mode (XMODE = 1).

- 2. Disable Automatic Gain Control (AGCEN) and enable Bias Doubling (BIASX2) for fast crystal startup.

- 3. Set the desired loading capacitance (RTC0XCF).

- 4. Enable power to the SmaRTClock oscillator circuit (RTC0EN = 1).

- 5. Wait 20 ms.

- 6. Poll the SmaRTClock Clock Valid Bit (CLKVLD) until the crystal oscillator stabilizes.

- 7. Poll the SmaRTClock Load Capacitance Ready Bit (LOADRDY) until the load capacitance reaches its programmed value.

- 8. Enable Automatic Gain Control (AGCEN) and disable Bias Doubling (BIASX2) for maximum power savings.

- 9. Enable the SmaRTClock missing clock detector.

- 10. Wait 2 ms.

- 11. Clear the PMU0CF wake-up source flags.

In Crystal Mode, the SmaRTClock oscillator may be driven by an external CMOS clock. The CMOS clock should be applied to XTAL3. XTAL4 should be left floating. The input low voltage (VIL) and input high voltage (VIH) for XTAL3 when used with an external CMOS clock are 0.1 and 0.8 V, respectively. The SmaRTClock oscillator should be configured to its lowest bias setting with AGC disabled. The CLKVLD bit is indeterminate when using a CMOS clock, however, the OSCFAIL bit may be checked 2 ms after SmaRTClock oscillator is powered on to ensure that there is a valid clock on XTAL3.

## Internal Register Definition 20.4. RTC0CN: SmaRTClock Control

| Bit   | 7                        | 6                                                                                                         | 5                                                                                                                                                                                        | 4                                                             | 3                             | 2           | 1                                                                                                                                                                                                                                                                                                                        | 0          |  |  |  |  |  |  |

|-------|--------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|--|--|

| Name  | e RTCOEN                 | MCLKEN                                                                                                    | OSCFAIL                                                                                                                                                                                  | RTC0TR                                                        | RTC0AEN                       | ALRM        | <b>RTC0SET</b>                                                                                                                                                                                                                                                                                                           | RTC0CAP    |  |  |  |  |  |  |

| Туре  | Type R/W R/W R/W R/W R/W |                                                                                                           |                                                                                                                                                                                          |                                                               |                               |             | R/W                                                                                                                                                                                                                                                                                                                      | R/W        |  |  |  |  |  |  |

| Rese  | <b>t</b> 0               | 0                                                                                                         | Varies                                                                                                                                                                                   | 0                                                             | 0                             | 0           | 0                                                                                                                                                                                                                                                                                                                        | 0          |  |  |  |  |  |  |

| SmaR  | TClock Add               | ress = $0x04$                                                                                             |                                                                                                                                                                                          |                                                               |                               |             |                                                                                                                                                                                                                                                                                                                          |            |  |  |  |  |  |  |

| Bit   | Name                     |                                                                                                           |                                                                                                                                                                                          |                                                               | Function                      |             |                                                                                                                                                                                                                                                                                                                          |            |  |  |  |  |  |  |

| 7     | RTC0EN                   | SmaRTClock<br>Enables/disat<br>0: SmaRTClo<br>1: SmaRTClo                                                 | oles the Sma<br>ck oscillator                                                                                                                                                            | disabled.                                                     | cillator and a                | ssociated b | pias currents.                                                                                                                                                                                                                                                                                                           |            |  |  |  |  |  |  |

| 6     | MCLKEN                   | Missing Sma<br>Enables/disat<br>0: Missing Sn<br>1: Missing Sn                                            | oles the miss<br>naRTClock d                                                                                                                                                             | ing SmaRT<br>etector disa                                     | Clock detecto<br>bled.        | or.         |                                                                                                                                                                                                                                                                                                                          |            |  |  |  |  |  |  |

| 5     | OSCFAIL                  | SmaRTClock<br>Set by hardwa<br>cleared by so<br>oscillator is di                                          | are when a r<br>ftware. The v                                                                                                                                                            | nissing Sma                                                   | RTClock det                   |             |                                                                                                                                                                                                                                                                                                                          |            |  |  |  |  |  |  |

| 4     | RTC0TR                   | SmaRTClock<br>Controls if the<br>0: SmaRTClo<br>1: SmaRTClo                                               | e SmaRTClo<br>ck timer is st                                                                                                                                                             | ck timer is ru<br>topped.                                     | unning or sto                 | pped (holds | s current valu                                                                                                                                                                                                                                                                                                           | e).        |  |  |  |  |  |  |

| 3     | RTC0AEN                  | SmaRTClock<br>Enables/disat<br>0: SmaRTClo<br>1: SmaRTClo                                                 | oles the Sma<br>ck alarm dis                                                                                                                                                             | RTClock ala abled.                                            | arm function.                 | Also clears | the ALRM fl                                                                                                                                                                                                                                                                                                              | ag.        |  |  |  |  |  |  |

| 2     | ALRM                     | SmaRTClock<br>Flag and Aut<br>Enable.<br>Reads return<br>alarm event fl<br>Writes enable<br>Auto Reset fu | 0: Sma<br>event f<br>he 1: Sma                                                                                                                                                           | RTClock ala<br>lag is de-ass<br>RTClock ala<br>lag is asserte | sserted. 1: Enable Auto Reset |             |                                                                                                                                                                                                                                                                                                                          |            |  |  |  |  |  |  |

| 1     | RTC0SET                  | SmaRTClock<br>Writing 1 initia<br>ware to indica                                                          | ates a SmaR<br>ate that the ti                                                                                                                                                           | mer set ope                                                   |                               |             | is cleared to                                                                                                                                                                                                                                                                                                            | 0 by hard- |  |  |  |  |  |  |

| 0     | RTC0CAP                  | Writing 1 initia                                                                                          | SmaRTClock Timer Capture.<br>Writing 1 initiates a SmaRTClock timer capture operation. This bit is cleared to 0 by<br>mardware to indicate that the timer capture operation is complete. |                                                               |                               |             |                                                                                                                                                                                                                                                                                                                          |            |  |  |  |  |  |  |

| Note: | Managemen                | it" on page 143 f                                                                                         | or information                                                                                                                                                                           |                                                               |                               |             | hardware to indicate that the timer capture operation is complete.<br>The ALRM flag will remain asserted for a maximum of one SmaRTClock cycle. See Section "Power<br>Management" on page 143 for information on how to capture a SmaRTClock Alarm event using a flag which<br>is not automatically cleared by hardware. |            |  |  |  |  |  |  |

## SFR Definition 21.3. XBR2: Port I/O Crossbar Register 2

| Bit   | 7       | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---------|-------|-----|-----|-----|-----|-----|-----|

| Name  | WEAKPUD | XBARE |     |     |     |     |     |     |

| Туре  | R/W     | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0       | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Page = 0x0; SFR Address = 0xE3

| Bit     | Name           | Function                                                                                                               |

|---------|----------------|------------------------------------------------------------------------------------------------------------------------|

| 7       | WEAKPUD        | <b>Port I/O Weak Pullup Disable.</b><br>0: Weak Pullups enabled (except for Port I/O pins configured for analog mode). |

| 6       | XBARE          | Crossbar Enable.                                                                                                       |

|         |                | 0: Crossbar disabled.<br>1: Crossbar enabled.                                                                          |

| 5:0     | Unused         | Unused.                                                                                                                |

|         |                | Read = 000000b; Write = Don't Care.                                                                                    |

| Note: T | he Crossbar mu | ust be enabled (XBARE = 1) to use any Port pin as a digital output.                                                    |

## 21.5. Special Function Registers for Accessing and Configuring Port I/O

All Port I/O are accessed through corresponding special function registers (SFRs) that are both byte addressable and bit addressable. When writing to a Port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the Port's input pins are returned regardless of the XBRn settings (i.e., even when the pin is assigned to another signal by the Crossbar, the Port register can always read its corresponding Port I/O pin). The exception to this is the execution of the read-modify-write instructions that target a Port Latch register as the destination. The read-modify-write instructions when operating on a Port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SETB, when the destination is an individual bit in a Port SFR. For these instructions, the value of the latch register (not the pin) is read, modified, and written back to the SFR.

Each Port has a corresponding PnSKIP register which allows its individual Port pins to be assigned to digital functions or skipped by the Crossbar. All Port pins used for analog functions, GPIO, or dedicated digital functions such as the EMIF should have their PnSKIP bit set to 1.

The Port input mode of the I/O pins is defined using the Port Input Mode registers (PnMDIN). Each Port cell can be configured for analog or digital I/O. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is P2.7, which can only be used for digital I/O.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings.

The drive strength of the output drivers are controlled by the Port Drive Strength (PnDRV) registers. The default is low drive strength. See Section "4. Electrical Characteristics" on page 36 for the difference in output drive strength between the two modes.

### 22.4. Using the SMBus

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting control for serial transfers; higher level protocol is determined by user software. The SMBus interface provides the following application-independent features:

- Byte-wise serial data transfers

- Clock signal generation on SCL (Master Mode only) and SDA data synchronization

- Timeout/bus error recognition, as defined by the SMB0CF configuration register

- START/STOP timing, detection, and generation

- Bus arbitration

- Interrupt generation

- Status information

- Optional hardware recognition of slave address and automatic acknowledgement of address/data

SMBus interrupts are generated for each data byte or slave address that is transferred. When hardware acknowledgement is disabled, the point at which the interrupt is generated depends on whether the hardware is acting as a data transmitter or receiver. When a transmitter (i.e. sending address/data, receiving an ACK), this interrupt is generated after the ACK cycle so that software may read the received ACK value; when receiving data (i.e. receiving address/data, sending an ACK), this interrupt is generated before the ACK cycle so that software may define the outgoing ACK value. If hardware acknowledgement is enabled, these interrupts are always generated after the ACK cycle. See Section 22.5 for more details on transmission sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control register) to find the cause of the SMBus interrupt. The SMB0CN register is described in Section 22.4.2; Table 22.5 provides a quick SMB0CN decoding reference.

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 22.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD                                                                                                                                                                                                                                                                                                                   | Minimum SDA Setup Time              | Minimum SDA Hold Time |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------|--|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                           | T <sub>low</sub> – 4 system clocks  |                       |  |  |  |  |  |

| 0                                                                                                                                                                                                                                                                                                                         | or                                  | 3 system clocks       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                           | 1 system clock + s/w delay*         |                       |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                         | 1 11 system clocks 12 system clocks |                       |  |  |  |  |  |

| *Note: Setup Time for ACK bit transmissions and the MSB of all data transfers. When<br>using software acknowledgement, the s/w delay occurs between the time SMB0DAT<br>or ACK is written and when SI is cleared. Note that if SI is cleared in the same write<br>that defines the outgoing ACK value, s/w delay is zero. |                                     |                       |  |  |  |  |  |

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "22.3.4. SCL Low Timeout" on page 228). The SMBus interface will force Timer 3 to reload while SCL is high, and allow Timer 3 to count when SCL is low. The Timer 3 interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 22.4).

### 24.1. Signal Descriptions

The four signals used by each SPIn (MOSI, MISO, SCK, NSS) are described below.

#### 24.1.1. Master Out, Slave In (MOSI)

The master-out, slave-in (MOSI) signal is an output from a master device and an input to slave devices. It is used to serially transfer data from the master to the slave. This signal is an output when SPIn is operating as a master anSPInd an input when SPIn is operating as a slave. Data is transferred most-significant bit first. When configured as a master, MOSI is driven by the MSB of the shift register in both 3- and 4-wire mode.

#### 24.1.2. Master In, Slave Out (MISO)

The master-in, slave-out (MISO) signal is an output from a slave device and an input to the master device. It is used to serially transfer data from the slave to the master. This signal is an input when SPIn is operating as a master and an output when SPIn is operating as a slave. Data is transferred most-significant bit first. The MISO pin is placed in a high-impedance state when the SPI module is disabled and when the SPI operates in 4-wire mode as a slave that is not selected. When acting as a slave in 3-wire mode, MISO is always driven by the MSB of the shift register.

#### 24.1.3. Serial Clock (SCK)

The serial clock (SCK) signal is an output from the master device and an input to slave devices. It is used to synchronize the transfer of data between the master and slave on the MOSI and MISO lines. SPIn generates this signal when operating as a master. The SCK signal is ignored by a SPI slave when the slave is not selected (NSS = 1) in 4-wire slave mode.

#### 24.1.4. Slave Select (NSS)

The function of the slave-select (NSS) signal is dependent on the setting of the NSSnMD1 and NSSnMD0 bits in the SPInCN register. There are three possible modes that can be selected with these bits:

- NSSMD[1:0] = 00: 3-Wire Master or 3-Wire Slave Mode: SPIn operates in 3-wire mode, and NSS is disabled. When operating as a slave device, SPIn is always selected in 3-wire mode. Since no select signal is present, SPIn must be the only slave on the bus in 3-wire mode. This is intended for point-to-point communication between a master and one slave.

- 2. NSSMD[1:0] = 01: 4-Wire Slave or Multi-Master Mode: SPIn operates in 4-wire mode, and NSS is enabled as an input. When operating as a slave, NSS selects the SPIn device. When operating as a master, a 1-to-0 transition of the NSS signal disables the master function of SPIn so that multiple master devices can be used on the same SPI bus.

- NSSMD[1:0] = 1x: 4-Wire Master Mode: SPIn operates in 4-wire mode, and NSS is enabled as an output. The setting of NSSMD0 determines what logic level the NSS pin will output. This configuration should only be used when operating SPIn as a master device.

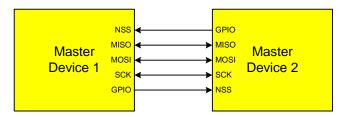

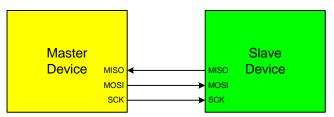

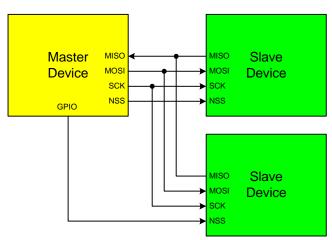

See Figure 24.2, Figure 24.3, and Figure 24.4 for typical connection diagrams of the various operational modes. **The setting of NSSMD bits affects the pinout of the device.** When in 3-wire master or 3-wire slave mode, the NSS pin will not be mapped by the crossbar. In all other modes, the NSS signal will be mapped to a pin on the device. See Section "21. Port Input/Output" on page 205 for general purpose port I/ O and crossbar information.

Figure 24.2. Multiple-Master Mode Connection Diagram

Figure 24.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagram

Figure 24.4. 4-Wire Single Master Mode and 4-Wire Slave Mode Connection Diagram

## SFR Definition 25.4. TL0: Timer 0 Low Byte

| Bit   | 7              | 6           | 5       | 4 | 3 | 2 | 1 | 0 |

|-------|----------------|-------------|---------|---|---|---|---|---|

| Nam   | e              | TL0[7:0]    |         |   |   |   |   |   |

| Туре  | Type R/W       |             |         |   |   |   |   |   |

| Rese  | et 0           | 0           | 0       | 0 | 0 | 0 | 0 | 0 |

| SFR F | Page = 0x0; SI | R Address = | = 0x8A  |   |   |   |   |   |

| Bit   | Name           | Function    |         |   |   |   |   |   |

| 7:0   | TL0[7:0]       | Timer 0 Lov | w Byte. |   |   |   |   |   |

| :0 | TL0[7:0] | Timer 0 Low Byte.                                       |

|----|----------|---------------------------------------------------------|

|    |          | The TL0 register is the low byte of the 16-bit Timer 0. |

## SFR Definition 25.5. TL1: Timer 1 Low Byte

| Bit   | 7             | 7 6 5 4 3 2 1 0                                         |                   |   |   |   |   |   |  |

|-------|---------------|---------------------------------------------------------|-------------------|---|---|---|---|---|--|

| Nam   | TL1[7:0]      |                                                         |                   |   |   |   |   |   |  |

| Туре  | •             | R/W                                                     |                   |   |   |   |   |   |  |

| Rese  | <b>t</b> 0    | 0                                                       | 0                 | 0 | 0 | 0 | 0 | 0 |  |

| SFR F | Page = 0x0; S | FR Address :                                            | = 0x8B            |   |   |   |   |   |  |

| Bit   | Name          | me Function                                             |                   |   |   |   |   |   |  |

| 7:0   | TL1[7:0]      | Timer 1 Lo                                              | Timer 1 Low Byte. |   |   |   |   |   |  |

|       |               | The TL1 register is the low byte of the 16-bit Timer 1. |                   |   |   |   |   |   |  |

## SFR Definition 25.6. TH0: Timer 0 High Byte

|          |                | _            | _        |   | _ |   |   | _ |

|----------|----------------|--------------|----------|---|---|---|---|---|

| Bit      | 7              | 6            | 5        | 4 | 3 | 2 | 1 | 0 |

| Nam      | e TH0[7:0]     |              |          |   |   |   |   |   |

| Type R/W |                |              |          |   |   |   |   |   |

| Rese     | et 0           | 0            | 0        | 0 | 0 | 0 | 0 | 0 |

| SFR F    | Page = 0x0; SI | FR Address = | = 0x8C   |   |   |   |   |   |

| Bit      | Name           | Function     |          |   |   |   |   |   |

| 7:0      | TH0[7:0]       | Timer 0 Hig  | gh Byte. |   |   |   |   |   |

The TH0 register is the high byte of the 16-bit Timer 0.

## SFR Definition 25.7. TH1: Timer 1 High Byte

| Bit   | 7             | 6         5         4         3         2         1         0 |                                                          |   |   |   |   |   |  |

|-------|---------------|---------------------------------------------------------------|----------------------------------------------------------|---|---|---|---|---|--|

| Nam   | TH1[7:0]      |                                                               |                                                          |   |   |   |   |   |  |

| Туре  | •             | R/W                                                           |                                                          |   |   |   |   |   |  |

| Rese  | et 0          | 0                                                             | 0                                                        | 0 | 0 | 0 | 0 | 0 |  |

| SFR F | Page = 0x0; S | FR Address :                                                  | = 0x8D                                                   |   |   |   |   |   |  |

| Bit   | Name          | Function                                                      |                                                          |   |   |   |   |   |  |

| 7:0   | TH1[7:0]      | Timer 1 Hig                                                   | Timer 1 High Byte.                                       |   |   |   |   |   |  |

|       |               | The TH1 re                                                    | The TH1 register is the high byte of the 16-bit Timer 1. |   |   |   |   |   |  |

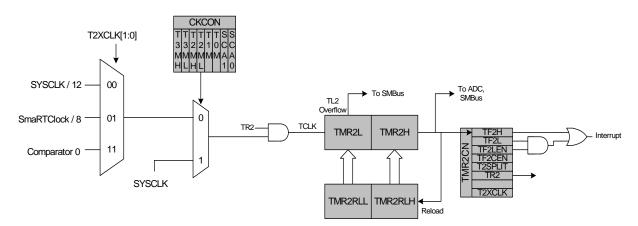

### 25.2. Timer 2

Timer 2 is a 16-bit timer formed by two 8-bit SFRs: TMR2L (low byte) and TMR2H (high byte). Timer 2 may operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T2SPLIT bit (TMR2CN.3) defines the Timer 2 operation mode. Timer 2 can also be used in Capture Mode to measure the SmaRTClock or the Comparator 0 period with respect to another oscillator. The ability to measure the Comparator 0 period with respect to the system clock is makes using Touch Sense Switches very easy.

Timer 2 may be clocked by the system clock, the system clock divided by 12, SmaRTClock divided by 8, or Comparator 0 output. Note that the SmaRTClock divided by 8 and Comparator 0 output is synchronized with the system clock.

#### 25.2.1. 16-bit Timer with Auto-Reload

When T2SPLIT (TMR2CN.3) is zero, Timer 2 operates as a 16-bit timer with auto-reload. Timer 2 can be clocked by SYSCLK, SYSCLK divided by 12, SmaRTClock divided by 8, or Comparator 0 output. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 2 reload registers (TMR2RLH and TMR2RLL) is loaded into the Timer 2 register as shown in Figure 25.4, and the Timer 2 High Byte Overflow Flag (TMR2CN.7) is set. If Timer 2 interrupts are enabled (if IE.5 is set), an interrupt will be generated on each Timer 2 overflow. Additionally, if Timer 2 interrupts are enabled and the TF2LEN bit is set (TMR2CN.5), an interrupt will be generated each time the lower 8 bits (TMR2L) overflow from 0xFF to 0x00.

Figure 25.4. Timer 2 16-Bit Mode Block Diagram

## **CONTACT INFORMATION**

#### Silicon Laboratories Inc.

400 West Cesar Chavez Austin, TX 78701

Please visit the Silicon Labs Technical Support web page: https://www.silabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc. Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.