Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                               |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 16                                                                |

| Program Memory Size        | 16KB (16K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 768 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                       |

| Data Converters            | A/D 15x10b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 24-WFQFN Exposed Pad                                              |

| Supplier Device Package    | 24-QFN (4x4)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f911-d-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Tables**

| 2                                                                                       | 26  |

|-----------------------------------------------------------------------------------------|-----|

| Table 2.1. Product Selection Guide                                                      | 26  |

| Table 3.1. Pin Definitions for the C8051F91x-C8051F90x                                  | 27  |

| Table 3.2. QFN-24 Package Dimensions                                                    | 32  |

| Table 3.3. PCB Land Pattern                                                             | 33  |

| Table 3.4. QSOP-24 Package Dimensions                                                   | 34  |

| Table 3.5. PCB Land Pattern                                                             | 35  |

| Table 4.1. Absolute Maximum Ratings                                                     | 36  |

| Table 4.2. Global Electrical Characteristics                                            |     |

| Table 4.3. Port I/O DC Electrical Characteristics                                       | 47  |

| Table 4.4. Reset Electrical Characteristics                                             |     |

| Table 4.5. Power Management Electrical Specifications                                   | 53  |

| Table 4.6. Flash Electrical Characteristics                                             | 53  |

| Table 4.7. Internal Precision Oscillator Electrical Characteristics                     | 53  |

| Table 4.8. Internal Low-Power Oscillator Electrical Characteristics                     | 53  |

| Table 4.9. SmaRTClock Characteristics                                                   | 54  |

| Table 4.10. ADC0 Electrical Characteristics                                             | 54  |

| Table 4.11. Temperature Sensor Electrical Characteristics                               | 55  |

| Table 4.12. Voltage Reference Electrical Characteristics                                |     |

| Table 4.13. IREF0 Electrical Characteristics                                            |     |

| Table 4.14. Comparator Electrical Characteristics                                       |     |

| Table 4.15. VREG0 Electrical Characteristics                                            |     |

| Table 4.16. DC-DC Converter (DC0) Electrical Characteristics                            |     |

| Table 5.1. Representative Conversion Times and Energy Consumption for the SAF           |     |

| ADC with 1.65 V High-Speed VREF                                                         |     |

| Table 8.1. CIP-51 Instruction Set Summary    1                                          |     |

| Table 11.1. Special Function Register (SFR) Memory Map (Page 0x0)         1             |     |

| Table 11.2. Special Function Register (SFR) Memory Map (Page 0xF)         1             |     |

| Table 11.3. Special Function Registers    1                                             |     |

| Table 12.1. Interrupt Summary    1                                                      |     |

| Table 13.1. Flash Security Summary    1                                                 |     |

| Table 14.1. Power Modes    1                                                            |     |

| Table 15.1. Example 16-bit CRC Outputs    1                                             |     |

| Table 16.1. IPeak Inductor Current Limit Settings    1                                  |     |

| Table 19.1. Recommended XFCN Settings for Crystal Mode         1                        |     |

| Table 19.2. Recommended XFCN Settings for RC and C modes         1                      |     |

| Table 20.1. SmaRTClock Internal Registers    1                                          | 89  |

| Table 20.2. SmaRTClock Load Capacitance Settings         1                              |     |

| Table 20.3. SmaRTClock Bias Settings    1                                               |     |

| Table 21.1. Port I/O Assignment for Analog Functions    2                               |     |

| Table 21.2. Port I/O Assignment for Digital Functions    2                              |     |

| Table 21.3. Port I/O Assignment for External Digital Event Capture Functions         20 |     |

| Table 22.1. SMBus Clock Source Selection    2                                           | :30 |

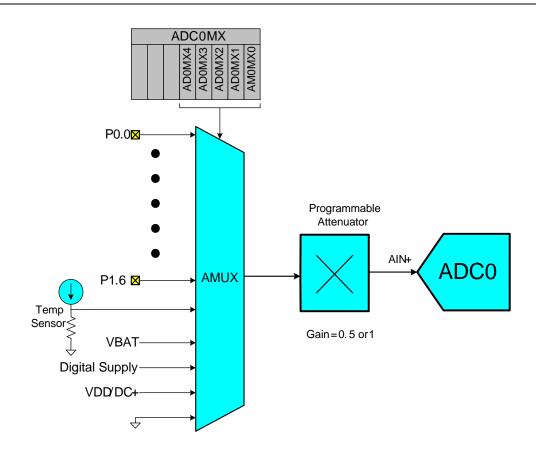

Figure 1.8. ADC0 Multiplexer Block Diagram

### 1.6. Programmable Current Reference (IREF0)

C8051F91x-C8051F90x devices include an on-chip programmable current reference (source or sink) with two output current settings: low power mode and high current mode. The maximum current output in low power mode is 63  $\mu$ A (1  $\mu$ A steps) and the maximum current output in high current mode is 504  $\mu$ A (8  $\mu$ A steps).

### 1.7. Comparators

C8051F91x-C8051F90x devices include two on-chip programmable voltage comparators: Comparator 0 (CPT0) which is shown in Figure 1.9; Comparator 1 (CPT1) which is shown in Figure 1.10. The two comparators operate identically but may differ in their ability to be used as reset or wake-up sources. See Section "18. Reset Sources" on page 171 and the Section "14. Power Management" on page 143 for details on reset sources and low power mode wake-up sources, respectively.

The Comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a synchronous "latched" output (CP0, CP1), or an asynchronous "raw" output (CP0A, CP1A). The asynchronous CP0A signal is available even when the system clock is not active. This allows the Comparator to operate and generate an output when the device is in some low power modes.

The comparator inputs may be connected to Port I/O pins or to other internal signals. Port pins may also be used to directly sense capacitive touch switches.

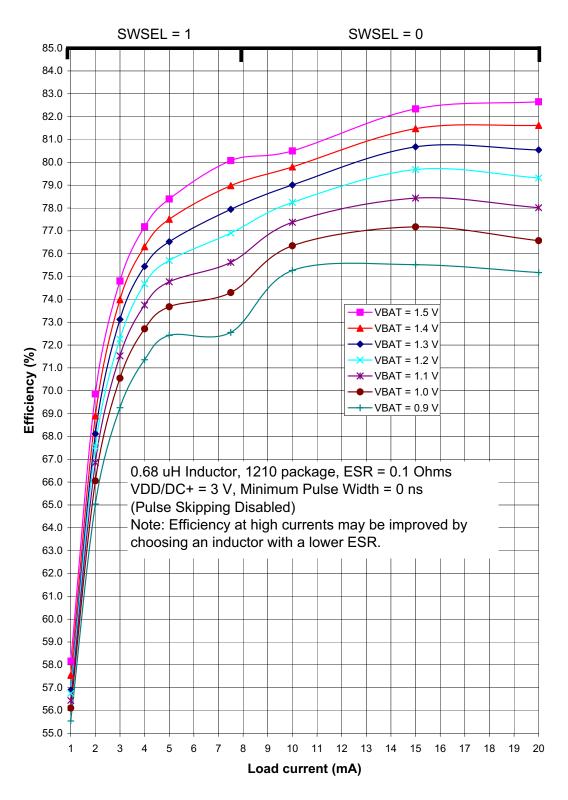

Figure 4.4. Typical DC-DC Converter Efficiency (High Current, VDD/DC+ = 3 V)

### Table 4.10. ADC0 Electrical Characteristics (Continued)

$V_{DD}$  = 1.8 to 3.6V V, VREF = 1.65 V (REFSL[1:0] = 11), -40 to +85 °C unless otherwise specified.

| Parameter                                                  | Conditions                                           | Min             | Тур        | Max    | Units |

|------------------------------------------------------------|------------------------------------------------------|-----------------|------------|--------|-------|

| Analog Inputs                                              |                                                      |                 |            |        |       |

| ADC Input Voltage Range                                    | Single Ended (AIN+ – GND)                            | 0               | —          | VREF   | V     |

| Absolute Pin Voltage with respect to GND                   | Single Ended                                         | V <sub>DD</sub> | V          |        |       |

| Sampling Capacitance<br>(C8051F912/11/02/01)               | 1x Gain<br>0.5x Gain                                 |                 | 28<br>26   |        | pF    |

| Input Multiplexer Impedance                                |                                                      | _               | 5          | —      | kΩ    |

| Power Specifications                                       | ••                                                   |                 | •          |        |       |

| Power Supply Current<br>(V <sub>DD</sub> supplied to ADC0) | Conversion Mode (300 ksps)<br>Tracking Mode (0 ksps) | _               | 720<br>680 | —<br>— | μA    |

| Power Supply Rejection                                     | Internal High Speed VREF<br>External VREF            | _               | 67<br>74   |        | dB    |

| Notes:                                                     |                                                      |                 | 1          | 1      |       |

1. Blue indicates a feature only available on 'F912 and 'F902 devices.

2. INL and DNL specifications for 12-bit mode do not include the first or last four ADC codes.

3. The maximum code in 12-bit mode is 0xFFFC. The Full Scale Error is referenced from the maximum code.

**4.** Performance in 8-bit mode is similar to 10-bit mode.

### Table 4.11. Temperature Sensor Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6V V, -40 to +85 °C unless otherwise specified.

| Parameter                                        | Conditions                                   | Min | Тур  | Max        | Units |

|--------------------------------------------------|----------------------------------------------|-----|------|------------|-------|

| Linearity                                        |                                              |     | ±1   | —          | °C    |

| Slope                                            |                                              | —   | 3.40 |            | mV/°C |

| Slope Error <sup>1</sup>                         |                                              | —   | 40   | —          | μV/°C |

| Offset                                           | Temp = 25 °C                                 | —   | 1025 |            | mV    |

| Offset Error <sup>1</sup>                        | Temp = 25 °C                                 | —   | 18   | —          | mV    |

| Temperature Sensor Settling<br>Time <sup>2</sup> | Initial Voltage=0 V<br>Initial Voltage=3.6 V | -   |      | 3.0<br>6.5 | μs    |

| Supply Current                                   |                                              | —   | 35   |            | μΑ    |

Notes:

1. Represents one standard deviation from the mean.

2. The temperature sensor settling time, resulting from an ADC mux change or enabling of the temperature sensor, varies with the voltage of the previously sampled channel and can be up to 6 µs if the previously sampled channel voltage was greater than 3 V. To minimize the temperature sensor settling time, the ADC mux can be momentarily set to ground before being set to the temperature sensor output. This ensures that the temperature sensor output will settle in 3 µs or less.

### 5.1. Output Code Formatting

The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code from the ADC at the completion of each conversion. Data can be right-justified or left-justified, depending on the setting of the AD0SJST[2:0]. When the repeat count is set to 1, conversion codes are represented as 10-bit unsigned integers. Inputs are measured from 0 to VREF x 1023/1024. Example codes are shown below for both right-justified and left-justified data. Unused bits in the ADC0H and ADC0L registers are set to 0.

| Input Voltage    | Right-Justified ADC0H:ADC0L<br>(AD0SJST = 000) | Left-Justified ADC0H:ADC0L<br>(AD0SJST = 100) |

|------------------|------------------------------------------------|-----------------------------------------------|

| VREF x 1023/1024 | 0x03FF                                         | 0xFFC0                                        |

| VREF x 512/1024  | 0x0200                                         | 0x8000                                        |

| VREF x 256/1024  | 0x0100                                         | 0x4000                                        |

| 0                | 0x0000                                         | 0x0000                                        |

When the repeat count is greater than 1, the output conversion code represents the accumulated result of the conversions performed and is updated after the last conversion in the series is finished. Sets of 4, 8, 16, 32, or 64 consecutive samples can be accumulated and represented in unsigned integer format. The repeat count can be selected using the ADORPT bits in the ADCOAC register. When a repeat count higher than 1, the ADC output must be right-justified (ADOSJST = 0xx); unused bits in the ADCOH and ADCOL registers are set to 0. The example below shows the right-justified result for various input voltages and repeat counts. Notice that accumulating  $2^n$  samples is equivalent to left-shifting by *n* bit positions when all samples returned from the ADC have the same value.

| Input Voltage                | Repeat Count = 4 | Repeat Count = 16 | Repeat Count = 64 |

|------------------------------|------------------|-------------------|-------------------|

| V <sub>REF</sub> x 1023/1024 | 0x0FFC           | 0x3FF0            | 0xFFC0            |

| V <sub>REF</sub> x 512/1024  | 0x0800           | 0x2000            | 0x8000            |

| V <sub>REF</sub> x 511/1024  | 0x07FC           | 0x1FF0            | 0x7FC0            |

| 0                            | 0x0000           | 0x0000            | 0x0000            |

The AD0SJST bits can be used to format the contents of the 16-bit accumulator. The accumulated result can be shifted right by 1, 2, or 3 bit positions. Based on the principles of oversampling and averaging, the effective ADC resolution increases by 1 bit each time the oversampling rate is increased by a factor of 4. The example below shows how to increase the effective ADC resolution by 1, 2, and 3 bits to obtain an effective ADC resolution of 11-bit, 12-bit, or 13-bit respectively without CPU intervention.

| Input Voltage                | Repeat Count = 4<br>Shift Right = 1<br>11-Bit Result | Repeat Count = 16<br>Shift Right = 2<br>12-Bit Result | Repeat Count = 64<br>Shift Right = 3<br>13-Bit Result |

|------------------------------|------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

| V <sub>REF</sub> x 1023/1024 | 0x07F7                                               | 0x0FFC                                                | 0x1FF8                                                |

| V <sub>REF</sub> x 512/1024  | 0x0400                                               | 0x0800                                                | 0x1000                                                |

| V <sub>REF</sub> x 511/1024  | 0x03FE                                               | 0x04FC                                                | 0x0FF8                                                |

| 0                            | 0x0000                                               | 0x0000                                                | 0x0000                                                |

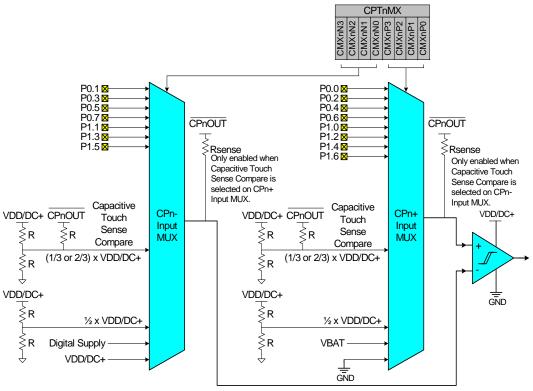

### 7.6. Comparator0 and Comparator1 Analog Multiplexers

Comparator0 and Comparator1 on C8051F91x-C8051F90x devices have analog input multiplexers to connect Port I/O pins and internal signals the comparator inputs; CP0+/CP0- are the positive and negative input multiplexers for Comparator0 and CP1+/CP1- are the positive and negative input multiplexers for Comparator1.

The comparator input multiplexers directly support capacitive touch switches. When the Capacitive Touch Sense Compare input is selected on the positive or negative multiplexer, any Port I/O pin connected to the other multiplexer can be directly connected to a capacitive touch switch with no additional external components. The Capacitive Touch Sense Compare provides the appropriate reference level for detecting when the capacitive touch switches have charged or discharged through the on-chip Rsense resistor. The Comparator outputs can be routed to Timer2 or Timer3 for capturing sense capacitor's charge and discharge time. See Section "25. Timers" on page 270 for details.

Any of the following may be selected as comparator inputs: Port I/O pins, Capacitive Touch Sense Compare, VDD/DC+ Supply Voltage, Regulated Digital Supply Voltage (Output of VREG0), the VBAT Supply voltage or ground. The Comparator's supply voltage divided by 2 is also available as an input; the resistors used to divide the voltage only draw current when this setting is selected. The Comparator input multiplexers are configured using the CPT0MX and CPT1MX registers described in SFR Definition 7.5 and SFR Definition 7.6.

Figure 7.4. CPn Multiplexer Block Diagram

**Important Note About Comparator Input Configuration:** Port pins selected as comparator inputs should be configured as analog inputs, and should be skipped by the Digital Crossbar. To configure a Port pin for analog input, set to 0 the corresponding bit in register PnMDIN and disable the digital driver (PnMDOUT = 0 and Port Latch = 1). To force the Crossbar to skip a Port pin, set to 1 the corresponding bit in register PnSKIP. See Section "21. Port Input/Output" on page 205 for more Port I/O configuration details.

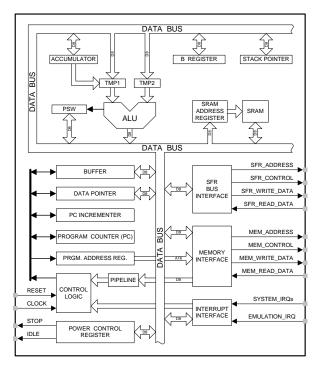

# 8. CIP-51 Microcontroller

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. The CIP-51 also includes on-chip debug hardware (see description in Section 27), and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 8.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 25 MIPS Peak Throughput with 25 MHz Clock

- 0 to 25 MHz Clock Frequency

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

### 8.1. Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

Figure 8.1. CIP-51 Block Diagram

### SFR Definition 11.1. SFR Page: SFR Page

| Bit   | 7   | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-----|--------------|---|---|---|---|---|---|--|--|

| Name  |     | SFRPAGE[7:0] |   |   |   |   |   |   |  |  |

| Туре  | R/W |              |   |   |   |   |   |   |  |  |

| Reset | 0   | 0            | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Page = All Pages; SFR Address = 0xA7

| Bit | Name         | Function                                                                                    |

|-----|--------------|---------------------------------------------------------------------------------------------|

| 7:0 | SFRPAGE[7:0] | SFR Page.                                                                                   |

|     |              | Specifies the SFR Page used when reading, writing, or modifying special function registers. |

### Table 11.3. Special Function Registers

SFRs are listed in alphabetical order. All undefined SFR locations are reserved. SFRs highlighted in **blue** are only available on 'F912 and 'F902 devices.

| Register | Address | SFR Page | Description                      | Page |

|----------|---------|----------|----------------------------------|------|

| ACC      | 0xE0    | All      | Accumulator                      | 105  |

| ADC0AC   | 0xBA    | 0x0      | ADC0 Accumulator Configuration   | 71   |

| ADC0CF   | 0xBC    | 0x0      | ADC0 Configuration               | 70   |

| ADC0CN   | 0xE8    | 0x0      | ADC0 Control                     | 69   |

| ADC0GTH  | 0xC4    | 0x0      | ADC0 Greater-Than Compare High   | 75   |

| ADC0GTL  | 0xC3    | 0x0      | ADC0 Greater-Than Compare Low    | 75   |

| ADC0H    | 0xBE    | 0x0      | ADC0 High                        | 74   |

| ADC0L    | 0xBD    | 0x0      | ADC0 Low                         | 74   |

| ADC0LTH  | 0xC6    | 0x0      | ADC0 Less-Than Compare Word High | 76   |

| ADC0LTL  | 0xC5    | 0x0      | ADC0 Less-Than Compare Word Low  | 76   |

| ADC0MX   | 0xBB    | 0x0      | AMUX0 Channel Select             | 79   |

| ADC0PWR  | 0xBA    | 0xF      | ADC0 Burst Mode Power-Up Time    | 72   |

| ADC0TK   | 0xBD    | 0xF      | ADC0 Tracking Control            | 73   |

| В        | 0xF0    | All      | B Register                       | 105  |

| CKCON    | 0x8E    | 0x0      | Clock Control                    | 271  |

| CLKSEL   | 0xA9    | All      | Clock Select                     | 185  |

| CPT0CN   | 0x9B    | 0x0      | Comparator0 Control              | 92   |

| CPT0MD   | 0x9D    | 0x0      | Comparator0 Mode Selection       | 92   |

| CPT0MX   | 0x9F    | 0x0      | Comparator0 Mux Selection        | 96   |

| CPT1CN   | 0x9A    | 0x0      | Comparator1 Control              | 93   |

### Table 11.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved. SFRs highlighted in **blue** are only available on 'F912 and 'F902 devices.

| Register | Address | SFR Page | Description                       | Page |

|----------|---------|----------|-----------------------------------|------|

| PCA0MD   | 0xD9    | 0x0      | PCA0 Mode                         | 307  |

| PCA0PWM  | 0xDF    | 0x0      | PCA0 PWM Configuration            | 308  |

| PCON     | 0x87    | 0x0      | Power Control                     | 151  |

| PMU0CF   | 0xB5    | 0x0      | PMU0 Configuration                | 149  |

| PMU0MD   | 0xB5    | 0xF      | PMU0 Mode                         | 150  |

| PSCTL    | 0x8F    | 0x0      | Program Store R/W Control         | 140  |

| PSW      | 0xD0    | All      | Program Status Word               | 106  |

| REF0CN   | 0xD1    | 0x0      | Voltage Reference Control         | 85   |

| REG0CN   | 0xC9    | 0x0      | Voltage Regulator (VREG0) Control | 170  |

| RSTSRC   | 0xEF    | 0x0      | Reset Source Configuration/Status | 178  |

| RTC0ADR  | 0xAC    | 0x0      | RTC0 Address                      | 193  |

| RTC0DAT  | 0xAD    | 0x0      | RTC0 Data                         | 193  |

| RTC0KEY  | 0xAE    | 0x0      | RTC0 Key                          | 192  |

| SBUF0    | 0x99    | 0x0      | UART0 Data Buffer                 | 253  |

| SCON0    | 0x98    | 0x0      | UART0 Control                     | 252  |

| SFRPAGE  | 0xA7    | All      | SFR Page                          | 115  |

| SMB0ADM  | 0xF5    | 0x0      | SMBus Slave Address Mask          | 237  |

| SMB0ADR  | 0xF4    | 0x0      | SMBus Slave Address               | 237  |

| SMB0CF   | 0xC1    | 0x0      | SMBus Configuration               | 232  |

| SMB0CN   | 0xC0    | 0x0      | SMBus Control                     | 234  |

| SMB0DAT  | 0xC2    | 0x0      | SMBus Data                        | 238  |

| SP       | 0x81    | All      | Stack Pointer                     | 105  |

| SPI0CFG  | 0xA1    | 0x0      | SPI0 Configuration                | 263  |

| SPI0CKR  | 0xA2    | 0x0      | SPI0 Clock Rate Control           | 265  |

| SPI0CN   | 0xF8    | 0x0      | SPI0 Control                      | 264  |

| SPI0DAT  | 0xA3    | 0x0      | SPI0 Data                         | 266  |

| SPI1CFG  | 0x84    | 0x0      | SPI1 Configuration                | 263  |

| SPI1CKR  | 0x85    | 0x0      | SPI1 Clock Rate Control           | 265  |

| SPI1CN   | 0xB0    | 0x0      | SPI1 Control                      | 264  |

| SPI1DAT  | 0x86    | 0x0      | SPI1 Data                         | 266  |

| TCON     | 0x88    | 0x0      | Timer/Counter Control             | 276  |

| TH0      | 0x8C    | 0x0      | Timer/Counter 0 High              | 279  |

| TH1      | 0x8D    | 0x0      | Timer/Counter 1 High              | 279  |

### 15.2. Preparing for a CRC Calculation

To prepare CRC0 for a CRC calculation, software should select the desired polynomial and set the initial value of the result. Two polynomials are available: 0x1021 (16-bit) and 0x04C11DB7 (32-bit). The CRC0 result may be initialized to one of two values: 0x00000000 or 0xFFFFFFFF. The following steps can be used to initialize CRC0.

- 1. Select a polynomial (Set CRC0SEL to 0 for 32-bit or 1 for 16-bit).

- 2. Select the initial result value (Set CRC0VAL to 0 for 0x0000000 or 1 for 0xFFFFFFF).

- 3. Set the result to its initial value (Write 1 to CRC0INIT).

### **15.3.** Performing a CRC Calculation

Once CRC0 is initialized, the input data stream is sequentially written to CRC0IN, one byte at a time. The CRC0 result is automatically updated after each byte is written. The CRC engine may also be configured to automatically perform a CRC on one or more Flash sectors. The following steps can be used to automatically perform a CRC on Flash memory.

- 1. Prepare CRC0 for a CRC calculation as shown above.

- 2. Write the index of the starting page to CRC0AUTO.

- 3. Set the AUTOEN bit in CRC0AUTO.

- 4. Write the number of Flash sectors to perform in the CRC calculation to CRC0CNT. Note: Each Flash sector is 512 bytes on 'F91x and 'F90x devices.

- 5. Write any value to CRC0CN (or OR its contents with 0x00) to initiate the CRC calculation. The CPU will not execute code any additional code until the CRC operation completes. See the note in SFR Definition 15.1. CRC0CN: CRC0 Control for more information on how to properly initiate a CRC calculation.

- 6. Clear the AUTOEN bit in CRC0AUTO.

- 7. Read the CRC result using the procedure below.

### 15.4. Accessing the CRC0 Result

The internal CRC0 result is 32-bits (CRC0SEL = 0b) or 16-bits (CRC0SEL = 1b). The CRC0PNT bits select the byte that is targeted by read and write operations on CRC0DAT and increment after each read or write. The calculation result will remain in the internal CR0 result register until it is set, overwritten, or additional data is written to CRC0IN.

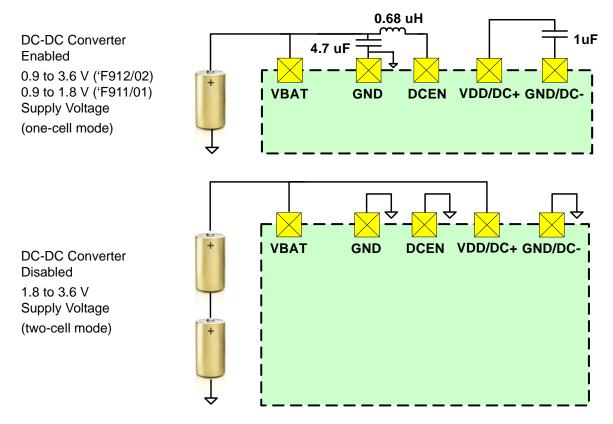

### 16.4. Enabling the DC-DC Converter

On power-on reset, the state of the DCEN pin is sampled to determine if the device will power up in onecell or two-cell mode. In two-cell mode, the dc-dc converter always remains disabled. In one-cell mode, the dc-dc converter remains disabled in Sleep Mode, and enabled in all other power modes. See Section "14. Power Management" on page 143 for complete details on available power modes.

The dc-dc converter is enabled (one-cell mode) in hardware by placing a 0.68  $\mu$ H inductor between DCEN and VBAT. The dc-dc converter is disabled (two-cell mode) by shorting DCEN directly to GND. The DCEN pin should never be left floating. The device can only switch between one-cell and two-cell mode during a power-on reset. See Section "18. Reset Sources" on page 171 for more information regarding reset behavior.

Figure 16.2 shows the two dc-dc converter configuration options.

Figure 16.2. DC-DC Converter Configuration Options

When the dc-dc converter "Enabled" configuration (one-cell mode) is chosen, the following guidelines apply:

- In most cases, the GND/DC- pin should not be externally connected to GND.

- The 0.68 µH inductor should be placed as close as possible to the DCEN pin for maximum efficiency.

- The 4.7 µF capacitor should be placed as close as possible to the inductor.

- The current loop including GND, the 4.7  $\mu$ F capacitor, the 0.68  $\mu$ H inductor and the DCEN pin should be made as short as possible.

- The PCB traces connecting VDD/DC+ to the output capacitor and the output capacitor to GND/DC- should be as short and as thick as possible in order to minimize parasitic inductance.

## SFR Definition 16.2. DC0CF: DC-DC Converter Configuration

| Bit   | 7    | 6    | 5       | 4        | 3      | 2      | 1      | 0      |

|-------|------|------|---------|----------|--------|--------|--------|--------|

| Name  | LPEN | CLKD | IV[1:0] | AD0CKINV | CLKINV | ILIMIT | VDDSLP | CLKSEL |

| Туре  | R/W  | R/W  | R/W     | R/W      | R/W    | R/W    | R/W    | R/W    |

| Reset | 0    | 0    | 0       | 0        | 0      | 0      | 0      | 0      |

SFR Page = 0x0; SFR Address = 0x96

| Bit | Name        | Function                                                                                                                                                                                           |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | LPEN        | Low Power Mode Enable.                                                                                                                                                                             |

|     |             | Enables the dc-dc low power mode which reduces bias currents, reduces peak inductor current, and increases efficiency for low load currents. Only available on 'F912 and 'F902 devices.            |

|     |             | 0: Low Power Mode Disabled.<br>1: Low Power Mode Enabled.                                                                                                                                          |

| 6:5 | CLKDIV[1:0] | DC-DC Clock Divider.                                                                                                                                                                               |

|     |             | Divides the dc-dc converter clock when the system clock is selected as the clock source for dc-dc converter. These bits are ignored when the dc-dc converter is clocked from its local oscillator. |

|     |             | 00: The dc-dc converter clock is system clock divided by 1.                                                                                                                                        |

|     |             | 01: The dc-dc converter clock is system clock divided by 2.                                                                                                                                        |

|     |             | <ol> <li>The dc-dc converter clock is system clock divided by 4.</li> <li>The dc-dc converter clock is system clock divided by 8.</li> </ol>                                                       |

| 4   | AD0CKINV    | ADC0 Clock Inversion (Clock Invert During Sync).                                                                                                                                                   |

| -   | ADUCKINV    | Inverts the ADC0 SAR clock derived from the dc-dc converter clock when the SYNC                                                                                                                    |

|     |             | bit (DC0CN.3) is enabled. This bit is ignored when the SYNC bit is set to zero.                                                                                                                    |

|     |             | 0: ADC0 SAR clock is inverted.                                                                                                                                                                     |

|     |             | 1: ADC0 SAR clock is not inverted.                                                                                                                                                                 |

| 3   | CLKINV      | DC-DC Converter Clock Invert.                                                                                                                                                                      |

|     |             | Inverts the system clock used as the input to the dc-dc clock divider.                                                                                                                             |

|     |             | 0: The dc-dc converter clock is not inverted.                                                                                                                                                      |

|     |             | 1: The dc-dc converter clock is inverted.                                                                                                                                                          |

| 2   | ILIMIT      | Peak Current Limit Threshold.                                                                                                                                                                      |

|     |             | Sets the threshold for the maximum allowed peak inductor current according to Table 16.1.                                                                                                          |

| 1   | VDDSLP      | VDD-DC+ Sleep Mode Connection.                                                                                                                                                                     |

|     |             | Specifies the power source for VDD/DC+ in Sleep Mode when the dc-dc converter is enabled.                                                                                                          |

|     |             | <ul><li>0: VDD-DC+ connected to VBAT in Sleep Mode.</li><li>1: VDD-DC+ is floating in Sleep Mode.</li></ul>                                                                                        |

| 0   | CLKSEL      | DC-DC Converter Clock Source Select.                                                                                                                                                               |

|     |             | Specifies the dc-dc converter clock source.                                                                                                                                                        |

|     |             | 0: The dc-dc converter is clocked from its local oscillator.                                                                                                                                       |

|     |             | 1: The dc-dc converter is clocked from the system clock.                                                                                                                                           |

### SFR Definition 19.2. OSCICN: Internal Oscillator Control

| Bit   | 7      | 6     | 5             | 4      | 3      | 2      | 1      | 0      |

|-------|--------|-------|---------------|--------|--------|--------|--------|--------|

| Name  | IOSCEN | IFRDY | Reserved[5:0] |        |        |        |        |        |

| Туре  | R/W    | R     | R/W           | R/W    | R/W    | R/W    | R/W    | R/W    |

| Reset | 0      | 0     | Varies        | Varies | Varies | Varies | Varies | Varies |

SFR Page = 0x0; SFR Address = 0xB2

| Bit | Name     | Function                                                           |

|-----|----------|--------------------------------------------------------------------|

| 7   | IOSCEN   | Internal Oscillator Enable.                                        |

|     |          | 0: Internal oscillator disabled.                                   |

|     |          | 1: Internal oscillator enabled.                                    |

| 6   | IFRDY    | Internal Oscillator Frequency Ready Flag.                          |

|     |          | 0: Internal oscillator is not running at its programmed frequency. |

|     |          | 1: Internal oscillator is running at its programmed frequency.     |

| 5:0 | Reserved | Reserved.                                                          |

|     |          | Must perform read-modify-write.                                    |

Note: Read-modify-write operations such as ORL and ANL must be used to set or clear the enable bit of this register.

### SFR Definition 19.3. OSCICL: Internal Oscillator Calibration

| Bit   | 7   | 6      | 5           | 4      | 3      | 2      | 1      | 0      |  |

|-------|-----|--------|-------------|--------|--------|--------|--------|--------|--|

| Name  | SSE |        | OSCICL[6:0] |        |        |        |        |        |  |

| Туре  | R/W | R      | R/W         | R/W    | R/W    | R/W    | R/W    | R/W    |  |

| Reset | 0   | Varies | Varies      | Varies | Varies | Varies | Varies | Varies |  |

SFR Page = 0x0; SFR Address = 0xB3

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                      |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SSE    | Spread Spectrum Enable.                                                                                                                                                                                                                                                                                                       |

|     |        | 0: Spread Spectrum clock dithering disabled.                                                                                                                                                                                                                                                                                  |

|     |        | 1: Spread Spectrum clock dithering enabled.                                                                                                                                                                                                                                                                                   |

| 6:0 | OSCICL | Internal Oscillator Calibration.                                                                                                                                                                                                                                                                                              |

|     |        | Factory calibrated to obtain a frequency of 24.5 MHz. Incrementing this register decreases the oscillator frequency and decrementing this register increases the oscillator frequency. The step size is approximately 1% of the calibrated frequency. The recommended calibration frequency range is between 16 and 24.5 MHz. |

### 20.1.5. RTC0ADR Autoincrement Feature

For ease of reading and writing the 32-bit CAPTURE and ALARM values, RTC0ADR automatically increments after each read or write to a CAPTUREn or ALARMn register. This speeds up the process of setting an alarm or reading the current SmaRTClock timer value. Autoincrement is always enabled.

Recommended Instruction Timing for a multi-byte register read with short strobe and auto read enabled:

mov RTCOADR, #0d0h

nop

nop

mov A, RTCODAT

nop

mov A, RTCODAT

nop

nop

mov A, RTCODAT

nop

nop

mov A, RTCODAT

nop

nop

mov A, RTCODAT

Recommended Instruction Timing for a multi-byte register write with short strobe enabled:

mov RTCOADR, #010h

mov RTCODAT, #05h

nop

mov RTCODAT, #06h

nop

mov RTCODAT, #07h

nop

mov RTCODAT, #08h

nop

master continues its transmission without interruption; the losing master becomes a slave and receives the rest of the transfer if addressed. This arbitration scheme is non-destructive: one device always wins, and no data is lost.

### 22.3.3. Clock Low Extension

SMBus provides a clock synchronization mechanism, similar to I<sup>2</sup>C, which allows devices with different speed capabilities to coexist on the bus. A clock-low extension is used during a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

#### 22.3.4. SCL Low Timeout

If the SCL line is held low by a slave device on the bus, no further communication is possible. Furthermore, the master cannot force the SCL line high to correct the error condition. To solve this problem, the SMBus protocol specifies that devices participating in a transfer must detect any clock cycle held low longer than 25 ms as a "timeout" condition. Devices that have detected the timeout condition must reset the communication no later than 10 ms after detecting the timeout condition.

When the SMBTOE bit in SMB0CF is set, Timer 3 is used to detect SCL low timeouts. Timer 3 is forced to reload when SCL is high, and allowed to count when SCL is low. With Timer 3 enabled and configured to overflow after 25 ms (and SMBTOE set), the Timer 3 interrupt service routine can be used to reset (disable and re-enable) the SMBus in the event of an SCL low timeout.

### 22.3.5. SCL High (SMBus Free) Timeout

The SMBus specification stipulates that if the SCL and SDA lines remain high for more that 50 µs, the bus is designated as free. When the SMBFTE bit in SMB0CF is set, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods (as defined by the timer configured for the SMBus clock source). If the SMBus is waiting to generate a Master START, the START will be generated following this timeout. Note that a clock source is required for free timeout detection, even in a slave-only implementation.

## SFR Definition 22.2. SMB0CN: SMBus Control

| Bit   | 7      | 6      | 5   | 4   | 3     | 2       | 1   | 0   |

|-------|--------|--------|-----|-----|-------|---------|-----|-----|

| Name  | MASTER | TXMODE | STA | STO | ACKRQ | ARBLOST | ACK | SI  |

| Туре  | R      | R      | R/W | R/W | R     | R       | R/W | R/W |

| Reset | 0      | 0      | 0   | 0   | 0     | 0       | 0   | 0   |

### SFR Page = 0x0; SFR Address = 0xC0; Bit-Addressable

| Bit | Name    | Description                                                                                                                                                                                                      | Read                                                                                                                       | Write                                                                                                                                                                                |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | MASTER  | SMBus Master/Slave<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a master.                                                                                                     | 0: SMBus operating in<br>slave mode.<br>1: SMBus operating in<br>master mode.                                              | N/A                                                                                                                                                                                  |

| 6   | TXMODE  | SMBus Transmit Mode<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a transmitter.                                                                                               | 0: SMBus in Receiver<br>Mode.<br>1: SMBus in Transmitter<br>Mode.                                                          | N/A                                                                                                                                                                                  |

| 5   | STA     | SMBus Start Flag.                                                                                                                                                                                                | 0: No Start or repeated<br>Start detected.<br>1: Start or repeated Start<br>detected.                                      | 0: No Start generated.<br>1: When Configured as a<br>Master, initiates a START<br>or repeated START.                                                                                 |

| 4   | STO     | SMBus Stop Flag.                                                                                                                                                                                                 | 0: No Stop condition<br>detected.<br>1: Stop condition detected<br>(if in Slave Mode) or pend-<br>ing (if in Master Mode). | 0: No STOP condition is<br>transmitted.<br>1: When configured as a<br>Master, causes a STOP<br>condition to be transmit-<br>ted after the next ACK<br>cycle.<br>Cleared by Hardware. |

| 3   | ACKRQ   | SMBus Acknowledge<br>Request.                                                                                                                                                                                    | 0: No Ack requested<br>1: ACK requested                                                                                    | N/A                                                                                                                                                                                  |

| 2   | ARBLOST | SMBus Arbitration Lost<br>Indicator.                                                                                                                                                                             | 0: No arbitration error.<br>1: Arbitration Lost                                                                            | N/A                                                                                                                                                                                  |

| 1   | ACK     | SMBus Acknowledge.                                                                                                                                                                                               | 0: NACK received.<br>1: ACK received.                                                                                      | 0: Send NACK<br>1: Send ACK                                                                                                                                                          |

| 0   | SI      | <b>SMBus Interrupt Flag.</b><br>This bit is set by hardware<br>under the conditions listed in<br>Table 15.3. SI must be cleared<br>by software. While SI is set,<br>SCL is held low and the<br>SMBus is stalled. | <b>0: No interrupt pending</b><br>1: Interrupt Pending                                                                     | <ul><li>0: Clear interrupt, and initiate next state machine event.</li><li>1: Force interrupt.</li></ul>                                                                             |

|                              |                              |                      | Fre                              | quency: 24.5 M        | Hz                                              |                  |                                  |

|------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

|                              | 230400                       | -0.32%               | 106                              | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xCB                             |

|                              | 115200                       | -0.32%               | 212                              | SYSCLK                | XX                                              | 1                | 0x96                             |

|                              | 57600                        | 0.15%                | 426                              | SYSCLK                | XX                                              | 1                | 0x2B                             |

| ы<br>С<br>С                  | 28800                        | -0.32%               | 848                              | SYSCLK/4              | 01                                              | 0                | 0x96                             |

| Os<br>Os                     | 14400                        | 0.15%                | 1704                             | SYSCLK/12             | 00                                              | 0                | 0xB9                             |

| al                           | 9600                         | -0.32%               | 2544                             | SYSCLK/12             | 00                                              | 0                | 0x96                             |

| SC<br>err                    | 2400                         | -0.32%               | 10176                            | SYSCLK/48             | 10                                              | 0                | 0x96                             |

| SYSCLK from<br>Internal Osc. | 1200                         | 0.15%                | 20448                            | SYSCLK/48             | 10                                              | 0                | 0x2B                             |

| Notes:                       |                              | d T1M bit definit    | tions can be fo                  | und in Section 25     | 1                                               |                  |                                  |

### Table 23.1. Timer Settings for Standard Baud Rates Using The Internal 24.5 MHz Oscillator

SCA1–SCA0 and T1M bit definitions can be found in Section 25.1.

2. X = Don't care.

### Table 23.2. Timer Settings for Standard Baud Rates Using an External 22.1184 MHz Oscillator

|                      |                              |                      | Frequ                            | uency: 22.1184        | MHz                                             |                  |                                  |

|----------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|

|                      | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

|                      | 230400                       | 0.00%                | 96                               | SYSCLK                | XX <b>2</b>                                     | 1                | 0xD0                             |

| c from<br>Osc.       | 115200                       | 0.00%                | 192                              | SYSCLK                | XX                                              | 1                | 0xA0                             |

|                      | 57600                        | 0.00%                | 384                              | SYSCLK                | XX                                              | 1                | 0x40                             |

|                      | 28800                        | 0.00%                | 768                              | SYSCLK / 12           | 00                                              | 0                | 0xE0                             |

|                      | 14400                        | 0.00%                | 1536                             | SYSCLK / 12           | 00                                              | 0                | 0xC0                             |

| SYSCLK<br>External ( | 9600                         | 0.00%                | 2304                             | SYSCLK / 12           | 00                                              | 0                | 0xA0                             |

| SC<br>ter            | 2400                         | 0.00%                | 9216                             | SYSCLK / 48           | 10                                              | 0                | 0xA0                             |

| SY<br>Ext            | 1200                         | 0.00%                | 18432                            | SYSCLK / 48           | 10                                              | 0                | 0x40                             |

|                      | 230400                       | 0.00%                | 96                               | EXTCLK / 8            | 11                                              | 0                | 0xFA                             |

| from<br>Jsc.         | 115200                       | 0.00%                | 192                              | EXTCLK / 8            | 11                                              | 0                | 0xF4                             |

| < fror<br>Osc.       | 57600                        | 0.00%                | 384                              | EXTCLK / 8            | 11                                              | 0                | 0xE8                             |

|                      | 28800                        | 0.00%                | 768                              | EXTCLK / 8            | 11                                              | 0                | 0xD0                             |

| SYSCL<br>Internal    | 14400                        | 0.00%                | 1536                             | EXTCLK / 8            | 11                                              | 0                | 0xA0                             |

| SY<br>Inte           | 9600                         | 0.00%                | 2304                             | EXTCLK / 8            | 11                                              | 0                | 0x70                             |

| Notes:               | 0044 0040                    |                      |                                  |                       |                                                 |                  |                                  |

1. SCA1–SCA0 and T1M bit definitions can be found in Section 25.1.

**2.** X = Don't care.

### SFR Definition 25.6. TH0: Timer 0 High Byte

|       |                | _            | _        |   | _ |   |   |   |  |  |

|-------|----------------|--------------|----------|---|---|---|---|---|--|--|

| Bit   | 7              | 6            | 5        | 4 | 3 | 2 | 1 | 0 |  |  |

| Nam   | e              | TH0[7:0]     |          |   |   |   |   |   |  |  |

| Туре  | Type R/W       |              |          |   |   |   |   |   |  |  |

| Rese  | et 0           | 0            | 0        | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR F | Page = 0x0; SI | FR Address = | = 0x8C   |   |   |   |   |   |  |  |

| Bit   | Name           |              | Function |   |   |   |   |   |  |  |

| 7:0   | TH0[7:0]       | Timer 0 Hig  | gh Byte. |   |   |   |   |   |  |  |

The TH0 register is the high byte of the 16-bit Timer 0.

### SFR Definition 25.7. TH1: Timer 1 High Byte

| Bit           | 7             | 6            | 5                  | 4            | 3              | 2      | 1 | 0 |  |  |

|---------------|---------------|--------------|--------------------|--------------|----------------|--------|---|---|--|--|

| Name TH1[7:0] |               |              |                    |              |                |        |   |   |  |  |

| Туре          | kype R/W      |              |                    |              |                |        |   |   |  |  |

| Rese          | et 0          | 0            | 0                  | 0            | 0              | 0      | 0 | 0 |  |  |

| SFR F         | Page = 0x0; S | FR Address : | = 0x8D             |              |                |        |   |   |  |  |

| Bit           | Name          |              |                    |              | Function       |        |   |   |  |  |

| 7:0           | TH1[7:0]      | Timer 1 Hig  | Timer 1 High Byte. |              |                |        |   |   |  |  |

|               |               | The TH1 re   | gister is the      | high byte of | the 16-bit Tir | mer 1. |   |   |  |  |

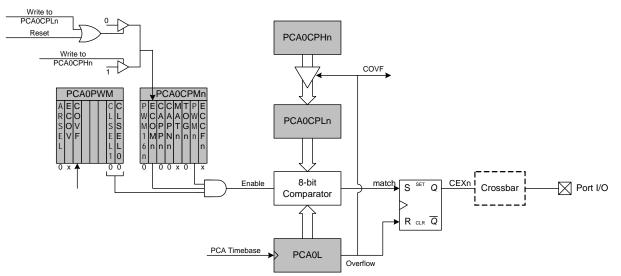

### 26.3.5. 8-Bit, 9-Bit, 10-Bit and 11-Bit Pulse Width Modulator Modes

Each module can be used independently to generate a pulse width modulated (PWM) output on its associated CEXn pin. The frequency of the output is dependent on the timebase for the PCA counter/timer, and the setting of the PWM cycle length (8, 9, 10 or 11-bits). For backwards-compatibility with the 8-bit PWM mode available on other devices, the 8-bit PWM mode operates slightly different than 9, 10 and 11-bit PWM modes. It is important to note that all channels configured for 8/9/10/11-bit PWM mode will use the same cycle length. It is not possible to configure one channel for 8-bit PWM mode and another for 11-bit mode (for example). However, other PCA channels can be configured to Pin Capture, High-Speed Output, Software Timer, Frequency Output, or 16-bit PWM mode independently.

#### 26.3.5.1. 8-Bit Pulse Width Modulator Mode

The duty cycle of the PWM output signal in 8-bit PWM mode is varied using the module's PCA0CPLn capture/compare register. When the value in the low byte of the PCA counter/timer (PCA0L) is equal to the value in PCA0CPLn, the output on the CEXn pin will be set. When the count value in PCA0L overflows, the CEXn output will be reset (see Figure 26.8). Also, when the counter/timer low byte (PCA0L) overflows from 0xFF to 0x00, PCA0CPLn is reloaded automatically with the value stored in the module's capture/compare high byte (PCA0CPHn) without software intervention. Setting the ECOMn and PWMn bits in the PCA0CPMn register, and setting the CLSEL bits in register PCA0PWM to 00b enables 8-Bit Pulse Width Modulator mode. If the MATn bit is set to 1, the CCFn flag for the module will be set each time an 8-bit comparator match (rising edge) occurs. The COVF flag in PCA0PWM can be used to detect the overflow (falling edge), which will occur every 256 PCA clock cycles. The duty cycle for 8-Bit PWM Mode is given in Equation 26.2.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =

$$\frac{(256 - PCA0CPHn)}{256}$$

Equation 26.2. 8-Bit PWM Duty Cycle

Using Equation 26.2, the largest duty cycle is 100% (PCA0CPHn = 0), and the smallest duty cycle is 0.39% (PCA0CPHn = 0xFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 26.8. PCA 8-Bit PWM Mode Diagram

## SFR Definition 26.2. PCA0MD: PCA Mode

| Bit   | 7          | 6                                                                                                                                                                                                                                                                                        | 5                                                                                                                                                                                                                                                       | 4                                                                                    | 3                                               | 2                                              | 1                       | 0        |  |  |

|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------|-------------------------|----------|--|--|

| Nam   | e CIDL     | WDTE                                                                                                                                                                                                                                                                                     | WDLCK                                                                                                                                                                                                                                                   |                                                                                      | CPS2                                            | CPS1                                           | CPS0                    | ECF      |  |  |

| Туре  | R/W        | R/W                                                                                                                                                                                                                                                                                      | R/W                                                                                                                                                                                                                                                     | R                                                                                    | R/W                                             | R/W                                            | R/W                     | R/W      |  |  |

| Rese  | t O        | 1                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                       | 0                                                                                    | 0                                               | 0                                              | 0                       | 0        |  |  |

| SFR F | age = 0x0; | SFR Address :                                                                                                                                                                                                                                                                            | = 0xD9                                                                                                                                                                                                                                                  |                                                                                      |                                                 |                                                | •                       |          |  |  |

| Bit   | Name       |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                         |                                                                                      | Function                                        |                                                |                         |          |  |  |

| 7     | CIDL       | Specifies PCA<br>0: PCA contin                                                                                                                                                                                                                                                           | PCA Counter/Timer Idle Control.<br>Specifies PCA behavior when CPU is in Idle Mode.<br>D: PCA continues to function normally while the system controller is in Idle Mode.<br>1: PCA operation is suspended while the system controller is in Idle Mode. |                                                                                      |                                                 |                                                |                         |          |  |  |

| 6     | WDTE       | If this bit is se<br>0: Watchdog                                                                                                                                                                                                                                                         | Vatchdog Timer Enable.         f this bit is set, PCA Module 2 is used as the watchdog timer.         b: Watchdog Timer disabled.         : PCA Module 2 enabled as Watchdog Timer.                                                                     |                                                                                      |                                                 |                                                |                         |          |  |  |

| 5     | WDLCK      | This bit locks/<br>Timer may no<br>0: Watchdog 1<br>1: Watchdog 1                                                                                                                                                                                                                        | Watchdog Timer Lock.<br>This bit locks/unlocks the Watchdog Timer Enable. When WDLCK is set, the Watchdog<br>Timer may not be disabled until the next system reset.<br>0: Watchdog Timer Enable unlocked.<br>1: Watchdog Timer Enable locked.           |                                                                                      |                                                 |                                                |                         |          |  |  |

| 4     | Unused     | Read = 0b, W                                                                                                                                                                                                                                                                             | rite = don't c                                                                                                                                                                                                                                          | are.                                                                                 |                                                 |                                                |                         |          |  |  |

| 3:1   | CPS[2:0]   | PCA Counter<br>These bits sel<br>000: System of<br>010: Timer 0 of<br>011: High-to-lo<br>100: System of<br>101: External<br>110: SmaRTO<br>able on 'F912<br>111: Reserved                                                                                                                | ect the time<br>clock divided<br>clock divided<br>overflow<br>ow transition<br>clock<br>clock divided<br>clock divided<br>and 'F902 d                                                                                                                   | base source<br>by 12<br>by 4<br>s on ECI (m<br>d by 8 (syncl<br><b>d by 8</b> (syncl | ax rate = sys<br>hronized with<br>chronized wit | stem clock di<br>n the system<br>th the systen | clock)<br>n clock and c |          |  |  |

| 0     | ECF        | <ul> <li>PCA Counter/Timer Overflow Interrupt Enable.</li> <li>This bit sets the masking of the PCA Counter/Timer Overflow (CF) interrupt.</li> <li>0: Disable the CF interrupt.</li> <li>1: Enable a PCA Counter/Timer Overflow interrupt request when CF (PCA0CN.7) is set.</li> </ul> |                                                                                                                                                                                                                                                         |                                                                                      |                                                 |                                                |                         |          |  |  |

| Note: |            | VDTE bit is set to<br>the PCA0MD reg                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         |                                                                                      |                                                 |                                                | odified. To cha         | ange the |  |  |